Table of Contents

Advertisement

Quick Links

FEATURES

Low cost 3.3 V CMOS MxFE

TM

12-bit D/A converter

2×/4× interpolation filter

200 MSPS DAC update rate

Integrated 23 dBm line driver with 19.5 dB gain control

12-bit, 80 MSPS A/D converter

−12 dB to +48 dB low noise RxPGA (< 2.5 nV/rtHz)

Third order, programmable low-pass filter

Flexible digital data path interface

Half- and full-duplex operation

Backward-compatible with AD9975 and AD9876

Various power-down/reduction modes

Internal clock multiplier (PLL)

2 auxiliary programmable clock outputs

Available in 64-lead chip scale package or bare die

APPLICATIONS

Powerline networking

VDSL and HPNA

GENERAL DESCRIPTION

The AD9866 is a mixed-signal front end (MxFE) IC for

transceiver applications requiring Tx and Rx path functionality

with data rates up to 80 MSPS. Its flexible digital interface, power

saving modes, and high Tx-to-Rx isolation make it well-suited

for half- and full-duplex applications. The digital interface is

extremely flexible allowing simple interfaces to digital back

ends that support half- or full-duplex data transfers, thus often

allowing the AD9866 to replace discrete ADC and DAC

solutions. Power saving modes include the ability to reduce

power consumption of individual functional blocks or to power

down unused blocks in half-duplex applications. A serial port

interface (SPI®) allows software programming of the various

functional blocks. An on-chip PLL clock multiplier and

synthesizer provide all the required internal clocks, as well as

two external clocks from a single crystal or clock source.

The Tx signal path consists of a bypassable 2×/4× low-pass

interpolation filter, a 12-bit TxDAC, and a line driver. The

transmit path signal bandwidth can be as high as 34 MHz at an

input data rate of 80 MSPS. The TxDAC provides differential

current outputs that can be steered directly to an external load

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

Broadband Modem Mixed-Signal Front End

for broadband modems

FUNCTIONAL BLOCK DIAGRAM

AD9866

2-4X

PWR DWN

MODE

TXEN/SYNC

TXCLK

12

ADIO[11:6]/

Tx[5:0]

ADIO[5:0]/

Rx[5:0]

12

RXE/SYNC

ADC

RXCLK

80MSPS

6

AGC[5:0]

4

REGISTER

SPI

CONTROL

or to an internal low distortion current amplifier. The current

amplifier (IAMP) can be configured as a current- or voltage-

mode line driver (with two external npn transistors) capable of

delivering in excess of 23 dBm peak signal power. Tx power can

be digitally controlled over a 19.5 dB range in 0.5 dB steps.

The receive path consists of a programmable amplifier

(RxPGA), a tunable low pass filter (LPF), and a 12-bit ADC.

The low noise RxPGA has a programmable gain range of

−12 dB to +48 dB in 1 dB steps. Its input referred noise is less

than 3.3 nV/rtHz for gain settings beyond 30 dB. The receive

path LPF cutoff frequency can be set over a 15 MHz to 35 MHz

range or simply bypassed. The 12-bit ADC achieves excellent

dynamic performance over a 5 MSPS to 80 MSPS span. Both

the RxPGA and the ADC offer scalable power consumption

allowing power/performance optimization.

The AD9866 provides a highly integrated solution for many

broadband modems. It is available in a space saving, 64-lead

lead frame chip scale package (LFCSP), and is specified over the

commercial (−40°C to +85°C) temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703

© 2004 Analog Devices, Inc. All rights reserved.

AD9866

IAMP

TxDAC

0 TO –12dB

0 TO –7.5dB

CLK

SYN.

M

2

CLK

MULTIPLIER

2-POLE

1-POLE

LPF

LPF

0 TO 6dB

– 6 TO 18dB

–6 TO 24dB

∆ = 1dB

∆ = 6dB

∆ = 6dB

Figure 1.

www.analog.com

IOUT_G+

IOUT_N+

IOUT_N–

IOUT_G–

CLKOUT_1

CLKOUT_2

OSCIN

XTAL

RX+

RX–

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Analog Devices AD9866

- Page 1 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use.

-

Page 2: Table Of Contents

AD9866 TABLE OF CONTENTS Specifications..................3 TxDAC and IAMP Architecture ..........28 Tx Path Specifications..............3 Tx Programmable Gain Control ..........30 Rx Path Specifications..............4 TxDAC Output Operation............30 Power Supply Specifications ............5 IAMP Current-Mode Operation..........30 Digital Specifications ..............6 IAMP Voltage-Mode Operation .......... -

Page 3: Specifications

AD9866 SPECIFICATIONS Tx PATH SPECIFICATIONS AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%; f = 50 MHz, f = 200 MHz, R = 2.0 kΩ, unless otherwise OSCIN noted. Table 1. Parameter... -

Page 4: Rx Path Specifications

AD9866 Parameter Temp Test Level Unit −3 dB Bandwidth Full 0.1202 Stop Band Rejection (0.289 f to 0.711 f Full OSCIN OSCIN PLL CLK MULTIPLIER OSCIN Frequency Range Full Internal VCO Frequency Range Full Duty Cycle Full OSCIN Impedance 25°C 100//3 ΜΩ//pF... -

Page 5: Power Supply Specifications

AD9866 Parameter Temp Test Level Unit Rx PATH COMPOSITE AC PERFORMANCE @ f = 50 MSPS RxPGA Gain = 48 dB (Full-Scale = 8.0 mV p-p) Signal-to-Noise (SNR) 25°C 43.7 Total Harmonic Distortion (THD) 25°C −71 RxPGA Gain = 24 dB (Full-Scale = 126 mV p-p) Signal-to-Noise (SNR) 25°C... -

Page 6: Digital Specifications

AD9866 Parameter Temp Test Level Unit Rx Mode 25°C AVDD CLKVDD 25°C 36.5 DVDD DRVDD POWER CONSUMPTION OF FUNCTIONAL BLOCKS AVDD CLKVDD RxPGA and LPF 25°C 25°C TxDAC 25°C IAMP (Programmable) 25°C Reference 25°C CLK PLL and Synthesizer 25°C MAXIMUM ALLOWABLE POWER DISSIPATION Full 1.66... -

Page 7: Serial Port Timing Specifications

AD9866 SERIAL PORT TIMING SPECIFICATIONS AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%, unless otherwise noted. Table 5. Parameter Temp Test Level Unit WRITE OPERATION (See Figure 46) SCLK Clock Rate (f... -

Page 8: Full-Duplex Data Interface (Tx And Rx Port) Timing Specifications

AD9866 FULL-DUPLEX DATA INTERFACE (Tx AND Rx PORT) TIMING SPECIFICATIONS AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%, unless otherwise noted. Table 7. Parameter Temp Test Level Unit Tx PATH INTERFACE (See Figure 53) Input Nibble Rate (2×... -

Page 9: Absolute Maximum Ratings

AD9866 ABSOLUTE MAXIMUM RATINGS Table 8. Parameter Rating Stresses above those listed under the Absolute Maximum ELECTRICAL Ratings may cause permanent damage to the device. This is a AVDD, CLKVDD Voltage 3.9 V maximum stress rating only; functional operation of the device at these or DVDD, DRVDD Voltage 3.9 V maximum... -

Page 10: Pin Configuration And Function Descriptions

AD9866 PIN CONFIGURATION AND FUNCTION DESCRIPTIONS AVSS ADIO11/Tx[5] AVSS ADIO10/Tx[4] PIN 1 IOUT_N– ADIO9/Tx[3] IDENTIFIER IOUT_G– ADIO8/Tx[2] AVSS ADIO7/Tx[1] AVDD ADIO6/Tx[0] AD9866 REFIO ADIO5/Rx[5] TOP VIEW REFADJ ADIO4/Rx[4] (Not to Scale) AVDD ADIO3/Rx[3] AVSS ADIO2/Rx[2] ADIO1/Rx[1] RX– ADIO0/Rx[0] AVSS RXEN/RXSYNC... - Page 11 AD9866 Pin No. Mnemonic Mode Description RXCLK ADIO Request Clock Input Rx and Tx Clock Output at 2 × f 17, 64 DRVDD Digital Output Driver Supply Input 18, 63 DRVSS Digital Output Driver Supply Return CLKOUT1 /N Clock Output (L = 1, 2, 4, or 8)

-

Page 12: Typical Performance Characteristics

AD9866 TYPICAL PERFORMANCE CHARACTERISTICS Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f = 50 MSPS, low-pass filter’s f = 22 MHz, AIN = −1 dBFS, OSCIN −3 dB RIN = 50 Ω, half- or full-duplex interface, default power bias settings. - Page 13 AD9866 Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f = 80 MSPS, low-pass filter’s f = 30 MHz, AIN = −1 dBFS, OSCIN −3 dB RIN = 50 Ω, half- or full-duplex interface, default power bias settings.

- Page 14 −3 dB –1 –0.1 –2 –0.2 DEVICE 1 –3 –0.3 DEVICE 2 DEVICE 3 AD9866: GAIN STEP ERROR @ +25°C –4 –0.4 AD9866: GAIN STEP ERROR @ +85°C DEVICE 4 AD9866: GAIN STEP ERROR @ –40°C –5 –0.5 –6 –6...

- Page 15 AD9866 Rx PATH TYPICAL PERFORMANCE CHARACTERISTICS AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f = 50 MSPS, low-pass filter disabled, RxPGA = 0 dB, AIN = −1 dBFS, OSCIN RIN = 50 Ω, half- or full-duplex interface, default power bias settings.

-

Page 16: Txdac Path Typical Performance Characteristics

AD9866 TxDAC PATH TYPICAL PERFORMANCE CHARACTERISTICS AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, fOSCIN = 50 MSPS and 80 MSPS, RSET = 1.96 kΩ, 2:1 transformer coupled output (see Figure 63) into 50 Ω load half-or full-duplex interface, default power bias settings. - Page 17 AD9866 –20 –20 PAR = 11.4 PAR = 11.4 RMS = –1.4 RMS = –1.4dBm –30 –30 –40 –40 –50 –50 –60 –60 –70 –70 –80 –80 –90 –90 –100 –100 FREQUENCY (MHz) FREQUENCY (MHz) Figure 33. Spectral Plot of 84-Carrier OFDM Test Vector Figure 36.

-

Page 18: Iamp Path Typical Performance Characteristics

AD9866 IAMP PATH TYPICAL PERFORMANCE CHARACTERISTICS AVDD = CLKVDD = DVDD = DRVDD = 3.3 V, f = 50 MSPS, R = 1.58 kΩ, 1:1 transformer coupled output (see Figure 64 and OSCIN Figure 65) into 50 Ω load, half- or full-duplex interface, default power bias settings. -

Page 19: Serial Port

AD9866 SERIAL PORT Table 10. SPI Register Mapping Power-Up Default Value MODE = 0 (Half-Duplex) MODE = 1 (Full-Duplex) Address Break- (Hex) down Description Width Comments CONFIG = 0 CONFIG = 1 CONFIG = 0 CONFIG = 1 SPI PORT CONFIGURATION AND SOFTWARE RESET... - Page 20 AD9866 Power-Up Default Value MODE = 0 (Half-Duplex) MODE = 1 (Full-Duplex) Address Break- (Hex) down Description Width Comments CONFIG = 0 CONFIG = 1 CONFIG = 0 CONFIG = 1 0x08 (7:0) Rx Filter Tuning Refer to Low-Pass Filter...

-

Page 21: Register Map Description

SERIAL PORT INTERFACE (SPI) The AD9866 serial port can support both MSB (most significant The serial port of the AD9866 has 3- or 4-wire SPI capability bit) first and LSB (least significant bit) first data formats. Figure 45 allowing read/write access to all registers that configure the illustrates how the serial port words are built for the MSB first and device’s internal parameters. - Page 22 SPI write operation applies. The SDO pin remains byte that includes the register address of the first address to be three-stated in a 3-wire read operation. accessed. The AD9866 automatically increments the address for each successive byte required for the multibyte communication SCLK cycle.

-

Page 23: Digital Interface

The half-duplex interface can be configured to act like a slave or TXEN a master to the digital ASIC. An example of a slave configura- tion is shown in Figure 51. In this example, the AD9866 accepts ADIO[9:0] all the clock and control signals from the digital ASIC. Because... -

Page 24: Full-Duplex Mode

OSCIN can also be directed to RXCLK by CLKOUT OSCIN setting Bit 2 of Register 0x05. This feature allows the AD9866 to be completely powered down (including the clock synthesizer) while serving as the master. Figure 51. Example of a Half-Duplex Digital Interface... -

Page 25: Rxpga Control

Optional RxPGA Gain Control via Tx[5:0] Invert RXSYNC RxPGA CONTROL LS nibble first The AD9866 contains a digital PGA in the Rx path that is used RXCLK negative edge to extend the dynamic range. The RxPGA can be programmed Twos complement over a −12 dB to +48 dB with 1 dB resolution using a 6-bit... - Page 26 AD9866 RXCLK SYNC [5:0] GAIN GAIN Figure 57. Updating RxPGA via Tx[5:0] in Full-Duplex Mode Updating the RxPGA (or TxPGA) via the PGA[5:0] port is an –6 option for both the half-duplex and full-duplex interfaces. The –12 PGA port consists of an input buffer that passes the 6-bit data...

-

Page 27: Txpga Control

The TxPGA register can be updated via the PGA[5:0] port or SPI port. The first method should be considered for fast updates The AD9866 also contains a digital PGA in the Tx path of the TxPGA register. Its operation is similar to the description distributed between the TxDAC and IAMP. -

Page 28: Transmit Path

Note that the additional two bits of resolution offered by the half-duplex interface with the half-duplex power-down mode AD9866 (vs. the AD9865) result in a 10 dB to 12 dB reduction enabled. This feature allows the user to set a programmable in the pass-band noise floor. -

Page 29: Change To Txdac And Iamp Architecture Section

AD9866 Applications demanding the highest spectral performance clearing Bit 0 of Register 0x0E. As a result, the IOUTP pins and/or lowest power consumption can use the TxDAC output must remain completely open, if the IAMP is to be used. The directly. -

Page 30: Tx Programmable Gain Control

AD9866 Table 19. SPI Registers for TxDAC and IAMP Address (Hex) Description 0.1µF 0x0E TxDAC output 0x10 Enable current mirror gain settings (6:4) Secondary path first stage gain of 0 IOUTN+ to 4 with ∆ = 1 IOUTG+ Not used... -

Page 31: Iamp Voltage-Mode Operation

AD9866 outputs left open for optimum linearity performance. The IAMP VOLTAGE-MODE OPERATION transformer should be specified to handle the dc standing The voltage-mode configuration is shown in Figure 65. This current, I , drawn by the IAMP. Also, because I... -

Page 32: Iamp Current Consumption Considerations

Tx output driver must go TxDACs AVDD into a high impedance state while in Rx mode. If the AD9866 is configured for the half-duplex mode (MODE = 0), the IAMP, TxDAC, and interpolation filter are automatically powered... -

Page 33: Receive Path

ADC. Note that the additional 2 bits of resolution offered by the cancellation loop is included. This cancellation loop is AD9866 (vs. the AD9865) result in a 3 dB to 5 dB lower noise automatically performed upon power-up and can also be floor depending on the RxPGA gain setting and LPF cutoff initiated via SPI. -

Page 34: Low-Pass Filter

AD9866 1.30 0.25 LOW-PASS FILTER 1.25 NORMALIZED GAIN RESPONSE The low-pass filter (LPF) provides a third order response with a 1.20 –0.25 cutoff frequency that is typically programmable over a 15 MHz 1.15 –0.50 to 35 MHz span. Figure 68 shows that the first real pole is im- –0.75... -

Page 35: Analog-To-Digital Converter (Adc)

Power Control and Dissipation section. ACTUAL 80MHz AND –40 ° C Lastly, the ADC can be completely powered down for half- ACTUAL 80MHz AND +25 ° C duplex operation, further reducing the AD9866’s peak power ACTUAL 80MHz AND +85 ° C consumption. TARGET-DECIMAL EQUIVALENT Figure 74. -

Page 36: Agc Timing Considerations

AD9866 AGC TIMING CONSIDERATIONS REFT When implementing a digital AGC timing loop, it is important 0.1µF to consider the Rx path latency and settling time of the Rx path 10µF ADCs 0.1µF in response to a change in gain setting. Figure 21 and Figure 24 REFB show the RxPGA’s settling response to a 60 dB and 5 dB change... -

Page 37: Clock Synthesizer

Table 22 Note: if the reference frequency appearing at OSCIN is chosen shows the SPI registers pertaining to the clock synthesizer. to be equal to the AD9866’s Tx and Rx path’s word rate, then M is simply equal to log (F). - Page 38 AD9866 at OSCIN (or RXCLK) can be determined upon power-up. Table 22. SPI Registers for CLK Synthesizer Also, this clock has near 50% duty cycle, because it is derived Address (Hex) Description from the VCO. As a result, CLKOUT1 should be selected before...

-

Page 39: Power Control And Dissipation

The power savings method depends allow two user-defined power settings that are pin selectable. on whether the AD9866 is configured for a full- or half-duplex The default settings are such that Register 0x01 has all blocks interface. -

Page 40: Power Reduction Options

Rx circuitry, set Bit 1 and/or Bit 0 to 0. POWER REDUCTION OPTIONS 2× INTERPOLATION The power consumption of the AD9866 can be significantly reduced from its default setting by optimizing the power consumption vs. performance of the various functional blocks 1×... - Page 41 AD9866 Because the CPGA processes signals in the continuous time domain, its performance vs. bias setting remains mostly independent of the sample rate. Table 25 shows how the typical current consumption seen at AVDD (Pins 35 and 40) varies as a function of Bits (7:5), while the remaining bits are maintained at their default settings of 0.

-

Page 42: Power Dissipation

A hardware ( RESET pin) or software (Bit 5 of Register 0x00) the application. reset can be used to place the AD9866 into a known state of POWER DISSIPATION operation as determined by the state of the MODE and CONFIG pins. -

Page 43: Analog And Digital Loopback Test Modes

Digital loopback can be used to test the full-duplex digital ANALOG AND DIGITAL LOOPBACK TEST MODES interface of the AD9866. In this test, data appearing on the The AD9866 features analog and digital loopback capabilities Tx[5:0] port is routed back to the Rx[5:0] port, thereby that can assist in system debug and final test. -

Page 44: Pcb Design Considerations

MxFE. partly achieved by incorporating an exposed die paddle on the The AD9866 has several pins that are used to decouple sensitive bottom surface of the package. However, to take full advantage internal nodes. These pins are REFIO, REFB, and REFT. The... - Page 45 AD9866 occur during undershoot or overshoot caused by ringing. If the form a differential pair and should be routed together as a pair. signal traces cannot be kept shorter than about 1.5 inches, By keeping the traces adjacent to each other, noise coupled onto the signals appears as common mode and is largely series termination resistors (33 Ω...

-

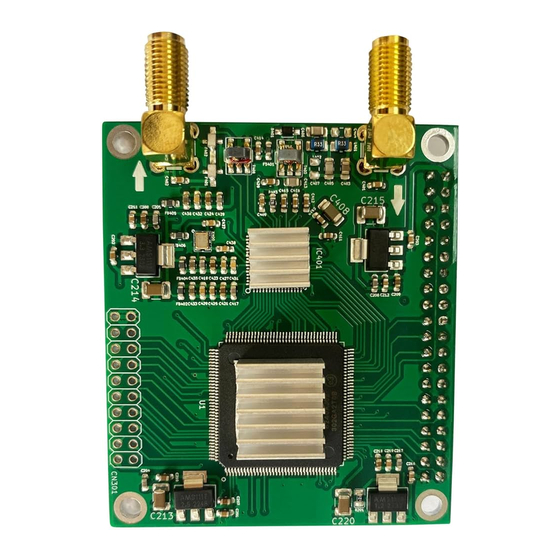

Page 46: Evaluation Board

AD9866 EVALUATION BOARD evaluation board allows complete optimization of power line An evaluation board is available for the AD9865 and AD9866. reference designs based around the AD9865 or AD9866. The digital interface to the evaluation board can be configured for a half- or full-duplex interface. Two 40-pin and one 26-pin Alternatively, the evaluation board allows independent evalua- male right angle headers (0.100 inches) provide easy interfacing... -

Page 47: Outline Dimensions

AD9866 OUTLINE DIMENSIONS 0.30 9.00 0.25 0.60 MAX BSC SQ 0.18 PIN 1 0.60 MAX INDICATOR PIN 1 INDICATOR * 7.25 8.75 EXPOSED PAD 7.10 SQ BSC SQ (BOTTOM VIEW) VIEW 6.95 0.45 0.40 0.35 0.25 MIN 7.50 0.80 MAX 1.00... - Page 48 AD9866 NOTES © 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. C04560–0–12/04(A) Rev. A | Page 48 of 48...

Need help?

Do you have a question about the AD9866 and is the answer not in the manual?

Questions and answers