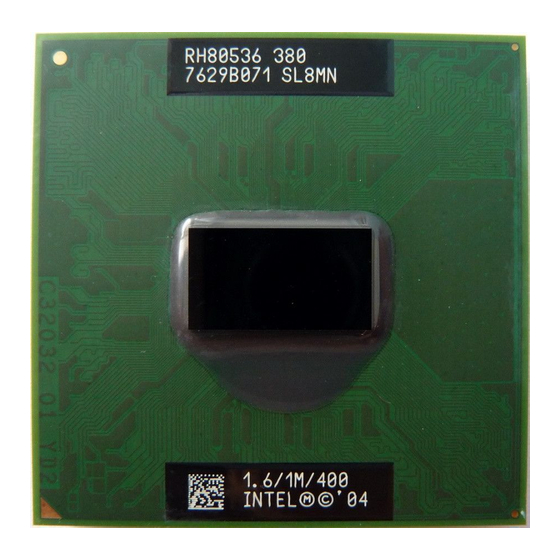

Summary of Contents for Intel RH80536GC0332M - Pentium M 1.8 GHz Processor

- Page 1 ® ® Intel Pentium M Processor on 90 nm Process with 2-MB L2 Cache Datasheet January 2006 Document Number: 302189-008...

- Page 2 Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See www.intel.com/products/processor_number for details. Intel, Pentium, Celeron, MMX, Intel SpeedStep and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

-

Page 3: Table Of Contents

2.1.6 Deep Sleep State....................13 2.1.7 Deeper Sleep State ....................14 ® Enhanced Intel SpeedStep Technology ................14 Front Side Bus Low Power Enhancements ................ 15 Processor Power Status Indicator (PSI#) Signal ..............15 Electrical Specifications ......................17 Power and Ground Pins...................... 17 3.1.1... - Page 4 Figures 2-1 Clock Control States........................11 3-1 Illustration of Active State VCC Static and Ripple Tolerances (HFM- VID#A)......31 3-2 Illustration of Deep Sleep State VCC Static and Ripple Tolerances (LFM- VID#A) ....32 3-3 Illustration of Active State VCC Static and Ripple Tolerances (HFM- VID#B)......33 3-4 Illustration of Deep Sleep State VCC Static and Ripple Tolerances (LFM- VID#B) ....

- Page 5 3-5 Voltage and Current Specifications - Low Voltage Processors ..........24 3-6 Voltage and Current Specifications - Ultra Low Voltage Processors.......... 26 3-7 Voltage and Current Specifications (Continued)................. 28 ® ® 3-8 Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#A ......31 ® ®...

-

Page 6: Revision History

1 January 2005 • Added Table 3-20 AGTL + Signal Group Signal DC Specifications ® ® • Table 3-18 - Voltage Tolerances for Intel Pentium processor ULV (Deep Sleep State) updated ® ® • Added Intel Pentium... -

Page 7: Introduction

Pentium processor architecture. Throughout this document, Intel Pentium M processor based on 90 nm technology featuring 2-MB L2 cache and 400 MHz FSB will be referred to as Pentium M processor, or simply the processor, including low voltage and ultra low voltage processors. - Page 8 Intel will validate this feature only on Intel 915 Express chipset family based platforms and recommends customers implement BIOS changes related to this feature, only on Intel 915 Express chipset family based platforms. Note: The term AGTL+ is used to refer to Assisted GTL+ signalling technology on some Intel processors. Datasheet...

-

Page 9: Terminology

305264.htm ® Mobile Intel 915PM/GM/GMS and 910GML Express Chipset Specification http://www.intel.com/ Update design/mobile/specupdt/ 307167.htm ® ® ® Intel 855PM Chipset Platform Design Guide: For use with Intel Pentium M and http://developer.intel.com/ ® ® Intel Celeron Processors design/mobile/desguide/ 252614.htm ® Intel 855PM Chipset Memory Controller Hub (MCH) Datasheet http://developer.intel.com/... - Page 10 Architecture Software Developer's Manual http://www.intel.com/ design/pentium4/ Volume 1: Basic Architecture manuals/index_new.htm Volume 2A: Instruction Set Reference Volume 2B: Instruction Set Reference Volume 3: System Programming Guide NOTE: Contact your Intel representative for the latest revision and document number of this document. § Datasheet...

-

Page 11: Low Power Features

LINT[1:0] (NMI, INTR), or FSB interrupt message. RESET# will cause the processor to immediately initialize itself. A system management interrupt (SMI) handler will return execution to either Normal state or the ® AutoHALT Power-Down state. See the IA-32 Intel Architecture Software Developer's Manual, Volume 3: System Programmer's Guide for more information. Datasheet... -

Page 12: Stop-Grant State

Low Power Features The system can generate a STPCLK# while the processor is in the AutoHALT Power-Down state. When the system deasserts the STPCLK# interrupt, the processor will return execution to the HALT state. While in AutoHALT Power-Down state, the processor will process bus snoops and interrupts. 2.1.3 Stop-Grant State When the STPCLK# pin is asserted, the Stop-Grant state of the processor is entered 20 bus clocks... -

Page 13: Sleep State

Sleep state is entered by asserting the DPSLP# pin while in the Sleep state. BCLK may be stopped during the Deep Sleep state for additional platform level power savings. BCLK stop/restart timings on 855PM and Intel 855GM chipset-based platforms are as follows: •... -

Page 14: Deeper Sleep State

— The processor waits for a fixed time period. If the die temperature is down to acceptable levels, an up transition to the previous frequency/voltage point occurs. — An interrupt is generated for the up and down Intel Thermal Monitor transitions enabling better system level thermal management. -

Page 15: Front Side Bus Low Power Enhancements

Low Power Features Front Side Bus Low Power Enhancements The Pentium M processor incorporates the following front side bus (processor system bus) low power enhancements: • Dynamic FSB Power Down • BPRI# control for address and control input buffers • Dynamic On Die Termination disabling •... - Page 16 Low Power Features Datasheet...

-

Page 17: Electrical Specifications

Electrical Specifications Electrical Specifications Power and Ground Pins For clean, on-chip power distribution, the Pentium M processor has a large number of V (power) and V (ground) inputs. All power pins must be connected to V power planes while all V pins must be connected to system ground planes. -

Page 18: Catastrophic Thermal Protection

Electrical Specifications Table 3-1. Voltage Identification Definition 1.708 1.196 1.692 1.180 1.676 1.164 1.660 1.148 1.644 1.132 1.628 1.116 1.612 1.100 1.596 1.084 1.580 1.068 1.564 1.052 1.548 1.036 1.532 1.020 1.516 1.004 1.500 0.988 1.484 0.972 1.468 0.956 1.452 0.940 1.436 0.924... -

Page 19: Signal Terminations And Unused Pins

These signals are used to select the FSB clock frequency. They should be connected between the processor and the chipset MCH and clock generator on Intel 915 Express chipset family based platforms. These signals must be left unconnected on platforms designed with the Intel 855 chipset family. -

Page 20: Cmos Signals

Electrical Specifications Table 3-2. FSB Pin Groups Signal Group Type Signals AGTL+ Common Clock Input Synchronous BPRI#, DEFER#, DPWR#, PREQ#, RESET#, RS[2:0]#, to BCLK[1:0] TRDY# AGTL+ Common Clock I/O Synchronous ADS#, BNR#, BPM[3:0]#, BR0#, DBSY#, DRDY#, HIT#, to BCLK[1:0] HITM#, LOCK#, PRDY# AGTL+ Source Synchronous I/O Synchronous to assoc. -

Page 21: Maximum Ratings

V NOTES: 1. This rating applies to any processor pin. 2. Contact Intel for storage requirements in excess of one year. Processor DC Specifications The processor DC specifications in this section are defined at the processor core (pads) unless noted otherwise. -

Page 22: Voltage And Current Specifications - Standard Voltage Processors

1.036 1.036 1.036 1.052 600 MHz 0.988 0.988 0.988 0.988 Pentium M Processor 755 1, 2 CCD755 Core V for Enhanced Intel SpeedStep Technology Operating Points: 2.0 GHz 1.340 1.324 1.308 1.276 1.8 GHz 1.292 1.276 1.276 1.244 1.6 GHz 1.244... - Page 23 VID#E Symbol Parameter Unit Notes Typical Typical Typical Typical Typical Pentium M Processor 735 1, 2 CCD735 Core V for Enhanced Intel SpeedStep Technology Operating Points: 1.7 GHz 1.340 1.324 1.308 1.276 1.4 GHz 1.244 1.244 1.228 1.212 1.2 GHz 1.180...

-

Page 24: Voltage And Current Specifications - Low Voltage Processors

Table 3-5. Voltage and Current Specifications - Low Voltage Processors (Sheet 1 of 2) Symbol Parameter Unit Note ® ® Intel Pentium 1, 2 CCD778 Processor, Low Voltage 778 Core VCC for Enhanced Intel ® SpeedStep Technology Operating Points: 1.6 GHz 1.116 1.5 GHz 1.116 1.4 GHz 1.100 1.3 GHz 1.084 1.2 GHz... - Page 25 Table 3-5. Voltage and Current Specifications - Low Voltage Processors (Sheet 2 of 2) Symbol Parameter Unit Note Pentium M Processor, 1, 2 CCD738 Low Voltage, 738 Core VCC for Enhanced Intel SpeedStep Technology Operating Points: 1.4 GHz 1.116 1.3 GHz 1.116 1.2 GHz 1.100 1.1 GHz 1.068...

-

Page 26: Voltage And Current Specifications - Ultra Low Voltage Processors

HTyp J Typ K Typ L Typ ® ® Intel Pentium 2, 3 CCD773 Processor, Ultra Low Voltage, 773 Core VCC for Enhanced Intel ® SpeedStep Technology Operating Points: 1.3 GHz 0.956 0.940 0.924 0.908 0.892 0.876 1.2 GHz 0.940 0.924... - Page 27 Note GTyp HTyp J Typ K Typ L Typ Pentium M Processor, 1, 3 CCD733 Ultra Low Voltage, 733 Core VCC for Enhanced Intel SpeedStep Technology Operating Points: 1.1 GHz 0.940 1.0 GHz 0.924 900 MHz 0.892 800 MHz 0.876 600 MHz 0.812...

-

Page 28: Voltage And Current Specifications (Continued)

Electrical Specifications Table 3-7. Voltage and Current Specifications (Continued) (Sheet 1 of 3) Symbol Parameter Unit Note Default V Voltage for 1.14 1.20 1.26 CC,BOOT Initial Power-Up AGTL+ Termination 0.997 1.05 1.102 voltage PLL Supply Voltage 1.71 1.89 PLL Supply Voltage for 2, 8 778, 758, Pentium M Processors... - Page 29 Electrical Specifications Table 3-7. Voltage and Current Specifications (Continued) (Sheet 2 of 3) Symbol Parameter Unit Note Auto-Halt & Stop- 4, 10 Grant for Pentium M SGNT Processors: 765/755/745/778/758/738/ 735/725/715 at LFM Vcc 765/755/745/735/725/715 15.1 at HFM Vcc 778/758/738 at HFM Vcc 773/753/733J at LFM Vcc 733/723 at LFM Vcc 773/753/733J HFM Vcc...

- Page 30 Electrical Specifications Table 3-7. Voltage and Current Specifications (Continued) (Sheet 3 of 3) Symbol Parameter Unit Note Deeper Sleep @ 4, 9, 10 DPRSLP1 0.748 V for Pentium M Processors: 765/755/745/778/758/738/ 735/725/715 753/733J/733/723 Deeper Sleep @ 4, 9, 10 DPRSLP1 0.726 V for Pentium M Processors: 765/755/745/778/758/738/...

-

Page 31: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-8. Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#A Highest Frequency Mode: VID=1.340V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.340 1.320 1.360 1.310 1.370 0.988 0.973 1.003 0.963... -

Page 32: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-9. Voltage Tolerances for the Intel Pentium M Processor (Deep Sleep State) VID#A Highest Frequency Mode: VID=1.340V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple 1.324 1.304 1.344 1.294 1.354 0.976 0.961 0.991... -

Page 33: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-10. Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#B Highest Frequency Mode: VID=1.324V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.324 1.304 1.344 1.294 1.354 0.988 0.973 1.003 0.963... -

Page 34: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-11. Voltage Tolerances for the Intel Pentium M Processor (Deep Sleep State) VID#B Highest Frequency Mode: VID=1.324V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple 1.308 1.288 1.328 1.278 1.338 0.976 0.961 0.991... -

Page 35: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-12. Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#C Highest Frequency Mode: VID=1.308V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.308 1.288 1.328 1.278 1.338 0.988 0.973 1.003 0.963... -

Page 36: Pentium ® M Processor (Deep Sleep State) Vid#C

Electrical Specifications ® ® Table 3-13. Voltage Tolerances for the Intel Pentium M Processor (Deep Sleep State) VID#C Highest Frequency Mode: VID=1.308V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple 1.292 1.273 1.312 1.263 1.322 0.976 0.961 0.991... -

Page 37: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-14. Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#D Highest Frequency Mode: VID=1.276V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.276 1.257 1.295 1.247 1.305 0.988 0.973 1.003 0.963... -

Page 38: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-15. Voltage Tolerances for the Intel Pentium M Processor (Deep Sleep State) VID#D Highest Frequency Mode: VID=1.276V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple M in 1.261 1.242 1.280 1.232 1.290 0.976... -

Page 39: Pentium ® M Processor (Active State) Vid#E

Electrical Specifications ® ® Table 3-16. Voltage Tolerances for the Intel Pentium M Processor (Active State) VID#E Highest Frequency Mode: VID=1.356V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.356 1.336 1.376 1.326 1.386 0.988 0.973 1.003 0.963... -

Page 40: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-17. Voltage Tolerances for the Intel Pentium M Processor (Deep Sleep State) VID#E Highest Frequency Mode: VID=1.356V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple 1.340 1.319 1.360 1.309 1.370 0.976 0.961 0.991... -

Page 41: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-18. Voltage Tolerances for the Intel Pentium M Processor LV (Active State) Highest Frequency Mode: VID=1.116V, Offset=0% Lowest Frequency Mode: VID=0.988V, Offset=0% MODE STATIC Ripple STATIC Ripple 1.116 1.099 1.133 1.089 1.143 0.988 0.973 1.003 0.963... -

Page 42: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-19. Voltage Tolerances for the Intel Pentium M Processor LV (Deep Sleep State) Highest Frequency Mode: VID=1.116V, Offset=-1.2% Lowest Frequency Mode: VID=0.988V, Offset=-1.2% MODE STATIC Ripple STATIC Ripple 1.103 1.086 1.119 1.076 1.129 0.976 0.961 0.991... -

Page 43: Voltage Tolerances For The Intel

Electrical Specifications ® ® Table 3-21. Voltage Tolerances for the Intel Pentium M Processor ULV (Deep Sleep State) H ighest Frequency M ode: VID=0.940V, Offset=-1.2% Lowest Frequency M ode: VID=0.812V, Offset=-1.2% M ODE STATIC Ripple STATIC Ripple M in M ax... - Page 44 Electrical Specifications Figure 3-12. Deep Sleep V and I Load Line Slope= -3.0 mV/A 10mV= RIPPLE Vcc nom {HFM | LFM} - 1.2% +/-1.5% from Nominal =VR Error Deep Sleep {HFM | LFM} Table 3-22. FSB Differential BCLK Specifications Symbol Parameter Unit Notes Input Low Voltage...

-

Page 45: Agtl+ Signal Group Dc Specifications

Electrical Specifications Table 3-23. AGTL+ Signal Group DC Specifications Symbol Parameter Unit Notes VCCP I/O Voltage 0.997 1.05 1.102 GTLREF Reference Voltage 2/3 VCCP - 2/3 VCCP 2/3 VCCP + Input High Voltage GTLREF+0.1 VCCP+0.1 Input Low Voltage -0.1 GTLREF-0.1 Output High Voltage VCCP Ω... -

Page 46: Open Drain Signal Group Dc Specifications

Electrical Specifications Table 3-25. Open Drain Signal Group DC Specifications Symbol Parameter Unit Notes Output High Voltage VCCP Output Low Voltage 0.20 Output Low Current Leakage Current ± 200 µA Cpad Pad Capacitance 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies. 2. -

Page 47: Package Mechanical Specifications And Pin Information

Package Mechanical Specifications and Pin Information Package Mechanical Specifications and Pin Information The Pentium M Processor is available in 478-pin, Micro-FCPGA and 479-ball, Micro-FCBGA packages. Different views of the Micro-FCPGA package are shown in Figure 4-1 through Figure 4-3. Package dimensions are shown in Table 4-1. -

Page 48: Micro-Fcpga Package - Top And Side Views

Package Mechanical Specifications and Pin Information Figure 4-2. Micro-FCPGA Package - Top and Side Views 0 .2 8 6 0 .2 8 6 0 .2 8 6 S U B S T R A T E K E E P O U T Z O N E S U B S T R A T E K E E P O U T Z O N E 7 (K 1) 7 (K 1) -

Page 49: Micro-Fcpga Package - Bottom View

Package Mechanical Specifications and Pin Information Figure 4-3. Micro-FCPGA Package - Bottom View 14 (K3) 14 (K3 ) 25X 1.27 2 5X 1.27 NOTE: All dimensions in millimeters. Values shown for reference only. Refer to Table 4-1 for details. Datasheet... -

Page 50: Micro-Fcpga Package Dimensions

Package Mechanical Specifications and Pin Information Table 4-1. Micro-FCPGA Package Dimensions Symbol Parameter Unit Overall height, top of die to package seating plane 1.88 2.02 – Overall height, top of die to PCB surface, including 4.74 5.16 socket (Refer to Note 1) Pin length 1.95 2.11... -

Page 51: Micro-Fcbga Package Top And Bottom Isometric Views

Package Mechanical Specifications and Pin Information Figure 4-4. Micro-FCBGA Package Top and Bottom Isometric Views PACKAGE KEEPOUT CAPACITOR AREA LABEL TOP VIEW BOTTOM VIEW Datasheet... -

Page 52: Micro-Fcbga Package Top And Side Views

Package Mechanical Specifications and Pin Information Figure 4-5. Micro-FCBGA Package Top and Side Views SUBSTRATE KEEPOUT ZONE 7 (K1) DO NOT CONTACT PACKAGE 8 places 0.20 INSIDE THIS LINE 5 (K) 4 places 35 (D) Ø 0.78 (b) 479 places 35 (E) PIN A1 CORNER NOTE: Die is centered on the Package. -

Page 53: Micro-Fcbga Package Dimensions

Package Mechanical Specifications and Pin Information Table 4-2. Micro-FCBGA Package Dimensions Symbol Parameter Unit Overall height, as delivered (Refer to Note 1) 2.60 2.85 Die height 0.82 Ball diameter 0.78 Package substrate length 34.9 35.1 Package substrate width 34.9 35.1 Die length 12.54 Die width... -

Page 54: Processor Pinout And Pin List

Package Mechanical Specifications and Pin Information Figure 4-6. Micro-FCBGA Package Bottom View 1.625 (S) 4 places 1.625 (S) 4 places 25X 1.27 25X 1.27 NOTE: All dimensions in millimeters. Values shown for reference only. Refer to Table 4-2 for details. Processor Pinout and Pin List Figure 4-7 on the next page shows the top view pinout of the Pentium M Processor. -

Page 55: The Coordinates Of The Processor Pins As Viewed From The Top Of The Package

Package Mechanical Specifications and Pin Information Figure 4-7. The Coordinates of the Processor Pins as Viewed from the Top of the Package ITP_CLK THER ITP_CLK IGNNE# IERR# SLP# DBR# VSS BPM[2]# PRDY# D[0]# D[6]# D[2]# D[4]# D[1]# PROC THER RSVD SMI# INIT# VSS DPSLP#... - Page 56 Package Mechanical Specifications and Pin Information This page is intentionally left blank. Datasheet...

-

Page 57: Pin Listing By Pin Name

Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Pin Name Direction Number Type Signal Buffer BPM[1]# Common Clock Output Pin Name Direction Number Type BPM[2]# Common Clock Output A[3]# Source Synch... - Page 58 Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type D[27]# Source Synch Input/Output DBSY# Common Clock Input/Output D[28]# Source Synch...

- Page 59 Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type REQ[4]# Source Synch Input/Output Power/Other RESET# Common Clock Input Power/Other...

- Page 60 Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type AC15 Power/Other VCCP Power/Other AC17 Power/Other VCCP Power/Other AC19...

- Page 61 Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other...

- Page 62 Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-3. Pin Listing by Pin Name Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type Power/Other AA12 Power/Other Power/Other AA14 Power/Other Power/Other AA16 Power/Other...

-

Page 63: Pin Listing By Pin Number

Package Mechanical Specifications and Pin Information Table 4-3. Pin Listing by Pin Name Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type AD22 Power/Other CMOS Input AD25 Power/Other Power/Other Power/Other ITP_CLK[1]... - Page 64 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type AA25 Power/Other AC11 Power/Other AA26 D[46]# Source Synch Input/Output AC12...

- Page 65 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type AD23 D[54]# Source Synch Input/Output Power/Other AD24 D[57]# Source Synch...

- Page 66 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type D[3]# Source Synch Input/Output Power/Other Power/Other Power/Other D[13]# Source Synch...

- Page 67 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other Power/Other D[14]#...

- Page 68 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type Power/Other Power/Other Power/Other D[27]# Source Synch Input/Output Power/Other D[30]#...

- Page 69 Package Mechanical Specifications and Pin Information Table 4-4. Pin Listing by Pin Number Table 4-4. Pin Listing by Pin Number Signal Buffer Signal Buffer Pin Name Direction Pin Name Direction Number Type Number Type D[34]# Source Synch Input/Output A[12]# Source Synch Input/Output Power/Other Power/Other...

-

Page 70: Alphabetical Signals Reference

In sub-phase 2, these pins transmit transaction type information. These signals ® ® must connect the appropriate pins of both agents on the Intel Pentium Processor FSB. A[31:3]# are source synchronous signals and are latched into the receiving buffers by ADSTB[1:0]#. Address signals are used as straps which are sampled before RESET# is deasserted. - Page 71 MCH and clock generator on Intel 915 chipset family based platforms. These signals must be left unconnected on platforms designed with the Intel 855 chipset family. On these platforms, FSB clock frequency should be configured on the motherboard.

- Page 72 Sleep State to the Deep Sleep state. In order to return to the Sleep state, DPSLP# must be deasserted. DPSLP# is driven by the ICH4-M component and also connects to the Intel 855 chipset family MCH-M component. ® DPWR#...

- Page 73 FERR#/PBE# indicates a floating point when the processor detects an unmasked floating-point error. FERR# is similar to the ERROR# signal on the Intel 387 coprocessor, and is included for compatibility with systems using MS- DOS*-type floating-point error reporting. When STPCLK# is asserted, an assertion of FERR#/PBE# indicates that the processor has a pending break event waiting for service.

- Page 74 Package Mechanical Specifications and Pin Information Table 4-5. Signal Description (Sheet 5 of 7) Name Type Description LINT[1:0] Input LINT[1:0] (Local APIC Interrupt) must connect the appropriate pins of all APIC Bus agents. When the APIC is disabled, the LINT0 signal becomes INTR, a maskable interrupt request signal, and LINT1 becomes NMI, a nonmaskable interrupt.

- Page 75 Package Mechanical Specifications and Pin Information Table 4-5. Signal Description (Sheet 6 of 7) Name Type Description RS[2:0]# Input RS[2:0]# (Response Status) are driven by the response agent (the agent responsible for completion of the current transaction), and must connect the appropriate pins of both FSB agents.

- Page 76 (Vcc). Unlike some previous generations of processors, these ® ® are CMOS signals that are driven by the Intel Pentium M processor. The voltage supply for these pins must be valid before the VR can supply Vcc to the processor.

-

Page 77: Thermal Specifications And Design Considerations

To allow for the optimal operation and long-term reliability of Intel processor-based systems, the system/processor thermal solution should be designed such that the processor must remain within... - Page 78 Thermal Specifications and Design Considerations ® Table 5-1. Power Specifications for the Intel Pentium M Processor (Sheet 1 of 3) Processor Core Frequency Thermal Design Symbol Unit Notes Number & Voltage Power 2.1 GHz & HFM Vcc At 100°C, Notes 1, 4, 5 2.0 GHz &...

-

Page 79: Power Specifications For The Intel ® Pentium M Processor

Thermal Specifications and Design Considerations ® Table 5-1. Power Specifications for the Intel Pentium M Processor (Sheet 2 of 3) Processor Symbol Parameter Unit Notes Number 765/755/745/ Sleep Power: At 50 °C, Note 2 735/725/715 LFM Vcc HFM Vcc 10.5... -

Page 80: Thermal Specifications

2. Not 100% tested. These power specifications are determined by characterization of the processor currents at higher temperatures and extrapolating the values for the temperature indicated. 3. As measured by the on-die Intel Thermal Monitor. The Intel Thermal Monitor’s automatic mode is used to indicate that the maximum T has been reached. -

Page 81: Thermal Diode Offset

2, 3, 5 NOTES: 1. Intel does not support or recommend operation of the thermal diode under reverse bias. Intel does not support or recommend operation of the thermal diode when the processor power supplies are not within their specified tolerance range. -

Page 82: Intel ® Thermal Monitor

Thermal Monitor uses two modes to activate the TCC: Automatic mode and On-Demand mode. If both modes are activated, Automatic mode takes precedence. Caution: The Intel Thermal Monitor Automatic Mode mst be enabled via BIOS for the processor to be operating within specifications. - Page 83 The TCC may also be activated via On-Demand mode. If bit 4 of the ACPI Intel Thermal Monitor Control Register is written to a 1, the TCC will be activated immediately, independent of the processor temperature.

- Page 84 Thermal Specifications and Design Considerations Datasheet...

Need help?

Do you have a question about the RH80536GC0332M - Pentium M 1.8 GHz Processor and is the answer not in the manual?

Questions and answers