Advertisement

Quick Links

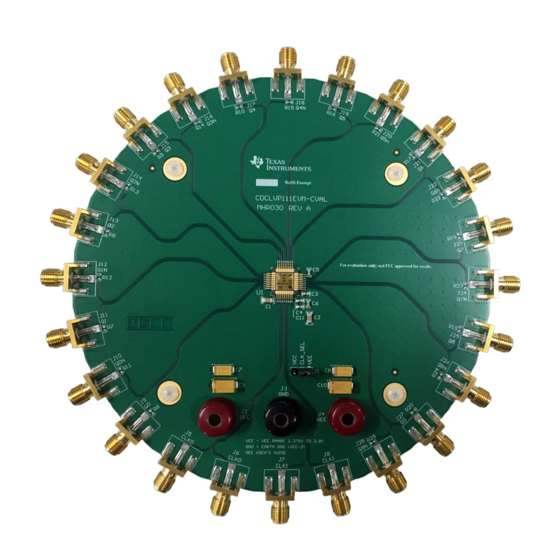

This user's guide provides an overview of the evaluation module (EVM) including hardware features to be

considered while using this module. This manual is applicable to the CDCLVP111-SP EVM which is

synonymous with CDCLVP111EVM-CVAL, the orderable part number. The EVM provides a platform for

evaluating the clock buffer under various voltage and bias configurations.

1

2

2.1

3

3.1

3.2

3.3

CDCLVP111-SP EVM Output Termination

4

CDCLVP111-SP EVM Schematic

5

CDCLVP111-SP EVM Bill of Materials (BOM)

1

CDCLVP111-SP EVM Block Diagram

2

Power Supply Connections

3

Input Biasing Schematic

4

Input Biasing Board View

5

LVDS Termination

6

On Board Optional Output Termination

7

CDCLVP111-SP Schematic

1

Power Supply Configuration

2

CDCLVP111-SP Jumper Configuration

3

Bill of Materials

Trademarks

All trademarks are the property of their respective owners.

SCAU055 - November 2016

Submit Documentation Feedback

CDCLVP111-SP Evaluation Module

..................................................................................

................................................................................................

........................................................................................

.........................................................................................

....................................................................................

.................................................................................................

....................................................................................................

...................................................................................................

...........................................................................................................

...................................................................................

................................................................................................

................................................................................................

...................................................................................

...............................................................................................................

Copyright © 2016, Texas Instruments Incorporated

(CDCLVP111EVM-CVAL)

Contents

.......................................................................

...........................................................................

.............................................................................

......................................................................

...........................................................................

List of Figures

List of Tables

CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL)

User's Guide

SCAU055 - November 2016

2

2

3

4

4

4

6

7

8

2

3

5

5

6

6

7

3

4

8

1

Advertisement

Subscribe to Our Youtube Channel

Summary of Contents for Texas Instruments CDCLVP111EVM-CVAL

-

Page 1: Table Of Contents

This user’s guide provides an overview of the evaluation module (EVM) including hardware features to be considered while using this module. This manual is applicable to the CDCLVP111-SP EVM which is synonymous with CDCLVP111EVM-CVAL, the orderable part number. The EVM provides a platform for evaluating the clock buffer under various voltage and bias configurations. -

Page 2: Cdclvp111-Sp Evm (Cdclvp111Evm-Cval)

50-Ω terminated test equipment. Connecting this way provides the proper termination for LVPECL drivers. The EVM also provides pads near SMA jacks for on-board 50-Ω termination for cases that may desire to utilize high-impedance probes. CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) SCAU055 – November 2016 Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated... -

Page 3: Power Supply Setup

VCC-GND CLK[0:1] amplitude CLK[0:1] offset 2.375 V 500 mV 0.625 V 3.3 V 500 mV –0.3 V 3.8 V 500 mV –0.8 V SCAU055 – November 2016 CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated... -

Page 4: Cdclvp111-Sp Evm Description

This configuration allows for direct use of LVPECL drivers. The termination resistors R1, R2, R4, and R5 are placed on the bottom side of the board in a fly-by configuration. CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) SCAU055 – November 2016 Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated... - Page 5 R2, R4 and R5. The pad placements are such that an 0402 100-Ω resistor can be placed between the top pads of R1 and R5 or R2 and R4 to differentially terminate either CLK0 or CLK1 pairs respectively (see Figure SCAU055 – November 2016 CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated...

- Page 6 6, install R7 and R12 for on-board termination. Leave them unconnected for direct termination to 50-Ω test equipment. Figure 6. On Board Optional Output Termination CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) SCAU055 – November 2016 Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated...

- Page 7 CLK_SEL 49.9 49.9 CDCLVP111HFG 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 Copyright © 2016, Texas Instruments Incorporated Figure 7. CDCLVP111-SP Schematic SCAU055 – November 2016 CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated...

- Page 8 RES, 49.9, 1%, 0.063 W, 0402 0402 RC0402FR-0749R9L Yageo America R12, R13, R14, R15, R16, R17, R18, R19, R20, R21, R22, R23, R24, R25 CDCLVP111-SP Evaluation Module (CDCLVP111EVM-CVAL) SCAU055 – November 2016 Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated...

- Page 9 STANDARD TERMS AND CONDITIONS FOR EVALUATION MODULES Delivery: TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, or documentation (collectively, an “EVM” or “EVMs”) to the User (“User”) in accordance with the terms and conditions set forth herein. Acceptance of the EVM is expressly subject to the following terms and conditions.

- Page 10 FCC Interference Statement for Class B EVM devices NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

- Page 11 【無線電波を送信する製品の開発キットをお使いになる際の注意事項】 開発キットの中には技術基準適合証明を受けて いないものがあります。 技術適合証明を受けていないもののご使用に際しては、電波法遵守のため、以下のいずれかの 措置を取っていただく必要がありますのでご注意ください。 1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用 いただく。 2. 実験局の免許を取得後ご使用いただく。 3. 技術基準適合証明を取得後ご使用いただく。 なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします。 上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。 日本テキサス・イ ンスツルメンツ株式会社 東京都新宿区西新宿6丁目24番1号 西新宿三井ビル 3.3.3 Notice for EVMs for Power Line Communication: Please see http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page 電力線搬送波通信についての開発キットをお使いになる際の注意事項については、次のところをご覧くださ い。http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page SPACER EVM Use Restrictions and Warnings: 4.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS.

- Page 12 Notwithstanding the foregoing, any judgment may be enforced in any United States or foreign court, and TI may seek injunctive relief in any United States or foreign court. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated...

- Page 13 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue.

Need help?

Do you have a question about the CDCLVP111EVM-CVAL and is the answer not in the manual?

Questions and answers