Table of Contents

Advertisement

Quick Links

™

Embedded Intel486

Processor

Hardware Reference Manual

Release Date: July 1997

Order Number: 273025-001

The embedded Intel486™ processors may contain design defects known as errata which may

cause the products to deviate from published specifications. Currently characterized errata are

available on request.

Advertisement

Chapters

Table of Contents

Summary of Contents for Intel Embedded Intel486

- Page 1 Embedded Intel486 Processor Hardware Reference Manual Release Date: July 1997 Order Number: 273025-001 The embedded Intel486™ processors may contain design defects known as errata which may cause the products to deviate from published specifications. Currently characterized errata are available on request.

- Page 2 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or oth- erwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of...

-

Page 3: Table Of Contents

CONTENTS CHAPTER 1 GUIDE TO THIS MANUAL MANUAL CONTENTS ....................1-1 NOTATIONAL CONVENTIONS..................1-3 SPECIAL TERMINOLOGY .................... 1-4 ELECTRONIC SUPPORT SYSTEMS ................1-5 1.4.1 FaxBack Service ......................1-5 1.4.2 World Wide Web ......................1-5 TECHNICAL SUPPORT ....................1-5 PRODUCT LITERATURE....................1-6 1.6.1 Related Documents ....................1-6 CHAPTER 2 INTRODUCTION... - Page 4 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL CHAPTER 3 INTERNAL ARCHITECTURE INSTRUCTION PIPELINING ..................3-6 BUS INTERFACE UNIT....................3-7 3.2.1 Data Transfers ......................3-8 3.2.2 Write Buffers ......................3-8 3.2.3 Locked Cycles......................3-9 3.2.4 I/O Transfers ......................3-9 CACHE UNIT ....................... 3-10 3.3.1 Cache Structure .......................3-10 3.3.2...

- Page 5 CONTENTS 4.3.3.2 Non-Burst Cacheable Cycles ................4-23 4.3.3.3 Burst Cacheable Cycles..................4-24 4.3.3.4 Effect of Changing KEN# during a Cache Line Fill..........4-25 4.3.4 Burst Mode Details....................4-26 4.3.4.1 Adding Wait States to Burst Cycles ..............4-26 4.3.4.2 Burst and Cache Line Fill Order................4-27 4.3.4.3 Interrupted Burst Cycles..................4-28 4.3.5 8- and 16-Bit Cycles....................4-29...

- Page 6 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL CHAPTER 5 MEMORY SUBSYSTEM DESIGN INTRODUCTION ......................5-1 PROCESSOR AND CACHE FEATURE OVERVIEW............ 5-1 5.2.1 The Burst Cycle ......................5-1 5.2.2 The KEN# Input ......................5-2 5.2.3 Bus Characteristics ....................5-4 5.2.4 Improving Write Cycle Latency ..................5-5 5.2.4.1...

- Page 7 CONTENTS CHAPTER 7 PERIPHERAL SUBSYSTEM PERIPHERAL/PROCESSOR BUS INTERFACE ............7-1 7.1.1 Mapping Techniques....................7-1 7.1.2 Dynamic Bus Sizing ....................7-3 7.1.3 Address Decoding for I/O Devices ................7-5 7.1.3.1 Address Bus Interface ...................7-6 7.1.3.2 8-Bit I/O Interface ....................7-7 7.1.3.3 16-Bit I/O Interface ....................7-10 7.1.3.4 32-Bit I/O Interface ....................7-14 BASIC PERIPHERAL SUBSYSTEM ................

- Page 8 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 7.6.2 82557 High Speed LAN Controller Interface............7-50 7.6.2.1 82557 Overview ....................7-50 7.6.2.2 Features and Enhancements ................7-51 7.6.2.3 PCI Bus Interface ....................7-52 7.6.2.4 82557 Bus Operations ..................7-52 7.6.2.5 Initializing the 82557 ...................7-52 7.6.2.6 Controlling the 82557 ..................7-53...

- Page 9 CONTENTS 8.4.5.5 Cycle Shortening ....................8-31 8.4.5.6 Status and Control Interface ................8-32 8.4.6 DMA Controller ......................8-33 8.4.6.1 DMA Status and Control Interface ..............8-34 CHAPTER 9 PERFORMANCE CONSIDERATIONS INTRODUCTION ......................9-1 9.1.1 Memory Performance Factors..................9-1 INSTRUCTION EXECUTION PERFORMANCE ............9-2 9.2.1 Intel486™ Processor Execution Times ..............9-2 9.2.2 Application Programs Used in Analysis ..............9-4 INTERNAL CACHE PERFORMANCE ISSUES ............

- Page 10 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL CHAPTER 10 PHYSICAL DESIGN AND SYSTEM DEBUGGING 10.1 GENERAL SYSTEM GUIDELINES ................10-1 10.2 POWER DISSIPATION AND DISTRIBUTION............. 10-1 10.2.1 Power and Ground Planes ..................10-2 10.3 HIGH-FREQUENCY DESIGN CONSIDERATIONS ............ 10-9 10.3.1 Transmission Line Effects ..................10-9 10.3.1.1...

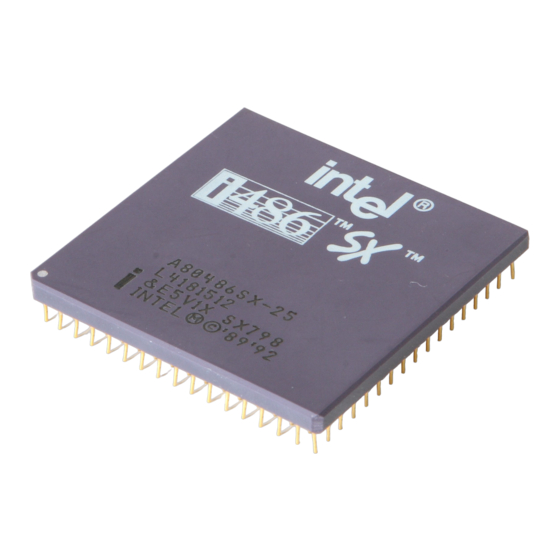

- Page 11 CONTENTS FIGURES Figure Page A Typical Intel486™ Processor System ...............2-8 Single-Processor System .....................2-9 Loosely Coupled Multi-processor System ..............2-10 External Cache ......................2-11 Embedded Personal Computer and Embedded Controller Example ......2-12 IntelDX2™ and IntelDX4™ Processors Block Diagram ..........3-2 Intel486™ SX Processor Block Diagram..............3-3 Ultra-Low Power Intel486™...

- Page 12 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL FIGURES Figure Page 4-32 Stop Grant Bus Cycle ....................4-42 4-33 Restarted Read Cycle ....................4-43 4-34 Restarted Write Cycle....................4-44 4-35 Bus State Diagram .....................4-45 4-36 DOS-Compatible Numerics Error Circuit ..............4-49 4-37 Basic Burst Read Cycle....................4-51 4-38 Snoop Cycle Invalidating a Modified Line..............4-55...

- Page 13 7-25 Bus Throttle Timers ....................7-48 7-26 596RESET, CA, and PORT# Equations..............7-49 7-27 Intel 82557 Block Diagram ..................7-52 Intel486™ Processor System ..................8-4 Block Diagram of EISA Bus Controller (EBC) ..............8-6 Block Diagram of Integrated System Peripheral (ISP) ..........8-8 EBB Byte Transfer......................8-15 Example System Block Diagram ................8-20...

- Page 14 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL FIGURES Figure Page 10-12 Lattice Diagram Example ..................10-17 10-13 Series Termination ....................10-19 10-14 Parallel Termination ....................10-19 10-15 Thevenin’s Equivalent Circuit ...................10-20 10-16 AC Termination ......................10-21 10-17 Active Termination....................10-22 10-18 Impedance Mismatch Example ................10-23 10-19 Use of Series Termination to Avoid Impedance Mismatch........10-24...

- Page 15 CONTENTS TABLES Table Page Product Options......................2-4 Intel486™ Processor Family Functional Units..............3-1 Cache Configuration Options ..................3-13 Byte Enables and Associated Data and Operand Bytes ..........4-1 Generating A31–A0 from BE3#–BE0# and A31–A2 ............4-2 Next Byte Enable Values for BS x # Cycles ..............4-4 Data Pins Read with Different Bus Sizes ..............4-5 Generating A1, BHE# and BLE# for Addressing 16-Bit Devices........4-7 Generating A0, A1 and BHE# from the Intel486™...

- Page 17 GUIDE TO THIS MANUAL Chapter Contents Manual Contents ..............1-1 Text Conventions ..............1-3 Special Terminology ............. 1-4 Electronic Support Systems ..........1-5 Technical Support ..............1-5 Product Literature ..............1-6...

-

Page 19: Guide To This Manual

CHAPTER 1 GUIDE TO THIS MANUAL This manual describes the embedded Intel486™ processors. It is intended for use by hardware designers familiar with the principles of embedded microprocessors and with the Intel486 pro- cessor architecture. MANUAL CONTENTS This manual contains 10 chapters and an index. This section summarizes the contents of the re- maining chapters. - Page 20 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Chapter 7: This chapter describes the connection of peripheral devices to the “Peripheral Intel486 processor bus. Design techniques are discussed for interfacing Subsystem” a variety of devices, including a LAN controller and an interrupt controller.

- Page 21 GUIDE TO THIS MANUAL TEXT CONVENTIONS The following notations are used throughout this manual. The pound symbol (#) appended to a signal name indicates that the signal is active low. Variables Variables are shown in italics. Variables must be replaced with correct values.

-

Page 22: Special Terminology

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Register Bits When the text refers to more that one bit, the range of bits is represented by the highest and lowest numbered bits, separated by a long dash (example: A15–A8). The first bit shown (15 in the example) is the most- significant bit and the second bit shown (8) is the least-significant bit. -

Page 23: Electronic Support Systems

GUIDE TO THIS MANUAL ELECTRONIC SUPPORT SYSTEMS Intel’s FaxBack* service provides up-to-date technical information. Intel also offers a variety of information on the World Wide Web. These systems are available 24 hours a day, 7 days a week, providing technical information whenever you need it. -

Page 24: Product Literature

Germany 44(0)1793-421777 France 81(0)120-47-88-32 Japan (fax only) 1.6.1 Related Documents The following Intel documents contain additional information on designing systems that incor- porate the Intel486 processors. Intel Document Name Intel Order Number Datasheets Embedded Intel486™ SX Processor datasheet 272769-001 Embedded IntelDX2™ Processor datasheet 272770-001 Embedded Ultra-Low Power Intel486™... - Page 25 GUIDE TO THIS MANUAL You can obtain the following resources from the Word Wide Web at the sites listed. Document Name Web Site Standard 1149.1—1990, IEEE Standard Test Access Port and Boundary- Contact the IEEE at Scan Architecture and its supplement, Standard 1149.1a—1993 http://www.ieee.org.

-

Page 27: Introduction

Introduction Chapter Contents Processor Features..............2-2 Intel486™ Processor Product Family ........2-4 System Components.............. 2-7 System Architecture.............. 2-7 Systems Applications............2-11... - Page 29 Management Interrupt (SMI#), a corresponding Resume (RSM) instruction and a new memory space for system management code. Although transparent to any application or operating system, Intel's SMM ensures seamless power control of the processor core, system logic, main memory, and one or more peripheral devices.

-

Page 30: Processor Features

• Instruction Pipelining — The fetching, decoding, address translation, and execution of instructions are overlapped within the Intel486 processor. • On-Chip Floating-Point Unit — The IntelDX2 and Intel DX4 processors support the 32-, 64-, and 80-bit formats specified in IEEE standard 754. The unit is binary compatible with ®... - Page 31 Standard Test Access Port and Boundary Scan Architecture. SL Technology provides the following features: • Intel System Management Mode — A unique Intel architecture operating mode provides a dedicated special purpose interrupt and address space that can be used to implement intelligent power management and other enhanced functions in a manner that is completely transparent to the operating system and applications software.

-

Page 32: Intel486™ Processor Product Family

An individual product has either a 5 V supply voltage or a 3.3 V supply voltage, but not both. Likewise, an individual product may have 1x, 2x, or 3x clock. Please con- tact Intel for the latest product availability and specifications. Table 2-1. Product Options... -

Page 33: Operating Modes And Compatibility

INTRODUCTION 2.2.1 Operating Modes and Compatibility The Intel486 processor can run in modes that give it object-code compatibility with software writ- ten for the 8086, 80286, and Intel386 processor families. The operating mode is set in software as one of the following: •... -

Page 34: On-Chip Cache

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 2.2.3 On-chip Cache A software-transparent 8-Kbyte cache (16-Kbyte on the IntelDX4 processor) stores recently ac- cessed information on the processor. Both instructions and data can be cached. If the processor needs to read data that is available in the cache, the cache responds, thereby avoiding a time-con- suming external memory cycle. -

Page 35: Upgrade Power Down Mode

Mode,” lowering its power consumption. The UP# pin of the Intel486 processor is driven active (low) by the UP# pin of the Intel OverDrive processor. (In the embedded Intel486 processor fam- ily, the UP# pin has been renamed Reserved, with no changes in functionality.) SYSTEM COMPONENTS Intel offers several chips that are highly compatible with the Intel486 processor. -

Page 36: Single Processor System

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Intel486™ Processor Processor Bus External Cache Processor Optional System Bus Memory Controller Coprocessor External Bus Figure 2-1. A Typical Intel486™ Processor System 2.4.1 Single Processor System In single-processor systems, the processor handles all peripheral resources and intelligent devic- es, and executes all software. -

Page 37: Loosely Coupled Multi-Processor System

INTRODUCTION of other components should be no more than 50% of the available processor-bus bandwidth. Traf- fic above 50% degrades performance of the processor. Intel486™ Level-2 Processor Cache Processor Bus Peripheral Memory Controller Controller Figure 2-2. Single-Processor System Two basic design approaches are used to elaborate the single-processor system into a more com- plex system. -

Page 38: External Cache

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Intel486™ Intel486™ Memory Memory Processor Processor Processor Bus Processor Bus Controller Controller System Bus Figure 2-3. Loosely Coupled Multi-processor System 2.4.3 External Cache External cache allows a system to achieve maximum performance. This cache is essential in tightly coupled multi-processor embedded systems. -

Page 39: Systems Applications

INTRODUCTION i486™ Intel486™ Processor Processor Processor Bus External Cache SRAM Controller System Bus DRAM DRAM Controller Array A5131-01 Figure 2-4. External Cache SYSTEMS APPLICATIONS Most Intel486 processor systems can be grouped as one of these types: • Embedded Personal Computer •... -

Page 40: Embedded Personal Computers

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 2.5.1 Embedded Personal Computers In single-processor embedded systems, the processor interacts directly with I/O devices and DRAM memory. Other bus masters such as a LAN coprocessor typically reside on the system bus; conventional personal computer architecture puts most peripherals on separate plug-in boards. - Page 41 INTRODUCTION pansion capability than other applications because they are tailored specifically to a single envi- ronment. If code must be stored in EPROM, ROM, or Flash for non-volatility, but performance is also a critical issue, then the code should be copied into RAM provided specifically for this purpose. Frequently used routines and variables, such as interrupt handlers and interrupt stacks, can be locked in the processor’s internal cache so they are always available quickly.

-

Page 43: Internal Architecture

Internal Architecture Chapter Contents Instruction Pipelining ............3-6 Bus Interface Unit ..............3-7 Cache Unit................3-10 Instruction Prefetch unit............3-13 Instruction Decode Unit ............3-14 Control Unit ................3-14 Integer (Datapath) Unit ............3-14 Floating-Point Unit .............3-15 Segmentation Unit...............3-15 3.10 Paging Unit .................3-16... - Page 45 IntelDX2 and IntelDX4 processors. Note that the cache unit is 8-Kbytes for the IntelDX2 processor and 16 Kbytes for the IntelDX4 processor. Figure 3-2 is a block diagram of the embedded Intel486 SX processor and Figure 3-3 is a block...

- Page 46 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 64-Bit Interunit Transfer Bus Core 32-Bit Data Bus Clock Clock 32-Bit Data Bus Multiplier Linear Address Bus Interface Base/ A31-A2 Barrel Segmentation Index Cache Unit BE3#- BE0# Paging Shifter Unit Address Unit Drivers Descriptor...

- Page 47 INTERNAL ARCHITECTURE 64-Bit Interunit Transfer Bus 32-Bit Data Bus 32-Bit Data Bus Linear Address Bus Interface Base/ A31-A2 Barrel Segmentation Index Cache Unit BE3#- BE0# Paging Shifter Unit Address Unit Drivers Descriptor Register Physical Registers File Write Buffers 8 Kbyte Address 4 x 32 Cache...

- Page 48 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 64-Bit Interunit Transfer Bus Core 32-Bit Data Bus Clock Clock 32-Bit Data Bus Control Linear Address Base/ Bus Interface Barrel Segmentation A31-A2 Index Cache Unit Paging BE3#- BE0# Shifter Unit Address Unit Drivers Descriptor...

- Page 49 MMU is completely compatible with the Intel386 processor MMU. Software written for previous members of the Intel architecture family runs on the Intel486 processor without modification. Memory is organized into one or more variable length segments, each up to four Gbytes bytes).

-

Page 50: Instruction Pipelining

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL The Intel486 processor has four modes of operation: Real Address Mode (Real Mode), Protected Mode, Virtual Mode (within Protected Mode), and System Management Mode (SMM). In Real Mode the Intel486 processor operates as a very fast 8086. Real Mode is required primarily to set up the Intel486 processor for Protected Mode operation. -

Page 51: Bus Interface Unit

INTERNAL ARCHITECTURE Instruction Fetch Stage-1 Decode Stage-2 Decode Execution Register Write-back A5140-01 Figure 3-4. Internal Pipelining The internal pipelining on the Intel486 processor offers an important performance advantage over many single-clock RISC processors: in the Intel486 processor, data can be loaded from the cache with one instruction and used by the next instruction in the next clock. -

Page 52: Data Transfers

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL The bus interface unit contains the following architectural features: • Address Transceivers and Drivers — The A31–A2 address signals are driven on the processor bus, together with their corresponding byte-enable signals, BE3#–BE0#. The high-order 28 address signals are bidirectional, allowing external logic to drive cache invalidation addresses into the processor. -

Page 53: Locked Cycles

INTERNAL ARCHITECTURE writes as fast as one per clock. Once a write request is buffered, the internal unit that generated the request is free to continue processing. If no higher-priority request is pending and the bus is free, the transfer is propagated as an immediate write cycle to the processor bus. When all four write buffers are full, any subsequent write transfer stalls inside the processor until a write buffer becomes available. -

Page 54: Cache Unit

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL • Writes — Single I/O writes are never buffered. When processing an OUT instruction, internal execution stops until all buffered writes and the I/O write are completed on the processor bus. This allows time for external logic to drive a cache invalidate cycle or mask interrupts before the processor executes the next instruction. - Page 55 INTERNAL ARCHITECTURE Valid/LRU Data Block Block Block Way 0 Way 1 Way 2 Way 3 Way 0 Way 1 Way 2 Way 3 Set 0 Set 1 Set 2 Set N Set 126 Set 127 † Valid Tag - 21 bits Data - 16 bytes X 1 X X Selects...

-

Page 56: Cache Updating

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 3.3.2 Cache Updating When a cache miss occurs on a read, the 16-byte block containing the requested information is written into the cache. Data in the neighborhood of the required data is also read into the cache, but the exact position of data within the cache line depends on its location in memory with respect to addresses divisible by 16. -

Page 57: Instruction Prefetch Unit

INTERNAL ARCHITECTURE Table 3-2. Cache Configuration Options Write-through Cache Enabled Operating Mode Enabled Cache line fills, cache write-throughs, and cache invalidations are disabled. This configuration allows the internal cache to be used as high-speed static RAM. Cache line fills are disabled, and cache write-throughs and cache invalidations are enabled. -

Page 58: Instruction Decode Unit

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL encountered in the program being executed, the prefetch unit gets copies of previously executed instructions from the cache. The prefetch unit has the lowest priority for processor bus access. Assuming zero wait-state mem- ory access, prefetch activity never delays execution. However, if there is no pending data transfer, prefetching may use bus cycles that would otherwise be idle. -

Page 59: Floating-Point Unit

INTERNAL ARCHITECTURE the cache unit. The contents of the general purpose registers are sent to the segmentation unit on a separate 32-bit bus for generation of effective addresses. FLOATING-POINT UNIT The floating-point unit executes the same instruction set as the 387 math coprocessor. The unit contains a push-down register stack and dedicated hardware for interpreting the 32-, 64-, and 80- bit formats as specified in IEEE Standard 754. -

Page 60: 3.10 Paging Unit

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Page Base Address Page Offset Physical Address Translated by the paging unit Page Directory Page Table Page Offset Offset Offset Linear Address Translated by the segmentation unit 32 31 Segment Segment Selector Offset Logical Address A5142-01 Figure 3-6. - Page 61 Paging is visible to the operating system, which uses it to satisfy application program memory require- ments. For more information on paging and segmentation, see the Embedded Intel486™ Devel- oper’s Manual.

-

Page 63: Bus Operation

Bus Operation Chapter Contents Data Transfer Mechanism ............. 4-1 Bus Arbitration Logic ............4-12 Bus Functional Description..........4-15 Enhanced Bus Mode Operation (Write-Back Mode) for the Write-Back Enhanced IntelDX4™ Processor ..4-50... -

Page 65: Data Transfer Mechanism

CHAPTER 4 BUS OPERATION All Intel486™ processors operate in Standard Bus (write-through) mode. However, when the in- ternal cache of the Write-Back Enhanced IntelDX4™ processor is configured in write-back mode, the processor bus operates in the Enhanced Bus mode, which is described in Section 4.4. -

Page 66: Memory And I/O Space Organization

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 00000000H to FFFFFFFFH (4 gigabytes). I/O addresses range from 00000000H to 0000FFFFH (64 Kbytes) for programmed I/O. (See Figure 4-1.) Table 4-2. Generating A31–A0 from BE3#–BE0# and A31–A2 Intel486™ Processor Address Signals through BE3#... -

Page 67: Dynamic Data Bus Sizing

BUS OPERATION The Intel486 processor includes bus control pins, BS16# and BS8#, which allow direct connec- tion to 16- and 8-bit memories and I/O devices. Cycles of 32-, 16- and 8-bits may occur in any sequence, since the BS8# and BS16# signals are sampled during each bus cycle. NOTE The Ultra-Low Power Intel486 GX processor has a 16-bit external data bus. - Page 68 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL each bus cycle. BS8# and BS16# must be deasserted when addressing 32-bit devices. An 8-bit bus width is selected if both BS16# and BS8# are asserted. BS16# and BS8# force the Intel486 processor to run additional bus cycles to complete requests larger than 16 or 8 bits.

-

Page 69: Interfacing With 8-, 16-, And 32-Bit Memories

BUS OPERATION Table 4-4. Data Pins Read with Different Bus Sizes BE3# BE2# BE1# BE0# w/o BS8#/BS16# w BS8# w BS16# D7–D0 D7–D0 D7–D0 D15–D0 D7–D0 D15–D0 D23–D0 D7–D0 D15–D0 D31–D0 D7–D0 D15–D0 D15–D8 D15–D8 D15–D8 D23–D8 D15–D8 D15–D8 D31–D8 D15–D8 D15–D8 D23–D16... - Page 70 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Figure 4-4 shows the Intel486 processor address bus interface to 32-, 16- and 8-bit memories. To address 16-bit memories the byte enables must be decoded to produce A1, BHE# and BLE# (A0). For 8-bit wide memories the byte enables must be decoded to produce A0 and A1. The same byte...

- Page 71 BUS OPERATION Table 4-5. Generating A1, BHE# and BLE# for Addressing 16-Bit Devices Intel486™ Processor 8-, 16-Bit Bus Signals Comments BE3# BE2# BE1# BE0# BHE# BLE# (A0) † † † † x–no asserted bytes † † † † x–not contiguous bytes †...

- Page 72 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 240950–42 240950–43 240950–44 Figure 4-5. Logic to Generate A1, BHE# and BLE# for 16-Bit Buses Combinations of BE3#–BE0# that never occur are those in which two or three asserted byte en- ables are separated by one or more deasserted byte enables. These combinations are “don't care”...

-

Page 73: Dynamic Bus Sizing During Cache Line Fills

BUS OPERATION D7–D0 D15–D8 32-Bit Intel486™ D23–D16 Processor Memory D31–D24 BS8# BS16# (A31–A2, BE3#–BE0#) Byte Swap 16-Bit Memory Logic Address Byte Swap 8-Bit Memory Decode Logic Figure 4-6. Data Bus Interface to 16- and 8-Bit Memories 4.1.4 Dynamic Bus Sizing During Cache Line Fills BS8# and BS16# can be driven during cache line fills. -

Page 74: Operand Alignment

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 4-6. Generating A0, A1 and BHE# from the Intel486™ Processor Byte Enables First Cache Fill Cycle Any Other Cycle BE3# BE2# BE1# BE0# BHE# BHE# † † † † KEY: † a non-occurring pattern of Byte Enables; either none are asserted or the pattern has byte enables asserted for non-contiguous bytes 4.1.5... - Page 75 BUS OPERATION Table 4-7. Transfer Bus Cycles for Bytes, Words and Dwords Byte-Length of Logical Operand Physical Byte Address in Memory (Low Order Bits) Transfer Cycles over 32-Bit † † † Transfer Cycles over 16-Bit † † † † † †...

-

Page 76: Bus Arbitration Logic

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL BUS ARBITRATION LOGIC Bus arbitration logic is needed with multiple bus masters. Hardware implementations range from single-master designs to those with multiple masters and DMA devices. Figure 4-7 shows a simple system in which only one master controls the bus and accesses the memory and I/O devices. - Page 77 BUS OPERATION Figure 4-8 shows a single processor and a DMA device. Here, arbitration is required to determine whether the processor, which acts as a master most of the time, or a DMA controller has control of the bus. When the DMA wants control of the bus, it asserts the HOLD request to the processor. The processor then responds with a HLDA output when it is ready to relinquish bus control to the DMA device.

- Page 78 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Figure 4-9 shows more than one primary bus master and two secondary masters, and the arbitra- tion logic is more complex. The arbitration logic resolves bus contention by ensuring that all de- vice requests are serviced one at a time using either a fixed or a rotating scheme. The arbitration logic then passes information to the Intel486 processor, which ultimately releases the bus.

-

Page 79: Bus Functional Description

BUS OPERATION The arbitration logic may be implemented in several different ways. The first technique is to “round-robin” or to “time slice” each master. Each master is given a block of time on the bus to match their priority and need for the bus. Another method of arbitration is to assign the bus to a master when the bus is needed. -

Page 80: Non-Cacheable Non-Burst Single Cycle

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.3.1 Non-Cacheable Non-Burst Single Cycle 4.3.1.1 No Wait States The fastest non-burst bus cycle that the Intel486 processor supports is two clocks. These cycles are called 2-2 cycles because reads and writes take two cycles each. The first “2” refers to reads and the second “2”... -

Page 81: Inserting Wait States

BUS OPERATION fer is complete after a single cycle. The Intel486 processor asserts BLAST# in the last cycle, “T2”, of a bus transfer. The timing of the parity check output (PCHK#) is shown in Figure 4-10. The Intel486 processor drives the PCHK# output one clock after RDY# or BRDY# terminates a read cycle. PCHK# in- dicates the parity status for the data sampled at the end of the previous clock. -

Page 82: Burst Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL The external system can cause a multiple cycle transfer when it can only supply 8- or 16-bits per cycle. Only multiple cycle transfers caused by internal requests are considered in this section. Cache- able cycles and 8- and 16-bit transfers are covered in Section 4.3.3, “Cacheable Cycles,”... -

Page 83: Terminating Multiple And Burst Cycle Transfers

BUS OPERATION 4.3.2.2 Terminating Multiple and Burst Cycle Transfers The Intel486 processor deasserts BLAST# for all but the last cycle in a multiple cycle transfer. BLAST# is deasserted in the first cycle to inform the external system that the transfer could take additional cycles. -

Page 84: Non-Cacheable Burst Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL ADS# A31–A2 M/IO# D/C# W/R# BE3#–BE0# RDY# BRDY# KEN# BLAST# † † DATA 1st Data 2nd Data † To Processor 242202-033 Figure 4-12. Non-Cacheable, Non-Burst, Multiple-Cycle Transfers Each cycle in the transfer begins when ADS# is asserted and the cycle is complete when the ex- ternal system asserts RDY#. -

Page 85: Cacheable Cycles

BUS OPERATION ADS# A31–A2 M/IO# D/C# W/R# BE3#–BE0# RDY# BRDY# KEN# BLAST# † † DATA † To Processor 242202-034 Figure 4-13. Non-Cacheable Burst Cycle 4.3.3 Cacheable Cycles Any memory read can become a cache fill operation. The external memory system can allow a read request to fill a cache line by asserting KEN# one clock before RDY# or BRDY# during the first cycle of the transfer on the external bus. -

Page 86: Byte Enables During A Cache Line Fill

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL paging is disabled, or to cache the page directory entry, control register 3 (CR3) must have PCD=0. The cache disable (CD) bit in control register 0 (CR0) must be clear. External hardware can determine when the Intel486 processor has transformed a read or prefetch into a cache fill by examining the KEN#, M/IO#, D/C#, W/R#, LOCK#, and PCD pins. -

Page 87: Non-Burst Cacheable Cycles

BUS OPERATION 4.3.3.2 Non-Burst Cacheable Cycles Figure 4-14 shows a non-burst cacheable cycle. The cycle becomes a cache fill when the Intel486 processor samples KEN# asserted at the end of the first clock. The Intel486 processor deasserts BLAST# in the second clock in response to KEN#. BLAST# is deasserted because a cache fill requires three additional cycles to complete. -

Page 88: Burst Cacheable Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.3.3.3 Burst Cacheable Cycles Figure 4-15 illustrates a burst mode cache fill. As in Figure 4-14, the transfer becomes a cache line fill when the external system asserts KEN# at the end of the first clock in the cycle. -

Page 89: Effect Of Changing Ken# During A Cache Line Fill

BUS OPERATION 4.3.3.4 Effect of Changing KEN# during a Cache Line Fill KEN# can change multiple times as long as it arrives at its final value in the clock before RDY# or BRDY# is asserted. This is illustrated in Figure 4-16. -

Page 90: Burst Mode Details

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.3.4 Burst Mode Details 4.3.4.1 Adding Wait States to Burst Cycles Burst cycles need not return data on every clock. The Intel486 processor strobes data into the chip only when either RDY# or BRDY# is asserted. Deasserting BRDY# and RDY# adds a wait state to the transfer. -

Page 91: Burst And Cache Line Fill Order

BUS OPERATION 4.3.4.2 Burst and Cache Line Fill Order The burst order used by the Intel486 processor is shown in Table 4-8. This burst order is followed by any burst cycle (cache or not), cache line fill (burst or not) or code prefetch. The Intel486 processor presents each request for data in an order determined by the first address in the transfer. -

Page 92: Interrupted Burst Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL progressing to the next 32-bit word. For example, a BS16# burst to address 4 has the following order: 4-6-0-2-C-E-8-A. 4.3.4.3 Interrupted Burst Cycles Some memory systems may not be able to respond with burst cycles in the order defined in Table 4-8. -

Page 93: 8- And 16-Bit Cycles

BUS OPERATION The order in which the Intel486 processor requests operands during an interrupted burst transfer is shown by Table 4-7 on page 4-11. Mixing RDY# and BRDY# does not change the order in which operand addresses are requested by the Intel486 processor. An example of the order in which the Intel486 processor requests operands during a cycle in which the external system mixes RDY# and BRDY# is shown in Figure... - Page 94 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL The timing of BS16# and BS8# is the same as that of KEN#. BS16# and BS8# must be asserted before the first RDY# or BRDY# is asserted. Asserting BS16# and BS8# can force the Intel486 processor to run additional cycles to complete what would have been only a single 32-bit cycle.

-

Page 95: Locked Cycles

BUS OPERATION ADS# ADDR SPEC BE3#–BE0# RDY# BRDY# BS8# BLAST# DATA ‡ ‡ From Processor 242202–143 Figure 4-22. Burst Write as a Result of BS8# or BS16# 4.3.6 Locked Cycles Locked cycles are generated in software for any instruction that performs a read-modify-write op- eration. -

Page 96: Pseudo-Locked Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL When LOCK# is asserted, the Intel486 processor recognizes address hold and backoff but does not recognize bus hold. It is left to the external system to properly arbitrate a central bus when the Intel486 processor generates LOCK#. -

Page 97: Floating-Point Read And Write Cycles

BUS OPERATION The first cycle of a 64-bit floating-point write is the only case in which both PLOCK# and BLAST# are asserted. Normally PLOCK# and BLAST# are the inverse of each other. During all of the cycles in which PLOCK# is asserted, HOLD is not acknowledged until the cycle completes. - Page 98 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Invalidations use two pins, address hold request (AHOLD) and valid external address (EADS#). There are two steps in an invalidation cycle. First, the external system asserts the AHOLD input forcing the Intel486 processor to immediately relinquish its address bus. Next, the external sys- tem asserts EADS#, indicating that a valid address is on the Intel486 processor address bus.

-

Page 99: Rate Of Invalidate Cycles

BUS OPERATION ADS# † ADDR AHOLD EADS# RDY# † DATA BREQ † To Processor 242202-092 Figure 4-26. Typical Internal Cache Invalidation Cycle 4.3.8.1 Rate of Invalidate Cycles The Intel486 processor can accept one invalidate per clock except in the last clock of a line fill. One invalidate per clock is possible as long as EADS# is deasserted in ONE or BOTH of the fol- lowing cases: In the clock in which RDY# or BRDY# is asserted for the last time. - Page 100 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL A potential problem exists if the external device is writing to an address in external memory, and at the same time the Intel486 processor is reading data from the same address in the second-level cache.

- Page 101 BUS OPERATION If the system asserts EADS# before the first data in the line fill is returned to the Intel486 proces- sor, the system must return data consistent with the new data in the external memory upon re- sumption of the line fill after the invalidation cycle. This is illustrated by the asserted EADS# signal labeled “1”...

-

Page 102: Bus Hold

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.3.9 Bus Hold The Intel486 processor provides a bus hold, hold acknowledge protocol using the bus hold re- quest (HOLD) and bus hold acknowledge (HLDA) pins. Asserting the HOLD input indicates that another bus master has requested control of the Intel486 processor bus. The Intel486 processor responds by floating its bus and asserting HLDA when the current bus cycle, or sequence of locked cycles, is complete. - Page 103 BUS OPERATION For cacheable and non-burst or burst cycles, HOLD is acknowledged during backoff only if HOLD and BOFF# are asserted during an active bus cycle (after ADS# asserted) and before the first RDY# or BRDY# has been asserted (see Figure 4-30).

-

Page 104: 4.3.10 Interrupt Acknowledge

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.3.10 Interrupt Acknowledge The Intel486 processor generates interrupt acknowledge cycles in response to maskable interrupt requests that are generated on the interrupt request input (INTR) pin. Interrupt acknowledge cy- cles have a unique cycle type generated on the cycle type pins. -

Page 105: 4.3.11 Special Bus Cycles

BUS OPERATION 4.3.11 Special Bus Cycles The Intel486 processor provides special bus cycles to indicate that certain instructions have been executed, or certain conditions have occurred internally. The special bus cycles are identified by the status of the pins shown in Table 4-9. - Page 106 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL The latency between a STPCLK# request and the Stop Grant bus cycle is dependent on the cur- rent instruction, the amount of data in the processor write buffers, and the system memory per- formance.

-

Page 107: 4.3.12 Bus Cycle Restart

BUS OPERATION 4.3.12 Bus Cycle Restart In a multi-master system, another bus master may require the use of the bus to enable the Intel486 processor to complete its current bus request. In this situation, the Intel486 processor must restart its bus cycle after the other bus master has completed its bus transaction. A bus cycle may be restarted if the external system asserts the backoff (BOFF#) input. - Page 108 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL ADS# ADDR SPEC RDY# BRDY# BOFF# ‡ ‡ DATA ‡ From Processor 242202-147 Figure 4-34. Restarted Write Cycle The device asserting BOFF# is free to run cycles while the Intel486 processor bus is in its high impedance state.

-

Page 109: 4.3.13 Bus States

BUS OPERATION AHOLD is asserted, and in the second clock BOFF# is asserted. This guarantees that ADS# is not floating low. This is necessary only in systems where BOFF# may be asserted in the same clock as ADS#. 4.3.13 Bus States A bus state diagram is shown in Figure 4-35. -

Page 110: Floating-Point Error Handling For The Inteldx2™ And Inteldx4™ Processors

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 4-10. Bus State Description State Means Bus is idle. Address and status signals may be driven to undefined values, or the bus may be floated to a high impedance state. First clock cycle of a bus cycle. Valid address and status are driven and ADS# is asserted. -

Page 111: Inteldx2™ And Inteldx4™ Processors Floating-Point Error Handling In At-Compatible Systems

AT-compatible numerics error reporting scheme. These features DO NOT replace the external circuit. Logic is still required that decodes the OUT F0 instruction and latches the FERR# signal. The use of these Intel Processor features is described below. •... - Page 112 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL To process a floating-point error in the DOS environment, the following sequence must take place: The error is detected by the IntelDX2 and IntelDX4 processor that activates the FERR# pin. FERR# is latched so that it can be cleared by the OUT F0 instruction.

- Page 113 BUS OPERATION RESET I/O Port 0F0H Address decoder Processor Bus FERR# Intel486™ Processor IGNNE# 8259A Programmable Interrupt Controller IRQ13 INTR Figure 4-36. DOS-Compatible Numerics Error Circuit 4-49...

-

Page 114: Enhanced Bus Mode Operation (Write-Back Mode)

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL ENHANCED BUS MODE OPERATION (WRITE-BACK MODE) FOR THE WRITE-BACK ENHANCED IntelDX4™ PROCESSOR All Intel486™ processors operate in Standard Bus (write-through) mode. However, when the in- ternal cache of the Write-Back Enhanced IntelDX4 processor is configured in write-back mode, the processor bus operates in the Enhanced Bus mode. -

Page 115: Non-Cacheable Burst Operation

BUS OPERATION ADS# A31–A4 M/IO# D/C# W/R# A3–A2 BLAST# CACHE# BRDY# KEN# WB/WT# 242202-149 Figure 4-37. Basic Burst Read Cycle 4.4.2.1 Non-Cacheable Burst Operation When CACHE# is asserted on a read cycle, the processor follows with BLAST# high when KEN# is asserted. However, the converse is not true. The Write-Back Enhanced IntelDX4 pro- cessor may elect to read burst data that are identified as non-cacheable by either CACHE# or KEN#. -

Page 116: Cache Consistency Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL shown in Table 4-8 on page 4-27. The burst order for reads is the same as the burst order for writes. (See Section 4.3.4.2, “Burst and Cache Line Fill Order.”) An attempted line fill caused by a read miss is indicated by the assertion of CACHE# and W/R#. - Page 117 BUS OPERATION snoop addresses and asserting EADS#. INV should be driven low during read operations to min- imize invalidations, and INV should be driven high to invalidate a cache line during write oper- ations. The Write-Back Enhanced IntelDX4 processor asserts HITM# if the cycle hits a modified line in the cache.

-

Page 118: Snoop Collision With A Current Cache Line Operation

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.4.3.1 Snoop Collision with a Current Cache Line Operation The system can also perform snooping concurrent with a cache access and may collide with a cur- rent cache bus cycle. Table 4-12 lists some scenarios and the results of a snoop operation collid- ing with an on-going cache fill or replacement cycle. - Page 119 BUS OPERATION When a line is written back, KEN#, WB/WT#, BS8#, and BS16# are ignored, and PWT and PCD are always low during write-back cycles. AHOLD EADS# HITM# A31–A4 A3–A2 ADS# BLAST# CACHE# BRDY# W/R# To Processor Write-back from Processor 242202-150 Figure 4-38.

- Page 120 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Snoop under AHOLD Overlaying a Line-Fill Cycle The assertion of AHOLD during a line fill is allowed on the Write-Back Enhanced IntelDX4 pro- cessor. In this case, when a snoop cycle is overlaid by an on-going line-fill cycle, the chipset must generate the burst addresses internally for the line fill to complete, because the address bus has the valid snoop address.

- Page 121 BUS OPERATION AHOLD EADS# HITM# ‡ A31–A4 Fill † Fill A3–A2 ADS# BLAST# CACHE# BRDY# W/R# † To Processor ‡ Write-back from Processor 242202-151 Figure 4-39. Snoop Cycle Overlaying a Line-Fill Cycle 4-57...

- Page 122 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL AHOLD Snoop Overlaying a Non-Burst Cycle When AHOLD overlays a non-burst cycle, snooping is based on the completion of the current non-burst transfer (ADS#-RDY# transfer). Figure 4-40 shows a snoop cycle under AHOLD over- laying a non-burst line-fill cycle.

-

Page 123: Snoop During Replacement Write-Back

BUS OPERATION AHOLD Snoop to the Same Line that is being Filled A system snoop does not cause a write-back cycle to occur if the snoop hits a line while the line is being filled. The processor does not allow a line to be modified until the fill is completed (and a snoop only produces a write-back cycle for a modified line). - Page 124 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL AHOLD EADS# HITM# † A31–A4 Replace Replace A3–A2 ADS# BLAST# CACHE# BRDY# W/R# † To Processor 242202-153 Figure 4-41. Snoop to the Line that is Being Replaced If the replacement write-back cycle is burst and there is a snoop hit to the same line as the line that is being replaced, the on-going replacement cycle runs to completion.

-

Page 125: Snoop Under Boff

BUS OPERATION tured replacement write-back cycle and is completed under HITM#. However, after AHOLD is deasserted, the replacement write-back cycle is not completed. If there is a snoop hit to a line that is different from the one being replaced, the non-burst replace- ment write-back cycle is fractured, and the snoop write-back cycle is reordered ahead of the re- placement write-back cycle. - Page 126 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 20 21 22 23 BOFF# EADS# HITM# † Linefill A31–A4 Write Back Cycle Line Fill Cycle Cont. A3–A2 ADS# BLAST# CACHE# RDY# BRDY# W/R# † To Processor 242202-154 Figure 4-42. Snoop under BOFF# during a Cache Line-Fill Cycle An ADS# is always issued when a cycle resumes after being fractured by BOFF#.

- Page 127 BUS OPERATION Figure 4-42 also shows the system asserting RDY# to indicate a non-burst line-fill cycle. Burst cache line-fill cycles behave similarly to non-burst cache line-fill cycles when snooping using BOFF#. If the system snoop hits the same line as the line being filled (burst or non-burst), the Write-Back Enhanced IntelDX4 processor does not assert HITM# and does not issue a snoop write-back cycle, because the line was not modified, and the line fill resumes upon the de-asser- tion of BOFF#.

-

Page 128: Snoop Under Hold

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4.4.3.5 Snoop under HOLD HOLD can only fracture a non-cacheable, non-burst code prefetch cycle. For all other cycles, the Write-Back Enhanced IntelDX4 processor does not assert HLDA until the entire current cycle is completed. If the system snoop hits a modified line under HLDA during a non-cacheable, non- burstable code prefetch, the snoop write-back cycle is reordered ahead of the fractured cycle. - Page 129 BUS OPERATION HOLD HLDA EADS# HITM# † Linefill A31–A4 A3–A2 ADS# BLAST# CACHE# BRDY# W/R# † To Processor 242202-156 Figure 4-44. Snoop under HOLD during Line Fill If HOLD is asserted during a non-cacheable, non-burst code prefetch cycle, as shown in Figure 4-45, the Write-Back Enhanced IntelDX4 processor issues HLDA in clock seven (which is the clock period in which the next RDY# is asserted).

-

Page 130: Snoop Under Hold During Replacement Write-Back

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL HOLD HLDA EADS# HITM# Prefetch † Prefetch Cycle A31–A4 Write Back Cycle Cont. A3–A2 ADS# BLAST# CACHE# RDY# BRDY# W/R# † To Processor 242202-157 Figure 4-45. Snoop using HOLD during a Non-Cacheable, Non-Burstable Code Prefetch 4.4.3.6... -

Page 131: Locked Cycles

BUS OPERATION 4.4.4 Locked Cycles In both Standard and Enhanced Bus modes, the Write-Back Enhanced IntelDX4 processor archi- tecture supports atomic memory access. A programmer can modify the contents of a memory variable and be assured that the variable is not accessed by another bus master between the read of the variable and the update of that variable. -

Page 132: Snoop/Lock Collision

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL ADS# ADDR CACHE# W/R# ‡ ‡ † † DATA RDY# BRDY# LOCK# † To Processor ‡ From Processor 242202-158 Figure 4-46. Locked Cycles (Back-to-Back) 4.4.4.1 Snoop/Lock Collision If there is a snoop cycle overlaying a locked cycle, the snoop write-back cycle fractures the locked cycle. -

Page 133: Flush Operation

BUS OPERATION Read Write ADS# WB1 WB2 WB3 WB4 Write RDY# BRDY# AHOLD † ‡ ADDR ‡ EADS# HITM# LOCK# CACHE# W/R# † To Processor ‡ From Processor 242202-159 Figure 4-47. Snoop Cycle Overlaying a Locked Cycle 4.4.5 Flush Operation The Write-Back Enhanced IntelDX4 processor executes a flush operation when the FLUSH# pin is asserted, and no outstanding bus cycles, such as a line fill or write back, are being processed. -

Page 134: Pseudo Locked Cycles

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL If the processor is in Standard Bus mode, the processor does not issue special acknowledge cycles in response to the FLUSH# input, although the internal cache is invalidated. The invalidation of the cache in this case, takes only two bus clocks. -

Page 135: Snoop Under Hold During Pseudo-Locked Cycles

BUS OPERATION AHOLD EADS# HITM# † Write Back Cycle A31–A4 A3–A2 ADS# BLAST# CACHE# PLOCK# W/R# BRDY# † To Processor 242202-161 Figure 4-49. Snoop under AHOLD Overlaying Pseudo-Locked Cycle 4.4.6.2 Snoop under Hold during Pseudo-Locked Cycles As shown in Figure 4-50, HOLD does not fracture the 64-bit burst transfer. -

Page 136: Snoop Under Boff# Overlaying A Pseudo-Locked Cycle

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL HOLD HLDA EADS# HITM# 64-Bit † A31–A4 Write Back Cycle Read Cycle A3–A2 ADS# BLAST# CACHE# PLOCK# BRDY# W/R# † To Processor 242202-162 Figure 4-50. Snoop under HOLD Overlaying Pseudo-Locked Cycle 4.4.6.3 Snoop under BOFF# Overlaying a Pseudo-Locked Cycle BOFF# is capable of fracturing any bus operation. - Page 137 BUS OPERATION AHOLD EADS# HITM# † Write Back Cycle A31–A4 A3–A2 ADS# BLAST# CACHE# PLOCK# W/R# BRDY# † To Processor 242202-163 Figure 4-51. Snoop under BOFF# Overlaying a Pseudo-Locked Cycle 4-73...

-

Page 139: Memory Subsystem Design

Memory Subsystem Design Chapter Contents Introduction ................5-1 Processor and Cache Feature Overview........ 5-1... -

Page 141: Introduction

CHAPTER 5 MEMORY SUBSYSTEM DESIGN INTRODUCTION The Intel486™ processor contains several improvements over its predecessor, the highly suc- cessful Intel386™ processor. One of the most important of these is the processor's data access rate. The Intel486 processor can access instructions and data from its on-chip cache in the same clock cycle. -

Page 142: The Ken# Input

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL cle takes place. Note that this cycle occurs regardless of the state of the KEN# input. The KEN# input’s function is discussed in the next section. With this definition we see that several cases are included as “burstable.” Some examples of... - Page 143 MEMORY SUBSYSTEM DESIGN cache unit. So, regardless of the state of KEN#, code fetches are always burstable. In addition, several types of data read cycles are generated as 8-byte cycles. These cycles, mentioned previ- ously, are descriptor loads and floating-point operand loads. These cycles can be burst at any time.

-

Page 144: Bus Characteristics

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL BLAST# Sampled Sampled here here KEN# DATA BRDY# A5243-01 Figure 5-2. Burst Cycle: KEN# Normally Active Some memory devices may be slow enough that 16-byte cycles are undesirable. In this case more than three wait states exist. The KEN# signal can be deactivated prior to returning RDY# or BRDY# if three or more wait states are present. -

Page 145: Improving Write Cycle Latency

MEMORY SUBSYSTEM DESIGN Intel386™ Bus Cycle Mix Intel486™ Bus Cycle Mix Write 12.79% Prefetch 21.65% 35.90% 12.37 Read 74.84% 42.45% Figure 5-3. Intel386™ Processor Bus Cycle Mix/Intel486™ Processor Bus Cycle Mix It seems obvious that many of these write cycles would be consecutive. In fact, 70% of all write cycles are consecutive. -

Page 146: Second-Level Cache

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Write posting can improve average write latency to under 3 clocks for many applications. This improvement is important in Intel486 processor-based systems because approximately 70% of all bus cycles are writes. Without using a latency improvement technique such as write posting, av- erage write latency is above 15 clocks. - Page 147 MEMORY SUBSYSTEM DESIGN By designing the cache subsystem as an option both users requirements can be met. A single-sys- tem design can be manufactured for both customers. The operating system user can add the cache module. Users can choose the system configuration which meets their price-performance needs.

-

Page 149: Cache Subsystem

Cache Subsystem Chapter Contents Introduction ................6-1 Cache Memory ..............6-1 Cache Trade-offs..............6-2 Updating Main Memory............6-11 Non-Cacheable Memory Locations ........6-15 Cache and DMA Operations ..........6-16 Cache for Single Versus Multiple Processor Systems ..6-16 An Intel486™ Processor System Example ......6-18... -

Page 151: Introduction

CHAPTER 6 CACHE SUBSYSTEM INTRODUCTION Cache is an important means of improving overall system performance. The Intel486™ proces- sors have an on-chip, unified code and data cache. The on-chip cache is used for both instruction and data accesses and operates on physical addresses. The Intel486 processor and most variants have an 8-Kbyte cache (the IntelDX4 processor has a 16-Kbyte cache) which is organized in a 4- way set associative manner. -

Page 152: Why Add An External Cache

Why Add an External Cache? System designers must take into account several factors when deciding whether to incorporate a Level II cache subsystem in an embedded Intel486 processor design. These considerations in- clude the performance expectations, operating system used, DRAM cycle speed, possible future upgrades to the initial application, and system costs. -

Page 153: Cache Size And Performance

CACHE SUBSYSTEM • Associativity (discussed in Section 6.2.2, “Why Add an External Cache?”): Increased associativity increases the cache hit rate but also increases its complexity and reduces its speed. • Line Size: The amount of data the cache must fetch during each cache line replacement (every miss) affects performance. - Page 154 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 6-1. Level-1 Cache Hit Rates (Sheet 2 of 2) Cache Configurations Hit Rate Size Associativity Line Size 32 Kbyte 2-way 4 bytes 32 Kbyte direct 8 bytes 64 Kbyte direct 4 bytes 64 Kbyte...

-

Page 155: Associativity And Performance Issues

CACHE SUBSYSTEM dated later. This allows the CPU to begin the next cycle without being delayed by the main mem- ory write access time. Both these memory updating techniques are discussed later in this chapter. 6.3.2 Associativity and Performance Issues Data and instructions are written into the cache by a function that maps the main memory address into a cache location. - Page 156 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL controller would have to compare the address with each of the 64 addresses in the cache for a match condition. This organization, shown in Figure 6-1, is called fully associative. Direct Mapped: In a direct mapped cache, the simplest of the three policies, only one address comparison is required to determine if the requested word is in the cache.

- Page 157 CACHE SUBSYSTEM 32-Bit Processor Address 24 23 16 15 Cache/DRAM Index Select 64 Kbyte Cache 16 Bits 16 Mbyte DRAM 24 Bits Main Memory - 16 MB Index Cache-64 Kbyte Data Index Data FFFC FFFC FFF8 FFF8 0008 0008 0004 0004 0000 0000...

- Page 158 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL cache may provide acceptable performance at a lower cost when compared to a fully associative cache memory. Set Associative: The set-associative cache is a compromise between the fully associative and di- rect-mapped cache. The set-associative cache has more than one set and it is equivalent to several direct mapped cache operating in parallel.

- Page 159 CACHE SUBSYSTEM Given an equal amount of cache memory as in the direct mapped example, the set associative cache has half as many locations, and the extra address bit becomes part of the tag field. Because the set-associative cache has several places for a block with the same cache index, the hit rate is increased.

-

Page 160: Block/Line Size

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 4-Way Set Associative 8-Kbyte Cache Set 0 Word 0 Word 1 Word 2 Word 3 Line Size = 4 DWORDS Line Size = 16 Bytes 2 Kbytes Set 1 2 Kbytes Set 2 2 Kbytes... -

Page 161: Replacement Policy

CACHE SUBSYSTEM This situation applies when using page mode accesses in dynamic RAM; and the initial word is read after the normal access time, whereas subsequent words can be accessed quickly by chang- ing only the column addresses. Taking advantage of this situation while selecting the optimum line size can greatly increase cache performance. -

Page 162: Write-Through And Buffered Write-Through Systems

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Main Memory Cache Processor reads data into cache from main memory. The data is processed and modified and stored in the cache (not in the main memory). Later, another read overwrites the cache data and the modified data is overwritten and lost before the main memory is updated. -

Page 163: Write-Back System

CACHE SUBSYSTEM Users sometimes adopt a buffered write-through approach in which the write accesses to the main memory can be buffered with a N-deep pipeline. A number of words are stored in pipelined reg- isters, and will subsequently be written to the main memory. The processor can begin a new op- eration before the write operation to main memory is completed. - Page 164 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL In snooping, cache controllers monitor the bus lines and invalidate any shared locations that are written by another processor. The common cache location is invalidated and cache consistency is maintained. This method is shown in Figure 6-7.

-

Page 165: Non-Cacheable Memory Locations

CACHE SUBSYSTEM receives stale data. This can be implemented with chip select logic or with the high order address bits. Figure 6-9 shows non-cacheable memory. Other Master Decoder Non-cacheable Cacheable Cache Figure 6-9. Non-Cacheable Share Memory In cache flushing, all cache locations with set dirty bits are written to main memory (for write- back systems), then cache contents are cleared. -

Page 166: Cache And Dma Operations

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL CACHE AND DMA OPERATIONS Some of the issues related to cache consistency in systems employing DMA have already been covered in the preceding section. Because a DMA controller or other bus master can update main memory, there is a possibility of stale data in the cache. - Page 167 CACHE SUBSYSTEM idation cycle must be generated by asserting AHOLD and EADS# to the second processor and its cache. This type of invalidation is true for the write-through cache such as the one shown in Figure 6-10. If the caches are write-back caches the invalidation protocol may be different. BREQ 2 BACK 2 BREQ 0...

-

Page 168: An Intel486™ Processor System Example

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL these multiprocessor environments. A write-back cache will, however, be more complex in its ar- chitecture and coherency mechanisms. AN Intel486™ PROCESSOR SYSTEM EXAMPLE A typical Intel486 processor system is shown in Figure 6-11. The Intel486 processor has a local bus that consists of address, data and control buses. -

Page 169: The Memory Hierarchy And Advantages Of A Second-Level Cache

CACHE SUBSYSTEM a similar manner, allowing the L2 cache to be implemented into an Intel486 processor system with ease. 6.8.1 The Memory Hierarchy and Advantages of a Second-level Cache The Intel486 processor has an on-chip cache and a high-speed register set. These registers are ac- corded the first level of memory hierarchy. - Page 171 Peripheral Subsystem Chapter Contents Peripheral/Processor Bus Interface ........7-1 Basic Peripheral Subsystem ..........7-17 I/O Cycles ................7-29 Differences Between the Intel486™ DX Processor Family and Intel386™ Processors...........7-33 Interfacing to x86 Peripherals ..........7-34 Intel486™ Processor LAN Controller Interface ....7-38...

-

Page 173: Peripheral/Processor Bus Interface

CHAPTER 7 PERIPHERAL SUBSYSTEM The peripheral (I/O) interface is an essential part of any embedded processor system. It supports communications between the microprocessor and the peripherals. Given the variety of existing peripheral devices, a peripheral system must allow a variety of interfaces. An important part of a microprocessor system is the bus that connects all major parts of the system. - Page 174 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL FFFFFFFFH Accessible Physical Memory 4 Gbyte Accessible 0000FFFFH Accessible Programmed 64 Kbyte I/O Space 00000000H 00000000H Physical Memory I/O Space Space Figure 7-1. Mapping Scheme I/O mapping and memory-mapping differ in the following respects: •...

-

Page 175: Dynamic Bus Sizing

PERIPHERAL SUBSYSTEM • Memory mapping offers more flexibility in Protected Mode than I/O mapping. Memory- mapped devices are protected by the memory management and protection features. A device can be inaccessible to a task, visible but protected, or fully accessible, depending on where it is mapped. - Page 176 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 7-1. Next Byte-Enable Values for the BS x # Cycles Current Next with BS8# Next with BS16# BE3# BE2# BE1# BE0# BE3# BE2# BE1# BE0# BE3# BE2# BE1# BE0# NOTE: “N” means that another bus cycle is not required to satisfy the request.

-

Page 177: Address Decoding For I/O Devices

PERIPHERAL SUBSYSTEM Table 7-2. Valid Data Lines for Valid Byte Enable Combinations BE3# BE23 BE1# BE0# w/o BS8#/BS16# w BS8# w BS16# D7–D0 D7–D0 D7–D0 D15–D0 D7–D0 D15–D0 D23–D0 D7–D0 D15–D0 D31–D0 D7–D0 D15–D0 D15–D8 D15–D8 D15–D8 D23–D8 D15–D8 D15–D8 D31–D8 D15–D8 D15–D8... -

Page 178: Address Bus Interface

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 7.1.3.1 Address Bus Interface Figure 7-2 shows the Intel486 processor address interface to 32-, 16- and 8-bit devices. To ad- dress 16-bit devices, the byte enables must be decoded to produce A1, BHE# and BLE# (A0) sig- nals. -

Page 179: 8-Bit I/O Interface

PERIPHERAL SUBSYSTEM BE0# BE1# BE1# BHE# BE3# BE0# BLE# (OR A0) BE2# BE0# BE1# Figure 7-3. Logic to Generate A1, BHE# and BLE# for 16-Bit Buses 7.1.3.2 8-Bit I/O Interface Due to the presence of dynamic data bus sizing and the variety of byte-enable pin combinations (Table 7-2), byte swapping logic for 32-to-8-bit conversions can be implemented in various ways. - Page 180 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Bidirectional Data Buffers BUFF BE3# BUFF Intel486™ 8-Bit BE2# Processor Interface BUFF BE1# BUFF BE0# BEN8H# BEN8UL# BEN8UH# A5283-02 Figure 7-4. Intel486™ Processor Interface to 8-Bit Device In this example of a 32-bit write, the BE3#–BE0# are enabled; hence 32 bits of data reside on the data buffer outputs.

- Page 181 PERIPHERAL SUBSYSTEM Table 7-3. PLD Input Signals BS8# The signal is from an 8-bit device or from the system logic that interfaces to an 8-bit device. BE3#–BE0# When processor drives all of these signals Low, external logic should look only for BE0# while in 8-bit mode.

-

Page 182: 16-Bit I/O Interface

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 7-5. 32-Bit to 8-Bit Steering (Sheet 2 of 2) Intel486™ Processor 8-Bit Interface BE3# BE2# BE1# BE0# BEN16# BEN8UH# BEN8UL# BEN8H# BHE# † † Inputs Outputs NOTES: X implies “do not care” (either 0 or 1). - Page 183 PERIPHERAL SUBSYSTEM BUFF 0 BE3# BUFF 1 BE2# BUFF 2 BE1# 16-Bit BUFF 3 BE0# BUFF 4 BEN16# BUFF 5 Figure 7-5. Bus Swapping 16-Bit Interface Table 7-9 shows the truth table for 32-to-16-bit bus swapping logic and A0, A1 and BHE# gen- eration.

- Page 184 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 7-6. PLD Input Signals BS16# Either from a 16-bit device or from system logic which indicates a 16-bit transfer. BE3#–BE0# Byte enable inputs from Intel486™ processor. In 16-bit mode, the external logic should look at BE0# and BE1# only.

- Page 185 PERIPHERAL SUBSYSTEM Table 7-9. 32-Bit to 16-Bit Bus Swapping Logic Truth Table (Sheet 2 of 2) Intel486™ Processor 8-Bit Interface BE3# BE2# BE1# BE0# BEN16# BEN8UH# BEN8UL# BEN8H# BHE# † † † Inputs Outputs NOTES: X implies “do not care” (either 0 or 1). BHE# (byte high enable) is not needed in 8-bit interface.

-

Page 186: 32-Bit I/O Interface

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL From 8-Bit BS8# BS16# From 16-Bit BEN16# BEN8UH# BS0# BEN8UL# BS1# BEN8H# BS2# BS3# BHE# Figure 7-6. Bus Swapping and Low Address Bit Generating Control Logic 7.1.3.4 32-Bit I/O Interface A simple 32-bit I/O interface is shown in Figure 7-7. - Page 187 PERIPHERAL SUBSYSTEM Intel486™ Processor Data Bus 32-Bit I/O Device BUFF 0 BE3# BUFF 1 BE2# BUFF 2 BE1# BUFF 3 BE0# Figure 7-7. 32-Bit I/O Interface 7-15...

- Page 188 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 7-10. 32-Bit to 32-Bit Bus Swapping Logic Truth Table Intel486™ Processor 8-Bit Interface BE3# BE2# BE1# BE0# BEN16# BEN8UH# BEN8UL# BEN8H# BHE# † † † † † † Inputs Outputs NOTES: 1. X implies “do not care” (either 0 or 1).

-

Page 189: Basic Peripheral Subsystem

Proprietary) Figure 7-8. System Block Diagram An embedded Intel486 processor system may consist of several subsystems. The heart of the sys- tem is the processor. The memory subsystem is also important and must be efficient and opti- mized to provide peak system level performance. As described in Chapter 5, “Memory... - Page 190 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Subsystem Design,” it is necessary to utilize the burst-bus feature of the Intel486 processor for the DRAM control implementation. The cache subsystem, as described in Chapter 6, “Cache Subsystem,” also plays an important role in overall system performance. For many systems how- ever, the on-chip cache provides sufficient performance.

- Page 191 PERIPHERAL SUBSYSTEM INTA (To Interrupt Controller) ADS# ADS# RECOV Clock M/IO# M/IO# D/C# D/C# IOR# W/R# W/R# IOW# Bus Control Intel486™ CS0# and Ready CS1# RDY# RDY# IOCYC Data Addr BE3#– BE0# CS1# Address Decoder CS0# Data Data CS0# Transceiver I/O #2 (32-Bit) CS1#...

-

Page 192: Bus Control And Ready Logic

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 7.2.1 Bus Control and Ready Logic A typical peripheral device has address inputs which the processor uses to select the device’s in- ternal registers. It also has a chip select (CS#) signal which enables it to read data from and write data to the data bus, as controlled by the READ (RD#) and WRITE (WR#) control signals. -

Page 193: Bus Control Signal Description

Memory write † NOTE: Intel reserved. Do not use. RDY#—Ready Output Signal. This signal is connected directly to the Intel486 processor’s RDY# input and indicates that the current bus cycle is complete. It also indicates that the I/O de- vice has returned valid data to the Intel486 processor’s data pins following an I/O write cycle. For the Intel486 processor, RDY# is ignored when the bus is idle and at the end of the first clock of the bus cycle. -

Page 194: Wait State Generation Signals

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL IOR#—The I/O Read Signal. This signal is active low and is generated when the Intel486 pro- cessor’s W/R# output signal is low, indicating a read cycle. When IOR# is low, data can be read from the peripheral device. -

Page 195: Address Decoder

PERIPHERAL SUBSYSTEM Figure 7-10 shows PLD equations for basic I/O control logic. A wait state generator should be implemented to optimize wait state generation. Inputs ADS#, M/IO#, D/C#, W/R#, SEL0, SEL1, SEL2 Outputs IOCYC, 0 C1, C2, IOR#, IOW#, RDY# IOCYC = IOCYCLE VALID C0, C1, C2 = Outputs of a 3-bit counter Sel 0, 1, 2 = Programmable wait state select input... - Page 196 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Address select signals are asserted within the range of addresses which is determined by the de- coded address lines. The relationship between memory and I/O mapping and address decoding is given by the following equation:...

- Page 197 PERIPHERAL SUBSYSTEM Figure 7-11, address lines A15–A8 are ignored to maintain simplicity. Lines A7–A2 are de- coded to generate addresses XXE0–XXFC. When a valid cycle begins, ADS# is latched in the flip-flop. (15) (14) (13) Enable G2A# Inputs G2B# (12) Data Outputs (11)

-

Page 198: Data Transceivers

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL When A5, A6 and A7 are high and ADS# is strobed, E2 on the decoder is enabled. Here, M/IO# is low and D/C# is high, enabling inputs E1 and E3 of the decoder. When RDY# is active, E2 is disabled and the address is no longer valid. -

Page 199: Write Buffers And I/O Cycles

PERIPHERAL SUBSYSTEM Bus control logic should implement recovery to eliminate bus contention. The logic generates a RECOV signal until the data from the previous read floats. It may or may not be possible to en- force this recovery with the hardware counter. The hardware counter method may not be feasible when recovery times are too fast for the hardware counter (i.e., when recovery time is in nano- seconds). -

Page 200: Intel486™ Processor On-Chip Cache Consistency

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL An example of when a read around could cause a problem follows: • The interrupt controller is memory-mapped in cacheable memory. • The write buffer is filled with write cache hits, so a read is reordered in front of the writes. -

Page 201: I/O Cycles

PERIPHERAL SUBSYSTEM I/O CYCLES The I/O read and write cycles used in a system are a factor of the I/O control logic implementa- tion. Figures 7-13 through 7-16 illustrate an I/O read and write cycle for a typical implementation. 7.3.1 Read Cycle Timing A new processor read cycle is initiated when ADS# is asserted in T1. - Page 202 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL ADS# M/IO# D/C# A31–A2 W/R# IOCYC IOR# To CPU DATA RDY# Figure 7-14. I/O Read Timings 7-30...

-

Page 203: Write Cycle Timings

PERIPHERAL SUBSYSTEM 7.3.2 Write Cycle Timings The I/O write cycle is similar to the I/O read cycle with the exception of W/R# being asserted high when sampled rather than low from the Intel486 processor side. This is shown in Figures 7-15 and 7-16. - Page 204 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Write Signal Valid Delay PLDpd = 10 ns Write Data Valid Delay † BUFpd = 19 + 9 = 28 ns Write Data Float Time † – T BUFpd = 0 + 9 = 9 ns †...

-

Page 205: Difference Between The Intel486 Dx Processor Family And Intel386 Processors

1x clock, parity support , burst cycles, cacheable cycles, cache invalidate cycles and 8-bit support. The Hardware Interface and Bus Operation chapters of the Embedded Intel486™ Processor Family Developer’s Manual explains of the bus functionality and its hardware interface. •... -

Page 206: Interfacing To X86 Peripherals

These microcontrollers have a slave interface on-board and include an 8-bit CPU, ROM, RAM, an I/O timer/counter and a clock. Intel supplies an EPROM implementation, which in- cludes the 8741 and 8742 microcontrollers. The 8742 has a 2 K x 8-bit ROM and 256 K x 8-bit RAM, an eight-bit timer/counter and 18 programmable I/O pins. -

Page 207: 82C59A Interface

Once the interrupt service rou- tine is executed, the previous processor state is restored, and program execution resumes. The Intel486 processor can handle up to 256 interrupts/exceptions. Refer to the Embedded Intel486™ Processor Family Developer’s Manual for the interrupt table. - Page 208 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Clock Generator Master Mode Byte Swap BE3#–BE0# Logic IRQ0 IRQ1 IRQ6 32 Bits 8 Bit DATA Data IRQ7 Transceivers W/R# 82C59A Address Address SP/EN# Decoder Intel486™ Processor INTA# CAS0 Bus Control INTR CAS1 M/IO#...

-

Page 209: Cascaded Interrupt Controllers

PERIPHERAL SUBSYSTEM 7.5.2.2 Cascaded Interrupt Controllers Figure 7-20 shows how several interrupt controllers can be cascaded to handle up to 64 interrupt requests. One device acts as the master and the rest as slaves. The interface between these devices resembles the single device interface with the following additional features: •... -

Page 210: Handling More Than 64 Interrupts

The additional hardware required to implement this configuration includes additional 82C59A devices and the chip-select logic. Intel486™ PROCESSOR LAN CONTROLLER INTERFACE This section describes two LAN interface solutions using Intel controllers: the 82596CA copro- cessor and the PCI-compliant 82557 controller for fast Ethernet networks. 7.6.1... - Page 211 PERIPHERAL SUBSYSTEM • Industry-Standard Network Support — IEEE 802.3 (Ethernet, Ethernet Twisted Pair, Cheapernet, StarLAN, etc.) — IBM PC Network (baseband and broadband) — Proprietary CSMA/CD networks up to 20 Mbits/second — HDLC frame delimiting • Compatible Intel486 Processor Interface —...

- Page 212 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Serial Subsystem FIFO Subsystem Subsystem LE/BE Ports Data FIFO Interface 2x32 D31–D0 Unit TxD, RTS# LPSK# CSMA/CD Control Interface Unit RxD, RxC# Micro TxC#, CTS# Machine CDT#, CRS# A31–A2 BE3#–BE0# Figure 7-21. 82596CA Coprocessor Block Diagram The coprocessor can be used in either baseband or broadband networks.

-

Page 213: Hardware Interface

The 82596 coprocessor is an extension of the earlier 82586 LAN coprocessor, which interfaces an Ethernet network to a 16-bit Intel bus. The 82596 coprocessor can be configured to run soft- ware drivers written for the 82586 device without modification. - Page 214 EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Table 7-12. 82596 Signals (Sheet 1 of 2) Signal Type Description Address and Data Buses A31–A2 Address D31–D0 Data BE3#–BE0# Byte-enables BS16# 16-bit data bus size LE/BE# Little endian or big endian byte ordering DP3–DP0...

- Page 215 PERIPHERAL SUBSYSTEM Table 7-12. 82596 Signals (Sheet 2 of 2) Signal Type Description Network (Serial) Interface † Transmit data † TxC# Transmit clock LPBK# Loopback Receive data RxC# Receive clock RTS# Request to send CTS# Clear to send CRS# Carrier sense CDT# Collision detect †...

-

Page 216: Processor And Coprocessor Interaction

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL A31–A2 D31–D0 BE3#–BE0# DP3–DP0, PCHK# RDY#, W/R#, ADS# BRDY#, BLAST# 82596 LAN Intel486™ AHOLD, BOFF# Controller Processor BS16#, LOCK# HOLD, HLDA BREQ CA, RESET M/IO#, D/C# Glue PORT# Figure 7-23. 82596-to-Processor Interfacing Access to memory and I/O resources can be overlapped between the processor and the coproces- sor with the bus backoff (BOFF#) output to the processor. - Page 217 PERIPHERAL SUBSYSTEM INTA# 82596 Intel486™ Processor INT/INT# Controller Shared Memory Initialization Root System Control Block Mailbox Command Line Receive Frame Area Transmit Buffer Figure 7-24. 82596 Shared Memory The coprocessor executes its command list from shared memory and, in parallel, receives frames from the network and places them in shared memory.

-

Page 218: Memory Structure

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL 7.6.1.3 Memory Structure The memory shared by the processor and 82596 coprocessor consists of four parts. • Initialization root • System control block • Command list (including transmit buffer) • Receive frame area The command list functions as a program. Individual commands are placed in blocks of memory called command blocks. -

Page 219: Transmit And Receive Operation

PERIPHERAL SUBSYSTEM • Proposed 10BASE-F • Proposed 10BASE-T 7.6.1.5 Transmit and Receive Operation Most of the bus traffic initiated by the coprocessor consists of DMA transfers of frame data. The coprocessor transmits data as a series of frames by executing a series of high-level commands from the command list in memory. -

Page 220: Design Considerations

BREQ output can be tied directly to the coprocessor’s BREQ input. 7.6.1.7 Design Considerations The glue logic for interfacing the 82596 coprocessor to the Intel486 processor can be contained in a single Intel 85C220 PLD, as shown in Figure 7-26. This logic provides four functions: •... -

Page 221: 82596 Co-Processor Performance

PERIPHERAL SUBSYSTEM The CA, 596RESET, and PORT# signals are generated according to the equations shown in Fig- 7-26. The M/IO# and D/C# signals are also generated by the glue logic. When both HOLD and HLDA are asserted, indicating that the coprocessor has requested and been granted the bus, M/IO# and D/C# must be driven high. -

Page 222: 82557 High Speed Lan Controller Interface

7.6.2.1 82557 Overview The 82557 is Intel’s first highly-integrated 32-bit PCI LAN controller for 10 or 100 Mbps Fast Ethernet networks. The 82557 offers a high performance LAN solution while maintaining low- cost through its high integration. It contains a 32-bit PCI Bus Master interface to fully utilize the high bandwidth (up to 132 Mbytes per second) available to masters on the PCI bus. -

Page 223: Features And Enhancements

PERIPHERAL SUBSYSTEM which will allow connection to 100/10 Mbps networks. For 10 Mbps networks, the 82557 can be interfaced to a standard ENDEC device (such as the Intel 82503 Serial Interface), while maintain- ing software compatibility with 100 Mbps solutions. -

Page 224: Pci Bus Interface

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL Parallel Side Serial Side Flash/EEPROM Interface Target Interface TX FIFO On-board System Micro- 10/100 Mbps FIFO Extender Control Machine CSMA/CD Block Control (SCB) Structure RX FIFO Serial 4-Channel PCI Interface Bus Master Interface Figure 7-27. Intel 82557 Block Diagram 7.6.2.3... -

Page 225: Controlling The 82557

PERIPHERAL SUBSYSTEM 7.6.2.6 Controlling the 82557 The CPU issues control commands to the Command Unit (CU) and Receive Unit (RU) through the SCB, which is part of the CSR. The CPU instructs the 82557 to Activate, Suspend, Resume or Idle the CU or RU by placing the appropriate control command in the CU or RU control field. A CPU write access to the SCB causes the 82557 to read the SCB, including the Status word, Command word, CU and RU Control fields, and the SCB General Pointer. - Page 227 System Bus Design Chapter Contents Introduction ................8-1 System Bus Interface ............8-1 EISA Bus: System Design Example ........8-2 PCI Bus: System Design Example........8-19...

-

Page 229: Introduction