Summary of Contents for Motorola MC68030

- Page 1 MOTOROLA MC68030 ENHANCED 32-BIT MICROPROCESSOR USER’S MANUAL Third Edition © MOTOROLA INC., 1992...

- Page 2 PREFACE The MC68030 User's Manual describes the capabilities, operation, and programming of the MC68030 32-bit second-generation enhanced microprocessor. The manual consists of the following sections and appendix. For detailed information on the MC68030 instruction set refer to M68000PM/AD, M68000 Family Programmer's Reference Manual.

- Page 3 Motorola microprocessors throughout the manual. However, Section 1 and Appendix A specifically identify the MC68030 within the rest of the family and contrast its differences. xxiv MC68030 USER’S MANUAL...

-

Page 4: Table Of Contents

Features ..........1-3 MC68030 Extensions to the M68000 Family ....1-4 Programming Model . - Page 5 Exception Processing........4-6 xxvi MC68030 USER’S MANUAL MOTOROLA...

- Page 6 Pipeline Refill (REFILL) ........5-10 5.11.4 Internal Microsequencer Status (STATUS) ....5-10 MOTOROLA MC68030 USER’S MANUAL xxvii...

- Page 7 Dynamic Bus Sizing........7-6 xxviii MC68030 USER’S MANUAL MOTOROLA...

- Page 8 Address, Size, and Data Bus Relationships ....7-22 7.2.5 MC68030 versus MC68020 Dynamic Bus Sizing ....7-24 7.2.6 Cache Filling .

- Page 9 Long-Format Indirect Descriptor ......9-27 9.5.1.11 Short-Format Indirect Descriptor ......9-27 MC68030 USER’S MANUAL MOTOROLA...

- Page 10 Write Protect ........9-48 MC68030 and MC68851 Mmu Differences ....9-51 Registers .

- Page 11 Save CIR ..........10-30 xxxii MC68030 USER’S MANUAL MOTOROLA...

- Page 12 Trace Exceptions ........10-70 MOTOROLA MC68030 USER’S MANUAL xxxiii...

- Page 13 Bit Field Manipulation Instructions......11-47 11.6.15 Conditional Branch Instructions......11-48 xxxiv MC68030 USER’S MANUAL MOTOROLA...

- Page 14 Floating-Point Units ........12-5 12.3 Byte Select Logic for the MC68030 ......12-9 12.4 Memory Interface .

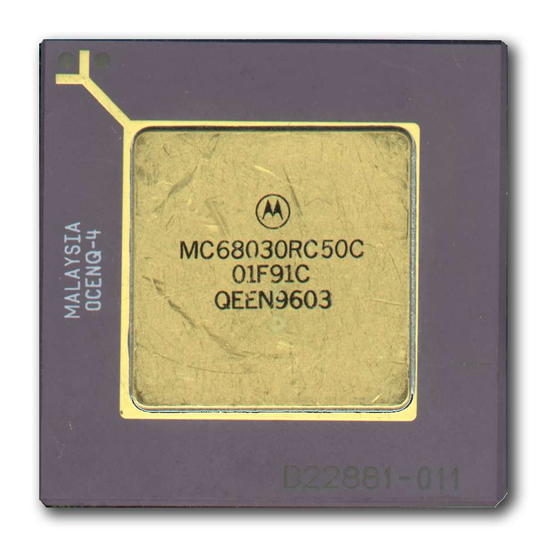

- Page 15 Mechanical Data 14.1 Standard MC68030 Ordering Information ..... 14-1 14.2 Pin Assignments — Pin Grid Array (RC Suffix) ....14-2 14.3...

- Page 16 Functional Signal Groups ........5-1 Internal Caches and the MC68030....... 6-2 On-Chip Instruction Cache Organization .

- Page 17 Internal Operand Representation ....... . 7-8 MC68030 Interface to Various Port Sizes ......7-9 Example of Long-Word Transfer to Word Port .

- Page 18 Burst Request — CBACK and CIIN Asserted ..... . 7-66 7-42 MC68030 CPU Space Address Encoding ......7-69 7-43 Interrupt Acknowledge Cycle Flowchart .

- Page 19 Translation Control Register (TC) Format ......9-54 9-37 Transparent Translation Register (TT0 and TT1) Format ... . . 9-57 MC68030 USER’S MANUAL MOTOROLA...

- Page 20 Asynchronous Non-DMA M68000 Coprocessor Interface Signal Usage . . 10-6 10-3 MC68030 CPU Space Address Encodings ......10-7 10-4 Coprocessor Address Map in MC68030 CPU Space.

-

Page 21: Adapting The Mc68030 To Mc68020 Designs

Example MC68030 Byte Select PAL System Configuration ... 12-12 12-7 MC68030 Byte Select PAL Equations ......12-13 12-8 Access Time Computation Diagram. -

Page 22: Microsequencer

Data Bus Requirements for Read Cycles......7-10 MC68030 Internal to External Data Bus......7-11 Memory Alignment and Port Size Influence on Write Bus Cycles . - Page 23 GND Pin Assignments....... . . 12-46 xliv MC68030 USER’S MANUAL MOTOROLA...

- Page 24 The MC68030 fully supports the nonmultiplexed bus structure of the MC68020, with 32 bits of address and 32 bits of data. The MC68030 bus has an enhanced controller that supports both asynchronous and synchronous bus cycles and burst data transfers. It also supports...

- Page 25 Introduction Figure 1-1. Block Diagram MC68030 USER’S MANUAL MOTOROLA...

-

Page 26: Features

Floating-Point Support Provided by the MC68881/MC68882 Floating-Point Coproces- sors • 4-Gbyte Logical and Physical Addressing Range • Implemented in Motorola's HCMOS Technology That Allows CMOS and HMOS (High- Density NMOS) Gates to be Combined for Maximum Speed, Low Power, and Optimum Die Size •... -

Page 27: Mc68030 Extensions To The M68000 Family

Introduction 1.2 MC68030 EXTENSIONS TO THE M68000 FAMILY In addition to the on-chip instruction cache present in the MC68020, the MC68030 has an internal data cache. Data that is accessed during read cycles may be stored in the on-chip cache, where it is available for subsequent accesses. The data cache reduces the number of external bus cycles when the data operand required by an instruction is already in the data cache. - Page 28 I/O control, and memory management subsystems. The supervisor programming model contains all the controls to access and enable the special features of the MC68030. This segregation was carefully planned so that all application software is written to run at the nonprivileged user level and migrates to the MC68030 from any M68000 platform without modification.

- Page 29 All of the 16 general-purpose registers (D0–D7, A0–A7) may be used as index registers. 16 15 DATA REGISTERS 16 15 ADDRESS REGISTERS 16 15 USER STACK A7 (USP) POINTER PROGRAM COUNTER CONDITION CODE REGISTER Figure 1-2. User Programming Model MC68030 USER’S MANUAL MOTOROLA...

- Page 30 The program counter (PC) contains the address of the next instruction to be executed by the MC68030. During instruction execution and exception processing, the processor automatically increments the contents of the PC or places a new value in the PC, as appropriate.

-

Page 31: Translation Table Structure

The CPU root pointer (CRP) contains a pointer to the root of the translation tree for the currently executing task of the MC68030. This tree contains the mapping information for the task's address space. When the MC68030 is configured to provide a separate address space for supervisor routines, the supervisor root pointer (SRP) contains a pointer to the root of the translation tree describing the supervisor's address space. -

Page 32: Data Types And Addressing Modes

1.5 INSTRUCTION SET OVERVIEW The instructions in the MC68030 instruction set are listed in Table 1-2. The instruction set has been tailored to support structured high-level languages and sophisticated operating systems. Many instructions operate on bytes, words, or long words, and most instructions can use any of the 18 addressing modes. - Page 33 16 or 32 bits. = Program Counter (data) = Immediate value of 8, 16, or 32 bits = Effective Address = Use as indirect access to long-word address. 1-10 MC68030 USER’S MANUAL MOTOROLA...

-

Page 34: Virtual Memory And Virtual Machine Concepts

Introduction 1.6 VIRTUAL MEMORY AND VIRTUAL MACHINE CONCEPTS The full addressing range of the MC68030 is 4 Gbytes (4,294,967,296 bytes) in each of eight address spaces. Even though most systems implement a smaller physical memory, the system can be made to appear to have a full 4 Gbytes of memory available to each user program by using virtual memory techniques. - Page 35 Trap on Overflow LSL, LSR Logical Shift Left and Right TRAPV Test on Overflow MOVE Move Test Operand MOVEA Move Address UNLK Unlink MOVE CCR Move Condition Code Register UNPK Unpack BCD MOVE SR Move Status Register 1-12 MC68030 USER’S MANUAL MOTOROLA...

-

Page 36: Virtual Machine

(and should be emulated) are trapped to the governing operating system and performed by its software. In the MC68030 implementation of a virtual machine, the virtual application runs at the user privilege level. The governing operating system executes at the supervisor privilege level and any attempt by the new operating system to access supervisor resources or execute privileged instructions causes a trap to the governing operating system. -

Page 37: The Memory Management Unit

The technique used by the MC68030 is paged memory management because physical memory is managed in blocks of a specified number of bytes, called page frames. -

Page 38: Pipelined Architecture

Addition of the data cache in the MC68030 extends the benefits of cache techniques to all memory accesses. During a write cycle, the data cache circuitry writes data to a cached data item as well as to the item in memory, maintaining consistency between data in the cache and that in memory. -

Page 39: Data Organization And Addressing Capabilities

A third type of external reference used for coprocessor communications, interrupt acknowledge cycles, and breakpoint acknowledge cycles is classified as a CPU space reference. The MC68030 automatically sets the function codes to access the program space, the data space, or the CPU space for special functions as required. -

Page 40: Organization Of Data In Registers

BCD format, a byte contains one digit; the four least significant bits contain the binary value and the four most significant bits are undefined. Each byte of the packed BCD format contains two digits; the least significant four bits contain the least significant digit. MC68030 USER’S MANUAL MOTOROLA... - Page 41 Note: If width + offset < 32, bit filed wraps around within the register. Unpacked BCD (a = MSB) Packed BCD (a = MSB First Digit, e = MSB Second Digit) Data Organization in Data Registers MOTOROLA MC68030 USER’S MANUAL...

-

Page 42: Address Registers

The status register (SR), shown in Figure 1–4, is 16 bits wide. Only 12 bits of the status register are defined; all undefined values are reserved by Motorola for future definition. The undefined bits are read as zeros and should be written as zeros for future compatibility. The lower byte of the status register is the CCR. -

Page 43: Organization Of Data In Memory

N + 2, leaving the least significant byte at address N + 3 (refer to Figure 2–1). Notice that the MC68030 does not require data to be aligned on word boundaries (refer to Figure 2–2), but the most efficient data transfers occur when data is aligned on the same byte boundary as its operand size. - Page 44 Data Organization and Addressing Capabilities The data types supported in memory by the MC68030 are bit and bit field data; integer data of 8, 16, or 32 bits; 32-bit addresses; and BCD data (packed and unpacked). These data types are organized in memory as shown in Figure 2–2. Note that all of these data types can be accessed at any byte address.

- Page 45 PACKED BINARY-CODED DATA BYTE n - 1 BYTE n + 1 BYTE n + 2 ADDRESS UNPACKED BINARY-CODED DATA BYTE n - 1 BYTE n + 2 ADDRESS XX = USER DEFINED VALUE Figure 2-2. Memory Data Organization MOTOROLA MC68030 USER’S MANUAL...

-

Page 46: Addressing Modes

EFFECTIVE ADDRESS MODE REGISTER Figure 2-3. Single Effective Address Many instructions imply the addressing mode for one of the operands. The formats of these instructions include appropriate fields for operands that use only one addressing mode. MC68030 USER’S MANUAL MOTOROLA... -

Page 47: Data Register Direct Mode

In the data register direct mode, the operand is in the data register specified by the effective address register field. GENERATION: EA = Dn ASSEMBLER SYNTAX: MODE: REGISTER: DATA REGISTER: OPERAND OPERAND NUMBER OF EXTENSION WORDS: MOTOROLA MC68030 USER’S MANUAL... -

Page 48: Address Register Direct Mode

GENERATION: EA = (An) An = An + SIZE ASSEMBLER SYNTAX: (An) + MODE: REGISTER: MEMORY ADDRESS ADDRESS REGISTER: OPERAND LENGTH ( 1, 2, OR 4): MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 2-10 MC68030 USER’S MANUAL MOTOROLA... -

Page 49: Address Register Indirect With Predecrement Mode

GENERATION: An = An – SIZE EA = (An) ASSEMBLER SYNTAX: – (An) MODE: REGISTER: MEMORY ADDRESS ADDRESS REGISTER: OPERAND LENGTH (1, 2, OR 4): MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 0 MOTOROLA MC68030 USER’S MANUAL 2-11... -

Page 50: Address Register Indirect With Displacement Mode

EA = (An) + (XN) + d (d ,An,Xn.SIZE*SCALE) ASSEMBLER SYNTAX: MODE: REGISTER: ADDRESS REGISTER: MEMORY ADDRESS DISPLACEMENT: SIGN EXTENDED INTEGER INDEX REGISTER SIGN-EXTENDED VALUE SCALE: SCALE VALUE MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 2-12 MC68030 USER’S MANUAL MOTOROLA... -

Page 51: Address Register Indirect With Index (Base Displacement) Mode

EA = (An) + (Xn) + bd ASSEMBLER SYNTAX: (bd,An,Xn.SIZE*SCALE) MODE: REGISTER: ADDRESS REGISTER: MEMORY ADDRESS BASE DISPLACEMENT: SIGN-EXTENDED VALUE INDEX REGISTER: SIGN-EXTENDED VALUE SCALE: SCALE VALUE MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1,2, OR 3 MOTOROLA MC68030 USER’S MANUAL 2-13... -

Page 52: Memory Indirect Postindexed Mode

SIGN-EXTENDED VALUE INDIRECT MEMORY ADDRESS POINTS TO VALUE AT INDIRECT MEMORY ADDRESS INDEX REGISTER: SIGN-EXTENDED VALUE SCALE VALUE SCALE: OUTER DISPLACEMENT: SIGN-EXTENDED VALUE EFFECTIVE ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1,2, 3, 4, OR 5 2-14 MC68030 USER’S MANUAL MOTOROLA... -

Page 53: Memory Indirect Preindexed Mode

SIGN-EXTENDED VALUE SIGN-EXTENDED VALUE SCALE VALUE INDEX REGISTER: INDIRECT MEMORY ADDRESS POINTS TO SCALE: VALUE AT INDIRECT MEMORY ADDRESS OUTER DISPLACEMENT: SIGN-EXTENDED VALUE EFFECTIVE ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1,2, 3, 4, OR 5 MOTOROLA MC68030 USER’S MANUAL 2-15... -

Page 54: Program Counter Indirect With Displacement Mode

EA = (PC) + (Xn) + d ASSEMBLER SYNTAX: (d , PC,Xn. SIZE*SCALE) MODE: REGISTER: PROGRAM COUNTER: ADDRESS OF EXTENSION WORD DISPLACEMENT: SIGN EXTENDED INTEGER INDEX REGISTER SIGN-EXTENDED VALUE SCALE: SCALE VALUE MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 2-16 MC68030 USER’S MANUAL MOTOROLA... -

Page 55: Program Counter Indirect With Index (Base Displacement) Mode

ASSEMBLER SYNTAX: (bd, PC, Xn. SIZE*SCALE) MODE: REGISTER: PROGRAM COUNTER: ADDRESS OF EXTENSION WORD BASE DISPLACEMENT: SIGN-EXTENDED VALUE INDEX REGISTER SIGN-EXTENDED VALUE SCALE: SCALE VALUE MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1, 2 OR 3 MOTOROLA MC68030 USER’S MANUAL 2-17... -

Page 56: Program Counter Memory Indirect Postindexed Mode

INDIRECT MEMORY ADDRESS POINTS TO VALUE AT INDIRECT MEMORY ADDRESS IN PROGRAM SPACE INDEX REGISTER: SIGN-EXTENDED VALUE SCALE VALUE OUTER DISPLACEMENT: SIGN-EXTENDED VALUE EFFECTIVE ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1,2, 3, 4, OR 5 2-18 MC68030 USER’S MANUAL MOTOROLA... -

Page 57: Program Counter Memory Indirect Preindexed Mode

INDEX REGISTER SIGN-EXTENDED VALUE SCALE VALUE INDIRECT MEMORY ADDRESS POINTS TO VALUE AT INDIRECT MEMORY ADDRESS IN PROGRAM SPACE OUTER DISPLACEMENT: SIGN-EXTENDED VALUE EFFECTIVE ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 1, 2, 3, 4 OR 5 MOTOROLA MC68030 USER’S MANUAL 2-19... -

Page 58: Absolute Short Addressing Mode

GENERATION: EA GIVEN ASSEMBLER SYNTAX: (xxx).L MODE: REGISTER FIELD: FIRST EXTENSION WORD: ADDRESS HIGH SECOND EXTENSION WORD: ADDRESS LOW CONCATENATION MEMORY ADDRESS: OPERAND NUMBER OF EXTENSION WORDS: 2-20 MC68030 USER’S MANUAL MOTOROLA... -

Page 59: Immediate Data

Coprocessor instructions can support immediate data of any size. The instruction word is followed by as many extension words as are required. Generation: Operand given Assembler Syntax: #xxx Mode Field: Register Field: Number of Extension Words: 1 or 2, except for coprocessor instructions MOTOROLA MC68030 USER’S MANUAL 2-21... -

Page 60: Effective Address Encoding Summary

The longest instruction for the MC68030 contains 10 extension words. It is a MOVE instruction with full format extension words for both source and destination effective addresses and with 32-bit base displacements and 32-bit outer displacements for both addresses. -

Page 61: Format

A memory addressing effective address mode is one that refers to memory operands. Alterable An alterable addressing effective address mode is one that refers to alterable (writable) operands. Control A control addressing effective address mode is one that refers to memory operands without an associated size. MOTOROLA MC68030 USER’S MANUAL 2-23... -

Page 62: Programmer`s View Of Addressing Modes

2.6 PROGRAMMER`S VIEW OF ADDRESSING MODES Extensions to the indexed addressing modes, indirection, and full 32-bit displacements provide additional programming capabilities for both the MC68020 and the MC68030. This section describes addressing techniques that exploit these capabilities and summarizes the addressing modes from a programming point of view. -

Page 63: Addressing Capabilities

(if at all), particularly in programs that require maximum performance. 2.6.1 Addressing Capabilities In both the MC68020 and the MC68030, setting the base register suppress (BS) bit in the full format extension word (see Figure 2–4) suppresses use of the base address register in calculating the effective address. - Page 64 Data Organization and Addressing Capabilities For both the MC68020 and the MC68030, the register indirect modes can be extended further. Since displacements can be 32 bits wide, they can represent absolute addresses or the results of expressions that contain absolute addresses. This allows the general register indirect form to be (bd,Rn) or (bd,An,Rn) when the base register is not suppressed.

- Page 65 RECORD OF 8 WORDS (SCALE = 4) (SCALE = 8) A6 = 1 A6 = 1 NOTE: Regardless of array structure, software increments index by the appropriate amount to point to next record. Figure 2-7. Addressing Array Items MOTOROLA MC68030 USER’S MANUAL 2-27...

- Page 66 The preindexed indirect mode (see Figure 2–11) uses the contents of An as an index to the pointer list structure at the displacement. Register Xn is the index to the pointer, which contains the address of the data item. 2-28 MC68030 USER’S MANUAL MOTOROLA...

- Page 67 Data Organization and Addressing Capabilities SYNTAX: ([An],od) MEMORY STRUCTURE POINTER DATA ITEM Figure 2-9. Accessing an Item in a Structure Using a Pointer SYNTAX: ([bd,An]) POINTER LIST POINTER DATA ITEM Figure 2-10. Indirect Addressing, Suppressed Index Register MOTOROLA MC68030 USER’S MANUAL 2-29...

- Page 68 Data Organization and Addressing Capabilities SYNTAX: ([bd,An,Xn]) POINTER LIST DATA ITEM POINTER Figure 2-11. Preindexed Indirect Addressing 2-30 MC68030 USER’S MANUAL MOTOROLA...

- Page 69 SYNTAX: ([bd,An],Xn) POINTER LIST POSTINDEXED STRUCTURE DATA ITEM POINTER Figure 2-12. Postindexed Indirect Addressing SYNTAX: ([bd,An,Xn],od) POINTER LIST STRUCTURE DATA ITEM POINTER Figure 2-13. Preindexed Indirect Addressing with Outer Displacement MOTOROLA MC68030 USER’S MANUAL 2-31...

-

Page 70: General Addressing Mode Summary

If the displacement is 16 bits or less, the address register indirect with displacement mode (d ,An) is used. When a 32- bit displacement is required, the address register indirect with index (bd,An,Xn) is used with the index register suppressed. 2-32 MC68030 USER’S MANUAL MOTOROLA... - Page 71 Data Organization and Addressing Capabilities It is useful to examine the derived addressing modes available to a programmer (without regard to the MC68030 effective addressing mode actually encoded) because the programmer need not be concerned about these decisions. The assembler can choose the more efficient addressing mode to encode.

- Page 72 Absolute address with two variable indexes. Subscripting: (An,Rn*scale) Address register pointer subscript. (disp,An,Rn*scale) Address register pointer subscript with constant displacement (or base address with subscript). (addr,Rn*scale) Absolute address with subscript. (addr,An,Rn*scale) Absolute address subscript with variable index. Program Relative: 2-34 MC68030 USER’S MANUAL MOTOROLA...

- Page 73 ([preindexed],disp) Memory pointer as base with displacement to data operand. ([postindexed],Rn) Memory pointer with variable index. ([postindexed],disp,Rn) Memory pointer with constant and variable index. ([postindexed],Rn*scale) Memory pointer subscripted. ([postindexed],disp,Rn*scale) Memory pointer subscripted with constant index. MOTOROLA MC68030 USER’S MANUAL 2-35...

-

Page 74: M68000 Family Addressing Compatibility

When S = 1 and M = 0, the interrupt stack pointer (ISP) is the active system stack pointer. This mode is the MC68030 default mode after reset and corresponds to the MC68000, MC68008, and MC68010 supervisor mode. The term supervisor stack pointer (SSP) refers to the master or interrupt stack pointers, depending on the state of the M bit. - Page 75 In long-word-organized memory, aligning the stack pointer on a long-word address signed significantly increases the efficiency of stacking exception frames, subroutine calls and returns, and other stacking operations. MOTOROLA MC68030 USER’S MANUAL 2-37...

-

Page 76: User Program Stacks

LOW MEMORY (FREE) TOP OF STACK BOTTOM OF STACK HIGH MEMORY To implement stack growth from low to high memory, use: (An)+ to push data on the stack, –An to pull data from the stack. 2-38 MC68030 USER’S MANUAL MOTOROLA... -

Page 77: Queues

To implement the queue as a circular buffer, the relevant address register should be checked and adjusted, if necessary, before performing the "put'' or "get'' operation. The address register is adjusted by subtracting the buffer length (in bytes) from the register. MOTOROLA MC68030 USER’S MANUAL 2-39... - Page 78 To implement the queue as a circular buffer, the "get'' or "put'' operation should be performed first, and then the relevant address register should be checkout and adjusted, if necessary. The address register is adjusted by adding the buffer length (in bytes) to the register contents. 2-40 MC68030 USER’S MANUAL MOTOROLA...

-

Page 79: Instruction Set Summary

3.1 INSTRUCTION FORMAT All MC68030 instructions consist of at least one word; some have as many as 11 words (see Figure 3–1). The first word of the instruction, called the operation word, specifies the length of the instruction and the operation to be performed. The remaining words, called extension words, further specify the instruction and operands. -

Page 80: Instruction Summary

The instructions form a set of tools to perform the following operations: Data Movement Bit Field Manipulation Integer Arithmetic Binary-Coded Decimal Arithmetic Logical Program Control Shift and Rotate System Control Bit Manipulation Multiprocessor Communications Each instruction type is described in detail in the following paragraphs MC68030 USER’S MANUAL MOTOROLA... -

Page 81: Format

= list of registers, for example D3 — D0 # 〈 data 〉 = immediate data; a literal integer {offset:width} = bit field selection label = assemble program label [m] = bit m of an operand [m:n] = bits m through n of operand MOTOROLA MC68030 USER’S MANUAL... -

Page 82: Data Movement Instructions

MOVE instructions, there are several special data movement instructions: move multiple registers (MOVEM), move peripheral data (MOVEP), move quick (MOVEQ), exchange registers (EXG), load effective address (LEA), push effective address (PEA), link stack (LINK), and unlink stack (UNLK). MC68030 USER’S MANUAL MOTOROLA... -

Page 83: Integer Arithmetic Instructions

A set of extended instructions provides multiprecision and mixed-size arithmetic. These instructions are add extended (ADDX), subtract extended (SUBX), sign extended (EXT), and negate binary with extend (NEGX). Refer to Table 3–2 for a summary of the integer arithmetic operations. MOTOROLA MC68030 USER’S MANUAL... -

Page 84: Logical Instructions

A similar set of immediate instructions (ANDI, ORI, and EORI) provide these logical operations with all sizes of immediate data. The TST instruction compares the operand with zero arithmetically, placing the result in the condition code register. Table 3–3 summarizes the logical operations. MC68030 USER’S MANUAL MOTOROLA... -

Page 85: Shift And Rotate Instructions

SWAP instruction exchanges the 16-bit halves of a register. Performance of shift/rotate instructions is enhanced so that use of the ROR and ROL instructions with a shift count of eight allows fast byte swapping. Table 3–4 is a summary of the shift and rotate operations. MOTOROLA MC68030 USER’S MANUAL... -

Page 86: Bit Manipulation Instructions

Register operands are 32 bits long, and memory operands are 8 bits long. In Table 3–5, the summary of the bit manipulation operations, Z refers to bit 2, the zero bit of the status register. MC68030 USER’S MANUAL MOTOROLA... -

Page 87: Bit Field Operations

8, 32 3.2.6 Bit Field Operations The MC68030 supports variable-length bit field operations on fields of up to 32 bits. The bit field insert (BFINS) instruction inserts a value into a bit field. Bit field extract unsigned (BFEXTU) and bit field extract signed (BFEXTS) extract a value from the field. Bit field find first one (BFFFO) finds the first bit that is set in a bit field. -

Page 88: Binary-Coded Decimal Instructions

16→8 #〈data〉 destination Dn,Dn,# 〈data〉 16→8 – X → destination SBCD Dn,Dn destination - source –(An),–(An) packed source → unpacked source UNPK –(An) 8→16 unpacked source + immediate data → #〈data〉 Dn,Dn,#〈data〉 8→16 unpacked destination 3-10 MC68030 USER’S MANUAL MOTOROLA... -

Page 89: Program Control Instructions

Greater than — Less than — Always true* — Equal — Higher — Minus — Overflow clear — Never true* — -Less or equal — Not equal — Overflow set *Not applicable to the Bcc instructions. MOTOROLA MC68030 USER’S MANUAL 3-11... -

Page 90: System Control Instructions

Condition Code Register immediate data Λ CCR → CCR ANDI #〈data〉,CCR immediate data ⊕ CCR → CCR EORI #〈data〉,CCR 〈ea〉,CCR source → CCR MOVE CCR → destination CCR,〈ea〉 immediate data V CCR → CCR #〈data〉,CCR 3-12 MC68030 USER’S MANUAL MOTOROLA... -

Page 91: Memory Management Unit Instructions

〈ea〉 save coprocessor state at 〈ea〉 cpSAVE none 〈ea〉 if cpcc true, then 1's → destination; else 0's → destination cpScc cpTRAPcc none none if cpc true, then TRAPcc exception #〈data〉 16, 32 MOTOROLA MC68030 USER’S MANUAL 3-13... -

Page 92: Integer Condition Codes

Cleared otherwise. C (carry) Set if a carry out of the most significant bit of the operand occurs for an addition. Also set if a borrow occurs in a subtraction. Cleared otherwise. 3-14 MC68030 USER’S MANUAL MOTOROLA... -

Page 93: Condition Code Computation

Z = Z Λ Rm Λ . . . Λ R0 ? V = Dm Λ Rm C = Dm V Rm ? V = Dm Λ Rm NEGX C = Dm V Rm Z = Z Λ Rm Λ . . . Λ R0 MOTOROLA MC68030 USER’S MANUAL 3-15... - Page 94 UB = Upper Bound Z = Rm Λ . . . Λ R0 Λ = Boolean AND Destination Operand — Most Significant Bit V = Boolean OR Destination Operand — Most Significant Bit Rm = NOT Rm 3-16 MC68030 USER’S MANUAL MOTOROLA...

-

Page 95: Conditional Tests

N •V •Z + N • V •Z Greater Than 1110 Z + N •V + N • V Less or Equal 1111 • = Boolean AND + = Boolean OR N = Boolean NOT N *Not available for the Bcc instruction. MOTOROLA MC68030 USER’S MANUAL 3-17... -

Page 96: Instruction Set Summary

Instruction Set Summary 3.4 INSTRUCTION SET SUMMARY Table 3–14 provides a alphabetized listing of the MC68030 instruction set listed by opcode, operation, and syntax. Table 3–14 use notational conventions for the operands, the subfields and qualifiers, and the operations performed by the instructions. In the syntax descriptions, the left operand is the source operand, and the right operand is the destination operand. - Page 97 "else'' clause is present, the opera- tions after "else" are performed. If the condition is false and else is omitted, the instruction performs no operation. Refer to the Bcc instruction description as an example. MOTOROLA MC68030 USER’S MANUAL 3-19...

- Page 98 BSET BSET Dn,〈ea〉BSET #〈data〉,〈ea〉 1 → 〈bit number〉 of Destination SP – 4 → SP; PC → (SP); PC + d → PC BSR (label〉 –(〈bit number〉 of Destination) → Z; BTST BTST Dn,〈ea〉BTST #〈data〉,〈ea〉 3-20 MC68030 USER’S MANUAL MOTOROLA...

-

Page 99: Scanpc

DIVU.W 〈ea〉,Dn32/16 → 16r:16q DIVU DIVU.L 〈ea〉,Dq 32/32 → 32q DIVUL DIVU.L 〈ea〉,Dr:Dq 64/32 → 32r:32q DIVUL.L 〈ea〉,Dr:Dq32/32 → 32r:32q Source ⊕ Destination → Destination EOR Dn,〈ea〉 Immediate Data ⊕ Destination → Destination EORI EORI #〈data〉,〈ea〉 MOTOROLA MC68030 USER’S MANUAL 3-21... - Page 100 Rc → Rn or Rn → Rc MOVEC Rn,Rc else TRAP Registers → Destination MOVEM MOVEM register list,〈ea〉MOVEM Source → Registers 〈ea〉,register list Source → Destination MOVEP MOVEP Dx,(d,Ay) MOVEP (d,Ay),Dx Immediate Data → Destination MOVEQ MOVEQ #〈data〉,Dn 3-22 MC68030 USER’S MANUAL MOTOROLA...

- Page 101 If supervisor state RESET then Assert RSTO Line else TRAP Destination Rotated by 〈count〉 → Destination ROL,ROR Rx,Dy #〈data〉,Dy 〈ea〉 Destination Rotated with X by 〈count〉 → Destination ROXL, ROXd Dx,Dy ROXR ROXd #〈data〉,Dy 〈ea〉 ROXd MOTOROLA MC68030 USER’S MANUAL 3-23...

- Page 102 ( –). 4. A list of any combination of the three floating-point system control registers (FPCR, FPSR, and FPIAR) with indvidual register names separated by a slash (/). 5. Where d is direction, L or R. 3-24 MC68030 USER’S MANUAL MOTOROLA...

-

Page 103: Instruction Examples

INC_LOOP MOVE.W D0,D1 make a copy of it ADDQ.W #1,D1 and increment it CAS.W D0,D1,SYS_CNTR if countr value is still the same, update it INC_LOOP if not, try again MOTOROLA MC68030 USER’S MANUAL 3-25... - Page 104 IF NOT, TRY AGAIN BEFORE INSERTING AN ELEMENT: ENTRY ENTRY ENTRY + NEXT + NEXT + NEXT HEAD AFTER INSERTING AN ELEMENT: ENTRY ENTRY ENTRY + NEXT + NEXT + NEXT HEAD Figure 3-2. Linked List Insertion 3-26 MC68030 USER’S MANUAL MOTOROLA...

- Page 105 (MAY BE NULL) BEFORE DELETING AN ELEMENT: ENTRY ENTRY ENTRY + NEXT + NEXT + NEXT HEAD AFTER DELETING AN ELEMENT: ENTRY ENTRY ENTRY + NEXT + NEXT + NEXT HEAD Figure 3-3. Linked List Deletion MOTOROLA MC68030 USER’S MANUAL 3-27...

- Page 106 D1 to the LIST-GET pointer and to the address in register A2. If the pointers have not been updated, the CAS2 instruction loads the address in D2 into the LIST_GET pointer and zero into the address in register A2. 3-28 MC68030 USER’S MANUAL MOTOROLA...

- Page 107 DDEMPTY after moving a zero pointer value into D2. This instruction checks the addresses in LIST_PUT and LIST_GET to verify that no other routine has inserted another element or deleted the last element. Then the instruction moves zero into both pointers, and the list is empty. MOTOROLA MC68030 USER’S MANUAL 3-29...

-

Page 108: Nested Subroutine Calls

When the operand of the instruction is the address of the link address at the bottom of a stack frame, the effect is to remove the stack frame from the stack and from the linked list. 3-30 MC68030 USER’S MANUAL MOTOROLA... -

Page 109: Bit Field Operations

Instruction Set Summary 3.5.3 Bit Field Operations One data type provided by the MC68030 is the bit field, consisting of as many as 32 consecutive bits. A bit field is defined by an offset from an effective address and a width value. -

Page 110: Pipeline Synchronization With The Nop Instruction

All previous integer instructions and floating-point external operand accesses complete execution before the NOP begins. The NOP instruction does not synchronize the FPU pipeline; floating-point instructions with floating-point register operand destinations can be executing when the NOP begins. MOTOROLA MC68030 USER’S MANUAL 3-32... -

Page 111: Processing States

SECTION 4 PROCESSING STATES This section describes the processing states of the MC68030. It describes the functions of the bits in the supervisor portion of the status register and the actions taken by the processor in response to exception conditions. -

Page 112: Privilege Levels

The MC68030 provides two supervisor stacks, master and interrupt; the M bit of the status register selects which of the two is active. When the M bit is set to one, supervisor stack pointer references (either implicit or by specifying address register A7) access the master stack pointer (MSP). -

Page 113: User Privilege Level

Processing States When the M bit is clear, the MC68030 is in the interrupt mode of the supervisor privilege level, and operation is the same as in the MC68000, MC68008, and MC68010 supervisor mode. (The processor is in this mode after a reset operation.) All supervisor stack pointer references access the interrupt stack pointer (ISP) in this mode. -

Page 114: Changing Privilege Level

S bit of the restored status register. If the frame on top of the stack was generated by a bus fault (bus error or address error exception), the RTE instruction restores the entire saved processor state from the stack. MC68030 USER’S MANUAL MOTOROLA... -

Page 115: Address Space Types

Table 4-1 lists the types of accesses defined for the MC68030 and the corresponding values of function codes FC0–FC2. Table 4-1. Address Space Encodings... -

Page 116: Exception Processing

Details of exception processing are provided in Section 8 Exception Processing , and Table 8-1 lists the exception vector assignments. MC68030 USER’S MANUAL MOTOROLA... -

Page 117: Exception Stack Frame

Figure 4-1. Refer to Section 8 Exception Processing for a complete list of exception stack frames. STATUS REGISTER PROGRAM COUNTER FORMAT VECTOR OFFSET ADDITIONAL PROCESSOR STATE INFORMATION (2, 6, 12, OR 42 WORDS, IF NEEDED) Figure 4-1. General Exception Stack Frame MOTOROLA MC68030 USER’S MANUAL... -

Page 118: Signal Description

RESET BUS EXCEPTION HALT MC68EC030 CONTROL BERR SYNCHRONOUS ASYNCHRONOUS STERM BUS CONTROL BUS CONTROL DBEN REFILL EMULATOR DSACK0 STATUS SUPPORT DSACK1 CDIS CIIN CIOUT CACHE (10) CBREQ CONTROL CBACK GND (14) Figure 5-1. Functional Signal Groups MOTOROLA MC68030 USER’S MANUAL... -

Page 119: Signal Index

(high or low) that they represent. 5.1 SIGNAL INDEX The input and output signals for the MC68030 are listed in Table 5-1. Both the names and mnemonics are shown along with brief signal descriptions. For more detail on each signal, refer to the paragraph in this section named for the signal and the reference in that paragraph to a description of the related operations. - Page 120 Termination may be latched on the next falling clock edge. Cache Inhibit In CIIN Prevents data from being loaded into the MC68030 instruction and data caches. Cache Inhibit Out CIOUT Reflects the CI bit in ATC entries or TTx register; indicates that external...

-

Page 121: Function Code Signals (Fc0-Fc2)

These three-state bidirectional signals provide the general-purpose data path between the MC68030 and all other devices. The data bus can transfer 8, 16, 24, or 32 bits of data per bus cycle. D31 is the most significant bit of the data bus. Refer to 7.1.4 Data Bus for more information on the data bus and its relationship to bus operation. -

Page 122: Bus Control Signals

Signal Description 5.6 BUS CONTROL SIGNALS The following signals control synchronous bus transfer operations for the MC68030. 5.6.1 Operand Cycle Start (OCS) This output signal indicates the beginning of the first external bus cycle for an instruction prefetch or a data operand transfer. OCS is not asserted for subsequent cycles that are performed due to dynamic bus sizing or operand misalignment. -

Page 123: Data Strobe (Ds)

During a read cycle, this three-state output indicates that an external device should place valid data on the data bus. During a write cycle, the data strobe indicates that the MC68030 has placed valid data on the bus. During two-clock synchronous write cycles, the MC68030 does not assert DS. -

Page 124: Cache Control Signals

The following signals relate to the on-chip caches. 5.7.1 Cache Inhibit Input (CIIN) This input signal prevents data from being loaded into the MC68030 instruction and data caches. It is a synchronous input signal and is interpreted on a bus-cycle-by-bus-cycle basis. -

Page 125: Interrupt Control Signals

Also, refer to 7.4.1 Interrupt Acknowledge Bus Cycles for bus information related to interrupts. 5.8.3 Autovector (AVEC) This input signal indicates that the MC68030 should generate an automatic vector during an interrupt acknowledge cycle. Refer to 7.4.1.2 Autovector Interrupt Acknowledge Cycle for more information about automatic vectors. -

Page 126: Bus Grant (Bg)

Signal Description 5.9.2 Bus Grant (BG) This output indicates that the MC68030 will release ownership of the bus master when the current processor bus cycle completes. Refer to 7.7.2 Bus Grant for more information. 5.9.3 Bus Grant Acknowledge (BGACK) This input indicates that an external device has become the bus master. Refer to 7.7.3 Bus Grant Acknowledge for more information. -

Page 127: Emulator Support Signals

ATC entries become available again when MMUDIS is negated. 5.11.3 Pipeline Refill (REFILL) The pipeline refill signal indicates that the MC68030 is beginning to refill the internal instruction pipeline. Refer to Section 12 Applications Information for a description of the use of this signal by an emulator. -

Page 128: Clock (Clk)

Signal Description 5.12 CLOCK (CLK) The clock signal is the clock input to the MC68030. It is a TTL-compatible signal. Refer to Section 12 Applications Information for suggestions on clock generation. 5.13 POWER SUPPLY CONNECTIONS The MC68030 requires connection to a V power supply, positive with respect to ground. - Page 129 Bus Error BERR Input — Cache Disable CDIS Input — MMU Disable MMUDIS Input — Pipeline Refill REFILL Output Microsequencer Status STATUS Output Clock Input — — Power Supply Input — — Ground Input — — 5-12 MC68030 USER’S MANUAL MOTOROLA...

-

Page 130: On-Chip Cache Memories

(in systems with more than one bus master, such as a processor and a DMA device) without degrading the performance of the MC68030. An increase in instruction throughput results when instruction words and data required by a program are available in the on-chip caches and the time required to access them on the external bus is eliminated. - Page 131 On-Chip Cache Memories Figure 6-1. Internal Caches and the MC68030 MC68030 USER’S MANUAL MOTOROLA...

-

Page 132: On-Chip Cache Organization And Operation

Therefore, the state of the corresponding CI bits in the MMU are also ignored. The MMU is used to validate all accesses that require external bus cycles; an address translation must be available and valid, protections are checked, and the CIOUT signal is asserted appropriately. MOTOROLA MC68030 USER’S MANUAL... -

Page 133: Instruction Cache

Dynamic RAMs supporting fast access modes (page, nibble, or static column) are easily employed to support the MC68030 burst mode. MC68030 USER’S MANUAL... -

Page 134: Registers

A1 is supplied to the instruction pipe. When the address and function code bits do not match or the requested entry is not valid, a miss occurs. The bus controller initiates a long-word prefetch operation for the required MOTOROLA MC68030 USER’S MANUAL... -

Page 135: Data Cache

The data cache on the MC68030 is a writethrough cache. When a hit occurs on a write cycle, the data is written both to the cache and to external memory (provided the MMU validates the access), regardless of the operand size and even if the cache is frozen. - Page 136 Thus, an aligned long-word data write may replace a previously valid entry; whereas, a misaligned data write or a write of data that is not long word may invalidate a previously valid entry or entries. MOTOROLA MC68030 USER’S MANUAL...

-

Page 137: Write Allocation

B) b8-b9 b8'-b9' B) b8-b9 b8'-b9' USER LONG-WORD WRITE OF b6'-b9' to $00001056 (TAG MATCH, LONG-WORD DATA, MISALIGNED, b6-b7 RESULT IN A CACHE MISS, b8-b9 RESULT IN A CACHE HIT) Figure 6-4. No-Write-Allocation and Write-Allocation Mode Examples MC68030 USER’S MANUAL MOTOROLA... -

Page 138: Read-Modify-Write Accesses

For example, a 32-bit port must always supply 32 bits, even for 8- and 16-bit transfers; a 16- bit port must supply 16 bits, even for 8-bit transfers. The MC68030 assumes that a 32-bit termination signal for the bus cycle indicates availability of 32 valid data bits, even if only 16 or 8 bits are requested. - Page 139 8-bit port. Provided the data item is cachable, this operation results in four bus cycles. The first cycle requested by the MC68030 reads a byte from address $03. The 8-bit DSACKx response causes the MC68030 to fetch the remainder of the long word starting at address $00.

- Page 140 If the bus error occurs on a read cycle for a portion of the required operand (not the remaining bytes of the cache entry) to be loaded into the data cache, the processor immediately takes a bus error exception. If MOTOROLA MC68030 USER’S MANUAL 6-11...

- Page 141 Operation . The device must also assert CBACK (at the same time as STERM) at the end of the cycle in which the MC68030 asserts CBREQ. CBACK causes the processor to continue driving the address and bus control signals and to latch a new data value for the next cache entry at the completion of each subsequent cycle (as defined by STERM), for a total of up to four cycles (until four long words have been read).

-

Page 142: Burst Mode Filling

A2 and A3 may have to be incremented externally to select the long words in the proper order for loading into the cache. The MC68030 holds the entire address bus constant for the duration of the burst cycle. Figure 6-12 shows an example of this address wraparound. The initial cycle is a long-word access from address $6. - Page 143 However, the data is not loaded into its corresponding cache. In addition, the MC68030 negates CBREQ, and the burst operation is aborted. If a portion of the requested operand remains to be read (due to misalignment), a second read cycle is initiated at the appropriate address with CBREQ negated.

-

Page 144: Cache Reset

The WA bit in the CACR is also cleared. 6.3 CACHE CONTROL Only the MC68030 cache control circuitry can directly access the cache arrays, but the supervisor program can set bits in the CACR to exercise control over cache operations. The supervisor also has access to the cache address register (CAAR), which contains the address for a cache entry to be cleared. -

Page 145: Write Allocate

MOVEC instruction loads a one into the CED bit of the CACR, regardless of the states of the ED and FD bits. The CED bit is always read as a zero. 6-16 MC68030 USER’S MANUAL MOTOROLA... -

Page 146: Freeze Data Cache

The processor clears only the specified long word by clearing the valid bit for the entry at the time a MOVEC instruction loads a one into the CEI bit of the CACR, regardless of the states of the EI and FI bits. The CEI bit is always read as a zero. MOTOROLA MC68030 USER’S MANUAL 6-17... -

Page 147: Freeze Instruction Cache

Although only the index field is used currently, all 32 bits of the register are implemented and are reserved for use by Motorola. CACHE FUNCTION ADDRESS INDEX Figure 6-15. Cache Address Register 6-18 MC68030 USER’S MANUAL MOTOROLA... -

Page 148: Bus Operation

The MC68030 contains an address bus that specifies the address for the transfer and a data bus that transfers the data. Control signals indicate the beginning of the cycle, the address space and the size of the transfer, and the type of cycle. - Page 149 The bus and control input signals used for asynchronous operation are internally synchronized to the MC68030 clock, introducing a delay. This delay is the time period required for the MC68030 to sample an asynchronous input signal, synchronize the input to the internal clocks of the processor, and determine whether it is high or low.

-

Page 150: Bus Control Signals

The external cycle start (ECS) signal is the earliest indication that the processor is initiating a bus cycle. The MC68030 initiates a bus cycle by driving the address, size, function code, read/write, and cache inhibit-out outputs and by asserting ECS. However, if the processor... -

Page 151: Address Bus

Bus Operation for user definition and two are reserved by Motorola for future use. The function code signals are valid while AS is asserted. At the beginning of a bus cycle, the size signals (SIZ0 and SIZ1) are driven along with ECS and the FC0–FC2. -

Page 152: Data Bus

These signals also indicate to the processor the size of the port for the bus cycle just completed, as shown in Table 7-1. Refer to 7.3.1 Asynchronous Read Cycle for timing relationships of DSACK0 and DSACK1. MOTOROLA MC68030 USER’S MANUAL... -

Page 153: Data Transfer Mechanism

DSACKx or STERM signals. Finally, the autovector (AVEC) signal can be used to terminate interrupt acknowledge cycles, indicating that the MC68030 should internally generate a vector number to locate an interrupt handler routine. AVEC is ignored during all other bus cycles. - Page 154 7.2.2 Misaligned Operands for the case of a word or byte address.) If the port responds that it is 32 bits wide, the MC68030 latches all 32 bits of data and continues with the next operation. If the port responds that it is 16 bits wide, the MC68030 latches the 16 bits of valid data and runs another bus cycle to obtain the other 16 bits.

- Page 155 BYTE OPERAND Figure 7-3. Internal Operand Representation Figure 7-4 shows the required organization of data ports on the MC68030 bus for 8, 16, and 32-bit devices. The four bytes shown in Figure 7-4 are connected through the internal data bus and data multiplexer to the external data bus. This path is the means through which the MC68030 supports dynamic bus sizing and operand misalignment.

- Page 156 (long word or word) so that the internal caches operate correctly. (For cachable accesses, the MC68030 assumes that all portions of the data bus for a given port size are valid.) This same table applies to noncachable read cycles except that the bytes labeled PRn and Nn are not required and can be replaced by “don't cares”.

- Page 157 (Table did not make it over in the conversion from Word) Table 7-5 lists the combinations of SIZ0, SIZ1, A0, and A1 and the corresponding pattern of the data transfer for write cycles from the internal multiplexer of the MC68030 to the external data bus.

- Page 158 Bus Operation Table 7-5. MC68030 Internal to External Data Bus. (Table did not make it over in the conversion from Word) LONG WORD OPERAND DATA BUS WORD MEMORY MC68EC030 MEMORY CONTROL SIZ1 SIZ0 DSACK1 DSACK0 Figure 7-5. Example of Long-Word Transfer to Word Port MOTOROLA MC68030 USER’S MANUAL...

- Page 159 Each bus cycle transfers a single byte. The size signals for the first cycle specify two bytes; for the second cycle, one byte. Figure 7-8 shows the associated bus transfer signal timing. 7-12 MC68030 USER’S MANUAL MOTOROLA...

-

Page 160: Misaligned Operands

MC68008, and MC68010 implementations allow long-word transfers on odd-word boundaries but force exceptions if word or long-word operand transfers are attempted at odd-byte addresses. Although the MC68030 does not enforce any alignment restrictions for data operands (including PC relative data addresses), some performance degradation occurs when additional bus cycles are required for long-word or word operands that are misaligned. - Page 161 Bus Operation A31-A2 FC2-FC0 SIZ1 SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BYTE WRITE BYTE WRITE WORD OPERAND WRITE Figure 7-8. Word Operand Write Timing (8-Bit Data Port) 7-14 MC68030 USER’S MANUAL MOTOROLA...

- Page 162 Figure 7-14 shows the equivalent operation for a cachable data read cycle. LONG WORD OPERAND DATA BUS WORD MEMORY MC68EC030 MEMORY CONTROL DSACK1 DSACK0 SIZ1 SIZ0 Figure 7-9. Misaligned Long-Word Transfer to Word Port Example MOTOROLA MC68030 USER’S MANUAL 7-15...

- Page 163 Bus Operation A31-A2 FC2-FC0 SIZ1 SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BYTE WRITE BYTE WRITE WORD WRITE LONG WORD OPERAND WRITE Figure 7-10. Misaligned Long-Word Transfer to Word Port 7-16 MC68030 USER’S MANUAL MOTOROLA...

- Page 164 DSACK0 SIZ1 SIZ0 Figure 7-11. Misaligned Cachable Long-Word Transfer from Word Port Example WORD OPERAND DATA BUS MEMORY CONTROL WORD MEMORY MC68030 SIZ1 SIZ0 DSACK1 DSACK0 Figure 7-12. Misaligned Word Transfer to Word Port Example MOTOROLA MC68030 USER’S MANUAL 7-17...

- Page 165 Bus Operation A31-A2 FC2-FC0 SIZ1 SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 WORD WRITE BYTE WRITE WORD OPERAND WRITE TO A1/A0=01 Figure 7-13. Misaligned Word Transfer to Word Port 7-18 MC68030 USER’S MANUAL MOTOROLA...

-

Page 166: Effects Of Dynamic Bus Sizing And Operand Misalignment

*Instruction prefetches are always two words from a long-word boundary. This table shows that bus cycle throughput is significantly affected by port size and alignment. The MC68030 system designer and programmer should be aware of and account for these effects, particularly in time-critical applications. - Page 167 Refer to Section 11 Instruction Execution Timing for a complete description of the cache holding register and pipeline operation. 7-20 MC68030 USER’S MANUAL MOTOROLA...

- Page 168 Bus Operation A31-A2 FC2-FC0 SIZ1 SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BYTE WRITE 3 - BYTE WRITE LONG WORD OPERAND WRITE Figure 7-16. Misaligned Write Cycles to Long-Word Port MOTOROLA MC68030 USER’S MANUAL 7-21...

-

Page 169: Address, Size, And Data Bus Relationships

A dash (—) implies that the byte enable signal does not apply. The MC68030 always drives all sections of the data bus because, at the start of a write cycle, the bus controller does not know the port size. The byte enable signals in the table apply only to read operations that are not to be internally cached and to write operations. - Page 170 Long Word — The table shows that the MC68030 transfers the number of bytes specified by the size signals to or from the specified address unless the operand is misaligned or the number of bytes is greater than the port width. In these cases, the device transfers the greatest number of bytes possible for the port.

-

Page 171: Mc68030 Versus Mc68020 Dynamic Bus Sizing

Bus Operation 7.2.5 MC68030 versus MC68020 Dynamic Bus Sizing The MC68030 supports the dynamic bus sizing mechanism of the MC68020 for asynchronous bus cycles (terminated with DSACKx) with two restrictions. First, for a cachable access within the boundaries of an aligned long word, the port size must be consistent throughout the transfer of each long word. -

Page 172: Cache Interactions

The organization and requirements of the on-chip instruction and data caches affect the interpretation of the DSACKx and STERM signals. Since the MC68030 attempts to load all data operands and instructions that are cachable into the on-chip caches, the bus may operate differently when caching is enabled. - Page 173 NOTE: These select lines can be combined with the address decode circuitry or all can be generated within the same programmed array logic unit. Figure 7-18. Byte Data Select Generation for 16- and 32-Bit Ports 7-26 MC68030 USER’S MANUAL MOTOROLA...

-

Page 174: Asynchronous Operation

Bus Operation 7.2.8 Asynchronous Operation The MC68030 bus may be used in an asynchonous manner. In that case, the external devices connected to the bus can operate at clock frequencies different from the clock for the MC68030. Asynchronous operation requires using only the handshake line (AS, DS, DSACK1, DSACK0, BERR, and HALT) to control data transfers. -

Page 175: Synchronous Operation With Dsackx

The devices that use these cycles must synchronize the responses to the MC68030 clock to be synchronous. Since they terminate bus cycles with the DSACKx signals, the dynamic bus sizing capabilities of the MC68030 are available. In addition, the minimum cycle time for these cycles is also three clocks. -

Page 176: Synchronous Operation With Sterm

(parameter #27A) prior to the falling clock edge one clock cycle after DSACKx is recognized. This setup time is critical, and the MC68030 may exhibit erratic behavior if it is violated. When operating synchronously, the data-in setup and hold times for synchronous cycles may be used instead of the timing requirements for data relative to the DS signal. -

Page 177: Data Transfer Cycles

AS signal. If STERM is asserted and no cycle is in progress (even if the cycle has begun, ECS is asserted and then the cycle is aborted), STERM is ignored by the MC68030. Similarly, CBACK can be asserted independently of the assertion of CBREQ. If a cache burst is not requested, the assertion of CBACK is ignored. -

Page 178: Asynchronous Read Cycle

During a read cycle, the processor receives data from a memory, coprocessor, or peripheral device. If the instruction specifies a long-word operation, the MC68030 attempts to read four bytes at once. For a word operation, it attempts to read two bytes at once, and for a byte operation, one byte. - Page 179 1)SAMPLE CACHE INHIBIT IN (CIIN) 2) LATCH DATA 3) NEGATE AS AND DS 4) NEGATE DBEN TERMINATE CYCLE 1) REMOVE DATA FROM D31-D0 2) NEGATE DSACK START NEXT CYCLE Figure 7-20. Asynchronous Byte Read Cycle Flowchart 7-32 MC68030 USER’S MANUAL MOTOROLA...

- Page 180 Bus Operation A31-A2 FC2-FC0 SIZ1 WORD BYTE SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 WORD READ BYTE READ BYTE READ Figure 7-21. Asynchronous Byte and Word Read Cycles — 32-Bit Port MOTOROLA MC68030 USER’S MANUAL 7-33...

- Page 181 BYTE SIZ0 CIOUT DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BYTE READ BYTE READ BYTE READ BYTE READ LONG WORD OPERAND READ FROM 8-BIT PORT Figure 7-22. Long-Word Read — 8-Bit Port with CIOUT Asserted MOTOROLA MC68030 USER’S MANUAL 7-35...

- Page 182 SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 WORD READ WORD READ LONG WORD READ FROM 32- BIT PORT LONG WORD OPERAND READ FROM 16-BIT PORT Figure 7-23. Long-Word Read — 16-Bit and 32-Bit Port 7-36 MC68030 USER’S MANUAL MOTOROLA...

- Page 183 AS or DS (whichever it detects first). The device must remove its data and negate DSACKx within approximately one clock period after sensing the negation of AS or DS. DSACKx signals that remain asserted beyond this limit may be prematurely detected for the next bus cycle. MOTOROLA MC68030 USER’S MANUAL 7-37...

-

Page 184: Asynchronous Write Cycle

3) ASSERT DATA TRANSFER AND SIZE TERMINATE OUTPUT TRANSFER ACKNOWLEDGE (DSACKx) 1) NEGATE AS AND DS 2) REMOVE DATA FROM D31-D0 TERMINATE CYCLE 3) NEGATE DBEN 1) NEGATE DSACKx START NEXT CYCLE Figure 7-24. Asynchronous Write Cycle Flowchart 7-38 MC68030 USER’S MANUAL MOTOROLA... - Page 185 FC0–FC2. The function codes select the address space for the cycle. The processor drives R/W low for a write cycle. SIZ0–SIZ1 become valid, indicating the number of bytes to be transferred. CIOUT also becomes valid, indicating MOTOROLA MC68030 USER’S MANUAL 7-39...

- Page 186 Bus Operation the state of the MMU CI bit in the address translation descriptor or in the appropriate TTx register. 7-40 MC68030 USER’S MANUAL MOTOROLA...

- Page 187 Bus Operation A31-A2 FC2-FC0 SIZ1 BYTE WORD SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 WORD WRITE BYTE WRITE BYTE WRITE Figure 7-26. Asynchronous Byte and Word Write Cycles — 32-Bit Port MOTOROLA MC68030 USER’S MANUAL 7-41...

- Page 188 LONG WORD 3-BYTE WORD BYTE SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BYTE WRITE BYTE WRITE BYTE WRITE BYTE WRITE LONG WORD OPERAND READ TO 8-BIT PORT Figure 7-27. Long-Word Operand Write — 8-Bit Port 7-42 MC68030 USER’S MANUAL MOTOROLA...

- Page 189 LONG WORD WORD SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 WORD WRITE WORD WRITE LONG WORD WRITE TO 32-BIT PORT LONG WORD OPERAND WRITE TO 16-BIT PORT Figure 7-28. Long-Word Operand Write — 16-Bit Port MOTOROLA MC68030 USER’S MANUAL 7-43...

- Page 190 DS (whichever it detects first). The device must negate DSACKx within approximately one clock period after sensing the negation of AS or DS. DSACKx signals that remain asserted beyond this limit may be prematurely detected for the next bus cycle. 7-44 MC68030 USER’S MANUAL MOTOROLA...

-

Page 191: Asynchronous Read-Modify-Write Cycle

7.3.3 Asynchronous Read-Modify-Write Cycle The read-modify-write cycle performs a read, conditionally modifies the data in the arithmetic logic unit, and may write the data out to memory. In the MC68030 processor, this operation is indivisible, providing semaphore capabilities for multiprocessor systems. During the entire read-modify-write sequence, the MC68030 asserts the RMC signal to indicate that an indivisible operation is occurring. - Page 192 2) REMOVE DATA FROM D31-D0 WRITTEN, THEN GO TO 3) NEGATE DBEN TERMINATE CYCLE D ; ELSE GO TO E 1) NEGATE DSACKx UNLOCK BUS 1) NEGATE RMC START NEXT CYCLE Figure 7-29. Asynchronous Read-Modify-Write Cycle Flowchart 7-46 MC68030 USER’S MANUAL MOTOROLA...

- Page 193 If a write cycle is required, the R/W signal remains in the read mode until S6 to prevent bus conflicts with the preceding read portion of the cycle; the data bus is not driven until S8. MOTOROLA MC68030 USER’S MANUAL 7-47...

- Page 194 A31-A2 FC2-FC0 SIZ1 SIZ0 CIIN CIOUT DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BERR HALT INDIVISIBLE CYCLE NEXT CYCLE Figure 7-30. Asynchronous Byte Read-Modify-Write Cycle — 32-Bit Port (TAS Instruction with CIOUT or CIIN Asserted) 7-48 MC68030 USER’S MANUAL MOTOROLA...

- Page 195 SIZ0–SIZ1 and A0–A1 select the data bus sections. If it has not already done so, the device asserts DSACKx when it has successfully stored the data. State 10 The processor issues no new control signals during S10. MOTOROLA MC68030 USER’S MANUAL 7-49...

-

Page 196: Synchronous Read Cycle

DSACKx for three-clock accesses. Figure 7-31 is a flowchart of a synchronous long-word read cycle. Byte and word operations are similar. Figure 7-32 is a functional timing diagram of a synchronous long-word read cycle. 7-50 MC68030 USER’S MANUAL MOTOROLA... - Page 197 (i.e., four long words can be read in), CBREQ is asserted. In addition, the ECS (and OCS, if asserted) signal is negated during S1. MOTOROLA MC68030 USER’S MANUAL 7-51...

- Page 198 DBEN may prevent its use. At the beginning of S2, the processor samples the level of STERM. If STERM is recognized, the processor latches the incoming data at the end of S2. If the selected data is not to be cached for the 7-52 MC68030 USER’S MANUAL MOTOROLA...

-

Page 199: Synchronous Write Cycle

AS and the required assertion of STERM for any two-clock synchronous bus cycle. The system must qualify a memory write with the assertion of AS to ensure that the write is not aborted by internal conditions within the MC68030. MOTOROLA MC68030 USER’S MANUAL... - Page 200 One-half clock later in S1, the processor asserts AS, indicating that the address on the address bus is valid. The processor also asserts DBEN during S1, which may be used to enable the external data buffers. In addition, the ECS (and OCS, if asserted) signal is negated during S1. 7-54 MC68030 USER’S MANUAL MOTOROLA...

- Page 201 If the device does not assert STERM by the rising edge of S2, the processor inserts wait states until it is recognized. The processor asserts DS at the end of S2 if wait states are inserted. For zero-wait-state synchronous write cycles, DS is not asserted. MOTOROLA MC68030 USER’S MANUAL 7-55...

-

Page 202: Synchronous Read-Modify-Write Cycle

Although the operation is synchronous, the burst mode is never used during read-modify-write cycles. Figure 7-35 is a flowchart of the synchronous read-modify-write operation. Timing for the cycle is shown in Figure 7-36. 7-56 MC68030 USER’S MANUAL MOTOROLA... - Page 203 2) REMOVE DATA FROM D31–D0 OPERAND 3) NEGATE DBEN TERMINATE CYCLE WRITTEN, THEN GO TO D : ELSE GO TO E 1) NEGATE STERM UNLOCK BUS 1) NEGATE RMC START NEXT CYCLE Figure 7-35. Synchronous Read-Modify-Write Cycle Flowchart MOTOROLA MC68030 USER’S MANUAL 7-57...

- Page 204 The processor places a valid address on A0–A31 and valid function codes on FC0– FC2. The function codes select the address space for the operation. SIZ0–SIZ1 become valid in S0 to indicate the operand size. The processor drives R/W high for a read cycle 7-58 MC68030 USER’S MANUAL MOTOROLA...

- Page 205 S2, wait states are inserted after S2, and STERM is sampled on every rising edge thereafter until it is recognized. Once STERM is recognized, data is latched on the next falling edge of the clock (corresponding to the beginning of S3). MOTOROLA MC68030 USER’S MANUAL 7-59...

- Page 206 S6, the processor inserts wait states until it is recognized. The processor asserts DS at the end of S6 if wait states are inserted. Note that for zero-wait-state synchronous write cycles, DS is not asserted. 7-60 MC68030 USER’S MANUAL MOTOROLA...

-

Page 207: Burst Operation Cycles

The MC68030 provides a set of handshake control signals for the burst mode. When a miss occurs in one of the caches, the MC68030 initiates a bus cycle to obtain the required data or instruction stream fetch. If the data or instruction can be cached, the MC68030 attempts to fill a cache entry. - Page 208 CBREQ signal, and burst mode is only initiated if both of these signals are asserted for a synchronous cycle. If the MC68030 executes a full burst operation and fetches four long words, CBREQ is negated after STERM is asserted for the third cycle, indicating that the MC68030 only requests one more long word (the fourth cycle).

- Page 209 The processor also asserts DS during S1. CBREQ is also asserted, indicating that the MC68030 can perform a burst operation into one of its caches and can read in four long words. In addition, ECS (and OCS, if asserted) is negated during S1.

- Page 210 Figure 7-37. Burst Operation Flowchart — Four Long Words Transferred not to be cached, CIIN must be asserted at the same time as STERM. The assertion of CIIN also has the effect of aborting the burst operation. 7-64 MC68030 USER’S MANUAL MOTOROLA...

- Page 211 A2–A0 FC2-FC0 SIZ1–SIZ0 STERM CIIN CIOUT CBREQ CBACK b4–b7 b8–bB bC–bF bC–bF D31–D0 DBEN VALUE OF A3:A2 INCREMENTED BY THE SYSTEM HARDWARE Figure 7-38. Long-Word Operand Request from $07 with Burst Request and Wait Cycle MOTOROLA MC68030 USER’S MANUAL 7-65...

- Page 212 2. Continued assertion of CBACK causes data to be placed on D31–D0. 3. Negation of CBACK causes AS to be negated. Figure 7-39. Long-Word Operand Request from $07 with Burst Request — CBACK Negated Early 7-66 MC68030 USER’S MANUAL MOTOROLA...

- Page 213 A3–A1 FC2-FC0 SIZ1 SIZ0 STERM CBREQ CBACK b0–b3 b4–b7 b8–bB bC–bF D31–D0 bC–bF DBEN PREVIOUS CACHE BLOCK NEXT CACHE BLOCK - START BURST CYCLE Figure 7-40. Long-Word Operand Request from $0E — Burst Fill Deferred MOTOROLA MC68030 USER’S MANUAL 7-67...

- Page 214 CIOUT CBREQ CBACK b4-b7 D31–D0 DBEN BURST MODE ENDS, DATA NOT CACHED VALUE OF A3:A2 INCREMENTED BY THE SYSTEM HARDWARE Figure 7-41. Long-Word Operand Request from $07 with Burst Request — CBACK and CIIN Asserted 7-68 MC68030 USER’S MANUAL MOTOROLA...

- Page 215 The same hold times for STERM and data described for S3 apply here. State 6 This state is identical to S4 except that once STERM is recognized, the third long word of data for the burst is latched at the end of S6. MOTOROLA MC68030 USER’S MANUAL 7-69...

-

Page 216: Cpu Space Cycles

SIZ1, and FC0–FC2 valid throughout S9. The same hold times for data described for S3 apply here. Note that the address bus of the MC68030 remains driven to a constant value for the duration of a burst transfer operation (including the first transfer before burst mode is entered). -

Page 217: Interrupt Acknowledge Bus Cycles

The CPU space type is encoded on A16-A19 during a CPU space operation and indicates the function that the processor is performing. On the MC68030, three of the encodings are implemented as shown in Figure 7-42. All unused values are reserved by Motorola for future additional CPU space types. -

Page 218: Interrupt Acknowledge Cycle - Terminated Normally

Bus Operation 7.4.1.1 INTERRUPT ACKNOWLEDGE CYCLE — TERMINATED NORMALLY. When the MC68030 processes an interrupt exception, it performs an interrupt acknowledge cycle to obtain the number of the vector that contains the starting location of the interrupt service routine. Some interrupting devices have programmable vector registers that contain the interrupt vectors for the routines they use. -

Page 219: Autovector Interrupt Acknowledge Cycle

When AVEC is asserted instead of DSACK or STERM during an interrupt acknowledge cycle, the MC68030 ignores the state of the data bus and internally generates the vector number, the sum of the interrupt level plus 24 ($18). There are seven distinct autovectors that can be used, corresponding to the seven levels of interrupt available with signals IPL0–IPL2. - Page 220 DSACK1 DSACK0 DBEN D31-D24 VECTOR # FROM 8-BIT PORT VECTOR # FROM 16-BIT PORT D23-D16 VECTOR # FROM 32-BIT PORT D7-D0 IPL2-IPL0 IPEND INTERRUPT READ CYCLE WRITE STACK ACKNOWLEDGE Figure 7-44. Interrupt Acknowledge Cycle Timing 7-74 MC68030 USER’S MANUAL MOTOROLA...

- Page 221 Bus Operation A31-A4 INTERRUPT LEVEL A3-A1 FC2-FC0 SIZ1 SIZ0 DSACK1 DSACK0 DBEN D31-D0 IPL2-IPL0 AVEC INTERRUPT WRITE STACK ACKNOWLEDGE READ CYCLE AUTOVECTORED Figure 7-45. Autovector Operation Timing MOTOROLA MC68030 USER’S MANUAL 7-75...

-

Page 222: Spurious Interrupt Cycle

CpID of zero correspond to MMU instructions and are not generated by the MC68030 as a result of the coprocessor interface. These cycles can only be generated by the MOVES instruction. Refer to Section 10 Coprocessor Interface Description for further information. -

Page 223: Bus Exception Control Cycles

Figure 7-46. Breakpoint Operation Flow 7.5 BUS EXCEPTION CONTROL CYCLES The MC68030 bus architecture requires assertion of either DSACKx or STERM from an external device to signal that a bus cycle is complete. DSACKx, STERM, or AVEC is not asserted if: •... - Page 224 A15-A2 BREAKPOINT NUMBER A1-A0 CPU SPACE FC2-FC0 SIZ1 WORD SIZ0 DSACK1 DSACK0 DBEN D31-D24 D23-D16 D15-D8 D7-D0 BERR HALT BREAKPOINT FETCHED ACKNOWLEDGE INSTRUCTION READ CYCLE INSTRUCTION WORD EXECUTION FETCH Figure 7-47. Breakpoint Acknowledge Cycle Timing 7-78 MC68030 USER’S MANUAL MOTOROLA...

- Page 225 Another signal that is used for bus exception control is HALT. This signal can be asserted by an external device for debugging purposes to cause single bus cycle operation or (in combination with BERR) a retry of a bus cycle in error. MOTOROLA MC68030 USER’S MANUAL 7-79...

- Page 226 To properly control termination of a bus cycle for a retry or a bus error condition, DSACKx, BERR, and HALT can be asserted and negated with the rising edge of the MC68030 clock. This assures that when two signals are asserted simultaneously, the required setup time (#47A) and hold time (#47B) for both of them is met for the same falling edge of the processor clock.

- Page 227 Table 7-8 shows various combinations of control signal sequences and the resulting bus cycle terminations. To ensure predictable operation, BERR and HALT should be negated according to the specifications in MC68030EC/D, MC68030 Electrical Specifications . DSACKx, BERR, and HALT may be negated after AS. If DSACKx or BERR remain asserted into S2 of the next bus cycle, that cycle may be terminated prematurely.

- Page 228 HALT and BERR are asserted in lieu of, at the same time, or before STERM (case 5) or after STERM (case 6); BERR is negated at the same time or after STERM; HALT may be negated at the same time or after BERR. 7-82 MC68030 USER’S MANUAL MOTOROLA...

- Page 229 —Signal was asserted in previous state and remains asserted in this state — —State N+2 not part of bus cycle EXAMPLE A: A system uses a watchdog timer to terminate accesses to an unpopulated address space. The timer asserts BERR after timeout (case 3). MOTOROLA MC68030 USER’S MANUAL 7-83...

-

Page 230: Bus Errors

When the bus error signal is issued to terminate a bus cycle, the MC68030 may enter exception processing immediately following the bus cycle, or it may defer processing the exception. -

Page 231: External Caches

In the second case, where BERR is asserted after DSACKx is asserted, BERR must be asserted within specification #48 (refer to MC68030EC/D, MC68030 Electrical Specifications ) for purely asynchronous operation, or it must be asserted and remain stable during the sample window, defined by specifications #27A and #47B, around the next falling edge of the clock after DSACKx is recognized. - Page 232 BREAKPOINT NUMBER A1-A0 FC2-FC0 CPU SPACE SIZ1 WORD SIZ0 DSACK1 DSACK0 DBEN D31 -D24 D23-D16 D15-D8 D7-D0 BERR HALT BREAKPOINT FETCHED READ CYCLE ACKNOWLEDGE INSTRUCTION BUS ERROR EXECUTION ASSERTED Figure 7-49. Bus Error without DSACKx 7-86 MC68030 USER’S MANUAL MOTOROLA...

- Page 233 If the cycle is for a data fetch, the bus error exception is taken immediately. Refer to Section 11 Instruction Execution Timing for more information about pipeline operation. MOTOROLA MC68030 USER’S MANUAL 7-87...

- Page 234 Figure 7-53. If BERR is asserted again, the MC68030 then takes an exception. The MC68030 supports late bus errors during a burst fill operation; the timing is the same relative to STERM and the clock as for a late bus error in a normal synchronous cycle.

- Page 235 D31–D0 DBEN BERR HALT LATE BERR ENDS BURST; NO EXCEPTION TAKEN 0111 1000 1100 VALUE OF A3:A0 INCREMENTED BY THE SYSTEM HARDWARE Figure 7-52. Long-Word Operand Request — Late BERR on Third Access MOTOROLA MC68030 USER’S MANUAL 7-89...

- Page 236 BURST ABORTED RERUN CYCLE TO GET LAST INTERNAL BUS ERROR ASSERTED 3 BYTES OF OPERAND PROCESSING 0111 1000 VALUE OF A3:A0 INCREMENTED BY THE SYSTEM HARDWARE Figure 7-53. Long-Word Operand Request — BERR on Second Access 7-90 MC68030 USER’S MANUAL MOTOROLA...

-

Page 237: Retry Operation

Asserting BR along with BERR and HALT provides a relinquish and retry operation. The MC68030 does not relinquish the bus during a read-modify-write operation, except during the first read cycle. Any device that requires the processor to give up the bus and retry a bus cycle during a read-modify-write cycle must either assert BERR and BR only (HALT must not be included) or use the single wire arbitration method discussed in 7.7.4 Bus... - Page 238 Bus Operation A31-A0 FC2-FC0 SIZ1–SIZ0 DSACK1 DSACK0 DATA BUS NOT DRIVEN D31–D0 BERR HALT WRITE CYCLE RETRY SIGNALED HALT RETRY CYCLE Figure 7-54. Asynchronous Late Retry 7-92 MC68030 USER’S MANUAL MOTOROLA...

-

Page 239: Halt Operation

Figure 7-55. Synchronous Late Retry 7.5.3 Halt Operation When HALT is asserted and BERR is not asserted, the MC68030 halts external bus activity at the next bus cycle boundary. HALT by itself does not terminate a bus cycle. Negating and reasserting HALT in accordance with the correct timing requirements provides a single-step (bus cycle to bus cycle) operation. - Page 240 The single-step operation and the software trace capability allow the system debugger to trace single bus cycles, single instructions, or changes in program flow. These processor capabilities, along with a software debugging package, give complete debugging flexibility. 7-94 MC68030 USER’S MANUAL MOTOROLA...

- Page 241 Bus Operation A31-A0 FC2-FC0 SIZ1/SIZ0 DSACK1 DSACK0 DBEN D31-D0 BERR HALT BGACK READ HALT READ (ARBITRATION PERMITTED WHILE THE CONTROLLER IS HALTED) Figure 7-57. Halt Operation Timing 7-95 MC68030 USER’S MANUAL MOTOROLA...

-

Page 242: Double Bus Fault

Once bus mastership is returned to the MC68030, if HALT is still asserted, the address, function code, size, and read/write signals are again driven to their previous states. The processor does not service interrupt requests while it is halted, but it may assert the IPEND signal as appropriate. -

Page 243: Bus Synchronization

Since the MMU always checks the validity of write cycles before they proceed to the data cache and are executed externally, the MC68030 is guaranteed to write correct data to the cache. Thus, there is no danger in subsequent instructions using erroneous data from the cache before an external bus error signals an error. -

Page 244: Bus Arbitration

Figure 7-58. Bus Synchronization Example 7.7 BUS ARBITRATION The bus design of the MC68030 provides for a single bus master at any one time: either the processor or an external device. One or more of the external devices on the bus can have the capability of becoming bus master. - Page 245 • AS must be negated, indicating that no bus cycle is in progress, and the external device must ensure that all appropriate processor signals have been placed in the high-imped- ance state (by observing specification #7 in MC68030EC/D, MC68030 Electrical Spec- ifications ).

-

Page 246: Bus Request

BR is negated. This prevents unnecessary interference with ordinary processing if the arbitration circuitry inadvertently responds to noise or if an external device determines that it no longer requires use of the bus before it has been granted mastership. 7-100 MC68030 USER’S MANUAL MOTOROLA... -

Page 247: Bus Grant

During a read-modify-write cycle, the processor does not assert BG until the entire operation has completed. RMC is asserted to indicate 7-101 MC68030 USER’S MANUAL MOTOROLA... -

Page 248: Bus Grant Acknowledge

BG in this case. 7.7.4 Bus Arbitration Control The bus arbitration control unit in the MC68030 is implemented with a finite state machine. As discussed previously, all asynchronous inputs to the MC68030 are internally synchronized in a maximum of two cycles of the processor clock. - Page 249 The bus control signals (controlled by T) are driven by the processor, immediately following a state change, when bus mastership is returned to the MC68030. State 0, at the top center of the diagram, in which G and T are both negated, is the state of the bus arbiter while the processor is bus master.

- Page 250 (assertions of BR) that occur after the first read cycle of the read-modify-write sequence by not issuing bus grants (asserting BG). In some cases, however, it may be necessary to force the MC68030 to release the bus during an read-modify-write sequence. One way for an alternate bus master to force the MC68030 to release the bus applies only to the first read cycle of an read-modify-write sequence.

-

Page 251: Reset Operation

RESET negates, all control signals are driven to their inactive state, the data bus is in read mode, and the address bus is driven. After this, the first bus cycle for reset exception processing begins. 7-105 MC68030 USER’S MANUAL MOTOROLA... - Page 252 RESET should be asserted for at least 520 clock periods to ensure that the processor resets. Asserting RESET for 10 clock periods is sufficient for resetting the processor logic; the additional clock periods prevent a reset instruction from overlapping the external RESET signal. 7-106 MC68030 USER’S MANUAL MOTOROLA...

- Page 253 Figure 7- 65 shows the timing information for the reset instruction. 7-107 MC68030 USER’S MANUAL MOTOROLA...

- Page 254 Bus Operation A31-A0 FC2-FC0 SIZ1-SIZ0 DSACK1 DSACK0 DBEN D31-D0 HALT RESET RESUME NORMAL RESET INTERNAL READ OPERATION 512 CLOCKS Figure 7-65. Processor-Generated Reset Operation 7-108 MC68030 USER’S MANUAL MOTOROLA...