Infineon XMC7000 Manual

Hide thumbs

Also See for XMC7000:

- Manual (52 pages) ,

- Using manual (33 pages) ,

- Quick start manual (14 pages)

Table of Contents

Advertisement

Quick Links

AN234253

Clock configuration setup in XMC7000 MCU

family

About this document

Scope and purpose

This application note describes how to set up the various clock sources in XMC7000 family MCUs and provides

examples including configuring PLL/FLL and calibrating the ILO.

Intended audience

This document is intended for anyone using XMC7000 family MCUs.

Associated part family

XMC7000 family of

XMC™ industrial microcontrollers.

Application note

Please read the sections "Important notice" and "Warnings" at the end of this document

002-34253 Rev. *C

www.infineon.com

2023-11-08

Advertisement

Table of Contents

Summary of Contents for Infineon XMC7000

-

Page 1: About This Document

About this document Scope and purpose This application note describes how to set up the various clock sources in XMC7000 family MCUs and provides examples including configuring PLL/FLL and calibrating the ILO. Intended audience This document is intended for anyone using XMC7000 family MCUs. -

Page 2: Table Of Contents

Table of contents About this document ........................1 Table of contents ..........................2 Introduction .......................... 4 Clock system for XMC7000 family MCUs ..................5 Overview ..............................5 Clock resources ............................5 Clock system functions ........................... 6 Basic clock system settings ........................12 Configuring the clock resources .................... - Page 3 Clock configuration setup in XMC7000 MCU family Table of contents 6.2.2 Use case ............................35 6.2.3 Configuration ........................... 35 6.2.3.1 Sample code for initial configuration of clock calibration counter with ILO0 and ECO... 36 CSV diagram and relationship of monitored clock and reference clock ..........37 Glossary ............................

-

Page 4: Introduction

(PLL) and frequency-locked loop (FLL) to generate clocks that operate the internal circuit at a high speed. XMC7000 family also supports a function to monitor the clock operation and to measure the clock difference of each clock with reference to a known clock. -

Page 5: Clock System For Xmc7000 Family Mcus

Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Clock system for XMC7000 family MCUs Overview The clock system in this series of MCUs is divided into two blocks. One selects the clock resources (such as external oscillator and internal oscillator) and multiplies the clock (using FLL and PLL). -

Page 6: Clock System Functions

Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Clock system functions Figure 2 shows the details of the clock selection and multiplier block. This block generates root frequency clocks CLK_HF0 to CLK_HF7 from the clock resources. This block has the capability to select one of the supported clock resources –... - Page 7 Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Domain/block Description Active domain Region of operation only in Active power mode DeepSleep Region of operation in Active and DeepSleep power modes domain Hibernate domain Region of operation in the All Power mode ECO prescaler Divides the ECO and creates a clock that can be used with the CLK_LF clock.

- Page 8 Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Figure 3 shows the distribution of CLK_HF0. CLK_HF0 is the root clock for the CPU subsystem (CPUSS) and peripheral clock dividers. For more details on Figure 3, see the XMC7000 MCU family architecture reference manual and the datasheet.

- Page 9 Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Clock input Description CLK_MEM Clock input to the CPUSS of Fast Infrastructure, Ethernet, and Serial Memory Interface (SMIF) CLK_PERI Clock source for CLK_GR and peripheral clock divider CLK_SLOW Clock input to the CPUSS of Cortex®-M0+ and Slow Infrastructure, SDHC, and SMIF...

- Page 10 Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Figure 5 shows the distribution of CLK_HF1. CLK_HF1 is a clock source for CLK_FAST_0 and CLK_FAST_1. The clock distribution of CLK_HF1 is shown in Figure 5. CLK_FAST_0 and CLK_FAST_1 are the input sources for the CM7_0 and CM7_1 respectively.

- Page 11 Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Figure 7 shows details of peripheral clock divider #1. Peripheral clock divider #1 has many peripheral clock dividers to generate PCLK. See the datasheet for the number of each divider. The output of any of these dividers can be routed to any peripheral. Note that dividers already in use cannot be used for other peripherals or channels.

-

Page 12: Basic Clock System Settings

Clock configuration setup in XMC7000 MCU family Clock system for XMC7000 family MCUs Basic clock system settings This section displays the configuration of the clock system in the Device Configurator of ModusToolbox™ software. You can configure the clock system according to your system in the Device Configurator as follows:... -

Page 13: Configuring The Clock Resources

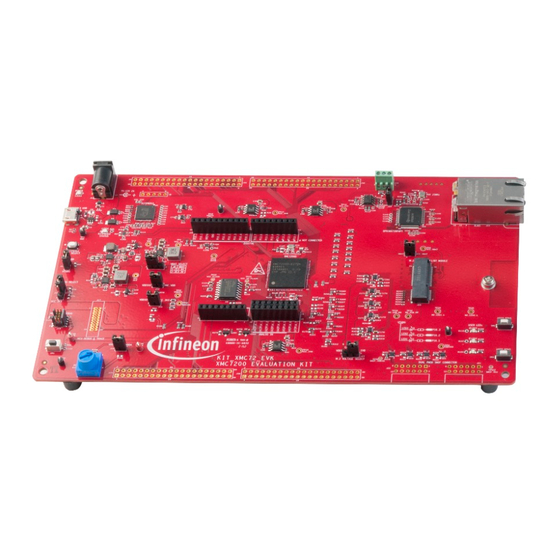

Clock configuration setup in XMC7000 MCU family Configuring the clock resources Configuring the clock resources ECO configuration The ECO is disabled by default and needs to be enabled for usage. Also, trimming is necessary to use the ECO. This device can set the trimming parameters that control the oscillator according to the crystal unit and ceramic resonator. - Page 14 Clock configuration setup in XMC7000 MCU family Configuring the clock resources Double-click the Device Configurator on the left Quick Panel. (you can also double-click design.modus to open the Device Configurator in your project,\bsps\TARGET_APP_KIT_XMC72_EVK\config\design.modus) Figure 11 Quick Panel Figure 12 ECO use case Application note 002-34253 Rev.

-

Page 15: Code Preview

Clock configuration setup in XMC7000 MCU family Configuring the clock resources 3.1.2 Code preview This code is auto generated after configuration in the Device Configurator. Figure 13 Code preview Application note 002-34253 Rev. *C 2023-11-08... -

Page 16: Wco Configuration

Clock configuration setup in XMC7000 MCU family Configuring the clock resources WCO configuration 3.2.1 Overview The WCO is disabled by default. Accordingly, WCO cannot be used unless it is enabled. Figure 14 shows how to configure the registers for enabling the WCO. -

Page 17: Setting The Imo

Clock configuration setup in XMC7000 MCU family Configuring the clock resources This code is auto generated after configuration in the Device Configurator. Figure 16 Code preview Setting the IMO The IMO is enabled by default so that all functions operate properly. The IMO will automatically be disabled during DeepSleep, Hibernate, and XRES modes. -

Page 18: Fll And Pll Configuration

Clock configuration setup in XMC7000 MCU family FLL and PLL configuration FLL and PLL configuration This section shows the configuration of FLL and PLL in the clock system. Setting the FLL 4.1.1 Overview The FLL must be configured before it is used. The FLL has a current-controlled oscillator (CCO); the output frequency of this CCO is controlled by adjusting the trim of the CCO. -

Page 19: Code Preview

Clock configuration setup in XMC7000 MCU family FLL and PLL configuration Select FLL, and in the FLL – Parameters pane, under General, enter the Desired Frequency (MHz) as 100.000 to set the frequency as 100 MHz. Figure 18 Setting output clock frequency as 100.000 MHz 4.1.3... -

Page 20: Setting The Pll

Clock configuration setup in XMC7000 MCU family FLL and PLL configuration Setting the PLL 4.2.1 Overview You must configure the PLL before using it. You can configure these parameters in the System tab of the Device Configurator; based on these, ModusToolbox™... - Page 21 Clock configuration setup in XMC7000 MCU family FLL and PLL configuration Configure the corresponding desired frequency as follows: Figure 21 Configuring output frequency in ‘Parameters’ Figure 22 Configuring output frequency in ‘Parameters’ Application note 002-34253 Rev. *C 2023-11-08...

-

Page 22: Code Preview

Clock configuration setup in XMC7000 MCU family FLL and PLL configuration 4.2.3 Code preview Figure 23 Code preview for PLL200M#0 configuration Figure 24 Code preview for PLL200M#1 configuration Application note 002-34253 Rev. *C 2023-11-08... - Page 23 Clock configuration setup in XMC7000 MCU family FLL and PLL configuration Figure 25 Code preview for PLL400M#0 configuration Figure 26 Code preview for PLL400M#1 configuration Application note 002-34253 Rev. *C 2023-11-08...

-

Page 24: Internal Clock Configuration

Clock configuration setup in XMC7000 MCU family Internal clock configuration Internal clock configuration Configuring CLK_PATHx CLK_PATHx is used as the input source for root clocks CLK_HFx. CLK_PATHx can select all clock resources including the FLL and PLL using DSI_MUX and PATH_MUX. CLK_PATH5 cannot select the FLL and PLL, but other clock resources can be selected. -

Page 25: Code Preview

Clock configuration setup in XMC7000 MCU family Internal clock configuration You can configure CLK_PATHx in the System tab of the Device Configurator. ModusToolbox™ software automatically generates the corresponding code. Figure 28 CLK_PATHx configuration 5.1.1 Code preview Figure 29 Code preview for CLK_PATHx configuration Application note 002-34253 Rev. -

Page 26: Configuring Clk_Hfx

Clock configuration setup in XMC7000 MCU family Internal clock configuration Configuring CLK_HFx CLK_HFx (x=0,1,2,3,4,5,6,7) can be selected from any CLK_PATHy (y=0,1,2,3,4,5). A predivider is available to divide the selected CLK_PATHx. CLK_HF0 is always enabled because it is the source clock for the CPU cores. -

Page 27: Code Preview

Clock configuration setup in XMC7000 MCU family Internal clock configuration 5.2.1 Code preview Figure 32 Code preview for CLK_HFx configuration Configuring CLK_LF CLK_LF can be selected from one of the possible sources: WCO, ILO0, ILO1, and ECO_Prescaler. CLK_LF cannot be set when the WDT_LOCK bit in the WDT_CTL register is disabled because CLK_LF can select ILO0 that is input clock for the WDT. -

Page 28: Configuring Clk_Fast_0/Clk_Fast_1

Clock configuration setup in XMC7000 MCU family Internal clock configuration Configuring CLK_FAST_0/CLK_FAST_1 CLK_FAST_0 and CLK_FAST_1 are generated by dividing CLK_HF1 by (x+1). When configuring CLK_FAST_0 and CLK_FAST_1, configure a value (x = 0..255) divided by the FRAC_DIV bit and INT_DIV bit of the CPUSS_FAST_0_CLOCK_CTL register and CPUSS_FAST_1_CLOCK_CTL register. - Page 29 Clock configuration setup in XMC7000 MCU family Internal clock configuration Start PERI_DIV_CMD.DISABLE=1 Disable the Peripheral Clock Divider. PERI_CLOCK_CTL.DIV_SEL=X_1 Select DIV to use. (X_1 = 0..255) PERI_CLOCK_CTL.TYPE_SEL=X_2 Select TYPE to use. (X_2 = 0, 1, 2, 3) Select Clock Divider Select the Clock Divider to use.

-

Page 30: Pclk Configuration Example

Clock configuration setup in XMC7000 MCU family Internal clock configuration 5.9.1 PCLK configuration example 5.9.1.1 Use case Parameter Value Input clock frequency 80 MHz Output clock frequency 2 MHz Divider type Clock divider 16.0 Used divider Clock divider 16.0#0 Peripheral clock output number... -

Page 31: Configuration

Clock configuration setup in XMC7000 MCU family Internal clock configuration 5.9.1.2 Configuration You can configure these parameters in the Peripheral-Clocks tab of the Device Configurator; based on these, ModusToolbox™ software automatically generates the corresponding code. In the Device Configurator, select the System tab. -

Page 32: Code Preview

Clock configuration setup in XMC7000 MCU family Internal clock configuration 5.9.2 Code preview Figure 37 Code preview for PCLK configuration Application note 002-34253 Rev. *C 2023-11-08... -

Page 33: Configuring The Eco Prescaler

Clock configuration setup in XMC7000 MCU family Internal clock configuration 5.10 Configuring the ECO Prescaler 5.10.1 Overview The ECO_Prescaler divides the ECO and creates a clock that can be used with CLK_LF. The division function has a 10-bit integer divider and an 8-bit fractional divider. -

Page 34: Supplementary Information

Clock configuration setup in XMC7000 MCU family Supplementary information Supplementary information Input clocks in peripheral functions You can view the clock inputs for each peripheral function in the System tab of the Device Configurator. For detailed values of PCLK, see the “Peripheral Clocks” section of the datasheet. -

Page 35: Use Case

Clock configuration setup in XMC7000 MCU family Supplementary information Start Configure ECO and ILO0 Set ECO to Conuter 1 Set ILO0 to Counter 2 Set Count value and Start Counter Check completion of Clock Calibration Calibration Counter Done Counter operation... -

Page 36: Sample Code For Initial Configuration Of Clock Calibration Counter With Ilo0 And Eco

Clock configuration setup in XMC7000 MCU family Supplementary information Table 3 Functions for clock calibration counter with ILO0 and ECO Functions Description Value GetILOClockFreq() Get the ILO 0 Frequency – Cy_SysClk_StartClk Set and start calibration [Set the counter] MeasurementCounters Clk1: Reference clock... -

Page 37: Csv Diagram And Relationship Of Monitored Clock And Reference Clock

Clock configuration setup in XMC7000 MCU family Supplementary information CSV diagram and relationship of monitored clock and reference clock Figure 42 shows the clock diagram with monitored clock and reference clock for CSV. Table 4 shows the relationship between monitored clock and reference clock. - Page 38 Clock configuration setup in XMC7000 MCU family Supplementary information Table 4 Monitored clock and reference clock CSV components Monitor clock Reference clock Notes CSV_HF0 CSV_HF0 CLK_REF_HF CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO. CSV_HF1 CLK_HF1 CLK_REF_HF CLK_REF_HF is selected from CLK_IMO, EXT_CLK, or CLK_ECO.

-

Page 39: Glossary

ADC” chapter of the XMC7000 MCU family architecture reference manual details. Serial communication block. See the “Serial Communication Block (SCB)” chapter of the XMC7000 MCU family manual for details. SDHC Secure Digital High-Capacity Host Controller. See the “SDHC Host Controller” chapter of the XMC7000 MCU family architecture reference manual for details. -

Page 40: References

Clock configuration setup in XMC7000 MCU family References References Datasheet XMC7100 XMC7000 microcontroller 32-bit Arm® Cortex®-M7 • XMC7200 XMC7000 microcontroller 32-bit Arm® Cortex®-M7 • Architecture reference manual XMC7000 MCU family architecture reference manual • Registers reference manual Note: Contact Technical support to obtain these documents. -

Page 41: Revision History

Clock configuration setup in XMC7000 MCU family Revision history Revision history Document Date Description of changes revision 2021-12-13 Initial release 2022-05-06 Updated 5.9 Configuring PCLK Updated 5.10 Configuring the ECO Prescaler Updated Supplementary information 2023-01-09 Updated 3.1.1 Use case 2023-11-08 Updated 2.2 Clock resources... -

Page 42: Disclaimer

Infineon Technologies hereby Infineon Technologies’ products may not be used in disclaims any and all warranties and liabilities of any applications where a failure of the product or any any kind (including without limitation warranties of © 2023 Infineon Technologies AG.

Need help?

Do you have a question about the XMC7000 and is the answer not in the manual?

Questions and answers