Table of Contents

Advertisement

Quick Links

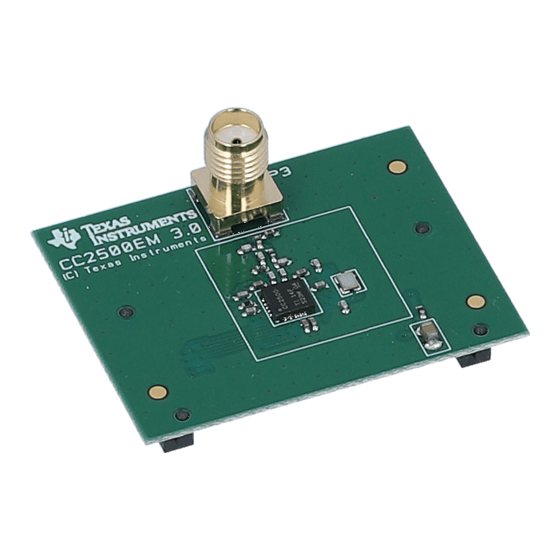

CC2500

Low-Cost Low-Power 2.4 GHz RF Transceiver

Applications

2400-2483.5 MHz ISM/SRD band systems

Consumer electronics

Wireless game controllers

Product Description

The CC2500 is a low-cost 2.4 GHz transceiver

designed for very low-power wireless appli-

cations. The circuit is intended for the 2400-

2483.5 MHz ISM (Industrial, Scientific and

Medical) and SRD (Short Range Device)

frequency band.

The RF transceiver is integrated with a highly

configurable baseband modem. The modem

supports various modulation formats and has

a configurable data rate up to 500 kBaud.

CC2500 provides extensive hardware support

for packet handling, data buffering, burst

transmissions, clear channel assessment, link

quality indication, and wake-on-radio.

The main operating parameters and the 64-

byte transmit/receive FIFOs of CC2500 can be

Key Features

RF Performance

High sensitivity (–104 dBm at 2.4 kBaud,

1% packet error rate)

Low current consumption (13.3 mA in RX,

250 kBaud, input well above sensitivity

limit)

Programmable output power up to +1 dBm

Excellent receiver selectivity and blocking

performance

Programmable data rate from 1.2 to 500

kBaud

Frequency range: 2400 – 2483.5 MHz

Analog Features

OOK, 2-FSK, GFSK, and MSK supported

Suitable for frequency hopping and multi-

channel systems due to a fast settling

Wireless audio

Wireless keyboard and mouse

RF enabled remote controls

controlled via an SPI interface. In a typical

system, the CC2500 will be used together with

a microcontroller and a few additional passive

components.

frequency synthesizer with 90 us settling

time

Automatic

(AFC) can be used to align the frequency

synthesizer

frequency

Integrated analog temperature sensor

Digital Features

Flexible

systems: On-chip support for sync word

detection, address check, flexible packet

length, and automatic CRC handling

Efficient SPI interface: All registers can be

programmed with one "burst" transfer

Digital RSSI output

Programmable channel filter bandwidth

Programmable

indicator

SWRS040C

CC2500

Frequency

Compensation

to

the

received

support

for

packet

Carrier

Sense

Page 1 of 89

centre

oriented

(CS)

Advertisement

Table of Contents

Need help?

Do you have a question about the CC2500 TK and is the answer not in the manual?

Questions and answers