Table of Contents

Advertisement

Quick Links

Getting started with STM32H7x3 hardware development

Introduction

This application note is intended for system designers who develop applications based on

STM32H7x3 microcontroller line (STM32H743xx or STM32H753xx) and need an

implementation overview of the following hardware features:

•

Power supply

•

Package selection

•

Clock management

•

Reset control

•

Boot mode settings

•

Debug management.

This document describes the minimum hardware resources required to develop an

application based on an STM32H743xx or STM32H753xx microcontroller.

Reference documents

The following documents are available on www.st.com:

•

STM32H743xx data brief

•

STM32H753xx data brief

•

Oscillator design guide for STM8S, STM8A and STM32 microcontrollers application note

(AN2867)

• STM32 microcontroller system memory boot mode application note (AN2606).

June 2017

DocID029918 Rev 1

AN4938

Application note

1/48

www.st.com

1

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for ST STM32H7 3 Series

- Page 1 • Debug management. This document describes the minimum hardware resources required to develop an application based on an STM32H743xx or STM32H753xx microcontroller. Reference documents The following documents are available on www.st.com: • STM32H743xx data brief • STM32H753xx data brief •...

-

Page 2: Table Of Contents

Contents AN4938 Contents Power supplies ..........7 Introduction . - Page 3 AN4938 Contents SWJ debug port (serial wire and JTAG) ......26 5.2.1 TPIU trace port ......... . . 26 5.2.2 External debug trigger .

- Page 4 Contents AN4938 Conclusion ..........46 Revision history .

- Page 5 AN4938 List of tables List of tables Table 1. Boot modes............. 23 Table 2.

- Page 6 List of figures AN4938 List of figures Figure 1. VDD33USB connected to VDD power supply ........8 Figure 2.

-

Page 7: Power Supplies

AN4938 Power supplies Power supplies Introduction STM32H743/753xx devices require a 1.71 to 3.6 V operating voltage supply (V ), which can be reduced down to 1.62 V by using an external power supervisor and connecting PDR_ON pin to V (refer to the datasheets for details). The digital power can be supplied either by a internal linear voltage regulator or directly by an external supply voltage. -

Page 8: Figure 1. Vdd33Usb Connected To Vdd Power Supply

Power supplies AN4938 • When the VDD33USB pin is available, this pin can be used to supply the internal transceiver. In this case, VDD33USB pin should receive a voltage ranging from 3.0 to 3.6 V. If VDD50USB is also available, it must be connected to VDD33USB. As an example, when the device is powered at 1.8 V, an independent 3.3 V power supply can be applied to VDD33USB. -

Page 9: Figure 2. Vdd33Usb Connected To External Power Supply

AN4938 Power supplies Figure 2. VDD33USB connected to external power supply Figure 3. VDD50USB power supply DocID029918 Rev 1 9/48... -

Page 10: Battery Backup Domain

Power supplies AN4938 1.1.3 Battery backup domain Backup domain description To retain the content of the RTC backup registers, backup SRAM, and supply the RTC when is turned off, V pin can be connected to an optional 1.2-3.6 V standby voltage supplied by a battery. -

Page 11: Power Supply Scheme

AN4938 Power supplies Power supply scheme Power supplies • = 1.62 to 3.6 V: external power supply for I/Os, Flash memory and system analog blocks such as reset and PLL This power supply is provided externally through VDD pins. VDD pins must be connected to V with external decoupling capacitors: one single tantalum or ceramic capacitor (of 4.7 µF minimum capacitance) for the package and a 100 nF ceramic... -

Page 12: Figure 4. Power Supply Overview

Power supplies AN4938 Figure 4. Power supply overview 12/48 DocID029918 Rev 1... -

Page 13: Reset And Power Supply Supervisor

AN4938 Power supplies Reset and power supply supervisor 1.3.1 Power-on reset (POR)/power-down reset (PDR) The devices have an integrated POR/PDR circuitry that allows a proper operation starting from 1.71 V. The devices remain in reset mode when V is below a specified threshold, VPOR/PDR, without the need for an external reset circuit. -

Page 14: Analog Voltage Detector (Avd)

Power supplies AN4938 Figure 6. PVD threshold 1.3.3 Analog voltage detector (AVD) The AVD can be used to monitor V power supply by comparing it to a threshold selected through the ALS[1:0] bits of the PWR power control register (PWR_CR1). The threshold value can be configured to 1.7, 2.1, 2.5 or 2.8 V (refer to the devices datasheets for the actual values). -

Page 15: Internal Reset On

AN4938 Power supplies Figure 7. Reset circuit 1.3.5 Internal reset ON On the packages embedding the PDR_ON pin, the power supply supervisor is enabled by holding PDR_ON high. On the other packages, the power supply supervisor is always enabled. For more details about the internal reset ON, refer to the datasheets. 1.3.6 Internal reset OFF This feature is available only on the packages featuring the PDR_ON pin. -

Page 16: Figure 8. Power Supply Supervisor Interconnection With Internal Reset Off

Power supplies AN4938 Figure 8. Power supply supervisor interconnection with internal reset OFF The supply ranges which never go below 1.71 V minimum should be better managed by the internal circuitry (no additional component needed, thanks to the fully embedded reset controller). -

Page 17: Bypass Mode

AN4938 Power supplies Figure 9. NRST circuitry timing example 1.3.7 Bypass mode The power management unit can be bypassed. This feature can be configured by software. When bypassed, the core power supply should be provided through VCAPx pins connected together. In Bypass mode, the internal voltage scaling is not managed internally, and the external voltage value (1.0 to 1.2 V) must be consistent with the targeted maximum frequency (see datasheet for the actual VOS level). -

Page 18: Alternate Function Mapping To Pins

Alternate function mapping to pins AN4938 Alternate function mapping to pins In order to easily explore the peripheral alternate functions mapping to the pins it is recommended to use the STM32CubeMX tool available on http://www.st.com. Figure 10. STM32CubeMX example screen-shot 18/48 DocID029918 Rev 1... -

Page 19: Clocks

AN4938 Clocks Clocks Four different clock sources can be used to drive the system clock (SYSCLK): • HSI oscillator clock • CSI oscillator clock. • HSE oscillator clock • Main PLL (PLL) clock The devices have the two following secondary clock sources: •... -

Page 20: External User Clock (Hse Bypass)

Clocks AN4938 3.1.1 External user clock (HSE bypass) In this mode, an external clock source must be provided. The user selects this mode by setting the HSEBYP and HSEON bits in the RCC clock control register (RCC_CR). The external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC_IN pin while the OSC_OUT pin should be left HI-Z. -

Page 21: External Clock (Lse Bypass)

AN4938 Clocks Figure 13. LSE external clock Figure 14. LSE crystal/ceramic resonators Figure 14: LSE crystal/ceramic resonators: To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL ≤... -

Page 22: Clock Security System (Css)

Clocks AN4938 Clock security system (CSS) The device provides two clock security systems (CSS), one for HSE oscillator and one for LSE oscillator. They can be independently enabled by software. When the clock security system on HSE is enabled, the clock detector is activated after the HSE oscillator startup delay, and disabled when this oscillator is stopped: •... -

Page 23: Boot Configuration

AN4938 Boot configuration Boot configuration Boot mode selection In STM32H743/753xx microcontrollers, two different boot spaces can be selected through the BOOT pin and the boot base address programmed in the BOOT_ADD0 or BOOT_ADD1 option bytes as shown in the Table Table 1. -

Page 24: Boot Pin Connection

1. Resistor values are given only as a typical example. System bootloader mode The embedded bootloader code is located in the system memory. It is programmed by ST during production. It is used to reprogram the Flash memory using one of the following serial interfaces. - Page 25 AN4938 Boot configuration Table 2. STM32H743/753xx bootloader communication peripherals (continued) Bootloader peripherals Bootloader pins SPI3 PC12/PC11/PC10/PA15 SPI4 PE11 / PE12 / PE13 / PE14 USB OTG_FS in Device mode PA11/PA12 (DFU) DocID029918 Rev 1 25/48...

-

Page 26: Debug Management

Debug management AN4938 Debug management Introduction The host/target interface is the hardware equipment that connects the host to the application board. This interface is made of three components: a hardware debug tool, a JTAG or SW connector and a cable connecting the host to the debug tool. Figure 16 shows the connection of the host to the evaluation board. -

Page 27: External Debug Trigger

AN4938 Debug management STM32H743/753xx, while still allowing enough space to attach the trace port analyzer probe. Refer to Table 3 for a summary of trace pins and GPIO assignment. Table 3. TPIU trace pins Trace pin name Type Description Pin assignment TRACED0 Output Trace synchronous data out 0... -

Page 28: Flexible Swj-Dp Pin Assignment

Debug management AN4938 Table 5. SWJ debug port pins JTAG debug port SW debug port SWJ-DP pin name assignment Type Description Type Debug assignment JTAG test mode Serial wire data JTMS/SWDIO PA13 Selection input/output JTCK/SWCLK JTAG test clock Serial wire clock PA14 JTDI JTAG test data input... -

Page 29: Internal Pull-Up And Pull-Down On Jtag Pins

AN4938 Debug management 5.3.3 Internal pull-up and pull-down on JTAG pins The devices embed internal pull-ups and pull-downs to guarantee a correct JTAG behavior. The following pins are consequently not left floating during reset and they are configured as follows until the user software takes control of them: •... -

Page 30: Recommendations

Recommendations AN4938 Recommendations Printed circuit board For technical reasons, it is best to use a multilayer printed circuit board (PCB) with a separate layer dedicated to the ground (V ) and another dedicated to the V supply. This provides a good decoupling and a good shielding effect. For many applications, economical reasons prohibit the use of this type of board. -

Page 31: Other Signals

AN4938 Recommendations Figure 18. Typical layout for V pair Other signals When designing an application, the EMC performance can be improved by closely studying: • Signals for which a temporary disturbance affects the running process permanently (the case of interrupts and handshaking strobe signals, and not the case for LED commands). -

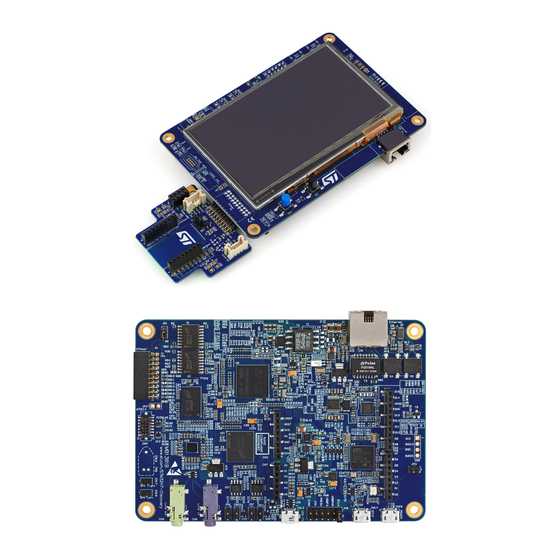

Page 32: Reference Design

Reference design AN4938 Reference design Description The reference design shown in Figure 19, is based on the STM32H753XI, a highly ® ® integrated microcontroller that combines the ARM Cortex -M7 32-bit RISC core running at up to 400 MHz with up to 2 Mbyte dual-bank Flash memory and 1 Mbytes of RAM (including 192 Kbytes of TCM RAM, 864 Kbytes of user RAM and 4 Kbytes of backup SRAM). -

Page 33: Table 8. Optional Components

AN4938 Reference design Table 8. Optional components Components Reference Quantity Comments name Resistor 10 kΩ Pull-up and pull-down for JTAG, BOOT pin, PDR Used as star connection point between V Resistor 0 Ω REF+ Capacitor 100 nF Ceramic capacitor Used for LSE: the value depends on the crystal Capacitor 1.5 pF characteristics... -

Page 34: Figure 19. Stm32H753Xi Reference Schematic

Figure 19. STM32H753XI reference schematic... -

Page 35: Table 9. Reference Connection For All Packages

AN4938 Reference design Table 9. Reference connection for all packages Pin/ball name Pin name (function after reset) VBAT PC14-OSC32_IN (1)(2) (PC14) PC15-OSC32_ OUT (1)(2) (PC15) PH0-OSC_IN (PH0) PH1-OSC_OUT (PH1) NRST VSSA VREF- VREF+ VDDA PA0-WKUP (PA0) DocID029918 Rev 1 35/48... - Page 36 Reference design AN4938 Table 9. Reference connection for all packages (continued) Pin/ball name Pin name (function after reset) VCAP1 VDDLDO1 VDD33 USB 36/48 DocID029918 Rev 1...

- Page 37 AN4938 Reference design Table 9. Reference connection for all packages (continued) Pin/ball name Pin name (function after reset) VDD50 USB VDD33 USB PA13 (JTMS/SWDIO) VCAP2 VDDLDO2 PA14 (JTCK/SWCLK) PA15(JTDI) DocID029918 Rev 1 37/48...

- Page 38 Reference design AN4938 Table 9. Reference connection for all packages (continued) Pin/ball name Pin name (function after reset) (JTDO/TRACESWO) PB4 (NJTRST) BOOT0 VCAP3 PDR_ON VDDLDO3 1. PC1, PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF.

-

Page 39: Recommended Pcb Routing Guidelines For Stm32H743/753Xx Devices

AN4938 Recommended PCB routing guidelines for STM32H743/753xx devices Recommended PCB routing guidelines for STM32H743/753xx devices PCB stack-up In order to reduce the reflections on high speed signals, it is necessary to match the impedance between the source, sink and transmission lines. The impedance of a signal trace depends on its geometry and its position with respect to any reference planes. -

Page 40: Crystal Oscillator

Recommended PCB routing guidelines for STM32H743/753xx devices AN4938 Figure 21. Six layer PCB stack-up example Crystal oscillator Use the application note: Oscillator design guide for STM8S, STM8A and STM32 microcontrollers (AN2867), for further guidance on how to layout and route crystal oscillator circuits. -

Page 41: Figure 22. Decoupling Capacitor Placement Depending On Package Type

AN4938 Recommended PCB routing guidelines for STM32H743/753xx devices Figure 22. Decoupling capacitor placement depending on package type Figure 23. Example of decoupling capacitor placed underneath the STM32H743/753xx DocID029918 Rev 1 41/48... -

Page 42: High Speed Signal Layout

Recommended PCB routing guidelines for STM32H743/753xx devices AN4938 High speed signal layout 8.4.1 SDMMC bus interface Interface connectivity The SD/SDIO MMC card host interface (SDMMC) provides an interface between the AHB peripheral bus and Multi Media Cards (MMCs), SD memory cards and SDIO cards. The SDMMC interface is a serial data bus interface, that consists of a clock (CK), command signal (CMD) and 8 data lines (D[0:7]). -

Page 43: Quadrature Serial Parallel Interface (Quadspi)

AN4938 Recommended PCB routing guidelines for STM32H743/753xx devices Interface signal layout guidelines • Reference the plane using GND or PWR (if PWR, add 10nf stitching cap between PWR and GND Trace the impedance: 50 Ω ± 10% • • The maximum trace length should be below 120mm. If the signal trace exceeds this trace-length/speed criterion, then a termination should be used •... - Page 44 Recommended PCB routing guidelines for STM32H743/753xx devices AN4938 Interface signal layout guidelines • Reference the plane using GND or PWR (if PWR, add 10nf stitching cap between PWR and GND • Trace the impedance: 50 W ± 10% • The maximum trace length should be below 120mm. If the signal trace exceeds this trace-length/speed criterion, then a termination should be used •...

-

Page 45: Embedded Trace Macrocell (Etm)

AN4938 Recommended PCB routing guidelines for STM32H743/753xx devices • Avoid using a serpentine routing for the clock signal and as less via(s) as possible for the whole path. a via alters the impedance and adds a reflection to the signal. 8.4.4 Embedded trace macrocell (ETM) Interface connectivity... - Page 46 Conclusion AN4938 Conclusion This application note should be used as a reference when starting a new design with an STM32H743xx or STM32H753xx microcontroller. 46/48 DocID029918 Rev 1...

-

Page 47: Table 10. Document Revision History

AN4938 Revision history Revision history Table 10. Document revision history Date Revision Changes 13-Jun-2017 Initial release. DocID029918 Rev 1 47/48... - Page 48 ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.

Need help?

Do you have a question about the STM32H7 3 Series and is the answer not in the manual?

Questions and answers