Table of Contents

Advertisement

Features

•

High Performance, Low Power AVR 8-bit Microcontroller

•

Advanced RISC Architecture

– 131 Powerful Instructions - Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 1MIPS throughput per MHz

– On-chip 2-cycle Multiplier

•

Data and Non-Volatile Program Memory

– 16K/32K/64K Bytes Flash of In-System Programmable Program Memory

• Endurance: 10,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

– In-System Programming by On-chip Boot Program

• True Read-While-Write Operation

– 512/1024/2048 Bytes of In-System Programmable EEPROM

• Endurance: 100,000 Write/Erase Cycles

•

Programming Lock for Flash Program and EEPROM Data Security

•

1024/2048/4096 Bytes Internal SRAM

•

On Chip Debug Interface (debugWIRE)

•

CAN 2.0A/B with 6 Message Objects - ISO 16845 Certified

•

LIN 2.1 and 1.3 Controller or 8-Bit UART

•

One 12-bit High Speed PSC (Power Stage Controller) (only ATmega16/32/64M1)

• Non Overlapping Inverted PWM Output Pins With Flexible Dead-Time

• Variable PWM duty Cycle and Frequency

• Synchronous Update of all PWM Registers

• Auto Stop Function for Emergency Event

•

Peripheral Features

– One 8-bit General purpose Timer/Counter with Separate Prescaler, Compare Mode

and Capture Mode

– One 16-bit General purpose Timer/Counter with Separate Prescaler, Compare

Mode and Capture Mode

– One Master/Slave SPI Serial Interface

– 10-bit ADC

• Up To 11 Single Ended Channels and 3 Fully Differential ADC Channel Pairs

• Programmable Gain (5x, 10x, 20x, 40x) on Differential Channels

• Internal Reference Voltage

• Direct Power Supply Voltage Measurement

– 10-bit DAC for Variable Voltage Reference (Comparators, ADC)

– Four Analog Comparators with Variable Threshold Detection

– 100µA ±6% Current Source (LIN Node Identification)

– Interrupt and Wake-up on Pin Change

– Programmable Watchdog Timer with Separate On-Chip Oscillator

– On-chipTemperature Sensor

•

Special Microcontroller Features

– Low Power Idle, Noise Reduction, and Power Down Modes

– Power On Reset and Programmable Brown Out Detection

– In-System Programmable via SPI Port

– High Precision Crystal Oscillator for CAN Operations (16MHz)

1.

See certification on Atmel

®

web site and note on

"Baud Rate" on page

(1)

177.

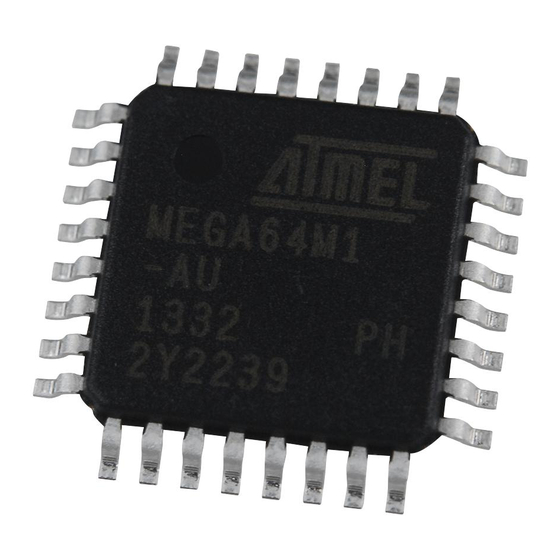

8-bit

Microcontroller

with

16K/32K/64K

Bytes In-System

Programmable

Flash

Atmel

ATmega16M1

ATmega32M1

ATmega64M1

ATmega32C1

ATmega64C1

Automotive

7647H–AVR–03/12

Advertisement

Table of Contents

Summary of Contents for Atmel ATmega32M1

-

Page 1: Features

– Power On Reset and Programmable Brown Out Detection – In-System Programmable via SPI Port – High Precision Crystal Oscillator for CAN Operations (16MHz) ® See certification on Atmel web site and note on “Baud Rate” on page 177. 7647H–AVR–03/12... - Page 2 Core Speed Grade: – 0 - 8MHz at 2.7 - 4.5V – 0 - 16MHz at 4.5 - 5.5V ATmega32/64/M1/C1 Product Line-up Part Number ATmega32C1 ATmega64C1 ATmega16M1 ATmega32M1 ATmega64M1 Flash Size 32 Kbyte 64 Kbyte 16 Kbyte 32 Kbyte 64 Kbyte...

-

Page 3: Pin Configurations

Atmel ATmega16/32/64/M1/C1 1. Pin Configurations Figure 1-1. ATmega16/32/64M1 TQFP32/QFN32 (7*7 mm) Package. ATmega32/64M1 TQFP32/QFN32 (PCINT18/PSCIN2/OC1A/MISO_A) PD2 PB4 (AMP0+/PCINT4) (PCINT19/TXD/TXLIN/OC0A/SS/MOSI_A) PD3 PB3 (AMP0-/PCINT3) (PCINT9/PSCIN1/OC1B/SS_A) PC1 PC6 (ADC10/ACMP1/PCINT14) AREF(ISRC) AGND AVCC (PCINT10/T0/TXCAN) PC2 PC5 (ADC9/ACMP3/AMP1+/PCINT13) (PCINT11/T1/RXCAN/ICP1B) PC3 PC4 (ADC8/ACMPN3/AMP1-/PCINT12) (PCINT0/MISO/PSCOUT2A) PB0 Note: On the engineering samples (Parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. - Page 4 PC6 (ADC10/ACMP1/PCINT14) AREF(ISRC) AGND (PCINT10/T0/TXCAN) PC2 AVCC PC5 (ADC9/ACMP3/AMP1+/PCINT13) (PCINT11/T1/RXCAN/ICP1B) PC3 PC4 (ADC8/ACMPN3/AMP1-/PCINT12) (PCINT0/MISO) PB0 Note: On the first engineering samples (Parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 5: Pin Descriptions

Atmel ATmega16/32/64/M1/C1 Pin Descriptions Table 1-1. Pin out description QFN32 Pin Number Mnemonic Type Name, Function and Alternate Function Power Ground: 0V reference AGND Power Analog Ground: 0V reference for analog part Power Power Supply Analog Power Supply: This is the power supply voltage for... - Page 6 MISO_A (Programming & alternate SPI Master In Slave Out) PCINT18 (Pin Change Interrupt 18) Note: 1. On the first engineering samples (Parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 7 Atmel ATmega16/32/64/M1/C1 Table 1-1. Pin out description (Continued) QFN32 Pin Number Mnemonic Type Name, Function and Alternate Function TXD (UART Tx data) TXLIN (LIN Transmit Output) OC0A (Timer 0 Output Compare A) SS (SPI Slave Select) MOSI_A (Programming & alternate Master Out SPI Slave In)

-

Page 8: Overview

32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con- ventional CISC microcontrollers. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 9: Automotive Quality Grade

Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16/32/64/M1/C1 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications. -

Page 10: Pin Descriptions

Reset, even if the clock is not running. The minimum pulse length is given in Table 7-1 on page 47. Shorter pulses are not guaranteed to generate a Reset. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 11: About Code Examples

Atmel ATmega16/32/64/M1/C1 Depending on the clock selection fuse settings, PE1 can be used as input to the inverting Oscil- lator amplifier and input to the internal clock operating circuit. Depending on the clock selection fuse settings, PE2 can be used as output from the inverting Oscillator amplifier. -

Page 12: Avr Cpu Core

While one instruction is being executed, the next instruc- tion is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 13: Alu - Arithmetic Logic Unit

Atmel ATmega16/32/64/M1/C1 The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typ- ical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File –... -

Page 14: Status Register

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. • Bit 1 – Z: Zero Flag The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 15: General Purpose Register File

Atmel ATmega16/32/64/M1/C1 • Bit 0 – C: Carry Flag The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. General Purpose Register File The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve... -

Page 16: Stack Pointer

AVR architecture is so small that only SPL is needed. In this case, the SPH Register will not be present. SP15 SP14 SP13 SP12 SP11 SP10 Read/Write Initial Value Top address of the SRAM (0x04FF/0x08FF/0x10FF) Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 17: Instruction Execution Timing

Atmel ATmega16/32/64/M1/C1 Instruction Execution Timing This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock clk , directly generated from the selected clock source for the chip. No internal clock division is used. - Page 18 When using the CLI instruction to disable interrupts, the interrupts will be immediately disabled. No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 19 Atmel ATmega16/32/64/M1/C1 Assembly Code Example in r16, SREG ; store SREG value ; disable interrupts during timed sequence sbi EECR, EEMWE ; start EEPROM write sbi EECR, EEWE out SREG, r16 ; restore SREG value (I-bit) C Code Example char cSREG;...

-

Page 20: Memories

– Load Program Memory. Timing diagrams for instruction fetch and execution are presented in “Instruction Execution Tim- ing” on page Figure 4-1. Program Memory Map Program Memory 0x0000 Application F lash Sec t ion Boot Flash S e ction 0x1FFF/0x3FFF/0x7F Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 21: Sram Data Memory

Atmel ATmega16/32/64/M1/C1 SRAM Data Memory Figure 4-2 shows how the ATmega16/32/64/M1/C1 SRAM Memory is organized. The ATmega16/32/64/M1/C1 is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used. -

Page 22: Eeprom Data Memory

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 23 Atmel ATmega16/32/64/M1/C1 4.3.2 The EEPROM Address Registers – EEARH and EEARL – – – – – EEAR10 EEAR9 EEAR8 EEARH EEAR7 EEAR6 EEAR5 EEAR4 EEAR3 EEAR2 EEAR1 EEAR0 EEARL Read/Write Initial Value • Bits 15.11 – Reserved Bits These bits are reserved bits in the ATmega16/32/64/M1/C1 and will always read as zero.

- Page 24 When the write access time has elapsed, the EEWE bit is cleared by hardware. The user soft- ware can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 25 Atmel ATmega16/32/64/M1/C1 • Bit 0 – EERE: EEPROM Read Enable The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read.

- Page 26 & (1<<EEWE)) /* Set up address and data registers */ EEAR = uiAddress; EEDR = ucData; /* Write logical one to EEMWE */ EECR |= (1<<EEMWE); /* Start eeprom write by setting EEWE */ EECR |= (1<<EEWE); Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 27 Atmel ATmega16/32/64/M1/C1 The next code examples show assembly and C functions for reading the EEPROM. The exam- ples assume that interrupts are controlled so that no interrupts will occur during execution of these functions. Assembly Code Example EEPROM_read: ; Wait for completion of previous write...

-

Page 28: I/O Memory

General Purpose I/O Register 1 – GPIOR1 GPIOR17 GPIOR16 GPIOR15 GPIOR14 GPIOR13 GPIOR12 GPIOR11 GPIOR10 GPIOR1 Read/Write Initial Value 4.5.3 General Purpose I/O Register 2 – GPIOR2 GPIOR27 GPIOR26 GPIOR25 GPIOR24 GPIOR23 GPIOR22 GPIOR21 GPIOR20 GPIOR2 Read/Write Initial Value Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 29: System Clock

Atmel ATmega16/32/64/M1/C1 5. System Clock Clock Systems and their Distribution Figure 5-1 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to unused modules can be halted by using different sleep modes, as described in “Power Management and... -

Page 30: Clock Sources

The number of WDT Oscillator cycles used for each time-out is shown in Table 5-2. The frequency of the Watchdog Oscillator is voltage dependent as shown in “Watchdog Oscillator Frequency versus V ” on page 342. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 31: Default Clock Source

Atmel ATmega16/32/64/M1/C1 Table 5-2. Number of Watchdog Oscillator Cycles Typ Time-out (V = 5.0V) Typ Time-out (V = 3.0V) Number of Cycles 4.1 ms 4.3 ms 4K (4,096) 65 ms 69 ms 64K (65,536) Default Clock Source The device is shipped with CKSEL = “0010”, SUT = “10”, and CKDIV8 programmed. The default clock source setting is the Internal RC Oscillator with longest start-up time and an initial system clock prescaling of 8. - Page 32 2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum fre- quency of the device, and if frequency stability at start-up is not important for the application. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 33: Calibrated Internal Rc Oscillator

Atmel ATmega16/32/64/M1/C1 Calibrated Internal RC Oscillator By default, the Internal RC OScillator provides an approximate 8.0MHz clock. Though voltage and temperature dependent, this clock can be very accurately calibrated by the user. The device is shipped with the CKDIV8 Fuse programmed. See “System Clock Prescaler”... -

Page 34: Pll

The internal PLL is enabled only when the PLLE bit in the register PLLCSR is set. The bit PLOCK from the register PLLCSR is set when PLL is locked. Both internal 8MHz RC Oscillator, Crystal Oscillator and PLL are switched off in Power-down and Standby sleep modes.03/12 Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 35 Atmel ATmega16/32/64/M1/C1 Table 5-7. Start-up Times when the PLL is selected as system clock CKSEL Start-up Time from Power-down Additional Delay from Reset 3..0 SUT1..0 and Power-save = 5.0V) 1K CK 14CK 1K CK 14CK + 4 ms 0011 RC Osc...

-

Page 36: 128 Khz Internal Oscillator

5-4. To run the device on an external clock, the CKSEL Fuses must be programmed to “0000”. Figure 5-4. External Clock Drive Configuration XTAL2 External XTAL1 Clock Signal Table 5-8. External Clock Frequency CKSEL3..0 Frequency Range 0000 0 - 16MHz Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 37: Clock Output Buffer

Atmel ATmega16/32/64/M1/C1 When this clock source is selected, start-up times are determined by the SUT Fuses as shown in Table 5-9. Table 5-9. Start-up Times for the External Clock Selection Start-up Time from Additional Delay from SUT1..0 Power-down and Power-save Reset (V = 5.0V) - Page 38 Fuse setting. The Application software must ensure that a sufficient division factor is chosen if the selcted clock source has a higher frequency than the maximum frequency of the device at the present operating conditions. The device is shipped with the CKDIV8 Fuse programmed. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 39 Atmel ATmega16/32/64/M1/C1 Table 5-10. Clock Prescaler Select CLKPS3 CLKPS2 CLKPS1 CLKPS0 Clock Division Factor Reserved Reserved Reserved Reserved Reserved Reserved Reserved 7647H–AVR–03/12...

-

Page 40: Power Management And Sleep Modes

To avoid the MCU entering the sleep mode unless it is the programmer’s purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 41: Idle Mode

Atmel ATmega16/32/64/M1/C1 Idle Mode When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing SPI, UART, Analog Comparator, ADC, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halt clk and clk , while allowing the other clocks to run. -

Page 42: Standby Mode

So its recommended to stop a peripheral before stopping its clock with PRR register. Module shutdown can be used in Idle mode and Active mode to significantly reduce the overall power consumption. In all other sleep modes, the clock is already stopped. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 43 Atmel ATmega16/32/64/M1/C1 6.6.1 Power Reduction Register - PRR PRCAN PRPSC PRTIM1 PRTIM0 PRSPI PRLIN PRADC Read/Write Initial Value • Bit 7 - Res: Reserved Bit This bit is unused bit in the ATmega16/32/64/M1/C1, and will always read as zero. • Bit 6 - PRCAN: Power Reduction CAN Writing a logic one to this bit reduces the consumption of the CAN by stopping the clock to this module.

-

Page 44: Minimizing Power Consumption

Watchdog Timer is enabled, it will be enabled in all sleep modes, and hence, always consume power. In the deeper sleep modes, this will contribute significantly to the total current consump- tion. Refer to “Watchdog Timer” on page 52 for details on how to configure the Watchdog Timer. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 45 Atmel ATmega16/32/64/M1/C1 6.7.6 Port Pins When entering a sleep mode, all port pins should be configured to use minimum power. The most important is then to ensure that no pins drive resistive loads. In sleep modes where both the I/O clock (clk...

-

Page 46: System Control And Reset

Watchdog Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog is enabled. • Brown-out Reset. The MCU is reset when the supply voltage V is below the Brown-out Reset threshold (V ) and the Brown-out Detector is enabled. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 47 Atmel ATmega16/32/64/M1/C1 Figure 7-1. Reset Logic DATA BUS MCU Status Register (MCUSR) Power-on Reset Circuit Brown-out Reset Circuit BODLEVEL [2..0] Pull-up Resistor Spike Filter Watchdog Oscillator Delay Counters Clock TIMEOUT Generator CKSEL[3:0] SUT[1:0] Table 7-1. Reset Characteristics Symbol Parameter Units...

- Page 48 Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage – V – on its positive edge, the delay counter starts the MCU after the Time-out period – t – has expired. TOUT Figure 7-4. External Reset During Operation Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 49 Atmel ATmega16/32/64/M1/C1 7.2.3 Brown-out Detection ATmega16/32/64/M1/C1 has an On-chip Brown-out Detection (BOD) circuit for monitoring the level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the BODLEVEL Fuses. The trigger level has a hysteresis to ensure spike free Brown-out Detection.

- Page 50 • Bit 2 – BORF: Brown-out Reset Flag This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 51: Internal Voltage Reference

Atmel ATmega16/32/64/M1/C1 • Bit 1 – EXTRF: External Reset Flag This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag. • Bit 0 – PORF: Power-on Reset Flag This bit is set if a Power-on Reset occurs. -

Page 52: Watchdog Timer

WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit. 2. Within the next four clock cycles, write the WDE and Watchdog prescaler bits (WDP) as desired, but with the WDCE bit cleared. This must be done in one operation. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 53 Atmel ATmega16/32/64/M1/C1 The following code example shows one assembly and one C function for turning off the Watch- dog Timer. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during the execution of these functions.

- Page 54 1. The example code assumes that the part specific header file is included. Note: The Watchdog Timer should be reset before any change of the WDP bits, since a change in the WDP bits can result in a time-out when switching to a shorter time-out period; Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 55 Atmel ATmega16/32/64/M1/C1 7.4.1 Watchdog Timer Control Register - WDTCSR WDIF WDIE WDP3 WDCE WDP2 WDP1 WDP0 WDTCSR Read/Write Initial Value • Bit 7 - WDIF: Watchdog Interrupt Flag This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is config- ured for interrupt.

- Page 56 64 ms 16K (16384) cycles 0.125 s 32K (32768) cycles 0.25 s 64K (65536) cycles 0.5 s 128K (131072) cycles 1.0 s 256K (262144) cycles 2.0 s 512K (524288) cycles 4.0 s 1024K (1048576) cycles 8.0 s Reserved Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 57: Interrupts

Atmel ATmega16/32/64/M1/C1 8. Interrupts T h i s s e c t i o n d e s c r i b e s t h e s p e c i f i c s o f t h e i n t e r r u p t h a n d l i n g a s p e r f o r m e d i n ATmega16/32/64/M1/C1. - Page 58 ; Timer0 Overflow Handler 0x024 CAN_INT ; CAN MOB,Burst,General Errors Handler 0x026 CAN_TOVF ; CAN Timer Overflow Handler 0x028 LIN_TC ; LIN Transfer Complete Handler 0x02A LIN_ERR ; LIN Error Handler 0x02C PCINT0 ; Pin Change Int Request 0 Handler Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 59 Atmel ATmega16/32/64/M1/C1 0x02E PCINT1 ; Pin Change Int Request 1 Handler 0x030 PCINT2 ; Pin Change Int Request 2 Handler 0x032 PCINT3 ; Pin Change Int Request 3 Handler 0x034 SPI_STC ; SPI Transfer Complete Handler 0x036 ; ADC Conversion Complete Handler 0x038 ;...

- Page 60 Interrupt Vector tables, a special write procedure must be followed to change the IVSEL bit: 1. Write the Interrupt Vector Change Enable (IVCE) bit to one. 2. Within four cycles, write the desired value to IVSEL while writing a zero to IVCE. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 61 Atmel ATmega16/32/64/M1/C1 Interrupts will automatically be disabled while this sequence is executed. Interrupts are disabled in the cycle IVCE is set, and they remain disabled until after the instruction following the write to IVSEL. If IVSEL is not written, interrupts remain disabled for four cycles. The I-bit in the Status Register is unaffected by the automatic disabling.

-

Page 62: I/O-Ports

67. Refer to the individual module sections for a full description of the alternate functions. Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 63: Ports As General Digital I/O

Atmel ATmega16/32/64/M1/C1 Ports as General Digital I/O The ports are bi-directional I/O ports with optional internal pull-ups. Figure 9-2 shows a func- tional description of one I/O-port pin, here generically called Pxn. Figure 9-2. General Digital I/O DDxn RESET PORTxn... - Page 64 Figure 9-3 shows a timing dia- gram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted t and t respectively. pd,max pd,min Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 65 Atmel ATmega16/32/64/M1/C1 Figure 9-3. Synchronization when Reading an Externally Applied Pin value SYSTEM CLK INSTRUCTIONS in r17, PINx SYNC LATCH PINxn 0x00 0xFF pd, max pd, min Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the “SYNC LATCH”...

- Page 66 “Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin” while the external interrupt is not enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned sleep modes, as the clamping in these sleep modes produces the requested logic change. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 67: Alternate Port Functions

Atmel ATmega16/32/64/M1/C1 Alternate Port Functions Most port pins have alternate functions in addition to being general digital I/Os. Figure 9-5 shows how the port pin control signals from the simplified Figure 9-2 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family. - Page 68 The signal is connected directly to the pad, and can be used Input/Output bi-directionally. The following subsections shortly describe the alternate functions for each port, and relate the overriding signals to the alternate function. Refer to the alternate function description for further details. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 69 Atmel ATmega16/32/64/M1/C1 9.3.1 MCU Control Register – MCUCR SPIPS – – – – IVSEL IVCE MCUCR Read/Write Initial Value • Bit 4 – PUD: Pull-up Disable When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01).

- Page 70 DDB1. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB1 and PUD bits. PSCOUT2B, Output 2B of PSC. PCINT1, Pin Change Interrupt 1. • PCINT0/MISO/PSCOUT2A – Bit 0 Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 71 Atmel ATmega16/32/64/M1/C1 MISO, Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a master, this pin is configured as an input regardless of the setting of DDB0. When the SPI is enabled as a slave, the data direction of this pin is controlled by DDB0. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB0 and PUD bits.

- Page 72 AMP2+, Analog Differential Amplifier 2 Positive Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Amplifier. PCINT15, Pin Change Interrupt 15. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 73 Atmel ATmega16/32/64/M1/C1 • ADC10/ACMP1/PCINT14 – Bit 6 ADC10, Analog to Digital Converter, input channel 10. ACMP1, Analog Comparator 1 Positive Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Ana- log Comparator.

- Page 74 Overriding Signals for Alternate Functions in PC3..PC0 PC1/PSCIN1/ PC0/INT3/ PC3/T1/RXCAN/ PC2/T0/TXCAN/ OC1B/SS_A/ PSCOUT1A/ Signal Name ICP1B/PCINT11 PCINT10 PCINT9 PCINT8 PUOE PUOV DDOE PSCen10 DDOV PVOE OC1Ben PSCen10 PVOV OC1B PSCout10 DIEOE In3en DIEOV In3en PSCin1 INT3 SS_A Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 75 Atmel ATmega16/32/64/M1/C1 9.3.4 Alternate Functions of Port D The Port D pins with alternate functions are shown in Table 9-9. Table 9-9. Port D Pins Alternate Functions Port Pin Alternate Function ACMP0 (Analog Comparator 0 Positive Input ) PCINT23 (Pin Change Interrupt 23)

- Page 76 DDD3. When the pin is forced to be an input, the pull-up can still be controlled by the PORTD3 bit. PCINT19, Pin Change Interrupt 19. • PCINT18/PSCIN2/OC1A/MISO_A, Bit 2 PCSIN2, PSC Digital Input 2. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 77 Atmel ATmega16/32/64/M1/C1 OC1A, Output Compare Match A output: This pin can serve as an external output for the Timer/Counter1 Output Compare A. The pin has to be configured as an output (DDD2 set “one”) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

- Page 78 PCINT25 (Pin Change Interrupt 25) RESET# (Reset Input) OCD (On Chip Debug I/O) PCINT24 (Pin Change Interrupt 24) Note: On the engineering samples (Parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 79 Atmel ATmega16/32/64/M1/C1 The alternate pin configuration is as follows: • PCINT26/XTAL2/ADC0 – Bit 2 XTAL2: Chip clock Oscillator pin 2. Used as clock pin for crystal Oscillator or Low-frequency crystal Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

-

Page 80: Register Description For I/O-Ports

Port D Data Register – PORTD PORTD7 PORTD6 PORTD5 PORTD4 PORTD3 PORTD2 PORTD1 PORTD0 PORTD Read/Write Initial Value 9.4.8 Port D Data Direction Register – DDRD DDD7 DDD6 DDD5 DDD4 DDD3 DDD2 DDD1 DDD0 DDRD Read/Write Initial Value Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 81 Atmel ATmega16/32/64/M1/C1 9.4.9 Port D Input Pins Address – PIND PIND7 PIND6 PIND5 PIND4 PIND3 PIND2 PIND1 PIND0 PIND Read/Write Initial Value 9.4.10 Port E Data Register – PORTE – – – – – PORTE2 PORTE1 PORTE0 PORTE Read/Write Initial Value 9.4.11...

-

Page 82: External Interrupts

An example of timing of a pin change interrupt is schown in Figure 10-1. Figure 10-1. Timing of a pin change interrupts pcint_sync pcint_set/flag pin_lat pin_sync pcint_in[i] PCINT[i] PCIF (interrupt flag) PCINT[i] bit (of PCMSK PCINT[i] pin pin_lat pin_sync pcint_in[i] pcint_syn pcint_set/flag PCIF Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 83: External Interrupt Control Register A - Eicra

Atmel ATmega16/32/64/M1/C1 10.2 External Interrupt Control Register A – EICRA The External Interrupt Control Register A contains control bits for interrupt sense control. ISC31 ISC30 ISC21 ISC20 ISC11 ISC10 ISC01 ISC00 EICRA Read/Write Initial Value • Bit 7..0 – ISC31, ISC30 - ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0 The External Interrupts 3 - 0 are activated by the external pins INT3:0 if the SREG I-flag and the corresponding interrupt mask in the EIMSK is set. - Page 84 0 is enabled. Any change on any enabled PCINT7..0 pin will cause an interrupt. The corresponding interrupt of Pin Change Interrupt Request is executed from the PCI0 Inter- rupt Vector. PCINT7..0 pins are enabled individually by the PCMSK0 Register. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 85 Atmel ATmega16/32/64/M1/C1 10.2.4 Pin Change Interrupt Flag Register - PCIFR – – – – PCIF3 PCIF2 PCIF1 PCIF0 PCIFR Read/Write Initial Value • Bit 7..4 - Res: Reserved Bits These bits are unused bits in the ATmega16/32/64/M1/C1, and will always read as zero.

- Page 86 If PCINT7..0 is set and the PCIE0 bit in PCICR is set, pin change interrupt is enabled on the corresponding I/O pin. If PCINT7..0 is cleared, pin change interrupt on the corresponding I/O pin is disabled. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 87: Timer/Counter0 And Timer/Counter1 Prescalers

Atmel ATmega16/32/64/M1/C1 11. Timer/Counter0 and Timer/Counter1 Prescalers Timer/Counter1 and Timer/Counter0 share the same prescaler module, but the Timer/Counters can have different prescaler settings. The description below applies to both Timer/Counter1 and Timer/Counter0. 11.1 Internal Clock Source The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This... - Page 88 When the TSM bit is written to zero, the PSRSYNC bit is cleared by hardware, and the Timer/Counters start counting simultaneously. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 89 Atmel ATmega16/32/64/M1/C1 • Bit6 – ICPSEL1: Timer 1 Input Capture selection Timer 1 capture function has two possible inputs ICP1A (PD4) and ICP1B (PC3). The selection is made thanks to ICPSEL1 bit as described in Table 11-1. Table 11-1. ICPSEL1...

-

Page 90: 12 8-Bit Timer/Counter0 With Pwm

Unit, in this case Compare Unit A or Compare Unit B. However, when using the register or bit defines in a program, the precise form must be used, i.e., TCNT0 for accessing Timer/Counter0 counter value and so on. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 91: Timer/Counter Clock Sources

Atmel ATmega16/32/64/M1/C1 The definitions in Table 12-1 are also used extensively throughout the document. Table 12-1. Definitions BOTTOM The counter reaches the BOTTOM when it becomes 0x00. The counter reaches its MAXimum when it becomes 0xFF (decimal 255). The counter reaches the TOP when it becomes equal to the highest value in the count sequence. -

Page 92: Output Compare Unit

Waveform Generator for handling the special cases of the extreme values in some modes of operation (“Modes of Operation” on page 95). Figure 12-3 shows a block diagram of the Output Compare unit. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 93 Atmel ATmega16/32/64/M1/C1 Figure 12-3. Output Compare Unit, Block Diagram DATA BUS OCRnx TCNTn (8-bit Comparator ) OCFnx (Int.Req.) bottom Waveform Generator OCnx FOCn WGMn1:0 COMnx1:0 The OCR0x Registers are double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the dou- ble buffering is disabled.

-

Page 94: Compare Match Output Unit

The design of the Output Compare pin logic allows initialization of the OC0x state before the out- put is enabled. Note that some COM0x1:0 bit settings are reserved for certain modes of operation. See “8-bit Timer/Counter Register Description” on page 101. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 95: Modes Of Operation

Atmel ATmega16/32/64/M1/C1 12.5.1 Compare Output Mode and Waveform Generation The Waveform Generator uses the COM0x1:0 bits differently in Normal, CTC, and PWM modes. For all modes, setting the COM0x1:0 = 0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next compare match. - Page 96 This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 97 Atmel ATmega16/32/64/M1/C1 In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 12-6.

- Page 98 (COMnx1:0 = 2) OCnx (COMnx1:0 = 3) Period The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 99: Timer/Counter Timing Diagrams

Atmel ATmega16/32/64/M1/C1 In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC0x pins. Setting the COM0x1:0 bits to two will produce a non-inverted PWM. An inverted PWM output can be generated by setting the COM0x1:0 to three: Setting the COM0A0 bits to one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. - Page 100 OCF0A and the clearing of TCNT0 in CTC mode and fast PWM mode where OCR0A is TOP. Figure 12-11. Timer/Counter Timing Diagram, Clear Timer on Compare Match mode, with Pres- caler (f clk_I/O (clk TCNTn TOP - 1 BOTTOM BOTTOM + 1 (CTC) OCRnx OCFnx Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 101: 8-Bit Timer/Counter Register Description

Atmel ATmega16/32/64/M1/C1 12.8 8-bit Timer/Counter Register Description 12.8.1 Timer/Counter Control Register A – TCCR0A COM0A1 COM0A0 COM0B1 COM0B0 – – WGM01 WGM00 TCCR0A Read/Write Initial Value • Bits 7:6 – COM0A1:0: Compare Match Output A Mode These bits control the Output Compare pin (OC0A) behavior. If one or both of the COM0A1:0 bits are set, the OC0A output overrides the normal port functionality of the I/O pin it is connected to. - Page 102 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Com- pare Match is ignored, but the set or clear is done at TOP. See “Fast PWM Mode” on page 96 for more details. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 103 Atmel ATmega16/32/64/M1/C1 Table 12-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase cor- rect PWM mode. Table 12-7. Compare Output Mode, Phase Correct PWM Mode COM0B1 COM0B0 Description Normal port operation, OC0B disconnected. Reserved Clear OC0B on Compare Match when up-counting. Set OC0B on Compare Match when down-counting.

- Page 104 No clock source (Timer/Counter stopped) /(No prescaling) /8 (From prescaler) /64 (From prescaler) /256 (From prescaler) /1024 (From prescaler) External clock source on T0 pin. Clock on falling edge. External clock source on T0 pin. Clock on rising edge. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 105 Atmel ATmega16/32/64/M1/C1 If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting. 12.8.3 Timer/Counter Register – TCNT0...

- Page 106 When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed. The setting of this flag is dependent of the WGM02:0 bit setting. Refer to Table 12-8, “Waveform Generation Mode Bit Description” on page 103. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 107: 16-Bit Timer/Counter1 With Pwm

Atmel ATmega16/32/64/M1/C1 13. 16-bit Timer/Counter1 with PWM The 16-bit Timer/Counter unit allows accurate program execution timing (event management), wave generation, and signal timing measurement. The main features are: • True 16-bit Design (i.e., Allows 16-bit PWM) • Two independent Output Compare Units •... - Page 108 Tn pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock (clk Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 109: Accessing 16-Bit Registers

Atmel ATmega16/32/64/M1/C1 The double buffered Output Compare Registers (OCRnx) are compared with the Timer/Counter value at all time. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pin (OCnx). - Page 110 Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 111 Atmel ATmega16/32/64/M1/C1 The following code examples show how to do an atomic read of the TCNTn Register contents. Reading any of the OCRnx or ICRn Registers can be done by using the same principle. Assembly Code Example TIM16_ReadTCNTn: ; Save global interrupt flag in r18,SREG ;...

-

Page 112: Timer/Counter Clock Sources

Clock Select logic which is controlled by the Clock Select (CSn2:0) bits located in the Timer/Counter control Register B (TCCRnB). For details on clock sources and prescaler, see “Timer/Counter0 and Timer/Counter1 Prescalers” on page Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 113: Counter Unit

Atmel ATmega16/32/64/M1/C1 13.4 Counter Unit The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings. Figure 13-2. Counter Unit Block Diagram DATA BUS (8-bit) TOVn (Int.Req.) -

Page 114: Input Capture Unit

(ICRnL) and then the high byte (ICRnH). When the low byte is read the high byte is copied into the high byte temporary register (TEMP). When the CPU reads the ICRnH I/O location it will access the TEMP Register. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 115 Atmel ATmega16/32/64/M1/C1 The ICRn Register can only be written when using a Waveform Generation mode that utilizes the ICRn Register for defining the counter’s TOP value. In these cases the Waveform Genera- tion mode (WGMn3:0) bits must be set before the TOP value can be written to the ICRn Register.

-

Page 116: Output Compare Units

(n = n for Timer/Counter n), and the “x” indicates Output Compare unit (x). The elements of the block diagram that are not directly a part of the Output Compare unit are gray shaded. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 117 Atmel ATmega16/32/64/M1/C1 Figure 13-4. Output Compare Unit, Block Diagram DATA BUS (8-bit) TEMP (8-bit) OCRnxH Buf. (8-bit) OCRnxL Buf. (8-bit) TCNTnH (8-bit) TCNTnL (8-bit) OCRnx Buffer (16-bit Register) TCNTn (16-bit Counter) OCRnxH (8-bit) OCRnxL (8-bit) OCRnx (16-bit Register) (16-bit Comparator ) OCFnx (Int.Req.)

-

Page 118: Compare Match Output Unit

(DDR and PORT) that are affected by the COMnx1:0 bits are shown. When referring to the OCnx state, the reference is for the internal OCnx Register, not the OCnx pin. If a system reset occur, the OCnx Register is reset to “0”. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 119 Atmel ATmega16/32/64/M1/C1 Figure 13-5. Compare Match Output Unit, Schematic COMnx1 Waveform COMnx0 Generator FOCnx OCnx OCnx PORT The general I/O port function is overridden by the Output Compare (OCnx) from the Waveform Generator if either of the COMnx1:0 bits are set. However, the OCnx pin direction (input or out- put) is still controlled by the Data Direction Register (DDR) for the port pin.

-

Page 120: Modes Of Operation

The timing diagram for the CTC mode is shown in Figure 13-6. The counter value (TCNTn) increases until a compare match occurs with either OCRnA or ICRn, and then counter (TCNTn) is cleared. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 121 Atmel ATmega16/32/64/M1/C1 Figure 13-6. CTC Mode, Timing Diagram OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) TCNTn OCnA (COMnA1:0 = 1) (Toggle) Period An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCFnA or ICFn Flag according to the register used to define the TOP value.

- Page 122 TOP value. The counter will then have to count to the MAX value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. The OCRnA Register however, is double buffered. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 123 Atmel ATmega16/32/64/M1/C1 This feature allows the OCRnA I/O location to be written anytime. When the OCRnA I/O location is written the value written will be put into the OCRnA Buffer Register. The OCRnA Compare Register will then be updated with the value in the Buffer Register at the next timer clock cycle the TCNTn matches TOP.

- Page 124 Note that when using fixed TOP values, the unused bits are masked to zero when any of the OCRnx Registers are written. As the third period shown in Figure 13-8 illustrates, changing the TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 125 Atmel ATmega16/32/64/M1/C1 The reason for this can be found in the time of update of the OCRnx Register. Since the OCRnx update occurs at TOP, the PWM period starts and ends at TOP. This implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value.

- Page 126 When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNTn and the OCRnx. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 127 Atmel ATmega16/32/64/M1/C1 Figure 13-9 shows the output generated is, in contrast to the phase correct mode, symmetri- cal in all periods. Since the OCRnx Registers are updated at BOTTOM, the length of the rising and the falling slopes will always be equal. This gives symmetrical output pulses and is therefore frequency correct.

-

Page 128: Timer/Counter Timing Diagrams

Figure 13-11. Timer/Counter Timing Diagram, Setting of OCFnx, with Prescaler (f clk_I/O (clk TCNTn OCRnx - 1 OCRnx OCRnx + 1 OCRnx + 2 OCRnx OCRnx Value OCFnx Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 129 Atmel ATmega16/32/64/M1/C1 Figure 13-12 shows the count sequence close to TOP in various modes. When using phase and frequency correct PWM mode the OCRnx Register is updated at BOTTOM. The timing diagrams will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on.

-

Page 130: 16-Bit Timer/Counter Register Description

1. A special case occurs when OCRnA/OCRnB equals TOP and COMnA1/COMnB1 is set. In this case the compare match is ignored, but the set or clear is done at TOP. See “Fast PWM Mode” on page 121. for more details. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 131 Atmel ATmega16/32/64/M1/C1 Table 13-3 shows the COMnx1:0 bit functionality when the WGMn3:0 bits are set to the phase correct or the phase and frequency correct, PWM mode. Table 13-3. Compare Output Mode, Phase Correct and Phase and Frequency Correct COMnA1/COMnB1...

- Page 132 No clock source (Timer/Counter stopped). /1 (No prescaling) /8 (From prescaler) /64 (From prescaler) /256 (From prescaler) /1024 (From prescaler) External clock source on Tn pin. Clock on falling edge. External clock source on Tn pin. Clock on rising edge. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 133 Atmel ATmega16/32/64/M1/C1 If external pin modes are used for the Timer/Countern, transitions on the Tn pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting. 13.10.3 Timer/Counter1 Control Register C – TCCR1C...

- Page 134 When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Output Compare B Match interrupt is enabled. The corresponding Interrupt Vector (Table 8-2 on page 58) is executed when the OCF1B Flag, located in TIFR1, is set. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 135 Atmel ATmega16/32/64/M1/C1 • Bit 1 – OCIE1A: Timer/Counter1, Output Compare A Match Interrupt Enable When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Output Compare A Match interrupt is enabled. The corresponding...

-

Page 136: Power Stage Controller - (Psc) (Only Atmega16/32/64M1)

To do a 16-bit write, the high byte must be written before the low byte. For a 16-bit read, the low byte must be read before the high byte. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 137: Psc Description

Atmel ATmega16/32/64/M1/C1 14.4 PSC Description Figure 14-1. Power Stage Controller Block Diagram PSC Counter Prescaler POCR0RB module 0 Waveform Generator B PSCOUT0B POCR0SB (Analog Comparator 0 Ouput) AC0O Overlap PSC Input 0 Protection POCR0RA PSCIN0 PISEL0 Waveform Generator A PSCOUT0A... -

Page 138: Functional Description

The PSC can be configured in one of two modes (1Ramp Mode or Centered Mode). This config- uration will affect the operation of all the waveform generators. Figure 14-2. Cycle Presentation in One Ramp Mode One PSC Cycle Sub-Cycle A Sub-Cycle B PSC Counter Value UPDATE Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 139 Atmel ATmega16/32/64/M1/C1 Figure 14-3. Cycle Presentation in Centered Mode One PSC Cycle PSC Counter Value UPDATE Figure 14-2 Figure 14-3 graphically illustrate the values held in the PSC counter. Centered Mode is like One Ramp Mode which counts down and then up.

- Page 140 Dead-Time B = (POCRnSBH/L - POCRnRAH/L) * 1/Fclkpsc Minimal value for Dead-Time A = 1/Fclkpsc If the overlap protection is disabled, in One-Ramp mode, PSCOUTnA and PSCOUTnB outputs can be configured to overlap each other, though in normal use this is not desirable. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 141 Atmel ATmega16/32/64/M1/C1 Figure 14-5. Controlled Start and Stop Mechanism in One-Ramp Mode POCRnRB POCRnSB POCRnRA POCRnSA PSC Counter PSCOUTnA PSCOUTnB Note: See “PSC Control Register – PCTL” on page 154. (PCCYC = 1) 14.5.3.2 Center Aligned Mode In center aligned mode, the center of PSCOUTnA and PSCOUTnB signals are centered.

-

Page 142: Update Of Values

With Set i With Set i With Set i With Set i Cycle With Set j End of Cycle The software can stop the cycle before the end to update the values and restart a new PSC cycle. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 143: Overlap Protection

For ATmega16/64M1, and ATmega32M1 since rev C, the overlap protection is activated with only one condition: 1. POVENn=0 (PSC Module n Overlap Enable) Up to rev B of ATmega32M1, the overlap protection was activated with the 2 following conditions: 2. POVENn=0 (PSC Module n Overlap Enable) 3. -

Page 144: Signal Description

14.8 Signal Description Figure 14-9. PSC External Block View POCRRB[11:0] PSCOUT0A PSCOUT0B POCR0SB[11:0] PSCOUT1A POCR0RA[11:0] PSCOUT1B POCR0SA[11:0] PSCOUT2A POCR1SB[11:0] PSCOUT2B POCR1RA[11:0] AC2O POCR1SA[11:0] AC1O POCR2SB[11:0] AC0O POCR2RA[11:0] PSCIN2 PSCIN1 POCR2SA[11:0] PSCIN0 IRQ PSC PSCASY Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 145 Atmel ATmega16/32/64/M1/C1 14.8.1 Input Description Table 14-1. Internal Inputs Type Name Description Width Register Compare Value which Reset Signal on Part B POCR_RB[11:0] (PSCOUTnB) 12 bits Register POCRnSB[11:0] Compare Value which Set Signal on Part B (PSCOUTnB) 12 bits Register...

-

Page 146: Psc Input

For detailed information on the PSC, please refer to Application Note ‘AVR138: PSC Cookbook’, available on the Atmel web site. Each module 0, 1 and 2 of PSC has its own system to take into account one PSC input. Accord- ing to PSC Module n Input Control Register (See “PSC Module n Input Control Register –... - Page 147 Atmel ATmega16/32/64/M1/C1 Figure 14-11. PSC Input Filterring Digital PSC Module n Input Filter 4 x CLK PSC Input Ouput PSCOUTnX Module X Stage 14.9.1.2 Signal Polarity One can select the active edge (edge modes) or the active level (level modes) See PELEVnx bit description in Section "PSC Module n Input Control Register –...

-

Page 148: Psc Input Modes 001B To 10Xb: Deactivate Outputs Without Changing Timing

14.11 PSC Input Mode 11xb: Halt PSC and Wait for Software Action Figure 14-14. PSC behaviour versus PSCn Input A in Fault Mode 11xb DT0 OT0 PSCOUTnA PSCOUTnB PSCn Input Software Action (1) Note: Software action is the setting of the PRUNn bit in PCTLn register. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 149: Analog Synchronization

Atmel ATmega16/32/64/M1/C1 Used in Fault mode 7, PSCn Input A or PSCn Input B act indifferently on On-Time0/Dead-Time0 or on On-Time1/Dead-Time1. 14.12 Analog Synchronization Each PSC module generates a signal to synchronize the ADC sample and hold; synchronisation is mandatory for measurements. -

Page 150: Interrupts

• PSC_Fault (Fault Event): When enabled and when a PSC input detects a Fault event. 14.15.2 PSC Interrupt Vectors in ATmega16/32/64/M1/C1 Table 14-7. PSC Interrupt Vectors Vector Program Address Source Interrupt Definition 0x0004 PSC_Fault PSC Fault event 0x0005 PSC_End PSC End of Cycle Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 151: Psc Register Definition

Atmel ATmega16/32/64/M1/C1 14.16 PSC Register Definition Registers are explained for PSC module 0. They are identical for module 1 and module 2. 14.16.1 PSC Output Configuration – POC POEN2B POEN2A POEN1B POEN1A POEN0B POEN0A Read/Write Initial Value • Bit 7 – not use not use •... - Page 152 Send signal on match with OCRnRA (during counting down of PSC). The min value of OCRnRA must be 1. Send signal on match with OCRnRA (during counting up of PSC). The min value of OCRnRA must be 1. no synchronization signal no synchronization signal Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 153 Atmel ATmega16/32/64/M1/C1 14.16.3 PSC Output Compare SA Register – POCRnSAH and POCRnSAL – – – – POCRnSA[11:8] POCRnSAH POCRnSA[7:0] POCRnSAL Read/Write Initial Value 14.16.4 PSC Output Compare RA Register – POCRnRAH and POCRnRAL – – – – POCRnRA[11:8] POCRnRAH POCRnRA[7:0]...

- Page 154 • Bit 5 – PCLKSEL: PSC Input Clock Select This bit is used to select between CLK or CLK clocks. Set this bit to select the fast clock input (CLK Clear this bit to select the slow clock input (CLK Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 155 Atmel ATmega16/32/64/M1/C1 • Bit 4:3:2 – SWAPn: SWAP Funtion Select (not implemented in ATmega32M1 up to revision C) When this bit is set; the channels PSCOUTnA and PSCOUTnB are exchanged. This allows to invert the waveforms of both channels at one time.

- Page 156 When this bit is set, an external event which can generates a fault on module 0 generates also an interrupt. • Bit 0 – PEOPE : PSC End Of Cycle Interrupt Enable When this bit is set, an interrupt is generated when PSC reaches the end of the whole cycle. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 157 Atmel ATmega16/32/64/M1/C1 14.16.11 PSC Interrupt Flag Register – PIFR PEV2 PEV1 PEV0 PEOP PIFR Read/Write Initial Value • Bit 7:4 – not use not use. • Bit 3 – PEV2 : PSC External Event 2 Interrupt This bit is set by hardware when an external event which can generates a fault on module 2 occurs.

-

Page 158: Serial Peripheral Interface - Spi

Double Speed (CK/2) Master SPI Mode Figure 15-1. SPI Block Diagram SPIPS MISO MISO MOSI MOSI DIVIDER /2/4/8/16/32/64/128 SS_A Note: 1. Refer to Figure 1-1 on page 3, and Table 9-3 on page 69 for SPI pin placement. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 159 Atmel ATmega16/32/64/M1/C1 The interconnection between Master and Slave CPUs with SPI is shown in Figure 15-2. The sys- tem consists of two shift Registers, and a Master clock generator. The SPI Master initiates the communication cycle when pulling low the Slave Select SS pin of the desired Slave. Master and Slave prepare the data to be sent in their respective shift Registers, and the Master generates the required clock pulses on the SCK line to interchange data.

- Page 160 DDR_SPI in the examples must be replaced by the actual Data Direction Register controlling the SPI pins. DD_MOSI, DD_MISO and DD_SCK must be replaced by the actual data direction bits for these pins. E.g. if MOSI is placed on pin PB2, replace DD_MOSI with DDB2 and DDR_SPI with DDRB. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 161 Atmel ATmega16/32/64/M1/C1 Assembly Code Example SPI_MasterInit: ; Set MOSI and SCK output, all others input r17,(1<<DD_MOSI)|(1<<DD_SCK) DDR_SPI,r17 ; Enable SPI, Master, set clock rate fck/16 r17,(1<<SPE)|(1<<MSTR)|(1<<SPR0) SPCR,r17 SPI_MasterTransmit: ; Start transmission of data (r16) SPDR,r16 Wait_Transmit: ; Wait for transmission complete...

- Page 162 /* Enable SPI */ SPCR = (1<<SPE); char SPI_SlaveReceive(void) /* Wait for reception complete */ while(!(SPSR & (1<<SPIF))) /* Return data register */ return SPDR; Note: 1. The example code assumes that the part specific header file is included. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 163: Ss Pin Functionality

Atmel ATmega16/32/64/M1/C1 15.2 SS Pin Functionality 15.2.1 Slave Mode When the SPI is configured as a Slave, the Slave Select (SS) pin is always input. When SS is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs. - Page 164 Figure 15-4 for an example. The CPOL functionality is summarized below: Table 15-3. CPHA Functionality CPHA Leading Edge Trailing Edge Sample Setup Setup Sample • Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0 Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 165 Atmel ATmega16/32/64/M1/C1 These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the clk frequency f is shown in clkio the following table: Table 15-4.

-

Page 166: Data Modes

CHANGE 0 MISO PIN MSB first (DORD = 0) Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 LSB first (DORD = 1) Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 167 Atmel ATmega16/32/64/M1/C1 Figure 15-4. SPI Transfer Format with CPHA = 1 SCK (CPOL = 0) mode 1 SCK (CPOL = 1) mode 3 SAMPLE I MOSI/MISO CHANGE 0 MOSI PIN CHANGE 0 MISO PIN MSB first (DORD = 0) Bit 6...

-

Page 168: Controller Area Network - Can

The priorities are laid down during system design in the form of corresponding binary values and cannot be changed dynamically. The identifier with the lowest binary number has the highest priority. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 169 Atmel ATmega16/32/64/M1/C1 Bus access conflicts are resolved by bit-wise arbitration on the identifiers involved by each node observing the bus level bit for bit. This happens in accordance with the "wired and" mechanism, by which the dominant state overwrites the recessive state. The competition for bus allocation is lost by all nodes with recessive transmission and dominant observation.

- Page 170 One CAN bit time is specified as four non-overlapping time segments. Each segment is con- structed from an integer multiple of the Time Quantum. The Time Quantum or TQ is the smallest discrete timing resolution used by a CAN node. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 171 Atmel ATmega16/32/64/M1/C1 Figure 16-3. CAN Bit Construction CAN Frame (producer) Transmission Point (producer) Nominal CAN Bit Time Time Quantum (producer) Segments SYNC_SEG PROP_SEG PHASE_SEG_1 PHASE_SEG_2 (producer) propagation delay Segments SYNC_SEG PROP_SEG PHASE_SEG_1 PHASE_SEG_2 (consumer) Sample Point 16.2.3.2 Synchronization Segment The first segment is used to synchronize the various bus nodes.

- Page 172 It is the time required for the logic to determine the bit level of a sampled bit. The IPT begins at the sample point, is measured in TQ and is fixed at 2TQ for the Atmel CAN. Since Phase Segment 2 also begins at the sample point and is the last segment in the bit time, PS2 minimum shall not be less than the IPT.

- Page 173 Atmel ATmega16/32/64/M1/C1 The bus access conflict is resolved during the arbitration field mostly over the identifier value. If a data frame and a remote frame with the same identifier are initiated at the same time, the data frame prevails over the remote frame (c.f. RTR bit).

-

Page 174: Can Controller

In this way, the CPU load is strongly reduced compared to a basic-CAN solution. Using full-CAN controller, high baudrates and high bus loads with many messages can be handled. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 175: Can Channel

Atmel ATmega16/32/64/M1/C1 Figure 16-5. CAN Controller Structure Low priority Control Status IDtag+IDmask Buffer MOb i Time Stamp MOb i Scanning Control Status IDtag+IDmask Buffer MOb2 Gen. Control Time Stamp Gen. Status Enable MOb Internal Interrupt TxCAN MOb2 Internal Bit Timing... - Page 176 The total number of TQ in a bit time has to be programmed at least from 8 to 25. Figure 16-7. Sample and Transmission Point Bit Timing PRS (3-bit length) Sample PHS1 (3-bit length) Point Fcan (Tscl) Prescaler BRP Time Quantum Transmission PHS2 (3-bit length) Point SJW (2-bit length) Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 177 Atmel ATmega16/32/64/M1/C1 Figure 16-8. General Structure of a Bit Period Bit Rate Prescaler Tscl (TQ) one nominal bit Data Tsyns(5) Tprs Tphs1 Tphs2 Notes: 1. Phase error < 0 2. Phase error > 0 Tphs1+Tsjw Tphs2+Tsjw 3. Phase error > 0 4.

-

Page 178: Message Objects

RTR Tag Operating Mode Disabled Tx Data Frame Tx Remote Frame Rx Data Frame Rx Remote Frame Rx Remote Frame then, Tx Data Frame (reply) Frame Buffer Receive Mode 16.5.2.1 Disabled In this mode, the MOb is “free”. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 179 Atmel ATmega16/32/64/M1/C1 16.5.2.2 Tx Data & Remote Frame 1. Several fields must be initialized before sending: – Identifier tag (IDT) – Identifier extension (IDE) – Remote transmission request (RTRTAG) – Data length code (DLC) – Reserved bit(s) tag (RBnTAG) – Data bytes of message (MSG) 2.

- Page 180 Upon a reception hit (i.e., a good comparison between the ID + RTR + RBn + IDE received and an IDT+ RTRTAG + RBnTAG + IDE specified while taking the comparison mask into account) the IDT + RTRTAG + RBnTAG + IDE received are updated in the MOb (written over the registers). Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 181 Atmel ATmega16/32/64/M1/C1 Figure 16-10. Acceptance Filter Block Diagram internal RxDcan Rx Shift Register (internal) ID & RB 14(33) RB excluded Hit MOb[i] 13(31) Write Enable 14(33) 13(31) - RB excluded 13(31) ID & RB RTRTAG IDMSK RTRMSK IDEMSK CANIDT Registers & CANCDMOB (MOb[i])

-

Page 182: Can Timer

16.6.4 Stamping Message The capture of the timer value is done in the MOb which receives or sends the frame. All man- aged MOb are stamped, the stamping of a received (sent) frame occurs on RxOk (TXOK). Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 183: Error Management

Atmel ATmega16/32/64/M1/C1 16.7 Error Management 16.7.1 Fault Confinement The CAN channel may be in one of the three following states: • Error active (default): The CAN channel takes part in bus communication and can send an active error frame when the CAN macro detects an error. -

Page 184: Interrupts

• Interrupt on frame buffer full, • Interrupt on “Bus Off” setting, • Interrupt on overrun of CAN timer. The general interrupt enable is provided by ENIT bit and the specific interrupt enable for CAN timer overrun is provided by ENORVT bit. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 185 Atmel ATmega16/32/64/M1/C1 Figure 16-14. CAN Controller Interrupt Structure CANGIE.4 CANGIE.5 CANGIE.3 ENTX ENRX ENERR CANSIT 1/2 SIT[i] CANSTMOB.6 TXOK[i] CANIE 1/2 CANSTMOB.5 RXOK[i] IEMOB[i] CANSTMOB.4 BERR[i] CANSTMOB.3 SERR[i] CANGIT.7 CANSTMOB.2 CERR[i] CANIT CANSTMOB.1 FERR[i] CANGIE.7 CANGIE.2 CANGIE.1 CANGIE.6 CANSTMOB.0 AERR[i]...

-

Page 186: Can Register Description

0 ID Mask 1 MOb0 - ID Mask 1 Time Stamp Low MOb0 - Time Stamp Low Time Stamp High MOb0 - Time Stamp High Message Data MOb0 - Mess. Data - byte 0 8 bytes Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 187: General Can Registers

Atmel ATmega16/32/64/M1/C1 16.10 General CAN Registers 16.10.1 CAN General Control Register - CANGCON ABRQ OVRQ SYNTTC LISTEN TEST ENA/STB SWRES CANGCON Read/Write Initial Value • Bit 7 – ABRQ: Abort Request This is not an auto resettable bit. – 0 - no request. - Page 188 • Bit 3 – RXBSY: Receiver Busy This flag does not generate an interrupt. – 0 - receiver not busy – 1 - receiver busy: set by hardware as long as a frame is received or monitored. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 189 Atmel ATmega16/32/64/M1/C1 • Bit 2 – ENFG: Enable Flag This flag does not generate an interrupt. – 0 - CAN controller disable: because an enable/standby command is not immediately effective, this status gives the true state of the chosen mode.

- Page 190 – 0 - interrupt disabled. – 1- CANIT interrupt enabled. • Bit 6 – ENBOFF: Enable Bus Off Interrupt – 0 - interrupt disabled. – 1- bus off interrupt enabled. • Bit 5 – ENRX: Enable Receive Interrupt Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 191 Atmel ATmega16/32/64/M1/C1 – 0 - interrupt disabled. – 1- receive interrupt enabled. • Bit 4 – ENTX: Enable Transmit Interrupt – 0 - interrupt disabled. – 1- transmit interrupt enabled. • Bit 3 – ENERR: Enable MOb Errors Interrupt – 0 - interrupt disabled.

- Page 192 BRP5 BRP4 BRP3 BRP2 BRP1 BRP0 CANBT1 Read/Write Initial Value • Bit 7– Reserved Bit This bit is reserved for future use. For compatibility with future devices, it must be written to zero when CANBT1 is written. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 193 Atmel ATmega16/32/64/M1/C1 • Bit 6:1 – BRP5:0: Baud Rate Prescaler The period of the CAN controller system clock Tscl is programmable and determines the individ- ual bit timing. BRP[5:0] Tscl -------------------------------------- - frequency If ‘BRP[5..0]=0’, see Section 16.4.3 “Baud Rate” on page 177 Section •...

- Page 194 • Bit 7:0 – TPRSC7:0: CAN Timer Prescaler Prescaler for the CAN timer upper counter range 0 to 255. It provides the clock to the CAN timer if the CAN controller is enabled. x 8 x (CANTCON [7:0] + 1) CANTIM Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 195 Atmel ATmega16/32/64/M1/C1 16.10.12 CAN Timer Registers - CANTIML and CANTIMH CANTIM7 CANTIM6 CANTIM5 CANTIM4 CANTIM3 CANTIM2 CANTIM1 CANTIM0 CANTIML CANTIM15 CANTIM14 CANTIM13 CANTIM12 CANTIM11 CANTIM10 CANTIM9 CANTIM8 CANTIMH Read/Write Initial Value • Bits 15:0 - CANTIM15:0: CAN Timer Count CAN timer counter range 0 to 65,535.

-

Page 196: Mob Registers

The communication enabled by reception is completed. RxOK rises at the end of the 6 bit of EOF field. In case of two or more message object reception hits, the lower MOb index (0 to 14) is updated first. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 197 Atmel ATmega16/32/64/M1/C1 • Bit 4 – BERR: Bit Error (Only in Transmission) This flag can generate an interrupt. It must be cleared using a read-modify-write software routine on the whole CANSTMOB register. The bit value monitored is different from the bit value sent.

- Page 198 IDT11 IDT10 IDT9 IDT8 IDT7 IDT6 IDT5 CANIDT3 IDT20 IDT19 IDT18 IDT17 IDT16 IDT15 IDT14 IDT13 CANIDT2 IDT28 IDT27 IDT26 IDT25 IDT24 IDT23 IDT22 IDT21 CANIDT1 31/23 30/22 29/21 28/20 27/19 26/18 25/17 24/16 Read/Write Initial Value Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 199 Atmel ATmega16/32/64/M1/C1 V2.0 part A • Bit 31:21 – IDT10:0: Identifier Tag Identifier field of the remote or data frame to send. This field is updated with the corresponding value of the remote or data frame received. • Bit 20:3 – Reserved Bits These bits are reserved for future use.

- Page 200 – 1 - bit comparison enabled. V2.0 part B • Bit 31:3 – IDMSK28:0: Identifier Mask – 0 - comparison true forced - See “Acceptance Filter” on page 180. – 1 - bit comparison enabled. - See “Acceptance Filter” on page 180. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 201 Atmel ATmega16/32/64/M1/C1 • Bit 2 – RTRMSK: Remote Transmission Request Mask – 0 - comparison true forced – 1 - bit comparison enabled. • Bit 1 – Reserved Bit Writing zero in this bit is recommended. • Bit 0 – IDEMSK: Identifier Extension Mask –...

-

Page 202: Examples Of Can Baud Rate Setting

75 % 0.500 0x0A 0x04 0x13 12.000 0.250 0x04 0x0E 0x4B 75 % 0.416666 0x08 0x08 0x25 0.500 0x0A 0x0C 0x37 75 % 1.000 0x16 0x04 0x13 0.500 0x0A 0x0E 0x4B 75 % 0.833333 0x12 0x08 0x25 Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 203 Atmel ATmega16/32/64/M1/C1 Table 16-2. Examples of CAN Baud Rate Settings for Commonly Frequencies (Continued) Description Segments Registers Rate Sampling Tbit Tprs Tph1 Tph2 Tsjw (MHz) (Kbps) Point (µs) (TQ) (TQ) (TQ) (TQ) (TQ) CANBT1 CANBT2 CANBT3 - - - n o...

-

Page 204: Lin / Uart - Local Interconnect Network Controller Or Uart

Full Duplex Operation (Independent Serial Receive and Transmit Processes) • Asynchronous Operation • High Resolution Baud Rate Generator • Hardware Support of 8 Data Bits, Odd/Even/No Parity Bit, 1 Stop Bit Frames • Data Over-Run and Framing Error Detection Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 205: Lin Protocol

Atmel ATmega16/32/64/M1/C1 17.3 LIN Protocol 17.3.1 Master and Slave A LIN cluster consists of one master task and several slave tasks. A master node contains the master task as well as a slave task. All other nodes contain a slave task only. -

Page 206: Lin / Uart Controller

• Rx LIN Header function, • LIN Response function. These functions mainly use two services: • Rx service, • Tx service. Because these two services are basically UART services, the controller is also able to switch into an UART function. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 207 Atmel ATmega16/32/64/M1/C1 17.4.1 LIN Overview The LIN/UART controller is designed to match as closely as possible to the LIN software appli- cation structure. The LIN software application is developed as independent tasks, several slave tasks and one master task (c.f.

- Page 208 Synchronization Monitoring Data FIFO BUFFER 17.4.4 LIN/UART Command Overview Figure 17-5. LIN/UART Command Dependencies Response Tx Header IDOK TXOK Response Rx Header RXOK LIN Abort Automatic Return Recommended DISABLE UART Possible Byte Transfer Byte Full Duplex Byte Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 209 Atmel ATmega16/32/64/M1/C1 Table 17-1. LIN/UART Command List LCMD[2 LCMD[1 LCMD[0 LENA Command Comment Disable peripheral Rx Header - LIN abort LIN withdrawal Tx Header LCMD[2..0]=000 after Tx Rx Response LCMD[2..0]=000 after Rx Tx Response LCMD[2..0]=000 after Tx Byte transfer no CRC, no Time out...

- Page 210 While the controller is sending or receiving a response, BREAK and SYNCH fields can be detected and the identifier of this new header will be recorded. Of course, specific errors on the previous response will be maintained with this identifier reception. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 211 Atmel ATmega16/32/64/M1/C1 17.4.6.4 Handling Data of LIN response A FIFO data buffer is used for data of the LIN response. After setting all parameters in the LIN- SEL register, repeated accesses to the LINDAT register perform data read or data write (c.f.

-

Page 212: Lin / Uart Description

• LIN13 = 1: LIN 1.3 protocol. The controller checks the LIN13 bit in computing the checksum (enhanced checksum in LIN2.1 / classic checksum in LIN 1.3). See “Rx & TX Response Functions” on page 210. This bit is irrelevant for UART commands. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 213 Atmel ATmega16/32/64/M1/C1 17.5.4 Configuration Depending on the mode (LIN or UART), LCONF[1..0] bits of the LINCR register set the controller in the following configuration (Table 17-3): Table 17-3. Configuration Table versus Mode Mode LCONF[1..0] Configuration LIN standard configuration (default) No CRC field detection or transmission...

- Page 214 Equation for calculating baud rate: BAUD = / LBT[5..0] x (LDIV[11..0] + 1) Equation for setting LINDIV value: LDIV[11..0] = ( / LBT[5..0] x BAUD ) - 1 Note that in reception a majority vote on three samplings is made. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 215 Atmel ATmega16/32/64/M1/C1 17.5.6.2 Re-synchronization in LIN Mode When waiting for Rx Header, LBT[5..0] = 32 in LINBTR register. The re-synchronization begins when the BREAK is detected. If the BREAK size is not in the range (11 bits min., 28 bits max. —...

- Page 216 • If an error occurs, Rx stops, the corresponding error flag is set and LTXDL will give the number of received bytes without error, • If no error occurs, LRXOK is set after the reception of the CHECKSUM, LRXDL will be unchanged (and LTXDL = LRXDL). Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 217 Atmel ATmega16/32/64/M1/C1 17.5.7.4 Data Length in Tx Response Figure 17-10. LIN1.3 - Tx Response - No error LIDOK LTXOK Byte Byte Byte Byte DATA-0 DATA-1 DATA-2 DATA-3 CHECKSUM LIN bus LRXDL (*) LTXDL (*) LBUSY LCMD2..0=000 LCMD=Tx Response (*) : LRXDL & LTXDL updated by Rx Response or Tx Response task •...

- Page 218 SYNCH and Frame_Maximum IDENTIFIER fields (see Section 17.5.10 “Frame Time Out” on page 219). • LOVERR = LIN OVerrun ERRor. Overrun error will be flagged if a new command (other than LIN Abort) is entered while ‘Busy Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 219 Atmel ATmega16/32/64/M1/C1 signal’ is present. In UART mode, an overrun error will be flagged if a received byte overwrites the byte stored in the serial input buffer. • LABORT LIN abort transfer reflects a previous LIN Abort command (LCMD[2..0] = 000) while ‘Busy signal’...

- Page 220 221, the four communication flags of the LINSIR register are combined to drive two interrupts. Each of these flags have their respective enable interrupt bit in LINENIR register. (see Section 17.5.8 “xxOK Flags” on page 218 Section 17.5.9 “xxERR Flags” on page 218). Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 221 Atmel ATmega16/32/64/M1/C1 Figure 17-13. LIN Interrupt Mapping LINERR.7 LABORT LINERR.6 LTOERR LINERR.5 LOVERR LINERR.4 LINSIR.3 LFERR LIN ERR LERR LINERR.3 LSERR LINENIR.3 LINENIR.2 LINENIR.1 LINENIR.0 LINERR.2 LPERR LENERR LENIDOK LENTXOK LENRXOK LINERR.1 LINSIR.2 LCERR LIDOK LINERR.0 LINSIR.1 LBERR LIN IT LTXOK LINSIR.0...

- Page 222 - Note that LAINC has no more effect on the auto-incrementation and the access to the full FIFO is done setting LINDX[2..0] of LINSEL. Note: When a debugger break occurs, the state machine of the LIN/UART controller is stopped (included frame time-out) and further communication may be corrupted. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 223: Lin / Uart Register Description

Atmel ATmega16/32/64/M1/C1 17.6 LIN / UART Register Description Table 17-5. LIN/UART Register Bits Summary Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 LSWRES LIN13 LCONF1 LCONF0 LENA LCMD2 LCMD1 LCMD0 LINCR... - Page 224 – 101 = Identifier 61 (0x3D), – 110 = Identifier 62 (0x3E), – 111 = Identifier 63 (0x3F). • Bit 4 - LBUSY: Busy Signal – 0 = Not busy, – 1 = Busy (receiving or transmitting). Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 225 Atmel ATmega16/32/64/M1/C1 • Bit 3 - LERR: Error Interrupt It is a logical OR of LINERR register bits. This bit generates an interrupt if its respective enable bit - LENERR - is set in LINENIR. – 0 = No error, –...

- Page 226 • Bit 3 - LSERR: Synchronization Error Flag – 0 = No error, – 1 = Synchronization error. This bit is cleared when LERR bit in LINSIR is cleared. • Bit 2 - LPERR: Parity Error Flag – 0 = No error, Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 227 Atmel ATmega16/32/64/M1/C1 – 1 = Parity error. This bit is cleared when LERR bit in LINSIR is cleared. • Bit 1 - LCERR: Checksum Error Flag – 0 = No error, – 1 = Checksum error. This bit is cleared when LERR bit in LINSIR is cleared.

- Page 228 In LIN 1.3 mode: 4-bit identifier. In UART mode this field is unused. • Bits 5:0 - LID[5:0]: LIN 2.1 Identifier In LIN 2.1 mode: 6-bit identifier (no length transported). In UART mode this field is unused. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

- Page 229 Atmel ATmega16/32/64/M1/C1 17.6.9 LIN Data Buffer Selection Register - LINSEL LAINC LINDX2 LINDX1 LINDX0 LINSEL Read/Write Initial Value • Bits 7:4 - Reserved Bits These bits are reserved for future use. For compatibility with future devices, they must be written to zero when LINSEL is written.

-

Page 230: Analog To Digital Converter - Adc

On-chip. The voltage refer- ence may be externally decoupled at the AREF pin by a capacitor (e.g., 10 nF) for better noise performance. In any case this capacitor shout not be greater than 10% of the AVCC smoothing capacitor. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... - Page 231 Atmel ATmega16/32/64/M1/C1 Figure 18-1. Analog to Digital Converter Block Schematic Current Source ISRCEN AREF / ISRC ISRC AREFEN AVCC Internal 2.56V Reference REFS0 REFS1 ADC0 ADC1 ADC2 ADC3 ADC4 Coarse/Fine DAC ADC5 AMP2-/ADC6 ADC7 ADCH AMP1-/ADC8 AMP1+/ADC9 ADCL ADC10 AMP0-...

-

Page 232: Operation

Global Interrupt Enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the interrupt flag must be cleared in order to trigger a new conversion at the next interrupt event. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12... -

Page 233: Prescaling And Conversion Timing

Atmel ATmega16/32/64/M1/C1 Figure 18-2. ADC Auto Trigger Logic ADTS[2:0] PRESCALER START ADIF ADATE SOURCE 1 CONVERSION LOGIC EDGE DETECTOR SOURCE n ADSC Using the ADC Interrupt Flag as a trigger source makes the ADC start a new conversion as soon as the ongoing conversion has finished. - Page 234 Figure 18-5. ADC Timing Diagram, Single Conversion One Conversion Next Conversion Cycle Number ADC Clock ADSC ADIF ADCH Sign and MSB of Result ADCL LSB of Result Sample & Hold Conversion MUX and REFS MUX and REFS Complete Update Update Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...

-

Page 235: Changing Channel Or Reference Selection

Atmel ATmega16/32/64/M1/C1 Figure 18-6. ADC Timing Diagram, Auto Triggered Conversion One Conversion Next Conversion Cycle Number ADC Clock Trigger Source ADATE ADIF ADCH Sign and MSB of Result ADCL LSB of Result Sample & Prescaler Conversion Prescaler Hold Reset Complete... - Page 236 When The ADC and COMPARATOR share the same channel (Possible configuration for AMP1+, AMP1- and AMP2-), up to revision B of ATmega32M1 the comparator is disconnected during the sampling of the ADC. For ATmega16/64 and ATmega32 revision C, the COMPARATOR is always connected.

-

Page 237: Adc Noise Canceler

Atmel ATmega16/32/64/M1/C1 If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between AV and 2.56V as... - Page 238 (LSBs). The lowest code is read as 0, and the highest code is read as 2 Several parameters describe the deviation from the ideal behavior: • Offset: The deviation of the first transition (0x000 to 0x001) compared to the ideal transition (at 0.5 LSB). Ideal value: 0 LSB. Atmel ATmega16/32/64/M1/C1 7647H–AVR–03/12...