Table of Contents

Advertisement

Quick Links

Features

•

High-performance, Low-power AVR

•

Advanced RISC Architecture

– 131 Powerful Instructions – Most Single-clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

•

Nonvolatile Program and Data Memories

– 32K Bytes of In-System Self-Programmable Flash

Endurance: 10,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 1024 Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 2K Byte Internal SRAM

– Programming Lock for Software Security

•

JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

•

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture

Mode

– Real Time Counter with Separate Oscillator

– Four PWM Channels

– 8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels in TQFP Package Only

2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

– Byte-oriented Two-wire Serial Interface

– Programmable Serial USART

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

•

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby

and Extended Standby

•

I/O and Packages

– 32 Programmable I/O Lines

– 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF

•

Operating Voltages

– 2.7 - 5.5V for ATmega32L

– 4.5 - 5.5V for ATmega32

•

Speed Grades

– 0 - 8 MHz for ATmega32L

– 0 - 16 MHz for ATmega32

•

Power Consumption at 1 MHz, 3V, 25°C for ATmega32L

– Active: 1.1 mA

– Idle Mode: 0.35 mA

– Power-down Mode: < 1 µA

®

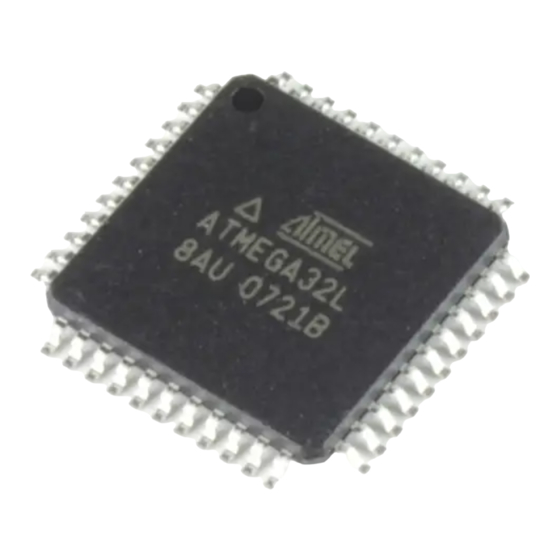

8-bit Microcontroller

8-bit

Microcontroller

with 32K Bytes

In-System

Programmable

Flash

ATmega32

ATmega32L

Advertisement

Table of Contents

Summary of Contents for Atmel AVR ATmega32

- Page 1 Features ® • High-performance, Low-power AVR 8-bit Microcontroller • Advanced RISC Architecture – 131 Powerful Instructions – Most Single-clock Cycle Execution – 32 x 8 General Purpose Working Registers – Fully Static Operation – Up to 16 MIPS Throughput at 16 MHz –...

-

Page 2: Pin Configurations

Pin Configurations Figure 1. Pinout ATmega32 PDIP (XCK/T0) PB0 PA0 (ADC0) (T1) PB1 PA1 (ADC1) (INT2/AIN0) PB2 PA2 (ADC2) (OC0/AIN1) PB3 PA3 (ADC3) (SS) PB4 PA4 (ADC4) (MOSI) PB5 PA5 (ADC5) (MISO) PB6 PA6 (ADC6) (SCK) PB7 PA7 (ADC7) RESET AREF AVCC XTAL2... -

Page 3: Block Diagram

ATmega32(L) Overview The ATmega32 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega32 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed. Block Diagram Figure 2. -

Page 4: Pin Descriptions

Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega32 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications. - Page 5 ATmega32(L) Port B (PB7..PB0) Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated.

- Page 6 Resources A comprehensive set of development tools, application notes and datasheets are avail- able for download on http://www.atmel.com/avr. ATmega32(L)

-

Page 7: About Code Examples

ATmega32(L) About Code This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is Examples included before compilation. Be aware that not all C Compiler vendors include bit defini- tions in the header files and interrupt handling in C is compiler dependent. -

Page 8: Avr Cpu Core

AVR CPU Core Introduction This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts. Architectural Overview Figure 3. - Page 9 ATmega32(L) an arithmetic operation, the Status Register is updated to reflect information about the result of the operation. Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format.

-

Page 10: Status Register

Status Register The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. -

Page 11: General Purpose Register File

ATmega32(L) • Bit 0 – C: Carry Flag The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruc- tion Set Description” for detailed information. General Purpose The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are Register File supported by the Register File:... -

Page 12: Stack Pointer

The X-register, Y-register and The registers R26..R31 have some added functions to their general purpose usage. Z-register These registers are 16-bit address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z are defined as described in Figure 5. Figure 5. -

Page 13: Instruction Execution Timing

ATmega32(L) Instruction Execution This section describes the general access timing concepts for instruction execution. The Timing AVR CPU is driven by the CPU clock clk , directly generated from the selected clock source for the chip. No internal clock division is used. Figure 6 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. - Page 14 – the External Interrupt Request 0. The Interrupt Vectors can be moved to the start of the Boot Flash section by setting the IVSEL bit in the General Interrupt Control Register (GICR). Refer to “Interrupts” on page 44 for more information. The Reset Vector can also be moved to the start of the boot Flash section by programming the BOOTRST fuse, see “Boot Loader Support –...

-

Page 15: Interrupt Response Time

ATmega32(L) When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example. Assembly Code Example ; set global interrupt enable sleep ; enter sleep, waiting for interrupt ;... -

Page 16: In-System Reprogrammable Flash Program Memory

AVR ATmega32 This section describes the different memories in the ATmega32. The AVR architecture has two main memory spaces, the Data Memory and the Program Memory space. In Memories addition, the ATmega32 features an EEPROM Memory for data storage. All three mem- ory spaces are linear and regular. -

Page 17: Sram Data Memory

ATmega32(L) SRAM Data Memory Figure 9 shows how the ATmega32 SRAM Memory is organized. The lower 2144 Data Memory locations address the Register File, the I/O Memory, and the internal data SRAM. The first 96 locations address the Register File and I/O Mem- ory, and the next 2048 locations address the internal data SRAM. -

Page 18: Eeprom Data Memory

Data Memory Access Times This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two clk cycles as described in Figure Figure 10. On-chip Data SRAM Access Cycles Address Address Valid Compute Address Data Data... - Page 19 ATmega32(L) The EEPROM Address Register – EEARH and EEARL – – – – – – EEAR9 EEAR8 EEARH EEAR7 EEAR6 EEAR5 EEAR4 EEAR3 EEAR2 EEAR1 EEAR0 EEARL Read/Write Initial Value • Bits 15..10 – Res: Reserved Bits These bits are reserved bits in the ATmega32 and will always read as zero. •...

- Page 20 When EEMWE has been written to one by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for an EEPROM write procedure. • Bit 1 – EEWE: EEPROM Write Enable The EEPROM Write Enable Signal EEWE is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be written to one to write the value into the EEPROM.

- Page 21 ATmega32(L) Note: 1. Uses 1 MHz clock, independent of CKSEL Fuse setting. The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (for example by dis- abling interrupts globally) so that no interrupts will occur during execution of these functions.

-

Page 22: Eeprom Write During Power- Down Sleep Mode

The next code examples show assembly and C functions for reading the EEPROM. The examples assume that interrupts are controlled so that no interrupts will occur during execution of these functions. Assembly Code Example EEPROM_read: ; Wait for completion of previous write sbic EECR,EEWE rjmp EEPROM_read ;... - Page 23 ATmega32(L) E E P R O M d a t a c o r r u p t i o n c a n e a s i l y b e a v o i d e d b y f o l l o w i n g t h i s d e s i g n recommendation: Keep the AVR RESET active (low) during periods of insufficient power supply volt- age.

-

Page 24: System Clock And Clock Options

System Clock and Clock Options Clock Systems and their Figure 11 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the Distribution clocks to modules not being used can be halted by using different sleep modes, as described in “Power Management and Sleep Modes”... -

Page 25: Default Clock Source

ATmega32(L) Asynchronous Timer Clock – The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external 32 kHz clock crystal. The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode. ADC Clock –... -

Page 26: Crystal Oscillator

Crystal Oscillator XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 12. Either a quartz crystal or a ceramic resonator may be used. The CKOPT Fuse selects between two dif- ferent Oscillator amplifier modes. - Page 27 ATmega32(L) The CKSEL0 Fuse together with the SUT1..0 fuses select the start-up times as shown in Table 5. Table 5. Start-up Times for the Crystal Oscillator Clock Selection Start-up Time from Additional Delay Power-down and from Reset CKSEL0 SUT1..0 Power-save = 5.0V) Recommended Usage Ceramic resonator, fast...

-

Page 28: Low-Frequency Crystal Oscillator

Low-frequency Crystal To use a 32.768 kHz watch crystal as the clock source for the device, the Low-fre- Oscillator quency Crystal Oscillator must be selected by setting the CKSEL fuses to “1001”. The crystal should be connected as shown in Figure 12. By programming the CKOPT Fuse, the user can enable internal capacitors on XTAL1 and XTAL2, thereby removing the need for external capacitors. -

Page 29: Calibrated Internal Rc Oscillator

RC Oscillator. At 5V, 25°C and 1.0 MHz Oscillator frequency selected, this calibration gives a frequency within ± 3% of the nominal frequency. Using calibration methods as described in application notes available at www.atmel.com/avr it is possible to achieve ± 1% accuracy at any given V and Temperature. - Page 30 When this Oscillator is selected, start-up times are determined by the SUT fuses as shown in Table 10. XTAL1 and XTAL2 should be left unconnected (NC). Table 10. Start-up Times for the Internal Calibrated RC Oscillator Clock Selection Start-up Time from Additional Delay Power-down and from Reset...

-

Page 31: External Clock

ATmega32(L) External Clock To drive the device from an external clock source, XTAL1 should be driven as shown in Figure 14. To run the device on an external clock, the CKSEL fuses must be pro- grammed to “0000”. By programming the CKOPT Fuse, the user can enable an internal 36 pF capacitor between XTAL1 and GND. -

Page 32: Power Management And Sleep Modes

Power Management Sleep modes enable the application to shut down unused modules in the MCU, thereby saving power. The AVR provides various sleep modes allowing the user to tailor the and Sleep Modes power consumption to the application’s requirements. To enter any of the six sleep modes, the SE bit in MCUCR must be written to logic one and a SLEEP instruction must be executed. -

Page 33: Idle Mode

ATmega32(L) Idle Mode When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing SPI, USART, Analog Comparator, ADC, Two- wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. -

Page 34: Extended Standby Mode

Asynchronous Timer should be considered undefined after wake-up in Power-save mode if AS2 is 0. This sleep mode basically halts all clocks except clk , allowing operation only of asyn- chronous modules, including Timer/Counter2 if clocked asynchronously. Standby Mode When the SM2..0 bits are 110 and an external crystal/resonator clock option is selected, the SLEEP instruction makes the MCU enter Standby mode. - Page 35 ATmega32(L) Analog Comparator When entering Idle mode, the Analog Comparator should be disabled if not used. When entering ADC Noise Reduction mode, the Analog Comparator should be disabled. In the other sleep modes, the Analog Comparator is automatically disabled. However, if the Analog Comparator is set up to use the Internal Voltage Reference as input, the Analog Comparator should be disabled in all sleep modes.

-

Page 36: System Control And Reset

System Control and Reset Resetting the AVR During Reset, all I/O Registers are set to their initial values, and the program starts exe- cution from the Reset Vector. The instruction placed at the Reset Vector must be a JMP – absolute jump – instruction to the reset handling routine. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. - Page 37 ATmega32(L) Figure 15. Reset Logic DATA BUS MCU Control and Status Register (MCUCSR) Power-on Reset Circuit Brown-out BODEN Reset Circuit BODLEVEL Pull-up Resistor SPIKE Reset Circuit FILTER JTAG Reset Watchdog Register Timer Watchdog Oscillator Delay Counters Clock TIMEOUT Generator CKSEL[3:0] SUT[1:0] Table 15.

- Page 38 Power-on Reset A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detec- tion level is defined in Table 15. The POR is activated whenever V is below the detection level. The POR circuit can be used to trigger the Start-up Reset, as well as to detect a failure in supply voltage.

- Page 39 ATmega32(L) External Reset An External Reset is generated by a low level on the RESET pin. Reset pulses longer than the minimum pulse width (see Table 15) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage –...

- Page 40 Watchdog Reset When the Watchdog times out, it will generate a short reset pulse of one CK cycle dura- tion. On the falling edge of this pulse, the delay timer starts counting the Time-out period . Refer to page 41 for details on operation of the Watchdog Timer. TOUT Figure 20.

-

Page 41: Internal Voltage Reference

ATmega32(L) Internal Voltage ATmega32 features an internal bandgap reference. This reference is used for Brown- Reference out Detection, and it can be used as an input to the Analog Comparator or the ADC. The 2.56V reference to the ADC is generated from the internal bandgap reference. Voltage Reference Enable The voltage reference has a start-up time that may influence the way it should be used. - Page 42 Watchdog Timer Control Register – WDTCR – – – WDTOE WDP2 WDP1 WDP0 WDTCR Read/Write Initial Value • Bits 7..5 – Res: Reserved Bits These bits are reserved bits in the ATmega32 and will always read as zero. • Bit 4 – WDTOE: Watchdog Turn-off Enable This bit must be set when the WDE bit is written to logic zero.

- Page 43 ATmega32(L) The following code example shows one assembly and one C function for turning off the WDT. The example assumes that interrupts are controlled (for example by disabling interrupts globally) so that no interrupts will occur during execution of these functions. Assembly Code Example WDT_off: ;...

- Page 44 Interrupts This section describes the specifics of the interrupt handling as performed in ATmega32. For a general explanation of the AVR interrupt handling, refer to “Reset and Interrupt Handling” on page 13. Interrupt Vectors in ATmega32 Table 18. Reset and Interrupt Vectors Program Vector No.

- Page 45 ATmega32(L) Table 19. Reset and Interrupt Vectors Placement BOOTRST IVSEL Reset address Interrupt Vectors Start Address $0000 $0002 $0000 Boot Reset Address + $0002 Boot Reset Address $0002 Boot Reset Address Boot Reset Address + $0002 Note: 1. The Boot Reset Address is shown in Table 99 on page 255. For the BOOTRST Fuse “1”...

- Page 46 When the BOOTRST Fuse is unprogrammed, the Boot section size set to 4K bytes and the IVSEL bit in the GICR Register is set before any interrupts are enabled, the most typical and general program setup for the Reset and Interrupt Vector Addresses is: Address Labels Code...

- Page 47 ATmega32(L) Moving Interrupts Between The General Interrupt Control Register controls the placement of the Interrupt Vector Application and Boot Space table. General Interrupt Control Register – GICR INT1 INT0 INT2 – – – IVSEL IVCE GICR Read/Write Initial Value • Bit 1 – IVSEL: Interrupt Vector Select When the IVSEL bit is cleared (zero), the Interrupt Vectors are placed at the start of the Flash memory.

- Page 48 • Bit 0 – IVCE: Interrupt Vector Change Enable The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above.

- Page 49 ATmega32(L) I/O Ports Introduction All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without uninten- tionally changing the direction of any other pin with the SBI and CBI instructions. The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input).

- Page 50 Ports as General Digital The ports are bi-directional I/O ports with optional internal pull-ups. Figure 23 shows a functional description of one I/O-port pin, here generically called Pxn. Figure 23. General Digital I/O DDxn RESET PORTxn RESET SLEEP SYNCHRONIZER PINxn WDx: WRITE DDRx PUD:...

- Page 51 ATmega32(L) enabled state is fully acceptable, as a high-impedant environment will not notice the dif- ference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports. Switching between input with pull-up and output low generates the same problem.

- Page 52 succeeding positive clock edge. As indicated by the two arrows t and t pd,max pd,min single signal transition on the pin will be delayed between ½ and 1½ system clock period depending upon the time of assertion. When reading back a software assigned pin value, a nop instruction must be inserted as indicated in Figure 25.

- Page 53 ATmega32(L) The following code example shows how to set port B pins 0 and 1 high, 2 and 3 low, and define the port pins from 4 to 7 as input with pull-ups assigned to port pins 6 and 7. The resulting pin values are read back again, but as previously discussed, a nop instruction is included to be able to read back the value recently assigned to some of the pins.

-

Page 54: Alternate Port Functions

Unconnected pins If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode). - Page 55 ATmega32(L) Table 21 summarizes the function of the overriding signals. The pin and port indexes from Figure 26 are not shown in the succeeding tables. The overriding signals are gen- erated internally in the modules having the alternate function. Table 21. Generic Description of Overriding Signals for Alternate Functions Signal Name Full Name Description...

- Page 56 Special Function I/O Register – SFIOR ADTS2 ADTS1 ADTS0 – ACME PSR2 PSR10 SFIOR Read/Write Initial Value • Bit 2 – PUD: Pull-up disable When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01).

- Page 57 ATmega32(L) Table 24. Overriding Signals for Alternate Functions in PA3..PA0 Signal Name PA3/ADC3 PA2/ADC2 PA1/ADC1 PA0/ADC0 PUOE PUOV DDOE DDOV PVOE PVOV DIEOE DIEOV – – – – ADC3 INPUT ADC2 INPUT ADC1 INPUT ADC0 INPUT Alternate Functions of Port B The Port B pins with alternate functions are shown in Table 25.

- Page 58 • MOSI – Port B, Bit 5 MOSI: SPI Master Data output, Slave Data input for SPI. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5.

- Page 59 ATmega32(L) Table 26. Overriding Signals for Alternate Functions in PB7..PB4 Signal Name PB7/SCK PB6/MISO PB5/MOSI PB4/SS PUOE SPE • MSTR SPE • MSTR SPE • MSTR SPE • MSTR PUOV PORTB7 • PUD PORTB6 • PUD PORTB5 • PUD PORTB4 • PUD DDOE SPE •...

- Page 60 Alternate Functions of Port C The Port C pins with alternate functions are shown in Table 28. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be acti- vated even if a reset occurs. Table 28.

- Page 61 ATmega32(L) • TCK – Port C, Bit 2 TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG inter- face is enabled, this pin can not be used as an I/O pin. • SDA – Port C, Bit 1 SDA, Two-wire Serial Interface Data: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface, pin PC1 is disconnected from the port and becomes the Serial Data I/O pin for the Two-wire Serial Interface.

- Page 62 Table 30. Overriding Signals for Alternate Functions in PC3..PC0 Signal Name PC3/TMS PC2/TCK PC1/SDA PC0/SCL PUOE JTAGEN JTAGEN TWEN TWEN PUOV PORTC1 • PUD PORTC0 • PUD DDOE JTAGEN JTAGEN TWEN TWEN DDOV SDA_OUT SCL_OUT PVOE TWEN TWEN PVOV DIEOE JTAGEN JTAGEN DIEOV...

- Page 63 ATmega32(L) • OC1A – Port D, Bit 5 OC1A, Output Compare Match A output: The PD5 pin can serve as an external output for the Timer/Counter1 Output Compare A. The pin has to be configured as an output (DDD5 set (one)) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

-

Page 64: Register Description For I/O Ports

Table 33. Overriding Signals for Alternate Functions in PD3..PD0 Signal Name PD3/INT1 PD2/INT0 PD1/TXD PD0/RXD PUOE TXEN RXEN PUOV PORTD0 • PUD DDOE TXEN RXEN DDOV PVOE TXEN PVOV DIEOE INT1 ENABLE INT0 ENABLE DIEOV INT1 INPUT INT0 INPUT – –... - Page 65 ATmega32(L) Port B Input Pins Address – PINB PINB7 PINB6 PINB5 PINB4 PINB3 PINB2 PINB1 PINB0 PINB Read/Write Initial Value Port C Data Register – PORTC PORTC7 PORTC6 PORTC5 PORTC4 PORTC3 PORTC2 PORTC1 PORTC0 PORTC Read/Write Initial Value Port C Data Direction Register –...

Need help?

Do you have a question about the AVR ATmega32 and is the answer not in the manual?

Questions and answers