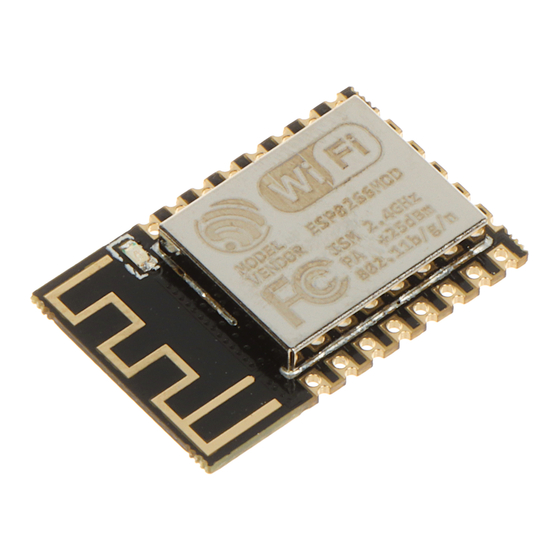

Espressif ESP8266 Technical Reference

Hide thumbs

Also See for ESP8266:

- User manual (51 pages) ,

- System description (30 pages) ,

- Manual (22 pages)

Table of Contents

Advertisement

Advertisement

Table of Contents

Summary of Contents for Espressif ESP8266

- Page 1 ESP8266 Technical Reference Version 1.0 Copyright © 2016...

- Page 3 About This Guide This document provides introduction to the interfaces integrated on ESP8266. Functional description, parameter configuration, function description, application demos and other information is included. The document is structured as below. Chapter Title Subject Chapter 1 Overview Overall introduction to the interfaces.

-

Page 5: Table Of Contents

2.3.5. Example of The Interrupt Function Processing Procedures ........3. SPI Compatibility Mode User Guide ..................3.1. Functional Overview ......................... 3.2. DEMO Solution ........................3.2.1. Introduction ......................... 3.2.2. ESP8266 Software Compiling and Downloading ............3.2.3. ESP8266 FLASH Software Downloading .............. - Page 6 ....................3.3.1. Protocol Principle: SDIO Line Breakage and SDIO Status Register ......3.3.2. Instructions on The Read/Write Buffer and The Registration Linked List ....3.3.3. API Functions in The ESP8266 DEMO ............... 3.4. STM32 Software Instruction ....................3.4.1. Important functions .....................

- Page 7 6.3.2. GPIO0 Line Breakage ....................6.4. ESP8266 SPI Slave API Functions ................... 7. SPI Wi-Fi Passthrough 2-Interrupt Mode ................7.1. Functional Overview ......................... 7.2. ESP8266 SPI Slave Protocol Format ..................7.2.1. SPI Slave Clock Polarity Configuration ..............7.2.2. Communication Format Supported by The SPI Slave ..........

- Page 8 10.3. API Function Description ......................10.3.1. Void Function ......................10.3.2. CONF Function ......................10.3.3. START Function ......................11. UART Introduction ........................ 11.1. Functional Overview ......................... 11.2. Hardware Resources ........................ 11.3. Parameter Configuration ......................11.3.1. The Baud Rate ......................11.3.2. Parity Bit ........................

- Page 9 13.IR Remote Control User Guide ..................... 13.1. Introduction to Infrared Transmission ..................13.1.1. Transmitting ........................ 13.1.2. Receiving ........................13.2. Parameters Configuration ......................13.3. Functions of Infrared Sample Codes ..................14. Sniffer Introduction ....................... 14.1. Sniffer Introduction ........................14.2. Sniffer Application Scenarios ....................

-

Page 10: Overview

Table 1-1: Pin Definitions of SDIOs Pin Name Pin Num Function Name SDIO_CLK SDIO_CLK SDIO_DATA0 SDIO_DATA0 SDIO_DATA1 SDIO_DATA1 SDIO_DATA_2 SDIO_DATA_2 SDIO_DATA_3 IO10 SDIO_DATA_3 SDIO_CMD IO11 SDIO_CMD 1.3. Serial Peripheral Interface (SPI/HSPI) ESP8266EX has 3 SPIs. One general Slave/Master SPI Espressif ! /86 2016.05... -

Page 11: General Spi (Master/Slave)

ESP8266EX has one I2C used to connect with micro-controller and other peripheral equipments such as sensors. The pin definition of I2C is as below. Table 1-4. Pin Definitions of I2C Pin Name Pin Num Function Name MTMS IO14 I2C_SCL GPIO2 I2C_SDA Espressif ! /86 2016.05... -

Page 12: I2S Interface

UART interfaces reaches 115200 x 40 (4.5 Mbps). UART0 can be used for communication. It supports fluid control. Since UART1 features only data transmit signal (Tx), it is usually used for printing log. Espressif ! /86 2016.05... -

Page 13: Pulse-Width Modulation (Pwm)

The larger the resistance value, the lower the current, so is the power, and vice versa. The transmission angle is between 15° and 30° which is determined by the radiation direction of the infrared receiver. Espressif ! /86 2016.05... -

Page 14: Sniffer

1. Overview 1.9. Sniffer ESP8266 can enter promiscuous mode (sniffer). ESP8266 can capture complete IEEE 802.11 packets in the air or it can obtain the length of the packets. Espressif ! /86 2016.05... -

Page 15: Gpio

2. GPIO GPIO 2.1. Functional Overview The ESP8266 has 16 general IOs. Their pin numbers and names are shown in the table below: Table 2-1. GPIO Pin Definition GPIO NO. Pin NO. Pin name GPIO0 pin15 GPIO0_U GPIO1 pin26 U0TXD_U... -

Page 16: Instruction On Gpio Registers

2. GPIO 2.2. Instruction on GPIO Registers 2.2.1. GPIO Function Selection Register The ESP8266 MTDI is used to demonstrate the GPIO function selection. Function selection register PERIPHS_IO_MUX_MTDI_U (this register differs for different GPIOs) PIN_FUNC_SELECT(PERIPHS_IO_MUX_MTDI_U,FUNC_GPIO12); FUNC_GPIO12=3. Configurations differ for different pins. -

Page 17: Gpio Input Register

Interrupt type register GPIO_PIN12 (this register differs for different GPIOs) • bit[9:7] (readable and writable): 0: the GPIO interrupt is disabled 1: rising edge triggered interrupt 2: falling edge triggered interrupt 3: double-edge triggered interrupt 4: low level 5: high level Espressif ! /! 8 86 2016.05... -

Page 18: Gpio16 Related Apis

PERIPHS_IO_MUX_MTDI_U are set to be 1, the MTDI is configured to the GPIO mode. For details of PERIPHS_IO_MUX_MTDI_U register, refer to Section 2.2, Instruction on GPIO Register. 2. Configure the MTDI output high level. GPIO_OUTPUT_SET(GPIO_ID_PIN(12), 1); Espressif ! /! 9 86 2016.05... -

Page 19: Parameter Configuration For Scene 2

GPIO_INPUT_GET(GPIO_ID_PIN(12)) gets the status of bit 12 of GPIO_IN register. The value of this register shows the input level of related pin. (Enable the input function of the related pin first to get effective register status) Espressif 10 86 2016.05... -

Page 20: Parameter Configuration For Scene 3

! Note: If users want to disable the MTDI interrupt function, write 0x02 into bit[9:7] of GPIO_PIN12 register. For other interrupt triggering mode configuration, refer to 2.2 Instruction on GPIO Registers. 6. Enable the GPIO interrupt. Espressif 11 86 2016.05... -

Page 21: Interrupt Function Processing Procedures

3. If it is double-edge triggered interrupt, check whether this interrupt is triggered by rising or falling edge. if(!GPIO_INPUT_GET(GPIO_ID_PIN(12))) //if this MTDI interrupt is triggered by falling edge. 2.3.5. Example of The Interrupt Function Processing Procedures Espressif 12 86 2016.05... -

Page 22: Spi Compatibility Mode User Guide

Therefore, the SDIO module communication protocol should be used. The ESP8266 should start in the SDIO mode, and then, the host will start the chip in the ESP8266 RAM through the SDIO downloaded programs. The majority of the programs that directly use CPU CACHE to call FLASH can be burnt to the FLASH chip connected to the HSPI interface beforehand. -

Page 23: Esp8266 Flash Software Downloading

3. SPI Compatibility Mode User Guide \XTCOM_UTIL. eagle.app.v6.irom0text.bin is all the functions of FLASH chip read directly through the SPI by CPU CACHE in the ESP8266 program. Run BinToArray.exe in SDIO communication demo\. Transfer • eagle.app.v6.flash.bin in SDIO communication demo \esp_iot_sdk_v0.9.3_sdio_demo\ bin to ANSI C format array. -

Page 24: Esp8266 Software Instruction

CMD52 command in order to resume the active high of the interrupt line.) the SDIO status register is 32 bits, it is revised by ESP8266 software, and it can be read by the host through CMD53 or CMD52 command. The address is 0x20-0x23. The data... -

Page 25: Instructions On The Read/Write Buffer And The Registration Linked List

3.3.2. Instructions on The Read/Write Buffer and The Registration Linked List DMA will directly send packets received and sent by the ESP8266 SDIO to corresponding memories. The ESP8266 software will define the linked list registration structure (or array), and buffer(s). -

Page 26: Api Functions In The Esp8266 Demo

Function and trigger condition: The SDIO interrupt processing function; this function will be triggered when the SDIO successfully receives or sends a packet. in DEMO, all the ESP8266 testing procedures are completed in the interrupt processing function. All the processing procedures of the registration linked lists, status registers and data during the communication process can be found in this function. -

Page 27: Stm32 Software Instruction

SDIO testing thread, it contains all the read/write procedures. Location: egl_thread.c. Registered by SPITest() of the same file in egl_thread.c. 2. int esp_sdio_probe(void) Function: Enable related programs in the ESP8266. Location: esp_main_sim.c. Called by SPITest() in egl_thread.c. 3. int sif_spi_write_bytes(u32 addr, u8*src,u16 count,u8 func) Function: Write the SDIO byte mode into the API;... - Page 28 In general, when initialising the SDIO, block_size of the ESP8266 SDIO should be configured. The starting value of DEMO is 512. During the operation, it is configured to be 1024. block_size should be an integer multiple of 4.

- Page 29 = 0, and whose addr=0x110-111. In general, when initialising the SDIO, block_size of the ESP8266 SDIO should be configured. The starting value of DEMO is 512. During the operation, it is configured to be 1024. block_size should be an integer multiple of 4.

-

Page 30: Spi Communication User Guide

(MOSI) or master input and slave output (MISO). 4.2.2. Master SPI Communication Format Supported by Current API The API function of ESP8266 SPI has two master initialization modes: one supports most of the general signals and the other is designed for driving a colored LCD screen. The device needs non-standard 9 bits SPI communication format. -

Page 31: Communication Format Supported By Slave Spi

4.3.4. Slave SPI Communication Format Supported by Current API The API function of ESP8266 SPI has a slave initialization mode which is compatible with most of the devices in bytes. Set the slave communication format of 7 bits command+8 bits read/write data so that other master SPI devices could read and write bytes of slave SPI via the 16 bits communication (or two times 8 bits with low lever CS). - Page 32 , i.e. 0x04. The second byte is data sending. The actual transmitting waveform is illustrated in Figure 4-1. Parameters: uint8 spi_no——The number of SPI module. Only input SPI and HSPI. Any other • inputs are invalid. Espressif 23 86 2016.05...

- Page 33 4. SPI Communication User Guide uint8 data——8 bit data sending. • Figure 4-1. The waveform of spi_byte_write_espslave written into slave ESP8266 ! Note: Yellow line: CS, blue line: CLK, red line: MOSI, green line: MISO. 6. void spi_byte_read_espslave(uint8 spi_no,uint8 *data) Function: Read one byte data from slave SPI and read other SPI slave devices.

-

Page 34: Master Spi Api Function Description

0x06master write and slave read, 0x0c master and slave read/write. The communication waveform is illustrated in Figure 4-1, 4-2. Parameters: spi_no The number of SPI module. ESP8266 processor has two SPI modules with the same function, i.e. SPI and HSPI. Optional values: SPI or HSPI. - Page 35 Code description: As SPI store the FLASH chip by the read/write program, HSPI is used for communication. For ESP8266 processor, there are multiple devices that share the interruption function, including SPI module, HSPI module, I2S module, the 4’s, 7’s and 9’s 0x3ff00020 in the register.

- Page 36 ⚠ Notice: Interruption program is unfit for time-consuming processing code because long-time interruption program will cause watchdog timer unable to realize normal reset and will also lead to unexpected restart of processor. Espressif 27 86 2016.05...

-

Page 37: Spi Overlap & Display Application Guide

Application Guide 5.1. Functional Overview The Overlap mode of ESP8266 Host SPI allows for two SPI modes (SPI and HSPI) to reuse the same IO interface (such as SCLK, MOSI and MISO) for the operation of multiple slave SPI devices. The hardware supports 3 line chip selection. If there are additional 3 slave devices, GPIO can be adopted as CS signal for the communication of multiple slave device. -

Page 38: Hardware Connection Of Spi Overlap Mode

SET_PERI_REG_MASK(SPI_PIN(HSPI), SPI_CS0_DIS |SPI_CS1_DIS) #define SELECT_TFT() CLEAR_PERI_REG_MASK(SPI_PIN(HSPI), SPI_CS1_DIS);\ SET_PERI_REG_MASK(SPI_PIN(HSPI), SPI_CS0_DIS |SPI_CS2_DIS) Therefore, users can change the macro definition. For example, the following macro can be defined if HSPI is used to the operate Flash: #define SELECT_FLASH() CLEAR_PERI_REG_MASK(SPI_PIN(HSPI), SPI_CS0_DIS);\ Espressif 29 86 2016.05... -

Page 39: Display Screen Console Program Demo

DEMO driver supports two screens currently, i.e. 3.5-inch TM035PDZV36 480*320 TFT colored LCD and Zhong JY. Tech 1.3-inch 128*64OLED. The driver programs can communicate with the display screen via ESP8266 HSPI interface under Overlap mode. Under SPI Overlap mode, the two screens and 8266 external program flash chip share SCLK, MOSI and MISO signals on the SPI bus. - Page 40 ...—— variable parameters that needs to be displayed in the corresponding string. • Location: \app\user\user_lcd.c and \app\include\user_lcd.h 4. void at_lcd_print(uint8* str) Function: shows the assigned character string displayed on the screen order. Parameters: uint8* str—— the starting address of string array. Espressif 31 86 2016.05...

-

Page 41: Pre-Compiled Macro Setting

The program supports the same character shown in two screens. Overlap_TEST is used for SPI Overlap test when TFT is used to display image. TFT should be set at 0 as it conflicts with the displayed characters. Espressif 32 86 2016.05... -

Page 42: Spi Wi-Fi Passthrough 1-Interrupt Mode

6.2. ESP8266 SPI Slave Protocol Format 6.2.1. SPI Slave Clock Polarity Configuration Clock polarity of the master clock which communicates with the ESP8266 SPI slave should be set to be low in the idle state, sampling for rising edge, and changing data for falling edge. -

Page 43: Slave Status Definition And Line Breakage

When there are changes in the slave status register, interrupt line GPIO0 will be set to be 1; when the master uses 0x04, 0x05 to read the slave status register, interrupt line GPIO0 will be set 0. 6.4. ESP8266 SPI Slave API Functions ⚠ Notice: Configure in spi.h if SPI status register single-threaded passthrough protocol is used. - Page 44 + 8 bits address + 256 bits (32 Bytes) read/write data. Parameters: spi_no: number of the SPI module. The ESP8266 processor has two SPI modules (SPI and HSPI) with the same functions. Value to be selected: SPI or HSPI.

- Page 45 // record the interrupt status regvalue=READ_PERI_REG(SPI_SLAVE(HSPI)); //***********interrupt handler flag, end this passthrough************// CLEAR_PERI_REG_MASK(SPI_SLAVE(HSPI), SPI_TRANS_DONE_EN| SPI_SLV_WR_STA_DONE_EN| SPI_SLV_RD_STA_DONE_EN| SPI_SLV_WR_BUF_DONE_EN| SPI_SLV_RD_BUF_DONE_EN); SET_PERI_REG_MASK(SPI_SLAVE(HSPI), SPI_SYNC_RESET); CLEAR_PERI_REG_MASK(SPI_SLAVE(HSPI), SPI_TRANS_DONE| SPI_SLV_WR_STA_DONE| SPI_SLV_RD_STA_DONE| SPI_SLV_WR_BUF_DONE| SPI_SLV_RD_BUF_DONE); SET_PERI_REG_MASK(SPI_SLAVE(HSPI), SPI_TRANS_DONE_EN| SPI_SLV_WR_STA_DONE_EN| SPI_SLV_RD_STA_DONE_EN| SPI_SLV_WR_BUF_DONE_EN| SPI_SLV_RD_BUF_DONE_EN); *******************************************************// /****************master writes interrupt handler***************/ Espressif 36 86 2016.05...

- Page 46 //***********************************// //************data transmission completed, wr_busy set to be 0*************// spi_sta.byte_value=READ_PERI_REG(SPI_STATUS(HSPI))&0xff; spi_sta.elm_value.wr_busy=0; WRITE_PERI_REG(SPI_STATUS(HSPI), (uint32)spi_sta.byte_value); ************************************************// /***testing part, it can be revised. This part of the program is used to copy the data read to the read buffer**/ Espressif 37 86 2016.05...

- Page 47 GPIO_OUTPUT_SET(0, 1); // interrupt line set to be 1, inform the master to read the slave status /****************master reads status interrupt handler***************/ if(regvalue&SPI_SLV_RD_STA_DONE){ GPIO_OUTPUT_SET(0,0); // interrupt line set to be 0, the master has read the status Espressif 38 86 2016.05...

- Page 48 6. SPI Wi-Fi Passthrough 1-Interrupt Mode }else if(READ_PERI_REG(0x3ff00020)&BIT9){ //bit7 is for i2s isr, } Espressif 39 86 2016.05...

-

Page 49: Spi Wi-Fi Passthrough 2-Interrupt Mode

If CS is pulled high when data is being sent, the slave interior status will be reset. 7.2.2. Communication Format Supported by The SPI Slave The ESP8266 SPI slave communication format is similar to that of the master, it should be command + address+ read/write data. To be specific: command: length, 8 bits;... -

Page 50: Instruction On The Data Flow Control Line

Then, GPIO0 will be written to be low level, and quit the interrupt program. After that, if data is sent to the ESP8266 through WiFi and is required to be forwarded by SPI, ESP8266 software will be written into SPI_W8 to SPI_W15, and GPIO2 will be set to be high level. - Page 51 SPI transmission, command 2 + address 0 + 32 bytes of data GPIO0_Raising_Edge_ISR() // rising edge interrupt program connected to the ESP8266 GPIO0 wr_rdy=1; // data sent by the master has been processed, ready for the next write operation...

-

Page 52: Esp8266 Spi Slave Api Functions

+ 8 bits address + 256 bits (32 Bytes) read/write data. Parameters: spi_no: number of the SPI module. The ESP8266 processor has two SPI modules (SPI and HSPI) with the same functions. value to be selected: SPI or HSPI. - Page 53 SPI_SLV_RD_BUF_DONE_EN); //MISO processing program if(regvalue&SPI_SLV_WR_BUF_DONE){ GPIO_OUTPUT_SET(0, 0); //GPIO0 set to be 0 idx=0; //read the data received while(idx<8){ recv_data=READ_PERI_REG(SPI_W0(HSPI)+4*idx); //os_printf("rcv data : 0x%x \n\r",recv_data); spi_data[4*idx+0] = recv_data&0xff; spi_data[4*idx+1] = (recv_data>>8)&0xff; spi_data[4*idx+2] = (recv_data>>16)&0xff; spi_data[4*idx+3] = (recv_data>>24)&0xff; Espressif 44 86 2016.05...

- Page 54 GPIO_OUTPUT_SET(0, 1); //GPIO0 set to be 1 SET_PERI_REG_MASK(SPI_SLAVE(HSPI), SPI_SLV_WR_BUF_DONE_EN); //master reads, slave sends the processing program if(regvalue&SPI_SLV_RD_BUF_DONE){ GPIO_OUTPUT_SET(2, 0); //GPIO2 set to be 0 }else if(READ_PERI_REG(0x3ff00020)&BIT9){ //bit7: I2S interrupt Espressif 45 86 2016.05...

-

Page 55: Hspi Host Multi-Device Api

SPI and HSPI. SPI bus is especially used to read CPU programming code from the external Flash, while HSPI bus is used for SPI device communication. When ESP8266 is working as a host, HSPI bus can operate with three user devices, besides, it also supports one external Flash writing operation. User devices are supported through selection with CS lines. -

Page 56: Api Description

8. HSPI Host Multi-device API Mode Pin Name of Host ESP8266 SPI bus Signal Line MTMS U0TXD SD_CLK SCLK SPI OVERLAP and CS1 SD_DATA0 MISO SD_DATA1 MOSI GPIO0 SD_CLK SCLK SPI OVERLAP and CS2 SD_DATA0 MISO SD_DATA1 MOSI ! Note: The pins used when HSPI operates with the Flash in OVERLAP mode is completely the same with that of SPI communication. - Page 57 If the device has not been initialized, ERROR will be printed and the function will be returned. If it the parameter should be other values, ERROR will be printed and the function will be returned. Espressif 48 86 2016.05...

-

Page 58: I2C User Guide

1. Select pin functionality and set as GPIO 2. Set the GPIO into open-drain mode 3. Initialize SDA and SCL as high levels 4. Disconnect GPIO and reset slave state i2c_master_init(void): Reset slave state 9.2.2. Start I2C i2c_master_start(void): master generates I2C start conditions. Espressif 49 86 2016.05... -

Page 59: Stop I2C

9. I2C User Guide 9.2.3. Stop I2C i2c_master_stop(void): master generates I2C stop conditions. 9.2.4. I2C Master Responds ACK i2c_master_send_ack(void): sets I2C master to respond ACK. 9.2.5. I2C Master Responds NACK I2C_master_send_nack(void): sets I2C master to respond NACK. Espressif 50 86 2016.05... -

Page 60: Check I2C Slave Response

Either slave address or data can be sent. 9.2.8. Read Data from I2C Bus i2c_master_readByte (void): read a byte from SPI slave. Return value: Read 1 Byte of data. 9.3. Demo Please refer to IOT_Demo provided by esp_iot_sdk, for example: Espressif 51 86 2016.05... - Page 61 9. I2C User Guide Espressif 52 86 2016.05...

-

Page 62: I2S Module Description

10. I2S Module Description I2S Module Description 10.1. Functional Overview The I2S module of the ESP8266 contains a Tx (transport) unit and a Rx (receive) unit. Both the Tx and the Rx unit have a three-wire interface that includes: Clock line;... - Page 63 Bits 13 ~ 15 of I2S_FIFO_CONF are used to control the transport data format for i2s_tx_fifo_mod. Value Description 16bits_per_channel full data (dual channel, FIFO data organisation, 16 bits data in the left channel,16 bits data in the right channel, and 16 bits data in the left channel) Espressif 54 86 2016.05...

- Page 64 Right channel (put a constant from regfile in the left channel) Left channel (put a constant from regfile in the right channel) Rx channel mode Bits 3~4 in the I2SCONF_CHAN are used for the Rx channel mode (rx_chan_mod). Espressif 55 86 2016.05...

-

Page 65: Link List Configuration

See the definitions of i2s_reg.h in DEMO. Other instructions will be updated. 10.2.2. Link List Configuration In the ESP8266, the DMA transfers the receive and transport packets in the SDIO to the corresponding memory. The software will define the structure (or group) of the registration list and cache space(s). -

Page 66: Slc Module Configuration

“0”, indicating that there is no empty buffer to receive any flames. 10.2.3. SLC Module Configuration 10.2.3.1. Basic Configuration The SLC module provides the ESP8266 with DMA service of several modules. Follow the instructions below so that the SLC module is used for the FIFO transmission of I2S. -

Page 67: Void Function

Configure the Rx link list address to the register. For configuration instructions, refer to Section 10.2.3. Feature SLC module configuration. Parameter addr: link list address CONF_TXLINK_ADDR Function CONF_TXLINK_ADDR(addr) Configure the TX link list address to the register. For configuration instructions, refer to Section 10.2.3. Feature SLC module configuration. Espressif 58 86 2016.05... -

Page 68: Start Function

Start the Rx transmission of the SLC module. For configuration instructions, refer to Section 10.2.3. SLC Feature module configuration. Parameter null START_TXLINK Function START_TXLINK() Start the Tx transmission of the SLC module. For configuration instructions, refer to Section 10.2.3. SLC Feature module configuration. Parameter null Espressif 59 86 2016.05... -

Page 69: Uart Introduction

11. UART Introduction UART Introduction 11.1. Functional Overview There are two group ESP8266 UART interfaces, respectively: UART0: • - U0TXD: pin26 (U0TXD) - U0RXD: pin25 (U0RXD) - U0CTS: pin12 (MTCK) - U0RTS: pin13 (MTDO) • UART1: - U1TXD: pin14 (GPIO2) The basic working process of transmission FIFO: As long as there has data filling into transmission FIFO, it will immediately start sending... -

Page 70: Hardware Resources

UART attribute parameters are all in UART_CONF0 register, can be found in the Uart_register.h. You can configure UART properties through modifying the different bit of the register. 11.3.1. The Baud Rate The serial of ESP8266 can support the baud rate range from 300 to 115200 * 40. Espressif 61 86 2016.05... -

Page 71: Parity Bit

#define UART_DTR_INV (BIT(24)) #define UART_RTS_INV (BIT(23)) #define UART_TXD_INV (BIT(22)) #define UART_DSR_INV (BIT(21)) #define UART_CTS_INV (BIT(20)) #define UART_RXD_INV (BIT(19)) Set the corresponding register,you can reverse the corresponding signal line input / output. Interface: void UART_SetLineInverse (uint8 uart_no, UART_LineLevelInverse inverse_mask); Espressif 62 86 2016.05... -

Page 72: Switch Output Port Of Print Function

#define UART_TXD_BRK (BIT(8)) //Line stop signal, 1:enable ; 0: disable 11.3.10. Flow Control Configuration process: Configure pin12, pin13 of UART0 pin as U0CTS and U0RTS functions. • #define FUNC_U0RTS 4 #define FUNC_U0CTS 4 PIN_FUNC_SELECT(PERIPHS_IO_MUX_MTDO_U, FUNC_U0RTS); Espressif 63 86 2016.05... -

Page 73: Other Interfaces

UART_INT_RAW Interrupt the original status register UART_INT_ENA Interrupt enable register: Indicates interrupt the current enable UART UART_INT_ST Interrupt Status Register: Indicates the currently active interrupt status UART_INT_CLR Clear Interrupt register:set the corresponding bit to clear the interrupt status register Espressif 64 86 2016.05... -

Page 74: Interface

As for special full interrupts you need first to read all fifo received data empty, then write the clear interruption status register.Otherwise, the interrupt status bit will be set again after exit. Please see details in examples of interrupt handling. Receive overflow interrupt Interrupt status bits:UART_RXFIFO_OVF_INT_ST Espressif 65 86 2016.05... - Page 75 Clear interrupt status: Like full interrupts,tout interrupt also need to firstly read out all received fifo data,then clear interrupt status register.Otherwise, interrupt status bit will still be set after exiting. Please see details in examples of interrupt handling. Espressif 66 86 2016.05...

- Page 76 Parity error interrupt (parity_err): received byte exists parity error. Termination line error interrupt(BRK_DET):receive break signal,or receive error initial conditions (rx line always stays low) Receive frame error interrupt (frm_err):stop bit is not 1. Application: Generally used for error detection. Espressif 67 86 2016.05...

- Page 77 In UART_INT_ENA register, #define UART_CTS_CHG_INT_ENA (BIT(6)) CTS //Line status enable interrupt bit, 1:enable;0:disable #define UART_DSR_CHG_INT_ENA (BIT(5)) DSR //Line status enable interrupt bit, 1:enable;0:disable Clear interrupt status: After dealing with the corresponding error,clear the interrupt status bit. Espressif 68 86 2016.05...

-

Page 78: Example Of Interrupt Handler Process

11.5. Example of Interrupt Handler Process 11.6. Abandon Serial Output During Booting When ESP8266 is booting, UART0 will default print out some information,if this should be un-acceptable,we can abandon these print output via setting UART internal switching pin functions,exchange U0TXD, U0RXD with U0RTS, U0CTS during initialization. - Page 79 11. UART Introduction U0RTS: pin26(u0txd) As the transceiver feet of UART0,hardware pin13 and pin12 won’t print out duing booting,but be attention to ensure pin13 (mtdo) can not be pulled up by external in ESP8266 is booting. Espressif 70 86 2016.05...

-

Page 80: Pwm Interface

To enter Deep Sleep mode, PWM needs to be stopped first. • 12.1.2. Implementation An optimized software algorithm provided by ESP8266 system enable the transmission of multi-channel PWM signals via GPIO (General Purpose Input Output) interface by way of mounting NMI on FRC1 timer. -

Page 81: Configuration

//define the structure of a single PWM parameter uint16 gpio_set; //GPIO needs to be set uint16 gpio_clear; //GPIO needs to be cleared uint32 h_time; //time needs to be written into FRC1_LOAD struct pwm_param { //define the structure of PWM parameter Espressif 72 86 2016.05... -

Page 82: Interface Specifications

= {{PWM_0_OUT_IO_MUX,PWM_0_OUT_IO_FUNC,PWM_0_OUT_IO_NUM}, {PWM_1_OUT_IO_MUX,PWM_1_OUT_IO_FUNC,PWM_1_OUT_IO_NUM}, {PWM_2_OUT_IO_MUX,PWM_2_OUT_IO_FUNC,PWM_2_OUT_IO_NUM}}; pwm_init(light_param.pwm_period,light_param.pwm_duty, 3,io_info); Call the function when the system is been initialized. Currently the function can be called Call only once. Returned Value Null 2. pwm_set_period Function Name pwm_set_period Definition Set PWM period. Espressif 73 86 2016.05... - Page 83 5. pwm_get_duty Function Name pwm_get_duty Description Get the duty ratio of current PWM signal at a certain channel. Sample code pwm_get_duty (uint8 channel) Parameter uint8 channel: get the current PWM channel. This parameter is defined in PWM_CHANNEL. Espressif 74 86 2016.05...

-

Page 84: Custom Channels

{PWM_0_OUT_IO_MUX,PWM_0_OUT_IO_FUNC,PWM_0_OUT_IO_NUM}, {PWM_1_OUT_IO_MUX,PWM_1_OUT_IO_FUNC,PWM_1_OUT_IO_NUM}, {PWM_2_OUT_IO_MUX,PWM_2_OUT_IO_FUNC,PWM_2_OUT_IO_NUM}, {PWM_3_OUT_IO_MUX,PWM_3_OUT_IO_FUNC,PWM_3_OUT_IO_NUM} {PWM_4_OUT_IO_MUX,PWM_4_OUT_IO_FUNC,PWM_4_OUT_IO_NUM}, pwm_init(light_param.pwm_period, light_param.pwm_duty, PWM_CHANNEL,io_info); 2. Modify user_light.h. #define PWM_0_OUT_IO_MUX PERIPHS_IO_MUX_MTDI_U #define PWM_0_OUT_IO_NUM 12 #define PWM_0_OUT_IO_FUNC FUNC_GPIO12 #define PWM_1_OUT_IO_MUX PERIPHS_IO_MUX_MTDO_U #define PWM_1_OUT_IO_NUM 15 #define PWM_1_OUT_IO_FUNC FUNC_GPIO15 #define PWM_2_OUT_IO_MUX PERIPHS_IO_MUX_MTCK_U #define PWM_2_OUT_IO_NUM 13 Espressif 75 86 2016.05... - Page 85 12. PWM Interface #define PWM_2_OUT_IO_FUN CFUNC_GPIO13 #define PWM_3_OUT_IO_MUX PERIPHS_IO_MUX_GPIO4_U #define PWM_3_OUT_IO_NUM 4 #define PWM_3_OUT_IO_FUNC FUNC_GPIO4 #define PWM_4_OUT_IO_MUX PERIPHS_IO_MUX_GPIO5_U #define PWM_4_OUT_IO_NUM 5 #define PWM_4_OUT_IO_FUNC FUNC_GPIO5 #define PWM_CHANNEL 5 Espressif 76 86 2016.05...

-

Page 86: Ir Remote Control User Guide

13.1. Introduction to Infrared Transmission Users can request the sample codes of infrared transmission by sending an e-mail to feedback@espressif.com. This document introduces how to implement transmitting or receiving remote control codes using the 32-bit NEC IR transmission protocol as an example. -

Page 87: Parameters Configuration

Modes of Transmitting Carrier Waveform: Mode 1: IIS Clock Mode MTMS pin, or GPIO14 is used to transmit carrier waveform under IIS clock mode. Please refer to Figure 1 below. #define GEN_IR_CLK_FROM_IIS #define IR_GPIO_OUT_MUX PERIPHS_IO_MUX_MTMS_U #define IR_GPIO_OUT_NUM Espressif 78 86 2016.05... -

Page 88: Functions Of Infrared Sample Codes

FUNC_GPIO5 13.3. Functions of Infrared Sample Codes The below functions can be implemented using infrared sample codes provided by Espressif Systems: Functions of infrared transmitting and receiving can be invoked in the initialization • process, and a 4s loop timer can be configured to transmit infrared remote control codes. -

Page 89: Sniffer Introduction

14. Sniffer Introduction Sniffer Introduction 14.1. Sniffer Introduction ESP8266 can enter promiscuous mode (sniffer) and capture IEEE 802.11 packets in the air. The following HT20 packets are support: 802.11b • 802.11g • 802.11n (from MCS0 to MCS7) • AMPDU types of packets •... - Page 90 14 bits are Fragment number (usually be 0) u8 addr3[6]; // the third address in packet struct sniffer_buf{ struct RxControl rx_ctrl; u8 buf[36]; // head of ieee80211 packet u16 cnt; // number count of packet struct LenSeq lenseq[1]; //length of packet Espressif 81 86 2016.05...

- Page 91 MAC address of both sides of communication nor length of the head of packet. For AMPDU packet, we can not get the count of packets or the length of packet. • This structure contains: length of packet, rssi and FEC_CODING. • Espressif 82 86 2016.05...

-

Page 92: Sniffer Application Scenarios

The distance between mobile phone and AP is longer than the distance between • mobile phone and IOT_device. IOT-device firmware can set filter of MAC address or MAC-header (include MAC-cryption- header), it can also set a filter for retransmission. Espressif 83 86 2016.05... -

Page 93: Phone App

- Length of packet in odd number to be 0 ~ 511, length of packet in even number to be 512 ~1023 14.3. Phone APP For Scenario 2, phone APP should notice: Time interval of each UDP packet to be longer than 20ms • Espressif 84 86 2016.05... -

Page 94: Iot-Device Firmware

AMPDU packet will be a multiple of 4, all of these should be taken into consideration. Use relative value to transmit information, for example, the value that the length of • data packet minus the length of packet that works as separative sign. Espressif 85 86 2016.05... -

Page 95: Appendix

Appendix 2 SPI Registers Information on SPI register names, addresses and description. Appendix 3 UART Registers Information on UART register names, addresses and description. Appendix 4 Timer Registers Information on Timer register names, addresses and description. Espressif 86 86 2016.05... - Page 96 Appendix 1 GPIO Registers GPIO Base Address 0x60000300 GPIO RegAddr = PERIPHS_GPIO_BASEADDR+ (OFFSET*4) OFFSET RegAddr RegName Signal BitPos SW(R/W) Description 0x0000 0x60000300 GPIO_OUT GPIO_BT_SEL [31:16] BT-Coexist Selection register GPIO_OUT_DATA [15:0] The output value when the GPIO pin is set as output. 0x0001 0x60000304 GPIO_OUT_W1TS [31:16]...

- Page 97 Appendix 2 SPI Registers Address RegName Signal BitPos Default SW(R/W) Description SPI_CMD spi_usr [18] 1'b0 In the master mode, it is the start bit of a single operation. Self-clear by hardware SPI_ADDR iodata_start_addr [31:0] 32'h0 In the master mode, it is the value of address in "address" phase. SPI_CTRL [31:27] 5'h0...

- Page 98 Appendix 3 UART Registers Address RegName Signal BitPos Default SW(R/W) Description UART_FIFO [31:8] 24'h0 UART FIFO,length 128 rxfifo_rd_byte [7:0] 8'b0 R/W share the same address UART_INT_RAW UART_INT_RAW UART INTERRUPT RAW STATE The interrupt raw bit for Rx time-out interrupt(depands on the rxfifo_tout_int_raw 1'b0 UART_RX_TOUT_THRHD)

- Page 99 Appendix 4 Timer Registers Address RegName Signal BitPos Default SW(R/W) Description FRC1_LOAD_ADDRESS frc1_load_value [22:0] 23'b0 the load value into the counter the current value of the counter. It is a decreasing FRC1_COUNT_ADDRESS frc1_count [22:0] 23'h7fffff RO counter. FRC1_CTRL_ADDRESS [31:9] 23'b0 the status of the interrupt, when the count is frc1_int 1'b0...

- Page 100 The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth logo is a registered trademark of Bluetooth SIG. All trade names, trademarks and registered trademarks mentioned in this document are Espressif IOT Team property of their respective owners, and are hereby acknowledged. www.espressif.com Copyright © 2016 Espressif Inc. All rights reserved.

Need help?

Do you have a question about the ESP8266 and is the answer not in the manual?

Questions and answers