Altera MAX 10 series User Manual

Fpga power management

Hide thumbs

Also See for MAX 10 series:

- User manual (67 pages) ,

- User manual (53 pages) ,

- User manual (32 pages)

Table of Contents

Advertisement

Quick Links

Download this manual

See also:

User Manual

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Altera MAX 10 series

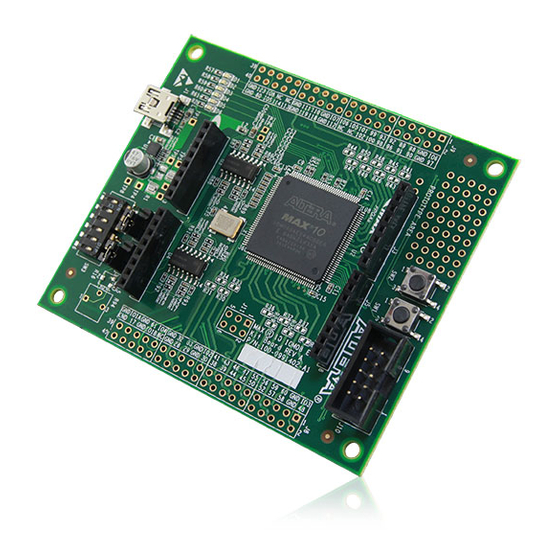

- Page 1 MAX 10 Power Management User Guide 101 Innovation Drive UG-M10PWR Subscribe 2015.11.02 San Jose, CA 95134 Send Feedback www.altera.com...

-

Page 2: Table Of Contents

Entering Sleep Mode........................3-4 Exiting Sleep Mode.......................... 3-4 Timing Parameters.......................... 3-5 Hardware Implementation and Current Measurement................. 3-5 Additional Information for MAX 10 Power Management User Guide ... A-1 Document Revision History for MAX 10 Power Management User Guide........A-1 Altera Corporation... -

Page 3: Max 10 Power Management Overview

Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. -

Page 4: Power Supply Device Options

Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. -

Page 5: Comparison Of The Max 10 Power Supply Device Options

This shows the number of power supplies required by the core and periphery of the MAX 10 devices. You may need additional voltage regulators to supply power to the if the does not have the same VCCIO VCCIO voltage level as the core and periphery supply. MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback... -

Page 6: Power Supply Design

5.267 Related Information Enpirion Power Management Solutions • Provides more information about Altera's Power Management IC and PowerSoC solutions designed for powering FPGAs. MAX 10 FPGA Device Family Pin Connection Guidelines • Provides a more detailed recommendation about how to group inputs in order to power a MAX 10 device. -

Page 7: Power-On Reset Circuitry

The observed value will be less than the published value after adding the decoupling capacitance on your design board. Altera recommends using a soft start regulator that is able to reduce the transient current when the device is powered. -

Page 8: Power Supplies Monitored And Not Monitored By The Por Circuitry

POR delay time on the Quartus Prime programmer user interface. For banks 1B and 8 for all MAX 10 devices and banks 1 and 8 for the 10M02 device. MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback... - Page 9 However, if you are using instant-on features, the POR circuit does monitor the VCCIO voltage drop for up to 9 ms after the last power rail reaches its trip point. MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback...

-

Page 10: Instant-On Support

You can power down the I/O buffer dynamically when your application is in idle or sleep mode. One example is the digital single lens reflex DSLR camera MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback... - Page 11 Altera provides a soft power management controller as reference design utilizing low-power features implemented in the MAX 10 devices. You can modify the reference design based on your application. The soft power management controller includes a simple finite state machine (FSM) to manage the low-power state mode by powering down the I/O buffer and GCLK gating during sleep mode.

-

Page 12: Hot Socketing

The MAX 10 device is a hot-socketing compliant device that does not need any external components or special design requirements. Hot-socketing support in the MAX 10 device has the following advantages: MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback... -

Page 13: Hot-Socketing Feature Implementation

Thus, it is CONF_DONE nSTATUS an expected behavior for these pins to drive out during power-up and power-down sequences. MAX 10 Power Management Features and Architecture Altera Corporation Send Feedback... -

Page 14: Hot-Socketing Feature Implementation

CCIO not in user mode. Altera uses GND as reference for hot-socketing operation and I/O buffer designs. To ensure proper operation, Altera recommends connecting the GND between boards before connecting the power supplies. This prevents the GND on your board from being pulled up inadvertently by a path to power through other components on your board. -

Page 15: Power Management Controller Reference Design

Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. -

Page 16: Clock Control Block

I/O buffers during sleep mode. Altera recommends using a separate Altera GPIO Lite IP when some of the I/O buffer is not required to be powered down. Internal Oscillator Internal Oscillator IP core ( ) is a free-running oscillator once you enable it. -

Page 17: Entering State

Upon entering sleep mode, the functionality of the device such as GCLK networks and I/O buffers are dynamically powered down—to minimize dynamic power dissipation. All configuration data is retained when the device is in the sleep mode. Power Management Controller Reference Design Altera Corporation Send Feedback... -

Page 18: Entering Sleep Mode

The running counter is then frozen. cnt_sleep_enter (GPIO) is tri-stated when is de-asserted. gpio_pad_output Exiting Sleep Mode Figure 3-4: Exiting Sleep Mode Timing Diagram sleep current_state Sleep Exiting Awake clk_ena[15:0] 16’h0000 Enabling 16’hFFFF sleep_status Power Management Controller Reference Design Altera Corporation Send Feedback... -

Page 19: Timing Parameters

The current in this design is measured using a current monitor component (the Linear Technologies LTC 2990). The measured current is further processed by a pre-programmed design in a MAX II device. The Power Management Controller Reference Design Altera Corporation Send Feedback... - Page 20 Hardware Implementation and Current Measurement 2015.11.02 measured current is shown on Altera power monitor GUI when the PowerMonitor.exe is launched. You will see a current monitor for each of the main supplies to the MAX 10 device as follows: • 2.5V_CORE •...

- Page 21 The results show an approximate 93% reduction in the core current (1.2V_ICC) consumption and an approximate 56% reduction in I/O current (2.5V_ICCIO) consumption in sleep mode relative to user mode. The total power consumption reduction in this design in sleep mode is about 68%. Power Management Controller Reference Design Altera Corporation Send Feedback...

-

Page 22: Additional Information For Max 10 Power Management User Guide

Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Need help?

Do you have a question about the MAX 10 series and is the answer not in the manual?

Questions and answers