Table of Contents

Advertisement

Quick Links

High Integration PC/104 SBC with Gigabit Ethernet and Data Acquisition

Revision

Date

A.00

12/6/2012

FOR TECHNICAL SUPPORT

PLEASE CONTACT:

support@diamondsystems.com

Athena IIII User Manual

Rev A.00: December 2012

Comment

Initial version

Copyright 2012

Diamond Systems Corporation

555 Ellis Street

Mountain View, CA 94043 USA

Tel 1-650-810-2500

Fax 1-650-810-2525

www.diamondsystems.com

Advertisement

Table of Contents

Summary of Contents for Diamond Systems Athena IIII

- Page 1 Athena IIII User Manual High Integration PC/104 SBC with Gigabit Ethernet and Data Acquisition Rev A.00: December 2012 Revision Date Comment A.00 12/6/2012 Initial version Copyright 2012 FOR TECHNICAL SUPPORT Diamond Systems Corporation PLEASE CONTACT: 555 Ellis Street Mountain View, CA 94043 USA support@diamondsystems.com...

-

Page 2: Table Of Contents

SATA (J3) ..................................18 (J4) ................................19 THERNET VGA (J5) ..................................19 LCD P , LVDS I (J7) ............................ 20 ANEL NTERFACE LCD B (J8) ............................... 21 ACKLIGHT PC/104 ISA B (J10, J11) ............................22 www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 3 ............................56 EGISTER EFINITIONS 12.4 ............................57 EGISTER EFINITIONS ANALOG-TO-DIGITAL INPUT RANGES AND RESOLUTION ..................59 13.1 ..................................59 VERVIEW 13.1.1 Input Range Selection ............................59 13.1.2 Input Range Table .............................. 59 www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 4 IEWING AND ODIFYING THE ETTINGS 22.2 BIOS S ............................. 77 CREEN ESCRIPTIONS SPECIFICATIONS ..............................80 23.1 CPU..................................... 80 23.2 ............................80 CQUISITION IRCUITRY 23.3 ................................81 OWER UPPLY 23.4 ..................................81 ENERAL www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 5: Important Safe Handling Information

This creates many opportunities for accidental damage during handling, installation and connection to other equipment. The list here describes common causes of failure found on boards returned to Diamond Systems for repair. This information is provided as a source of advice to help you prevent damaging your Diamond (or any vendor’s) embedded computer boards. - Page 6 The same situation can occur when pulling a ribbon cable off of a pin header. If the pins are bent too severely, bending them back can cause them to weaken unacceptably or even break, and the connector must be replaced. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 7: Introduction

The ISA bus is brought out to an expansion connector to mate with add-on boards. Diamond Systems manufactures a wide variety of compatible PC/104 add-on boards for analog I/O, digital I/O, counter/timer functions, serial ports and power supplies. -

Page 8: Data Acquisition

-40°C to +85°C ambient operating temperature without a fan MIL-STD-202G compatible Power input requirements: +5VDC +/- 5% Optional +12VDC to pass through to expansion buses and LCD backlight ONLY. No on-board circuits depend on +12VDC. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 9: Getting Started

3.1 Introducing the Athena III Development Kit The Athena III Development Kit (DK-ATHE1000A-01) provides everything required for Athena III based rapid application development. The table on the next page lists the boards, cables, and other items included. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 10: Athena Iii Cable Kit

Note: On each interface cable, the end of the cable connector that has a red wire going to it should be oriented toward the end of the board connector that is labeled “pin 1” (typically the pin with a square pad on the PCB). www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 11: System Setup

6981506 cable to connector J21 on the Athena III SBC. 3.2.7 Display Athena III provides interfaces for both LVDS flat panel displays and VGA output. Connect the VGA cable, 6981030, between the VGA connector, J5, and a VGA-compatible display. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 12: Booting The System

Drivers for Windows Embedded Standard 7, Windows Embedded CE, and Linux 2.6, if required, are included on the Software and Documentation CD that is included in the Athena III Development Kit. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 13: Functional Overview

1GB of soldered DRAM memory using 8 chips, a display controller with LVDS and onboard VGA/ DVI converter, plus SATA, USB, serial port and LAN interfaces. The ISA is available for stackable I/O expansion. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 14: Video

4.2.8 PC/104 Expansion Bus The PC/104 expansion bus enables installation of additional I/O boards. It consists of two stack-through connectors press-fit onto the board, enabling expansion both above and below the board. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 15: Power Supply

Support for various LCD configurations supported by the video chipset Console (display and keyboard) redirection to serial port BIOS recovery through USB attached storage or other means Configurable default settings in battery-less configurations Initialize USB keyboard & mouse Customizable splash screen www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

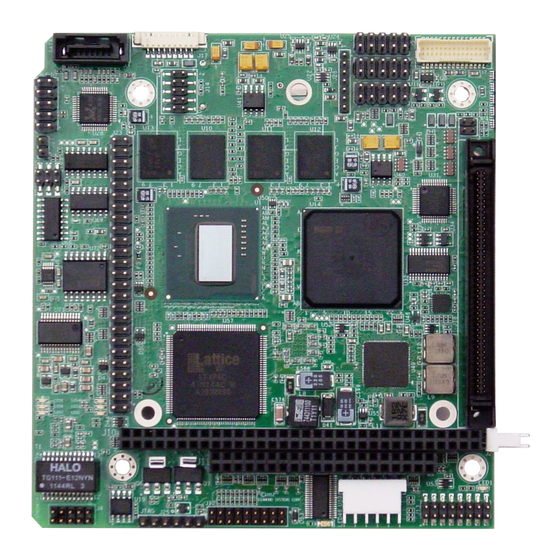

Page 16: Board Description

5. BOARD DESCRIPTION The figure below shows the Athena III board layout, including connectors, jumper blocks and mounting holes. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 17: Connector Summary

The following table lists the jumpers on the Athena III SBC. Jumper Block Description LCD scan direction and frame rate setting LCD panel voltage select System configuration settings RS-232/422/485 termination select JP26 Data acquisition configuration settings www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 18: Connectors

6. CONNECTORS This section describes the on-board Athena III connectors. Note: All cables mentioned in this chapter are included in Diamond Systems’ cable kit C-ATHE-KIT. Some cables are also available individually. External Battery (J2) Connector J2 is used to connect an external battery for maintaining the Real-Time Clock and the CMOS settings (BIOS settings for various system configurations). -

Page 19: Ethernet (J4)

Note: While the DDC serial detection pins are present, a 5V power supply is not provided (the old “Monitor ID” pins are also not used). Diamond Systems cable number 6981030 provides a female DB15 connection to interface with a standard RGB monitor. -

Page 20: Lcd Panel, Lvds Interface (J7)

(only powered up when LCD display is active) Ground Power Ground, 0V Connector on board: JST model number BM30B-SRDS-G-TF or equivalent Mating cable connector: JST model number SHDR-30V-S-B or equivalent Terminals: JST model number SSH-003GA-P0.2 or equivalent www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 21: Lcd Backlight (J8)

6 on this connector. A jumper selects the source of the brightness signal to this pin. Connector on board: Molex 53047-0610 or equivalent Mating Cable Connector: Molex 51021-0600 or equivalent Terminals: Molex 50058 / 50079 series or equivalent www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 22: Pc/104 Isa Bus (J10, J11)

DACK3- SD11 DACK7- SA15 DRQ3 SD12 DRQ7 SA14 DACK1- SD13 SA13 DRQ1 SD14 MASTER- SA12 REFRESH- SD15 Ground SA11 SYSCLK Ground SA10 IRQ7 IRQ6 IRQ5 IRQ4 IRQ3 DACK2- BALE Ground Ground Ground www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 23: Usb Flashdisk (J14)

Data + Data - Ground Connectors J15 and J16 mate with Diamond Systems cable number 698012, which provides two standard USB type A jacks in a panel-mount housing. Connector type: Standard 0.1” dual row straight pin headers with gold flash plating www.diamondsystems.com... -

Page 24: Main I/O (J18)

For RS-422 or RS-485, the following pinouts apply: 1/10/19/28 1/10/19/28 2/11/20/29 2/11/20/29 3/12/21/30 TXD+ 3/12/21/30 TXD/RXD+ 4/13/22/31 TXD- 4/13/22/31 TXD/RXD- RS-422 5/14/23/32 Ground RS-485 5/14/23/32 Ground 6/15/24/33 RXD- 6/15/24/33 7/16/25/34 RXD+ 7/16/25/34 8/17/26/35 8/17/26/35 9/18/27/36 Ground 9/18/27/36 Ground www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 25 RI4 35 35 Reset- GND 36 36 ATX Power Utilities A +5V Out 37 37 NC Speaker Out 38 38 NC IDE Drive LED 39 39 NC Power LED 40 40 NC www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 26 CPU to turn on, and a contact of 4 seconds or longer will generate a power shutdown. Connector J18 mates with Diamond Systems cable number C-PRZ-01, which consists of a dual-ribbon-cable assembly with industry-standard connectors at the user end. The SBC mating connector includes integral latches for enhanced reliability.

-

Page 27: Input Power (J21)

ATX control enables the +5V and +12V power to be switched on and off with an external momentary switch. A short press on the switch will turn on power, and holding the switch on for 4 seconds or longer will turn off power. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 28: Data Acquisition I/O (J23)

VIN0 35 36 VIN8 VIN1 37 38 VIN9 VIN2 39 40 VIN10 VIN3 41 42 VIN11 VIN4 43 44 VIN12 VIN5 45 46 VIN13 VIN6 47 48 VIN14 VIN7 49 50 VIN15 www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 29: Jumper Configuration

Analog ground; used for analog circuitry only Vout pin is for analog outputs, Vin pin is for analog inputs Diamond Systems cable number C-50-18 provides a standard 50-pin connector at each end and mates with this header. Connector type: Standard .1” single row straight pin header with gold flash plating 7. -

Page 30: Lcd Panel Voltage Select (Jp5)

It is possible to set up all three circuits to share either IRQ4 or IRQ5. However, only one device can use the shared IRQ at a time; the ability for all three devices to run simultaneously is not supported. Configure the IRQ options as shown in the following jumper settings. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 31: Rs-232/422/485 Termination Select (Jp7)

IRQ Configuration Options RS-232/422/485 Termination Select (JP7) Jumper block JP7 is used to configure RS-232/422/485 termination selection. JP7 RS-232/422/485 Default Jumper Settings www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 32: Data Acquisition Configuration (Jp26)

±35V. If you connect the analog inputs on Athena to a circuit whose ground potential plus maximum signal voltage exceeds ±35V, the analog input circuit may be damaged. Check the ground difference between the input source and Athena III before connecting analog input signals. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 33: Unipolar/Bipolar Input Settings

0V is halfway between -10V and +10V, for the ±10V range. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 34: System Operation

F2 (some programs or configurations trap special characters). The default Athena III BIOS setting disables console redirection. There are three possible configurations for console redirection: POST-only (default) Always On Disabled www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 35: Flash Memory

Over-current condition on output power line The ISA Reset signal is an active high pulse with a 200ms duration. The PCI Reset is active low, with a typical pulse width duration of 200 msec. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 36: Bios

This setting has no direct affect on PCI or memory speeds; it only affects ISA PC/104 devices. It is best to leave this setting at “Normal,” if there are no ISA I/O performance issues. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 37: Bios Console Redirection Settings

Console Connection: Direct (default) or Modem. Console Type: PC ANSI (default), VT100, VT100 (8-bit), PC-ANSI (7-bit), VT100+, or VT-UTF8. Flow Control: CTS/RTS (default), XON-XOFF, None. Number of video Pages to support: 1(default) to 8. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 38: System I/O

Note: Once these jumper selections are made, the user must update the Serial Port IRQ settings to match these selections. The IRQ settings are NOT auto detected in the same way as the address settings. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 39: Usb Ports

3. Insert the DOS installation floppy disk into the USB floppy drive and start/restart the system. 4. Install any drivers needed. Note: For DOS Ethernet, set Operating System to other in the BIOS. Note: DOS Sound emulation is currently not functional. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 40: Data Acquisition Circuit

The interrupt level is changed with jumper block JP7 and also with the IRQ number in the BIOS. The figure on the next page shows a block diagram of the data acquisition circuit. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 41: Data Acquisition Circuitry I/O Map

Write enable Page 1 select read back check Page 2 Base + Write Function Read Function ADC expanded FIFO ADC expanded FIFO ADC control ADC control Page 2 select read back check www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 42: Register Map Bit Summary

Base + CtrD7 CtrD6 CtrD5 CtrD4 CtrD3 CtrD2 CtrD1 CtrD0 CtrD15 CtrD14 CtrD13 CtrD12 CtrD11 CtrD10 CtrD9 CtrD8 CtrD23 CtrD22 CtrD21 CtrD20 CtrD19 CtrD18 CtrD17 CtrD16 CTRNO LATCH GTDIS GTEN CTDIS CTEN LOAD www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 43 Page 2 Write Register Summary Base + EXFIFO DACPOLE DACPOL ADPOL ADPOLEN ADSD ADSDEN SCANINT DAQ_LED Page 2 Read Register Summary Base + EXFIFO DACPOLE DACPOL ADPOL ADPOLEN ADSD ADSDEN SCANINT -- 0xA2 -- www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 44: Main Registers

The user’s interrupt routine must write to the appropriate bit prior to exiting in order to enable future interrupts. Otherwise the interrupt line will stay high indefinitely and no additional interrupt requests will be generated by the board. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 45 A/D data bits 15 – 8; AD15 is the MSB; A/D data is an unsigned 16-bit value. AD15 - 8 See Base + 0 Read on the previous page for information on A/D values and formulas. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 46 LOW and HIGH. For example, if LOW = 0 and HIGH = 3, the A/D channels will progress through the following sequence: 0, 1, 2, 3, 0, 1, 2, 3, 0, 1, …. Reading from this register returns the value previously written to it. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 47 Only one ADWAIT period must be observed between the last triggering condition (write to Base + 2 or Base + 3) and the start of an A/D conversion. The following table lists the possible analog input ranges: ADG1 ADG0 Gain Unipolar Range Bipolar Range 0-10V ±10V 0-5V ±5V 0-2.5V ±2.5V 0-1.25V ±1.25V www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 48 SCANEN Scan mode readback (see Base + 3 Write above). ADG1-0 A/D gain setting readback (see Base + 3 Write above). www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 49 The user’s interrupt routine must monitor the status bits to know which circuit has requested service. After processing the data but before exiting, the interrupt routine must then clear the appropriate interrupt request bit using the register at Base + 0. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 50 When EXFIFO = 1 (Enhanced Mode, See Register Description for Page 2 Base+12) Current FIFO Depth LSB. This value indicates the lower 8 bits of the number of A/D values currently stored in the FIFO. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 51 FIFO Full Bit. The next conversion will result in an overflow. FIFO Half Full Bit. FIFO is at least half full containing at least 1k words of A/D data. FIFO Empty. FIFO is empty. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 52 Read / Write Digital I/O Port B Bit No. Name Reset These registers are used for digital I/O on PortB. The direction of each register is controlled by the DIO control register at Base+11. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 53 Instead, a read of the register at Page 2, Base+15 will cause the update of the D/A converter. Base + 11 Read Digital I/O and DA Control Register Readback Bit No. Name DASIM DIRA DIRCH DIRB DIRCL Reset Read-back of Base+11. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 54: Counter / Timer Control

1, this register is ignored. When reading from this register, the MSB value of the most recent Latch command for counter 0 will be returned. The value returned is NOT the value written to this register. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 55 FPGA Revision Code Bit No. Name REV7 REV6 REV5 REV4 REV3 REV2 REV1 REV0 Reset REV7-0 Revision code, read as a 2-digit hex value. The first rev of this FPGA should be 0x48. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 56: Register Definitions

TDACWR TrimDAC Write. Writing 1 to this bit will initiate a transfer to the TrimDAC addressed by the register at page 1, base+13. (used in the autocalibration process). If both EE_EN and TDACWR are set to ‘1’ then TDACWR is ignored. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 57: P Age 2 R Egister D Efinitions

11-bit value. ADC Expanded FIFO: Base+12 (Write) Bit: Name: ADCEXF ADCEXF ADC expanded FIFO mode flag. 0 = Not in expanded FIFO mode. 1 = In expanded FIFO mode. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... - Page 58 SEDIFOE Output enable. When set, the SEDIFDI value is gated to the output. Page 2 Select Read Back Check: Base+15 (Read) Bit: Name: PG2ID PGID Register page 2 ID. This register always contains the value 0xA2. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 59: Analog-To-Digital Input Ranges And Resolution

Resolution 1LSB Bipolar ±10V 305µV Bipolar ±5V 153µV Bipolar ±2.5V 76µV Bipolar ±1.25V 38µV Unipolar Invalid Invalid Unipolar 0 - 10V 153µV Unipolar 0 - 5V 76µV Unipolar 0 - 2.5V 38µV www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 60: Athena Iiii User Manual Rev A.00 Www.diamondsystems.com

A/D if AINTE = 0 (interrupts are disabled). When AINTE = 1, the A/D can only be triggered by the on- board counter/timer or an external signal. This protects against accidental triggering by software during a long- running interrupt-based acquisition process. outp(base,0x80); www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 61: Wait For The Conversion To Finish

FIFO. The FIFO depth register increments by the scan size. When STS goes low, the program should read out the data for all channels. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 62: Convert The Numerical Data To A Meaningful Value

A/D Code Input Voltage Symbolic Formula Input Voltage for 5V Range -32768 -5.0000V -32767 + 1 LSB -4.9998V -1 LSB -0.00015V 0.0000V +1 LSB 0.00015V 32767 - 1 LSB 4.9998V www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 63: Conversion Formula For Unipolar Input Ranges

Input Voltage for 5V Range -32768 0.0000V -32767 1 LSB (V / 65536) 0.000076V / 2 - 1 LSB 2.4999V 2.5000V / 2 + 1 LSB 2.5001V 32767 - 1 LSB 4.9999V www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 64: A/D Scan, Interrupt And Fifo Operation

The table on the next page describes the board’s behavior for each of the 4 possible cases of AINTE and SCANEN. The given interrupt software behavior describes the operation of the Diamond Systems Universal Driver software. If you write your own software or interrupt routine you should conform to the described behavior for optimum results. - Page 65 STS stays high during the entire scan (multiple A/D conversions). A/D interrupt occurs when the FIFO reaches its programmed threshold. The interrupt routine reads the number of samples equal to the FIFO threshold (Base+5, bits 0-5). www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 66: Digital-To-Analog Output Ranges And Resolution

In most cases, for unipolar mode configure the board to reset to zero scale, and for bipolar mode configure the board for reset to mid-scale. In each case, the DACs reset to 0V. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 67: D/A Conversion Formulas And Tables

Output Voltage for 0-10V Range 0.0000V 1 LSB (V / 4096) 0.0024V 2047 / 2 - 1 LSB 4.9976V 2048 5.0000V 2049 / 2 + 1 LSB 5.0024V 4095 - 1 LSB 9.9976V www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 68: D/A Conversion Formulas For Bipolar Output Ranges

(VREF = Reference voltage). D/A Code Output Voltage Symbolic Formula Output Voltage for 10V Range -10.0000V + 1 LSB -9.9951V 2047 -1 LSB -0.0049V 2048 0.0000V 2049 +1 LSB 0.0049V 4095 - 1 LSB 9.9951V www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 69: Generating An Analog Output

The status bit DACBUSY (Base+3, bit 4) indicates if the D/A is busy updating (1) or idle (0). After writing to the D/A, monitor DACBUSY until it is zero before continuing with the next D/A operation. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 70: Analog Circuit Calibration

A/D and D/A circuits to within the specified tolerances regardless of time and temperature. Autocalibration is supported in the Diamond Systems Universal Driver software included with the board. The autocalibration circuit uses an ultra-stable +5V reference voltage IC as the source for its calibration. Both A/D and D/A circuits are calibrated in the analog domain by using a series of 8-bit “TrimDACs”... -

Page 71: Digital I/O Operation

C7-C4. When DIOCTR = 0, the lines are used for the counter/timer. Pin direction for DIOCTR = Pin No. DIOCTR = 1 DIOCTR = 0 Gate0 Input Gate1 Input Clk1 Input Out0 Output www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 72: Counter/Timer Operation

26 is of interest. In totalizer/counter mode, the counter value is of interest and may be read by first latching the value and then reading it. The width of the pulse is equal to the time period of the selected counters clock source. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 73: Command Sequences

20.3 Command Sequences Diamond Systems provides driver software to control the counter/timers on Athena III. The information in this section is intended as a guide for programmers writing their own code, instead of using the driver, and to give a better understanding of the counter/timer operation. -

Page 74: Disabling The Counter Gate Command

The value is returned in 3 bytes, low, middle, and high (2 bytes for counter 1). Counter 0: Counter 1: low=inp(base+12); low=inp(base+12); middle=inp(base+13); high=inp(base+13); high=inp(base+14); 23. Clear the counter. Counter 0: Counter 1: outp(base+15,0x01); outp(base+15,0x81); www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 75: Usb Flashdisk Module

Flashdisk Module 21.1 Installing the Flashdisk Module The flashdisk module installs directly on connector J14 and is held down with a spacer and two screws onto a mounting hole on the board. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 76: Bios Option Listing

Save changes and exit BIOS setup mode At any time, select Save & Exit to exit BIOS setup mode. Use the up/down arrow keys, followed by carriage return, to apply one of the exit actions. www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 77: Bios Screen Descriptions

This section describes the screen displays for each BIOS setup area. The data in the fields are examples only and may be different depending on future product releases from Diamond Systems or the user’s configuration. Sub-menus are prefixed with a . - Page 78 Bootup NumLock State [On] CSM16 Module Version 07.65 GateA20 Active [Upon Request] Option ROM Messages [Force BIOS] Interrupt 19 Capture [Disabled] Boot Option Priorities Boot Option #1 [Disabled] Security Administrator Password User Password www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

- Page 79 Discard Changes and Exit Save Changes and Reset Discard Changes and Reset Save Options Save Changes Discard Changes Restore Defaults Save as User Defaults Restore as User Defaults Boot Override Built-in EFI Shell www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

-

Page 80: Specifications

A/D and D/A Calibration: Automatic using on-board microcontroller and temperature sensor Analog Outputs: 4, 12-bit resolution Output ranges: ±5V, ±10V, 0-5V, 0-10V Output current: ±5mA max per channel Settling time: 7µS max to 0.01% Relative accuracy: ±1 LSB Nonlinearity: ±1 LSB, monotonic www.diamondsystems.com Athena IIII User Manual Rev A.00 Page... -

Page 81: Power Supply

Power Supply Input Voltage: +5VDC ±5% Power consumption: 9.4W 23.4 General Shock: IEC68-2-27 compatible Vibration: MIL-STD-810E 514.4 compatible Dimensions: 4.18 x 4.48 in. (106 x 114mm) Weight: 8.8oz.(249g) with heat sink RoHS: Compliant www.diamondsystems.com Athena IIII User Manual Rev A.00 Page...

Need help?

Do you have a question about the Athena IIII and is the answer not in the manual?

Questions and answers