Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for iWave iW-RainboW-G49D

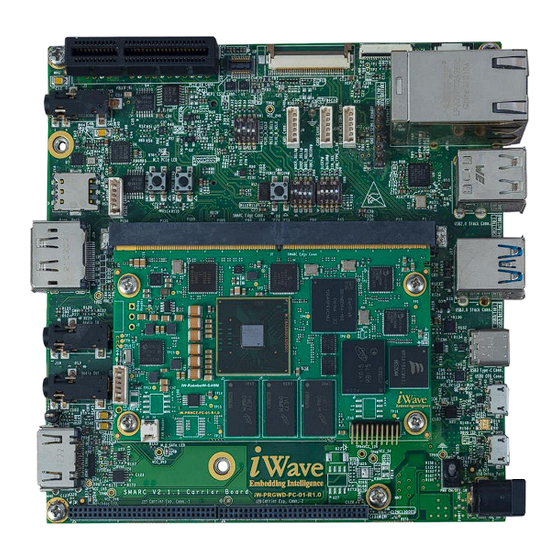

- Page 1 LS1021A SMARC Development Platform Hardware User Guide iW-RainboW-G49D QorIQ Layerscape LS1021A SMARC Development Platform Hardware User Guide DRAFT VERSION SUBJECTED TO CHANGE REL0.1 iWave Systems Technologies Pvt. Ltd. Page 1 of 65...

- Page 2 If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. “iWave Systems Tech. Pvt. Ltd.” REL0.1 iWave Systems Technologies Pvt.

- Page 3 No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

-

Page 4: Table Of Contents

TECHNICAL SPECIFICATION .......................... 57 OWER NPUT EQUIREMENT ................................OWER UTPUT PECIFICATION ............................... NVIRONMENTAL HARACTERISTICS ..............................3.3.1 Environmental Specification ........................59 3.3.2 RoHS Compliance ............................59 3.3.3 Electrostatic Discharge ..........................59 ECHANICAL HARACTERISTICS ............................... REL0.1 iWave Systems Technologies Pvt. Ltd. Page 4 of 65... - Page 5 LS1021A SMARC Development Platform Hardware User Guide 3.4.1 Layerscape LS1021A SMARC Carrier Board Mechanical Dimensions ............60 3.4.2 Guidelines to insert the SMARC SOM into Carrier Board ................62 ORDERING INFORMATION .......................... 64 REL0.1 iWave Systems Technologies Pvt. Ltd. Page 5 of 65...

- Page 6 ECHANICAL DIMENSIONS OF AYERSCAPE ARRIER OARD OTTOM IEW ..........21: M LS1021A SMARC C IGURE ECHANICAL DIMENSIONS OF AYERSCAPE ARRIER OARD IEW ........... 22: SOM I IGURE NSERTION UIDELINE ................................REL0.1 iWave Systems Technologies Pvt. Ltd. Page 6 of 65...

- Page 7 ONFIGURATION WITCH ..............................11: P ABLE OWER NPUT EQUIREMENT ................................12: P ABLE OWER UTPUT PECIFICATION ................................ 13: E ABLE NVIRONMENTAL PECIFICATION ............................... 14: O ABLE RDERABLE RODUCT UMBERS ............................. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 7 of 65...

-

Page 8: Introduction

This document is the Hardware User Guide for the Layerscape LS1021A SMARC V2.1.1 Development platform “iW- RainboW-G49D” based on the NXP’s LS1021A Application processor. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the Layerscape LS1021A based SMARC development platform from a Hardware Systems perspective. - Page 9 Serial Advanced Technology Attachment Secure Digital SMARC Smart Mobility ARChitecture System On Module To Be Defined UART Universal Asynchronous Receiver/Transmitter Universal Serial Bus USB OTG USB On The Go Voltage REL0.1 iWave Systems Technologies Pvt. Ltd. Page 9 of 65...

-

Page 10: Terminology Description

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On-SMARC SOM. References • LS1021A_Rev7.pdf • LS1021ARM_Rev3.1.pdf • SMARC Specification V2.1.1 REL0.1 iWave Systems Technologies Pvt. Ltd. Page 10 of 65... -

Page 11: Architecture And Design

Layerscape LS1021A SMARC Development Platform Block Diagram iW-RainboW-G49D_Layerscape_LS1021A_SMARC Development Kit Block Diagram Bottom Bottom Bottom PCIe0 PCIe1 PCIe0 PCIe1 PCIe2 PCIe3 iWave Systems Technologies Pvt. Ltd. mktg@iwavesystems.com Layerscape LS1021A Figure 1: SMARC Development Platform Block Diagram REL0.1 iWave Systems Technologies Pvt. Ltd. Page 11 of 65... -

Page 12: Layerscape Ls1021A Smarc Development Platform Features

Force Boot Switch (Not supported) Carrier board Expansion Connectors • SPI x 1 Port • CAN x 1 Port • USB3.0 Host x 2 Ports (through On-SOM USB Hub) • UART x 1 Port REL0.1 iWave Systems Technologies Pvt. Ltd. Page 12 of 65... - Page 13 At a time, do not set Both the PCIe Channel A & B neither to M.2 connector nor to PCIe X4 connector. Either USB Type C connector or USB 3.0 Type A TOP connector can be supported at a time. Anyone can be selected using on Board Switches. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 13 of 65...

-

Page 14: Smarc Mxm Connector

This standard 314-pin robust connector is capable of handling high-speed serialized signals and can be used for size constrained embedded applications. This SMARC MXM connector (J18) is physically located at the top of the board as shown below. Figure 2: SMARC MXM Connector REL0.1 iWave Systems Technologies Pvt. Ltd. Page 14 of 65... -

Page 15: Smarc Pcb Edge Connector Pin Assignment

GBE0_MDI2+ IO, GBE Gigabit Ethernet MDI differential pair 2 positive. GBE0_LINK_ACT# GBE0_LINK_ACT# I, 3.3V CMOS Gigabit Ethernet activity status GBE0_MDI1- GBE0_MDI1- IO, GBE Gigabit Ethernet MDI differential pair 1 negative. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 15 of 65... - Page 16 IO, 1.8/3.3V NC (Note: Optionally SD CMOS 10K Data3.) Note: 10K pullup option is provided. SPI0_CS0# SPI0_CS0# SPI1_PCS0 SPI1_PCS0/D O, 1.8V CMOS SPI0_CK SPI0_CK SPI1_SCK SPI1_SCK/C1 O, 1.8V CMOS/ 33E Series REL0.1 iWave Systems Technologies Pvt. Ltd. Page 16 of 65...

- Page 17 USB2.0 Port0 Data Minus. SMARC General Purpose USB0_EN_OC# GPIO3_14_3V3 GPIO3_14/AC6 IO, 3.3V CMOS 10k Input/output USB0_VBUS_DET LS_USB1_VBUS LS_USB1_VBUS/C1 5V, Power USB host power detection, when this port is used as a device. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 17 of 65...

- Page 18 Note: Connected to USB Hub. PCIE_B_CKREQ# GPIO2_15_3V3 IFC_PERR_B/C15 IO, 3.3V NC: (Optionally SMARC CMOS 10k General Purpose Input/output.) PCIE_A_CKREQ# GPIO2_15_3V3 IFC_PERR_B/C15 IO, 3.3V NC: (Optionally SMARC CMOS 10k General Purpose Input/output.) REL0.1 iWave Systems Technologies Pvt. Ltd. Page 18 of 65...

- Page 19 NC (Note: Optionally USB3.0 DP1_LANE0- Port3 Receive Minus,Connected to USB Hub.) Power Ground. HDMI_D1+ / USB3_HUB4_TXP O, USB SS NC (Note: Optionally USB3.0 DP1_LANE1+ Port3 Transmit Plus,Connected to USB Hub.) REL0.1 iWave Systems Technologies Pvt. Ltd. Page 19 of 65...

- Page 20 SMARC General Purpose CAM0_RST# CMOS Input/output P111 GPIO3 / GPIO3_13_1V8 GPIO3_13/AC3 IO, 1.8V SMARC General Purpose CAM1_RST# CMOS Input/output P112 GPIO4 / GPIO1_13 ASLEEP/E6 IO, 1.8V SMARC General Purpose HDA_RST# CMOS Input/output REL0.1 iWave Systems Technologies Pvt. Ltd. Page 20 of 65...

- Page 21 I, 1.8V CMOS Power ON /OFF Input to SOM. Note:Its connected to PMIC P129 SER0_TX UART1_SOUT UART1_SOUT/N1 O, 1.8V UART1 Transmitter. CMOS P130 SER0_RX UART1_SIN UART1_SIN/M1 I, 1.8V CMOS UART1 Receiver. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 21 of 65...

- Page 22 P154 VDD_IN VDD_SMARC_IN O, 5V Power Supply Voltage P155 VDD_IN VDD_SMARC_IN O, 5V Power Supply Voltage P156 VDD_IN VDD_SMARC_IN O, 5V Power Supply Voltage SMARC Secondary Side CSI1_TX+ / I2C_CAM1_CK REL0.1 iWave Systems Technologies Pvt. Ltd. Page 22 of 65...

- Page 23 Second Gigabit Ethernet MDI differential pair 2 positive. GBE1_MDI2- GBE1_MDI2- IO, GBE Second Gigabit Ethernet MDI differential pair 2 negative. Power GBE1_MDI3+ GBE1_MDI3+ IO, GBE Second Gigabit Ethernet MDI differential pair 3 positive. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 23 of 65...

- Page 24 Serial Audio Interface Channel3 Data Input O, 1.8V Serial Audio Interface I2S0_CK SAI3_TX_BCLK SAI3_TX_BCLK/J3 CMOS/ Channel3 Clock 33E Series ESPI_ALERT0# ESPI_ALERT1# MDIO_CLK SMARC_EMI1_MDC LS_EMI1_MDC/AB2 I, 1.8V CMOS Management Interface Clock REL0.1 iWave Systems Technologies Pvt. Ltd. Page 24 of 65...

- Page 25 USB3_SSTX+ USB3_HUB2_TXP O, USB SS NC (Note: Optionally USB3.0 Port1 Transmit Plus,Connected to USB Hub.) NC (Note: Optionally USB3.0 USB3_SSTX- USB3_HUB2_TXM O, USB SS Port1 Transmit Minus,Connected to USB Hub.) REL0.1 iWave Systems Technologies Pvt. Ltd. Page 25 of 65...

- Page 26 NC (Note: Optionally USB3.0 Port0 Receive Plus,Connected to USB Hub.) PCIE_C_RST# GPIO2_15_3V3 IFC_PERR_B/C15 IO, 3.3V SMARC General Purpose CMOS 10k Input/output PCIE_C_RX+ / LS_SD1_RX2_P LS_SD1_RX2_P/AC I, PCIe PCIe Channel-C Receive SERDES_1_RX+ Positive. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 26 of 65...

- Page 27 AC Couple Positive. PCIE_B_TX- LS_SD1_TX1_N LS_SD1_TX1_N/Y11 O, PCIe 0.1uF PCIe Channel-B Transmit AC Couple Negative. Power Ground. DP0_LANE0+ DP0_LANE0- DP0_AUX_SEL DP0_LANE1+ DP0_LANE1- DP0_HPD DP0_LANE2+ S100 DP0_LANE2- S101 Power Ground. S102 DP0_LANE3+ REL0.1 iWave Systems Technologies Pvt. Ltd. Page 27 of 65...

- Page 28 LCD1_VDD_EN LVDS1_2+ / S117 eDP1_TX2+ / DSI1_D2+ LVDS1_2- / S118 eDP1_TX2- / DSI1_D2- S119 Power Ground. S120 LVDS1_3+ / eDP1_TX3+ / DSI1_D3+ S121 LVDS1_3- / eDP1_TX3- / DSI1_D3- S122 LCD1_BKLT_PWM REL0.1 iWave Systems Technologies Pvt. Ltd. Page 28 of 65...

- Page 29 LCD0_VDD_EN S134 LVDS0_CK+ / eDP0_AUX+ / DSI0_CLK+ LVDS0_CK- / S135 eDP0_AUX- / DSI0_CLK- S136 Power Ground. S137 LVDS0_3+ / eDP0_TX3+ / DSI0_D3+ LVDS0_3- / S138 eDP0_TX3- / DSI0_D3- S139 I2C_LCD_CK REL0.1 iWave Systems Technologies Pvt. Ltd. Page 29 of 65...

- Page 30 Module boot device to be rewritten / restored from an external USB Host on Module USB0. The Module USB0 operates in Client Mode when in the Force Recovery function is invoked. S156 BATLOW# REL0.1 iWave Systems Technologies Pvt. Ltd. Page 30 of 65...

-

Page 31: Serial Interface Features

1.8V to 3.3V level Translator and FT232RQ is connected to USB Micro AB Connector (J24). This USB Micro AB Connector can be used for Debug purpose which is physically located at the top of the board as shown below. Figure 3: Debug UART Port REL0.1 iWave Systems Technologies Pvt. Ltd. Page 31 of 65... -

Page 32: Data Uart Interface

3.3V Supply Voltage. UART_RXD UART1_RX I, 3.3V CMOS UART1 interface Receive signal. UART_TXD UART1_TX O, 3.3V CMOS UART1 interface Transmit signal. UART_CTS# UART1_CTS_B O, 3.3V CMOS UART1 interface Clear to Send signal. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 32 of 65... -

Page 33: Rs232 Uart Interface (Optional)

RS232 UART header is physically located at the top of the board as shown below. Number of Pins Connector Part number : 53047-0610 from Molex Mating Connector Hosuing : 0510210600 from Molex Figure 5: RS232 UART Header REL0.1 iWave Systems Technologies Pvt. Ltd. Page 33 of 65... -

Page 34: High Speed Interface Features

Refer Dip Switch (SW1) Settings in “Table 14: Board Configuration Switch” for more details on selecting PCIe connector. PCIex4 Connector: PCIeX4 connector (J5) is physically located at the top of the board as shown below Figure 6: PCIex4 Connector REL0.1 iWave Systems Technologies Pvt. Ltd. Page 34 of 65... -

Page 35: Table 5: Pciex4 Connector Pinout

I, PCIe PCIe Port 0 Receive pair positive. Note: Refer SW1 setting from Table 10 to support PCIE0_RX. Power Ground. PCIE0_RX- LS_SD_RX0_P I, PCIe PCIe Port 0 Receive pair negative. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 35 of 65... - Page 36 Power Ground. Power Ground. PCIE3_TX+ LS_SD1_TX3_P PCIe Port 3 Transmit pair positive. Power Ground. PCIE3_TX- LS_SD1_TX3_N PCIe Port 3 Transmit pair negative. PCIE3_RX+ LS_SD1_RX3_P PCIe Port 3 Receive pair positive. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 36 of 65...

-

Page 37: Table 6: M.2 Pcie Connector Pinout

PCIe M.2 Connector: The Layerscape LS1021A SMARC carrier board supports M.2 Key-B Connector (J32) and is placed at the bottom side of the board.+ M.2 Connector Figure 7: Refer below table for M.2 connector pinout details. Table 6: M.2 PCIe Connector Pinout REL0.1 iWave Systems Technologies Pvt. Ltd. Page 37 of 65... - Page 38 Input _RX) (I/O)(0/1.8V) SAI4_RX_DATA GPIO11(WOWWAN# /HSIC_DATA(1.2V))(I /O) (0/1.8V) GPIO7(AUDIO2/I2S_ O, 1.8V CMOS Serial Audio Interface Channel1 Data TX) (I/O)(0/1.8V) Output SAI4_TX_DATA DPR (O) (0/1.8V) GPIO10_(W_DISABLE _2#/HSIC_STROBE(1. 2V)) (I/O)(0/1.8V) Power Ground. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 38 of 65...

- Page 39 Note: To select PCIe Chanel Refer Table GPIO2_(ALERT# /GNSS_IRQ/UIM_CLK 2)(I)/(0/1.8V) Power Ground. GPIO3(SYSCLK/GNSS _0/UIM_RST2) (I/O)(0/1.8V) PETN0/SATA_A- LS_SD1_TX0_N I, PCIe PCIe Channel-A/B Transmit Negative. Note: To select PCIe Chanel Refer Table REL0.1 iWave Systems Technologies Pvt. Ltd. Page 39 of 65...

- Page 40 3.3V Supply Voltage. Power Ground. VCC_3V3 VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. Power Ground. VCC_3V3 VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. CONFIG_2 M.2_CONFIG_2 I, 1.8V CMOS M.2 Configuration Pin 2. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 40 of 65...

-

Page 41: Sata M.2 Interface (Optional)

M.2_CONFIG_3 I, 1.8V CMOS M.2 Configuration Pin 3. 10K PU VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. VCC_3V3 Power Ground. VCC_3V3 VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. Power Ground. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 41 of 65... - Page 42 10K PU Mounted _2#/HSIC_STROBE(1. 2V)) (I/O)(0/1.8V) Power Ground. GPIO8(AUDIO3/I2S_ WS)(I/O)(0/1.8V) PERN1/USB30_RX- /SSIC_RX- UIM-RESET (I) M2_UIM_RST O, SIM SIM Card Reset Signal. PERP1/USB30_RX+/S SIC_RX+ UIM-CLK (I) M2_UIM_CLK I, SIM SIM Card Clock Signal. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 42 of 65...

- Page 43 GPIO4(TX_BLK/GNSS _1/UIM_PWR2)(I/O)( 0/1.8V) PETP0/SATA_A+ LS_SD1_TX0_P I, SATA SATA Channel Transmit Positive. PERST# (O)(0/3.3V) Power Ground. CLKREQ# (I/O)(0/3.3V) REFCLKN PEWAKE# (I/O)(0/3.3V) REFCLKP MFG_DATA Power Ground. MFG_CLOCK ANTCTL0 (I)(0/1.8 V) COEX3 (I/O)(0/1.8V) REL0.1 iWave Systems Technologies Pvt. Ltd. Page 43 of 65...

- Page 44 Ground. VCC_3V3 VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. Power Ground. VCC_3V3 VCC_3V3 O, 3.3V Power 3.3V Supply Voltage. CONFIG_2 M.2_CONFIG_2 I, 1.8V CMOS M.2 Configuration Pin 2. 10K PU REL0.1 iWave Systems Technologies Pvt. Ltd. Page 44 of 65...

-

Page 45: Usb3.0 Host Interface

SMARC MXM connector USB2 and USB3 ports. This USB3.0 connector is physically located at the top of the board as shown below. Figure 9: USB3.0 Host REL0.1 iWave Systems Technologies Pvt. Ltd. Page 45 of 65... -

Page 46: Communication Interface Features

(Yellow) and Link/Activity (Green) LED indications on RJ45 Magjack. This RJ45 Magjack combo connector is physically located at the top of the board as shown below. Figure 10: RJ45 Magjack REL0.1 iWave Systems Technologies Pvt. Ltd. Page 46 of 65... -

Page 47: Usb2.0 Host Interface

SMARC MXM connector USB1 and USB4 ports. This USB2.0 connector is physically located at the top of the board as shown below. Figure 11: USB2.0 Host REL0.1 iWave Systems Technologies Pvt. Ltd. Page 47 of 65... -

Page 48: Usb2.0 Otg Interface

USB0_EN_OC# should drive low to disable the power to the connector. This USB2.0 OTG connector is physically located at the top of the board as shown below. Figure 12: USB2.0 OTG REL0.1 iWave Systems Technologies Pvt. Ltd. Page 48 of 65... -

Page 49: Sdio Interface (Optional)

This power enable/disable is controlled from the SDIO_PWR_EN pin of SMARC MXM connector. The SD connector (J34) is physically located at the bottom of the board. Figure 13:Standard SD Connector REL0.1 iWave Systems Technologies Pvt. Ltd. Page 49 of 65... -

Page 50: Can Interface

5V Supply Voltage. VCC_12V Note: Optionally connected to 12V supply Volatge. CANL CAN0_LOW IO, DIFF CAN0 Low-Level Voltage I/O Power Ground. CANH CAN0_HIGH IO, DIFF CAN0 High-Level Voltage I/O Power Ground. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 50 of 65... -

Page 51: Table 9: Can1 Header Pinout

5V Supply Voltage. VCC_12V Note: Optionally connected to 12V supply Volatge. CANL CAN1_LOW IO, DIFF CAN1 Low-Level Voltage I/O Power Ground. CANH CAN1_HIGH IO, DIFF CAN1 High-Level Voltage I/O Power Ground. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 51 of 65... -

Page 52: Audio Feature

Headphone Stereo output and Mono Mic input through 3.5mm single audio Jack J7. Second Codec is not supported in default BSP, contact iWave support team for enabling second I2S Audio Codec “WM8960CGEFL/RV”. These Audio Jacks are physically located at the top of the board as shown below. -

Page 53: Additional Features

) for RTC back up voltage when VCC main power is off. This Coin Cell Holder (J37) is physically located on bottom of the board as shown below. Figure 16: RTC Battery Holder REL0.1 iWave Systems Technologies Pvt. Ltd. Page 53 of 65... -

Page 54: On Board Switches

1-Switch OFF State Reference (Pulled High) Select [SEL2,SEL1] image 0 -Switch ON (GND) Hi-Z (DIP SW) PCIe_A_SEL2 Note: At a time, do not set Both the M.2 Lane0 PCIe Channel REL0.1 iWave Systems Technologies Pvt. Ltd. Page 54 of 65... - Page 55 000- Boot from SOM FlexSPI (Optional) (Floating) BOOT_SEL1# 001- Boot from SOM eMMC (Default) (DIP SW) 011- Boot from SOM microSD 1 -Switch ON (Optional) BOOT_SEL2# (GND) 110- Boot from Carrier Board SD REL0.1 iWave Systems Technologies Pvt. Ltd. Page 55 of 65...

- Page 56 Type A (J17, Top) USB Type C (J20) connector. connector. Carrier Board Main 12V Carrier Board Carrier board (Toggle Carrier Power ON/ OFF Switch Power Power is ON Power is OFF On/Off Switch. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 56 of 65...

-

Page 57: Technical Specification

Plugs with an inner dimension of 2.5mm and an outer dimension of 5.5mm. This connector is physically placed at the top of the board as shown below. Figure 18: Power Jack REL0.1 iWave Systems Technologies Pvt. Ltd. Page 57 of 65... -

Page 58: Power Output Specification

Power to Add-On Module (through Expansion Connector1) VCC_5V 4.85V 5.15V 1000mA VCC_3V3 3.15 3.45 1000mA VCC_1V8 1000mA Power to Add-On Module (through Expansion Connector2) VCC_5V 4.85V 5.15V 1000mA VCC_3V3 3.15 3.45 1000mA VCC_1V8 1000mA REL0.1 iWave Systems Technologies Pvt. Ltd. Page 58 of 65... -

Page 59: Environmental Characteristics

3.3.3 Electrostatic Discharge iWave’s Layerscape LS1021A SMARC Development Platform is sensitive to electrostatic discharge and so high voltages caused by static electricity could damage some of the devices on board. It is packed with necessary protection while shipping. -

Page 60: Mechanical Characteristics

Layerscape LS1021A SMARC Development Platform PCB size is 120 mm x 120 mm x 1.6mm. SMARC carrier card mechanical dimensions is shown below. (All dimensions are shown in mm) Figure 19: Mechanical dimensions of Layerscape LS1021A SMARC Carrier Board- Top View REL0.1 iWave Systems Technologies Pvt. Ltd. Page 60 of 65... -

Page 61: Figure 20: Mechanical Dimensions Of Layerscape Ls1021A Smarc Carrier Board- Bottom View

Ethernet Jack J8 (28.58mm) followed by USB3.0 Stack slot J17(15.6mm) and bottom side maximum height component is inductor (7.3mm). Please refer the below figure which gives height details of the i.MX8 SMARC Development kit. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 61 of 65... -

Page 62: Figure 21: Mechanical Dimensions Of Layerscape Ls1021A Smarc Carrier Board - Side View

Once the SMARC module is inserted to the MXM connector properly, press the board vertically down as shown below, such that the board is fixed firmly into the expansion connectors and fix the board by screwing. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 62 of 65... -

Page 63: Figure 22: Som Insertion Guideline

LS1021A SMARC Development Platform Hardware User Guide Figure 22: SOM Insertion Guideline REL0.1 iWave Systems Technologies Pvt. Ltd. Page 63 of 65... -

Page 64: Table 14: Orderable Product Part Numbers

LS1021A, Dual Cortex A7, 1.2 GHz CPU, 2GB DDR4 with iW-G49D-SC02-4L002G-E016G-LCA 0°C to 60°C ECC, 16GB eMMC, TPM Note: For Development platform identification purpose, Product part number is pasted as Label with Barcode readable format. REL0.1 iWave Systems Technologies Pvt. Ltd. Page 64 of 65... - Page 65 LS1021A SMARC Development Platform Hardware User Guide REL0.1 iWave Systems Technologies Pvt. Ltd. Page 65 of 65...

- Page 66 Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: iWave Systems iW-G49D-SC02-4E002G-E016G-LCA...

Need help?

Do you have a question about the iW-RainboW-G49D and is the answer not in the manual?

Questions and answers