Table of Contents

Advertisement

Quick Links

A

- F

P

C

N Y

R E Q U E N C Y

R E C I S I O N

L O C K S

S i5 3 1 6 , S i 531 9, S i 5 3 2 2 , S i5 3 2 3 , S i5 3 2 4 , Si 5 3 2 5 ,

S i5 3 2 6 , S i 532 7, S i 5 3 2 8 , S i5 3 6 5 , S i5 3 6 6 , Si 5 3 6 7 ,

Si5 368 , S i 53 69 , S i5 3 7 4 , S i5 3 7 5 , S i5 3 7 6

F

R

M

A M I L Y

E F E R E N C E

A N U A L

Rev. 1.3 10/16

Copyright © 2016 by Silicon Laboratories

Si53xx-RM

Advertisement

Table of Contents

Summary of Contents for Silicon Laboratories Si5328

- Page 1 Si5 368 , S i 53 69 , S i5 3 7 4 , S i5 3 7 5 , S i5 3 7 6 A M I L Y E F E R E N C E A N U A L Rev. 1.3 10/16 Copyright © 2016 by Silicon Laboratories Si53xx-RM...

- Page 2 Si 53 xx -RM Rev. 1.3...

-

Page 3: Table Of Contents

3.9. Si5328 ........ - Page 4 6.1.1. Jitter Tolerance (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) ......63 6.1.2.

- Page 5 6.11.1. Loss-of-Signal Alarms (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) ..... . . 84 6.11.2.

- Page 6 7.4. Crystal/Reference Clock Interfaces (Si5316, Si5319, Si5323, Si5324, Si5326, Si5327, Si5328, Si5366, Si5368, Si5369, Si5374, Si5375, and Si5376) . .102 7.5. Three-Level (3L) Input Pins (No External Resistors) ..... . .104 7.6.

- Page 7 Figure 24. Narrowband PLL Divider Settings (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) ..... . . 65 Figure 25.

- Page 8 Si 53 xx -RM Figure 42. Typical Output Circuit (Differential) ........96 Figure 43.

- Page 9 Figure 88. 10 MHz In; 1 GHz Out ..........141 Figure 89. Si5324, Si5326, and Si5328 Alarm Diagram ......143 Figure 90.

- Page 10 Table 29. Manual Input Clock Selection (Si5367, Si5368, Si5369)..... 70 Table 30. Manual Input Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5374, and Si5376) .

- Page 11 Table 62. Si5319, Si5324, Si5328 Pullup/Down ........

-

Page 12: Any-Frequency Precision Clock Product Family Overview

Si5327, and Si5369 are much lower bandwidth devices, providing a user-programmable loop bandwidth from 4 to 525 Hz. The Si5328 is an ultra-low-loop BW device that is intended for SyncE timing card applications (G.8262) with loop BW values of from 0.05 to 6 Hz. - Page 13 PLL. Silicon Laboratories offers a PC-based software utility, DSPLLsim, that can be used to determine valid frequency plans and loop bandwidth settings for the Any-Frequency Precision Clock product family. For the microprocessor- controlled devices, DSPLLsim provides the optimum PLL divider settings for a given input frequency/clock multiplication ratio combination that minimizes phase noise and power consumption.

- Page 14 Si5327 C/SPI 1PLL, 2 | 2 0.002–710 0.002–808 0.5 ps 525 Hz 36-QFN 0.05 Hz to 6x6 mm Si5328 C/SPI 1PLL, 2 | 2 0.008–346 0.002–346 0.35 ps 6 Hz 36-QFN 60 Hz to 14x14 mm Si5366 1PLL, 4 | 5 0.008–707 0.008–1050...

-

Page 15: Wideband Devices

S i5 3 x x - R M 2. Wideband Devices These are not recommended for new designs. For alternatives, see the Si533x family of products. Table 2. Product Selection Guide (Si5322/25/65/67) Low Jitter Precision Clock Multipliers (Wideband) ... -

Page 16: Any-Frequency Clock Family Members

Si 53 xx -RM 3. Any-Frequency Clock Family Members 3.1. Si5316 The Si5316 is a low jitter, precision jitter attenuator for high-speed communication systems, including OC-48, OC- 192, 10G Ethernet, and 10G Fibre Channel. The Si5316 accepts dual clock inputs in the 19, 38, 77, 155, 311, or 622 MHz frequency range and generates a jitter-attenuated clock output at the same frequency. -

Page 17: Si5319

The Si5319 input clock frequency and clock multiplication ratio are programmable through an ® I2C or SPI interface. The Si5319 is based on Silicon Laboratories' 3rd-generation DSPLL technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. -

Page 18: Si5322

Si 53 xx -RM 3.3. Si5322 The Si5322 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter attenuation. The Si5322 accepts dual clock inputs ranging from 19.44 to 707 MHz and generates two frequency- multiplied clock outputs ranging from 19.44 to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI) rates. -

Page 19: Si5323

S i5 3 x x - R M 3.4. Si5323 The Si5323 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI). The Si5323 accepts dual clock inputs ranging from 8 kHz to 707 MHz and generates two frequency-multiplied clock outputs ranging from 8 kHz to 1050 MHz. -

Page 20: Si5324

4 Hz. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5324 is ideal for providing clock multiplication and jitter attenuation in high-performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

Page 21: Si5325

150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5325 is ideal for providing clock multiplication in high performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

Page 22: Si5326

1.8, 2.5, or 3.3 V supply, the Si5326 is ideal for providing clock multiplication and jitter attenuation in high-performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. Figure 7. Si5326 Clock Multiplier and Jitter Attenuator Block Diagram... -

Page 23: Si5327

Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5327 is ideal for providing clock multiplication and jitter attenuation in high-performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

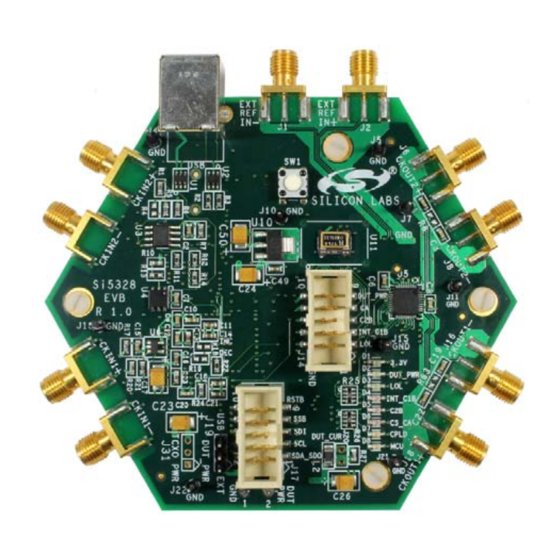

Page 24: Si5328

The Si5328 input clock frequency and clock multiplication ratio are programmable through and C or SPI interface. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5328 is ideal for providing multiplication and jitter/wander attenuation in high-performance timing applications like SyncE timing cards. See "6. -

Page 25: Si5365

S i5 3 x x - R M 3.10. Si5365 The Si5365 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter attenuation. The Si5365 accepts four clock inputs ranging from 19.44 MHz to 707 MHz and generates five frequency-multiplied clock outputs ranging from 19.44 MHz to 1050 MHz. -

Page 26: Si5366

Si 53 xx -RM 3.11. Si5366 The Si5366 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including SONET OC-48/OC-192, Ethernet, and Fibre Channel. The Si5366 accepts four clock inputs ranging from 8 kHz to 707 MHz and generates five frequency-multiplied clock outputs ranging from 8 kHz to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI) rates. -

Page 27: Si5367

150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5367 is ideal for providing clock multiplication in high performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

Page 28: Si5368

Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5368 is ideal for providing clock multiplication and jitter attenuation in high performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

Page 29: Si5369

2.5, or 3.3 V supply, the Si5369 is ideal for providing clock multiplication and jitter attenuation in high performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. -

Page 30: Si5374

The Si5374 input clock frequency and clock multiplication ratio are programmable through an I2C interface. The Si5374 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. -

Page 31: Si5375

Si5375 input clock frequency and clock multiplication ratio are programmable through an I2C interface. The Si5375 is based on Silicon Laboratories' third-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. -

Page 32: Si5376

The Si5376 input clock frequency and clock multiplication ratio are programmable through an I C interface. The Si5376 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. -

Page 33: Dspll (All Devices)

All members of the Any-Frequency Precision Clocks family incorporate a phase-locked loop (PLL) that utilizes Silicon Laboratories' third generation DSPLL technology to eliminate jitter, noise, and the need for external VCXO and loop filter components found in discrete PLL implementations. This is achieved by using a digital signal processing (DSP) algorithm to replace the loop filter commonly found in discrete PLL designs. -

Page 34: Clock Multiplication

To assist users in finding valid divider settings for a particular input frequency and clock multiplication ratio, Silicon Laboratories offers PC-based software (DSPLLsim) that calculates these settings automatically. When multiple divider combinations produce the same output frequency, the software recommends the divider settings yielding the recommended settings for phase noise performance and power consumption. -

Page 35: Pll Performance

S i5 3 x x - R M 4.2. PLL Performance All members of the Any-Frequency Precision Clock family of devices provide extremely low jitter generation, a well- controlled jitter transfer function, and high jitter tolerance. For more information the loop bandwidth and its effect on jitter attenuation, see "Appendix H—Jitter Attenuation and Loop BW"... -

Page 36: Jitter Tolerance

Si 53 xx -RM 4.2.3. Jitter Tolerance Jitter tolerance is defined as the maximum peak-to-peak sinusoidal jitter that can be present on the incoming clock before the DSPLL loses lock. The tolerance is a function of the jitter frequency, because tolerance improves for lower input jitter frequency. -

Page 37: Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)

S i5 3 x x - R M 5. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366) These parts provide high-performance clock multiplication with simple pin control. Many of the control inputs are three levels: High, Low, and Medium. High and Low are standard voltage levels determined by the supply voltage: and Ground. -

Page 38: Figure 22. Si5316 Divisor Ratios

Si 53 xx -RM The Si5316 can accept a CKIN1 input at a different frequency than the CKIN2 input. The frequency of one input clock can be 1x, 4x, or 32x the frequency of the other input clock. The output frequency is always equal to the lower of the two clock inputs and is set via the FRQSEL [1:0] pins. -

Page 39: Clock Multiplication (Si5322, Si5323, Si5365, Si5366)

S i5 3 x x - R M 5.1.2. Clock Multiplication (Si5322, Si5323, Si5365, Si5366) These parts provide flexible frequency plans for SONET, DATACOM, and interworking between the two (Table 7, Table 8, and Table 9 respectively). The CKINn inputs must be the same frequency as specified in the tables. The outputs are the same frequency;... - Page 40 Si 53 xx -RM Table 7. SONET Clock Multiplication Settings (FRQTBL=L) (Continued) FRQSEL Mult Factor Nominal All Devices Si5366 Only [3:0] (MHz) FS_OUT (MHz) CKOUT5 (CK_CONF = 1) (CK_CONF = 0) LLHM 19.44 19.44 19.44 0.008 LLHH 38.88 38.88 0.008 ...

- Page 41 S i5 3 x x - R M Table 7. SONET Clock Multiplication Settings (FRQTBL=L) (Continued) FRQSEL Mult Factor Nominal All Devices Si5366 Only [3:0] (MHz) FS_OUT (MHz) CKOUT5 (CK_CONF = 1) (CK_CONF = 0) MLLM 77.76 19.44 19.44 0.008 ...

- Page 42 Si 53 xx -RM Table 7. SONET Clock Multiplication Settings (FRQTBL=L) (Continued) FRQSEL Mult Factor Nominal All Devices Si5366 Only [3:0] (MHz) FS_OUT (MHz) CKOUT5 (CK_CONF = 1) (CK_CONF = 0) HLLL 167.33 237/255 155.52 155.52 MMHM 167.33 167.33 HLLM 4 x (237/255) 622.08...

- Page 43 S i5 3 x x - R M Table 7. SONET Clock Multiplication Settings (FRQTBL=L) (Continued) FRQSEL Mult Factor Nominal All Devices Si5366 Only [3:0] (MHz) FS_OUT (MHz) CKOUT5 (CK_CONF = 1) (CK_CONF = 0) HHLH 669.33 1/4 x 237/255 155.52 155.52 ...

- Page 44 Si 53 xx -RM Table 8. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) LLLL 15.625 31.25 LLLM 62.5 LLLH LLML LLMM 17/4 106.25 LLMH LLHL 25/4 x 66/64 161.13...

- Page 45 S i5 3 x x - R M Table 8. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) (Continued) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) MLHM 10/8 x 66/64 161.13 MLHH 10/8 x 66/64 x 255/238 172.64 MMLL 10/8 x 66/64 x 255/237...

- Page 46 Si 53 xx -RM Table 8. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) (Continued) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) HLML 173.37 4/5 x 64/66 x 237/255 HLMM 64/66 x 237/255 156.25 HLMH 237/255 161.13 HLHL 4 x 237/255 644.53...

- Page 47 S i5 3 x x - R M Table 8. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) (Continued) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) HHML 693.48 1/5 x 64/66 x 237/255 HHMM 1/4 x 64/66 x 237/255 156.25 ...

- Page 48 Si 53 xx -RM Table 9. SONET to Datacom Clock Multiplication Settings Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) LLLL 0.008 3125 LLLM 6480 51.84 LLLH 53125/8 53.125 LLML 15625/2 62.5 LLMM 53125/4 106.25 LLMH 15625 LLHL 78125/4 156.25 LLHM 159375/8 159.375 LLHH...

- Page 49 S i5 3 x x - R M Table 9. SONET to Datacom Clock Multiplication Settings (Continued) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) MLML 62.500 MLMM MLMH 74.176 91/250 MLHL 74.17582 MLHM 91 x 11/250 x 4 74.25 MLHH 74.250...

- Page 50 Si 53 xx -RM Table 9. SONET to Datacom Clock Multiplication Settings (Continued) Setting FRQSEL[3:0] (MHz) Mult Factor * (MHz) MHHM 155.520 15625/15552 156.25 MHHH 31875/31104 159.375 HLLL 15625/15552 x 66/64 161.13 HLLM 31875/31104 x 66/64 164.36 HLLH 15625/15552 x 66/ 172.64 64 x 255/238 HLML...

-

Page 51: Ckout3 And Ckout4 (Si5365 And Si5366)

Si5366, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 116. For examples of connections to the XA/XB pins, refer to "7.4. Crystal/Reference Clock Interfaces (Si5316, Si5319, Si5323, Si5324, Si5326, Si5327, Si5328, Si5366, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 102. -

Page 52: Pll Self-Calibration

Si 53 xx -RM 5.2. PLL Self-Calibration An internal self-calibration (ICAL) is performed before operation to optimize loop parameters and jitter performance. While the self-calibration is being performed, the DSPLL is being internally controlled by the self- calibration state machine, and the LOL alarm will be active for narrowband parts. Any of the following events will trigger a self-calibration: ... - Page 53 S i5 3 x x - R M Table 11. Si5316, Si5322, and Si5323 Pins and Reset Pin # Si5316 Pin Si5322 Pin Si5323 Pin Must Reset after Changing Name Name Name FRQTBL FRQTBL RATE 0 RATE 0 DBL_BY DBL2_BY DBL2_BY RATE1 RATE1...

-

Page 54: Pin Control Input Clock Control

Si 53 xx -RM 5.3. Pin Control Input Clock Control This section describes the clock selection capabilities (manual input selection, automatic input selection, hitless switching, and revertive switching). When switching between two clocks, LOL may temporarily go high if the two clocks differ in frequency by more than 100 ppm. -

Page 55: Automatic Clock Selection (Si5322, Si5323, Si5365, Si5366)

S i5 3 x x - R M 5.3.2. Automatic Clock Selection (Si5322, Si5323, Si5365, Si5366) The AUTOSEL input pin sets the input clock selection mode as shown in Table 15. Automatic switching is either revertive or non-revertive. Setting AUTOSEL to M or H, changes the CSn_CAm pins to output pins that indicate the state of the automatic clock selection (See Table 16 and Table 17). -

Page 56: Hitless Switching With Phase Build-Out (Si5323, Si5366)

CKINn that becomes valid. 5.3.3. Hitless Switching with Phase Build-Out (Si5323, Si5366) Silicon Laboratories switching technology performs “phase build-out” to minimize the propagation of phase transients to the clock outputs during input clock switching. All switching between input clocks occurs within the input multiplexor and phase detector circuitry. -

Page 57: Digital Hold/Vco Freeze

S i5 3 x x - R M 5.4. Digital Hold/VCO Freeze All Any-Frequency Precision Clock devices feature a hold over or VCO freeze mode, whereby the DSPLL is locked to a digital value. 5.4.1. Narrowband Digital Hold (Si5316, Si5323, Si5366) If an LOS or FOS condition exists on the selected input clock, the device enters digital hold. -

Page 58: Output Phase Adjust (Si5323, Si5366)

Si 53 xx -RM 5.6. Output Phase Adjust (Si5323, Si5366) Overall device skew (CKINn to CKOUT_n phase delay) is controllable via the INC and DEC input pins. A positive pulse applied at the INC pin increases the device skew by 1/f , one period of the DCO output clock. -

Page 59: Disabling Fs_Out (Si5366)

S i5 3 x x - R M 5.6.5. Disabling FS_OUT (Si5366) The FS_OUT maybe disabled via the DBLFS pin, see Table 20. The additional state (M) provided allows for FS_OUT to drive a CMOS load while the other clock outputs use a different signal format as specified by the SFOUT[1:0] pins. -

Page 60: Pll Bypass Mode

Si 53 xx -RM 5.8. PLL Bypass Mode The device supports a PLL bypass mode in which the selected input clock is fed directly to all enabled output buffers, bypassing the DSPLL. In PLL bypass mode, the input and output clocks will be at the same frequency. PLL bypass mode is useful in a laboratory environment to measure system performance with and without the effects of jitter attenuation provided by the DSPLL. -

Page 61: Fsync Align Alarm (Si5366 And Ck_Conf = 1 And Frqtbl = L)

S i5 3 x x - R M Table 23. Frequency Offset Control (FOS_CTL) FOS_CNTL Meaning FOS Disabled. Stratum 3/3E FOS Threshold (12 ppm) SONET Minimum Clock Threshold (48 ppm) 5.9.3. FSYNC Align Alarm (Si5366 and CK_CONF = 1 and FRQTBL = L) At power-up or any time after the PLL has lost lock and relocked, the device automatically performs a realignment of FS_OUT using the currently active sync input. -

Page 62: Device Reset

5.11. DSPLLsim Configuration Software To simplify frequency planning, loop bandwidth selection, and general device configuration of the Any-Frequency Precision Clocks. Silicon Laboratories offers the DSPLLsim configuration utility for this purpose. This software is available to download from www.silabs.com/timing. Rev. 1.3... -

Page 63: Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, And Si5376)

To assist users in finding valid divider settings for a particular input frequency and clock multiplication ratio, Silicon Laboratories offers the DSPLLsim utility to calculate these settings automatically. When multiple divider combinations produce the same output frequency, the software recommends the divider settings that yield the best combination of phase noise performance and power consumption. -

Page 64: Narrowband Parts (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, And Si5376)

References" on page 108 for more details. The Si5374, Si5375, and Si5376 must be used with an external crystal oscillator and cannot use crystals. Because of the wander requirements of SynE and G.8262, the Si5328 must be used with a suitable TCXO as its XAXB reference. -

Page 65: Figure 24. Narrowband Pll Divider Settings

2 kHz–2 MHz 4.85–5.67 GHz 2 kHz–1.475 GHz Note: Fmax = 346 MHz for the Si5328 and 808 MHz for the Si5327, Si5374, Si5375, and Si5376. Each entry has 500 ppm margins at both ends. The Si5374, Si5375, and Si5376 have an extend Fosc range of from 4.6 to 6 GHz. -

Page 66: Loop Bandwidth (Si5319, Si5326, Si5368, Si5375, And Si5376)

To provide the wander attenuation that is required for a SyncE G.8262-compatible timing card, the loop BW of the Si5328 can be programmed from 0.05 to 6 Hz. The loop BW values that are available are reported by DSPLLsim (Revision 4.8 or higher). -

Page 67: Initiating Internal Self-Calibration

6.2.1.1. PLL Self-Calibration (Si5324, Si5327, Si5328, Si5369, Si5374) Due to the low loop bandwidth of the Si5324, Si5327, Si5328, Si5369, and Si5374, the lock time of the Si5324/27/ 69/75 can be longer than the lock time of the Si5326. As a method of reducing the lock time, the FAST_LOCK register bit can be set to improve lock times. -

Page 68: Clock Output Behavior Before And During Ical (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, And Si5376)

Si 53 xx -RM 6.2.5. Clock Output Behavior Before and During ICAL (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) Table 28. CKOUT_ALWAYS_ON and SQ_ICAL Truth Table Cases CKOUT_ALWAYS_ON SQ_ICAL Results CKOUT OFF until after the first ICAL CKOUT OFF until after the first successful ICAL (i.e., when LOL is low) -

Page 69: Input Clock Configurations (Si5367 And Si5368)

Register values are indicated by underscored italics. Note that, when switching between two clocks, LOL may temporarily go high if the clocks differ in frequency by more than 100 ppm. Figure 25. Si5324, Si5325, Si5326, Si5327, Si5328, Si5374, and Si5376 Input Clock Selection Rev. 1.3... -

Page 70: Manual Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5367, Si5368, Si5369, Si5374, And Si5376)

Figure 26. Si5367, Si5368, and Si5369 Input Clock Selection 6.4.1. Manual Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5367, Si5368, Si5369, Si5374, and Si5376) Manual control of input clock selection is available by setting the AUTOSEL_REG[1:0] register bits to 00. In manual mode, the active input clock is chosen via the CKSEL_REG[1:0] register setting according to Table 29 and Table 30. -

Page 71: Automatic Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5367, Si5368, Si5369, Si5374, And Si5376)

S i5 3 x x - R M Table 30. Manual Input Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5374, and Si5376) CKSEL_REG or CS pin Active Input Clock CKIN1 CKIN2 If the selected clock enters an alarm condition, the PLL enters digital hold mode. The CKSEL_REG[1:0] controls are ignored if automatic clock selection is enabled. -

Page 72: Hitless Switching With Phase Build-Out (Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, And Si5376)

In non-revertive mode, once CKIN2 is selected, CKIN2 selection remains as long as it is valid even if alarms are cleared on CKIN1. 6.4.3. Hitless Switching with Phase Build-Out (Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, and Si5376) Silicon Laboratories switching technology performs phase build-out, which maintains the phase of the output when the input clock is switched. -

Page 73: Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, And Si5376 Free Run Mode

S i5 3 x x - R M 6.5. Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376 Free Run Mode Figure 27. Free Run Mode Block Diagram CKIN2 has an extra mux with a path to the crystal oscillator output. -

Page 74: Free Run Reference Frequency Constraints

Si 53 xx -RM 6.5.3. Free Run Reference Frequency Constraints XA/XB Frequency Min XA/XB Frequency Max Xtal 109 MHz 125.5 MHz 3rd overtone 37 MHz 41 MHz Fundamental CKIN XA-XB -------------- - ----------------- - CKOUT --------------------- - Integer XA-XB ... -

Page 75: Digital Hold

(LOS1_INT OR FOS1_INT) AND (LOS2_INT OR FOS2_INT) AND (LOS3_INT OR FOS3_INT) AND (LOS4_INT OR FOS4_INT) = enter digital hold 6.6.1.1. Digital Hold Detailed Description (Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, and Si5376) In this mode, the device provides a stable output frequency until the input clock returns and is validated. Upon entering digital hold, the internal DCO is initially held to its last frequency value, M (See Figure 28). - Page 76 Si 53 xx -RM Table 33. Digital Hold History Delay HIST_DEL[4:0] History Delay Time (ms) HIST_DEL[4:0] History Delay Time (ms) 00000 0.0001 10000 6.55 00001 0.0002 10001 00010 0.0004 10010 (default) 00011 0.0008 10011 00100 0.0016 10100 00101 0.0032 10101 00110 0.0064 10110...

-

Page 77: History Settings For Low Bandwidth Devices (Si5324, Si5327, Si5328, Si5369, Si5374)

Because of the extraordinarily low loop bandwidth of the Si5324, Si5369 and Si5374, it is recommended that the values for both history registers be increased for longer histories. 6.6.3. Recovery from Digital Hold (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, and Si5376) When the input clock signal returns, the device transitions from digital hold to the selected input clock. -

Page 78: Output Phase Adjust (Si5326, Si5368)

Si 53 xx -RM 6.7. Output Phase Adjust (Si5326, Si5368) The device has a highly accurate, digitally controlled device skew capability. For more information on Output Phase Adjustments, see both DSPLLsim and the respective data sheets. Both can be downloaded by going to www.silabs.com/timing and clicking on “Documentation”... -

Page 79: Independent Skew (Si5324, Si5326, Si5328, Si5368, Si5369, Si5374, And Si5376)

Because of its very low loop bandwidth, the output phase of the Si5324, Si5327, Si5328, Si5369, and Si5374 are not adjustable. This means that the Si5324, Si5327, Si5328, Si5369, and Si5374 do not have any INC or DEC pins and that they do not have CLAT or FLAT registers. -

Page 80: Figure 30. Frame Sync Frequencies

Si 53 xx -RM Table 35. CKIN3/CKIN4 Frequency Selection (CK_CONF = 1) CKLNnRATE[2:0] CKINn Frequency (kHz) Divisor 2–4 4–8 8–16 16–32 32–64 64–128 128–256 256–512 Figure 30. Frame Sync Frequencies Rev. 1.3... -

Page 81: Fsync Realignment (Si5368)

S i5 3 x x - R M The NC5_LS divider uses CKOUT2 as its clock input to derive FS_OUT. The limits for the NC5_LS divider are NC5_LS = [1, 2, 4, 6, …, 2 < 710 MHz CKOUT2 Note that when in frame synchronization realignment mode, writes to NC5_LS are controlled by FPW_VALID. See section “6.8.4. -

Page 82: Fsync Skew Control (Si5368)

Section “6.11. Alarms (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)”; however, in frame sync mode (CK_CONFIG_REG = 1), the FOS alarms for CKIN3 and CKIN4 are ignored. -

Page 83: Output Clock Drivers (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, Si5376)

S i5 3 x x - R M 6.9. Output Clock Drivers (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, Si5376) The device includes a flexible output driver structure that can drive a variety of loads, including LVPECL, LVDS, CML, and CMOS formats. -

Page 84: Pll Bypass Mode (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, And Si5376)

Si 53 xx -RM 6.10. PLL Bypass Mode (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) The device supports a PLL bypass mode in which the selected input clock is fed directly to the output buffers, bypassing the DSPLL. -

Page 85: Fos Algorithm (Si5324, Si5325, Si5326, Si5328, Si5368, Si5369, Si5374, And Si5376)

S i5 3 x x - R M 6.11.1.2. Standard LOS (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) To facilitate automatic hitless switching, the LOS trigger time can be significantly reduced by using the default LOS option (LOSn_EN = 11). -

Page 86: Figure 31. Fos Compare

Si 53 xx -RM FOS reference. When the XA/XB input is used as the FOS reference, there is only one reference frequency band that is allowed: from 37 MHz to 41 MHz. Table 41. FOS Reference Clock Selection FOS Reference FOSREFSEL[2:0] Si5326 Si5368... -

Page 87: C1B, C2B (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5374, Si5375, And Si5376)

CLK2RATE = 1 FOSREFSEL[2:0] = 010 6.11.3. C1B, C2B (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5374, Si5375, and Si5376) A LOS condition causes the associated LOS1_INT or LOS2_INT read only register bit to be set. A LOS condition on CKIN_1 will also be reflected onto C1B if CK1_BAD_PIN = 1. Likewise, a LOS condition on CKIN_2 will also be reflected onto C2B if CK2_BAD_PIN = 1. -

Page 88: C1B, C2B, C3B, Alrmout (Si5368 [Ck_Config_Reg = 1])

Si 53 xx -RM Table 43. Alarm Output Logic Equations (Si5367, Si5368, and Si5369 [CONFIG_REG = 0]) FOS_EN Alarm Output Equations C1B = LOS1_INT (Disables FOS) C2B = LOS2_INT C3B = LOS3_INT ALRMOUT = LOS4_INT C1B = LOS1_INT or FOS1_INT C2B = LOS2_INT or FOS2_INT C3B = LOS3_INT or FOS3_INT ALRMOUT = LOS4_INT or FOS4_INT... -

Page 89: Los Algorithm For Reference Clock Input (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, And Si5376)

S i5 3 x x - R M 6.11.7. LOS Algorithm for Reference Clock Input (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) The reference clock input on the XA/XB port is monitored for LOS. The LOS circuitry divides the signal at XA/XB by 128, producing a 78 kHz to 1.2 MHz signal, and monitors the signal for LOS using the same algorithm as described... -

Page 90: I 2 C Serial Microprocessor Interface

Si 53 xx -RM 6.13. I C Serial Microprocessor Interface When configured in I C control mode (CMODE = L), the control interface to the device is a 2-wire bus for bidirectional communication. The bus consists of a bidirectional serial data line (SDA) and a serial clock input (SCL). -

Page 91: Serial Microprocessor Interface (Spi)

S i5 3 x x - R M 6.14. Serial Microprocessor Interface (SPI) When configured in SPI control mode (CMODE = H), the control interface to the device is a 4-wire interface modeled after commonly available microcontroller and serial peripheral devices. The interface consists of a clock input (SCLK), slave select input (SSb), serial data input (SDI), and serial data output (SDO). -

Page 92: Figure 34. Spi Write/Set Address Command

Si 53 xx -RM Figure 34. SPI Write/Set Address Command Figure 35. SPI Read Command Figure 35 shows the SPI timing diagram. See the applicable data sheets for these timing parameters. Rev. 1.3... -

Page 93: Default Device Configuration

Precision Clocks. Silicon Laboratories has a configuration utility - DSPLLsim for the Si5319, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368 and Si5369. For the Si5374, Si5375, and Si5376, there is a different configuration utility - Si537xDSPLLsim. Both are available to download from www.silabs.com/timing. -

Page 94: High-Speed I/O

Si 53 xx -RM 7. High-Speed I/O 7.1. Input Clock Buffers Any-Frequency Precision Clock devices provide differential inputs for the CKINn clock inputs. These inputs are internally biased to a common mode voltage and can be driven by either a single-ended or differential source. Figure 37 through Figure 41 show typical interface circuits for LVPECL, CML, LVDS, or CMOS input clocks. -

Page 95: Figure 39. Cml/Lvds Termination (1.8, 2.5, 3.3 V)

S i5 3 x x - R M Figure 39. CML/LVDS Termination (1.8, 2.5, 3.3 V) Figure 40. Center Tap Bypassed Termination Figure 40 is recommended over a single 100 resistor whenever greater reduction of common-mode noise is desired. It can be used with any differential termination, either input or output. Figure 41. -

Page 96: Output Clock Drivers

“disable” to SFOUTn to disable the output buffer and reduce power. When the output mode is CMOS, bypass mode is not supported. Table 47. Output Driver Configuration Output Mode SFOUTn Pin Settings SFOUTn_REG [2:0] Settings (Si5316, Si5322, Si5323, Si5365) (Si5319, Si5325, SI5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) LVDS LVPECL Low-swing LVDS CMOS Disabled... -

Page 97: Figure 43. Differential Output Example Requiring Attenuation

The pin-controlled parts have a DBL2_BY pin that can be used to disable CKOUT2. Table 48. Disabling Unused Output Driver Output Driver Si5365, Si5366 Si5325, Si5326, Si5327, Si5328, Si5367, Si5368 CKOUT1 and CKOUT2 Use SFOUT_REG to disable individ- ual CKOUTn. -

Page 98: Typical Clock Output Scope Shots

Si 53 xx -RM Figure 45. Differential CKOUT Structure (not for CMOS) 7.2.3. Typical Clock Output Scope Shots Table 49. Output Format Measurements Name SFOUT Pin SFOUT Code Single Diff Vocm Vpk–pk Vpk–pk Reserved — — — — LVDS 3.05 LVPECL 2.10 Reserved... -

Page 99: Typical Scope Shots For Sfout Options

S i5 3 x x - R M 7.3. Typical Scope Shots for SFOUT Options Figure 46. sfout_2, CMOS Figure 47. sfout_3, lowSwingLVDS Rev. 1.3... - Page 100 Si 53 xx -RM Figure 48. sfout_5, LVPECL Figure 49. sfout_6, CML Rev. 1.3...

- Page 101 S i5 3 x x - R M Figure 50. sfout_7, LVDS Rev. 1.3...

-

Page 102: Crystal/Reference Clock Interfaces (Si5316, Si5319, Si5323, Si5324, Si5326, Si5327, Si5328, Si5366, Si5368, Si5369, Si5374, Si5375, And Si5376)

Si5328, Si5366, Si5368, Si5369, Si5374, Si5375, and Si5376) All devices other than the Si5328, Si5374, Si5375, and Si5376 can use an external crystal or external clock as a reference. The Si5374, Si5375, and Si5376 are limited to an external reference oscillator and cannot use a crystal. -

Page 103: Figure 53. Differential External Reference Input Example

S i5 3 x x - R M Figure 53. Differential External Reference Input Example (Not for Si5374, Si5375, or Si5376) Figure 54. Differential OSC Reference Input Example for Si5374, Si5375 and Si5376 Rev. 1.3... -

Page 104: Three-Level (3L) Input Pins (No External Resistors)

Si 53 xx -RM 7.5. Three-Level (3L) Input Pins (No External Resistors) Figure 55. Three Level Input Pins Parameter Symbol Input Voltage Low Vill — .15 x V Input Voltage Mid Vimm .45 x Vdd .55 x V Input Voltage High Vihh .85 x Vdd —... -

Page 105: Three-Level (3L) Input Pins (With External Resistors)

S i5 3 x x - R M 7.6. Three-Level (3L) Input Pins (With External Resistors) Figure 56. Three Level Input Pins Parameter Symbol –30 μA Input Low Current Iill — –11 μA –11 μA Input Mid Current Iimm –30 μA Input High Current Iihh —... -

Page 106: Power Supply

Si 53 xx -RM 8. Power Supply These devices incorporate an on-chip voltage regulator to power the device from supply voltages of 1.8, 2.5, or 3.3 V. Internal core circuitry is driven from the output of this regulator while I/O circuitry uses the external supply voltage directly. -

Page 107: Packages And Ordering Guide

S i5 3 x x - R M 9. Packages and Ordering Guide Refer to the respective data sheet for your device packaging and ordering information. Rev. 1.3... -

Page 108: Appendix A-Narrowband References

Si 53 xx -RM A—N PPENDIX ARROWBAND EFERENCES To provide jitter attenuation, all Si53xx any-frequency jitter attenuating clocks require an external reference. In most cases, this function can be provided by a low cost crystal. The Si5316, Si5317, Si5319, Si5323, Si5324, Si5326, Si5366, Si5368 and Si5369 support two crystal options. -

Page 109: Figure 59. Typical Reference Jitter Transfer Function

S i5 3 x x - R M Reference Drift and Wander During Digital Hold or VCO Freeze, the stability of the device output clocks is identical to the drift of the reference frequency. Any long-term or temperature-related drift of the reference input will result in a similar drift in the Si53xx output frequency. -

Page 110: Figure 60. Si5317 At 622.08 Mhz With A 40 Mhz Crystal

Si 53 xx -RM Other Design Considerations The absolute accuracy of the crystal does not impact the accuracy or jitter performance of the device output clocks when operating in jitter attenuation mode. Crystal accuracy is only a factor in Digital Hold and VCO Freeze applications. -

Page 111: Figure 61. Si53Xx At 622.08 Mhz With A 114.285 Mhz Crystal

S i5 3 x x - R M Figure 61. Si53xx at 622.08 MHz with a 114.285 MHz Crystal Jitter Band Jitter, RMS SONET_OC48, 12 kHz to 20 MHz 242 fs SONET_OC192_A, 20 kHz to 80 MHz 269 fs SONET_OC192_B, 4 to 80 MHz 166 fs SONET_OC192_C, 50 kHz to 80 MHz 265 fs... -

Page 112: Appendix B-Frequency Plans And Typical Jitter Performance (Si5316, Si5319, Si5323, Si5324, Si5326, Si5327, Si5366, Si5368, Si5369, Si5374, Si5375, And Si5376)

Si 53 xx -RM The Si53xx devices support options for a 114.285 MHz 3rd overtone crystal as well as a 114.285 MHz fundamental mode crystal. The figure below highlights the difference in Si5324 phase noise performance when either the fundamental mode crystal (lighter trace) or 3rd overtone crystal (darker trace) is used. The 3rd overtone crystal provides lower phase noise between 60 Hz and 2 kHz offset, however the 12 kHz to 20 MHz band is virtually identical. -

Page 113: Figure 63. 200 Mhz Output With A 40 Mhz Crystal Showing Mid-Band Spurs

S i5 3 x x - R M Figure 63. 200 MHz Output with a 40 MHz Crystal Showing Mid-Band Spurs and High Jitter Jitter Band Jitter, RMS SONET_OC48, 12 kHz to 20 MHz 987 fs SONET_OC192_A, 20 kHz to 80 MHz 980 fs SONET_OC192_B, 4 to 80 MHz 189 fs... -

Page 114: Figure 64. 200 Mhz Output With A 38.095 Mhz Crystal

Si 53 xx -RM Figure 64. 200 MHz Output with a 38.095 MHz Crystal Jitter Band Jitter, RMS SONET_OC48, 12 kHz to 20 MHz 448 fs SONET_OC192_A, 20 kHz to 80 MHz 453 fs SONET_OC192_B, 4 to 80 MHz 188 fs SONET_OC192_C, 50 kHz to 80 MHz 437 fs Brick Wall_800 Hz to 80 MHz... - Page 115 To use the Si5328 or another Si53xx device as a SyncE PLL with a 0.1 Hz or 1-10 Hz loop bandwidth, a TCXO or other high stability oscillator must be used. For details, see the Si5328 data sheet, "AN775: Si5327 / ITU-T G.8262Y.1362 EEC Options 1 and 2 Compliance Test Report"...

-

Page 116: Figure 65. Phase Noise Vs. F3

Si 53 xx -RM B—F (Si5316, Si5319, PPENDIX REQUENCY LANS AND YPICAL ITTER ERFORMANCE Si5323, Si5324, Si5326, Si5327, Si5366, Si5368, Si5369, Si5374, Si5375, Si5376) Introduction To achieve the best jitter performance from Narrowband Any-Frequency Clock devices, a few general guidelines should be observed: High f3 Value f3 is defined as the comparison frequency at the Phase Detector. -

Page 117: Figure 66. Jitter Integrated From 12 Khz To 20 Mhz Jitter, Fs Rms

S i5 3 x x - R M Jitter vs. f3 Jitter integrated from 12 kHz to 20 MHz jitter, fs RMS Figure 66. Jitter Integrated from 12 kHz to 20 MHz Jitter, fs RMS Rev. 1.3... -

Page 118: Figure 67. Jitter Integrated From 100 Hz To 40 Mhz Jitter, Fs Rms

Si 53 xx -RM Wideband Jitter vs. f3 Jitter integrated from 100 Hz to 40 MHz jitter, fs RMS 60000 50000 40000 30000 20000 10000 1000 10000 f3 frequency, kHz Figure 67. Jitter Integrated from 100 Hz to 40 MHz Jitter, fs RMS 1,2,3 Table 51. -

Page 119: Appendix C-Typical Phase Noise Plots

S i5 3 x x - R M Figure 68 shows similar results and ties them to RMS jitter values. It also helps to illustrate one potential remedy for solutions with low f3. Note that 38.88 MHz x 5 = 194.4 MHz. In this case, an FPGA was used to multiply a 38.88 MHz input clock up by a factor of five to 194.4 MHz, using a feature such as the Xilinx DCM (Digital Clock Manager). -

Page 120: Figure 69. Reference Vs. Output Frequency

Si 53 xx -RM Reference vs. Output Frequency Because of internal coupling, output frequencies that are an integer multiple (or close to an integer multiple) of the XA/XB reference frequency (either internal or external) should be avoided. Figure 69 illustrates this by showing a 38.88 MHz reference being used to generate both a 622.08 MHz output (which is an integer multiple of 38.88 MHz) and 696.399 MHz (which is not an integer multiple of 38.88 MHz). -

Page 121: Figure 70. 622.08 Mhz Output With A 114.285 Mhz Crystal

S i5 3 x x - R M High Reference Frequency When selecting a reference frequency, with all other things being equal, the higher the reference frequency, the lower the output jitter. Figures 70 and 71 compare the results with a 114.285 MHz crystal versus a 40 MHz crystal. Figure 70. -

Page 122: Figure 71. 622.08 Mhz Output With A 40 Mhz Crystal

Si 53 xx -RM Figure 71. 622.08 MHz Output with a 40 MHz Crystal Jitter Band Jitter, RMS SONET_OC48, 12 kHz to 20 MHz 379 fs SONET_OC192_A, 20 kHz to 80 MHz 376 fs SONET_OC192_B, 4 to 80 MHz 132 fs SONET_OC192_C, 50 kHz to 80 MHz 359 fs Brick Wall_800 Hz to 80 MHz... -

Page 123: Figure 72. 155.52 Mhz In; 622.08 Mhz Out

S i5 3 x x - R M C—T PPENDIX YPICAL HASE OISE LOTS Introduction The following are some typical phase noise plots. The clock input source is a Rohde and Schwarz model SML03 RF Generator. Except as noted, the phase noise analysis equipment is the Agilent E5052B. Also (except as noted), the Any-Frequency part was an Si5326 operating at 3.3 V with an ac-coupled differential PECL output and an ac- coupled differential sine wave input from the RF generator at 0 dBm. -

Page 124: Figure 73. 155.52 Mhz In; 622.08 Mhz Out; Loop Bw = 7 Hz, Si5324

Si 53 xx -RM Figure 73. 155.52 MHz In; 622.08 MHz Out; Loop BW = 7 Hz, Si5324 Rev. 1.3... -

Page 125: Figure 74. 19.44 Mhz In; 156.25 Mhz Out; Loop Bw = 80 Hz

S i5 3 x x - R M Figure 74. 19.44 MHz In; 156.25 MHz Out; Loop BW = 80 Hz Rev. 1.3... -

Page 126: Figure 75. 19.44 Mhz In; 156.25 Mhz Out; Loop Bw = 5 Hz, Si5324

Si 53 xx -RM Figure 75. 19.44 MHz In; 156.25 MHz Out; Loop BW = 5 Hz, Si5324 Rev. 1.3... -

Page 127: Figure 76. 27 Mhz In; 148.35 Mhz Out; Light Trace Bw = 6 Hz; Dark Trace Bw = 110 Hz

S i5 3 x x - R M Figure 76. 27 MHz In; 148.35 MHz Out; Light Trace BW = 6 Hz; Dark Trace BW = 110 Hz, Si5324 Rev. 1.3... -

Page 128: Figure 77. 61.44 Mhz In; 491.52 Mhz Out; Loop Bw = 7 Hz, Si5324

Si 53 xx -RM Figure 77. 61.44 MHz In; 491.52 MHz Out; Loop BW = 7 Hz, Si5324 Rev. 1.3... -

Page 129: Figure 78. 622.08 Mhz In; 672.16 Mhz Out; Loop Bw = 6.9 Khz

S i5 3 x x - R M Figure 78. 622.08 MHz In; 672.16 MHz Out; Loop BW = 6.9 kHz Rev. 1.3... -

Page 130: Figure 79. 622.08 Mhz In; 672.16 Mhz Out; Loop Bw = 100 Hz

Si 53 xx -RM Figure 79. 622.08 MHz In; 672.16 MHz Out; Loop BW = 100 Hz Rev. 1.3... -

Page 131: Figure 80. 156.25 Mhz In; 155.52 Mhz Out

S i5 3 x x - R M Figure 80. 156.25 MHz In; 155.52 MHz Out Rev. 1.3... -

Page 132: Figure 81. 78.125 Mhz In; 644.531 Mhz Out

Si 53 xx -RM Figure 81. 78.125 MHz In; 644.531 MHz Out Table 54. Jitter Values for Figure 74 Jitter Bandwidth 644.531 MHz Jitter (RMS) Broadband, 1 kHz to 10 MHz 223 fs OC-48, 12 kHz to 20 MHz 246 fs OC-192, 20 kHz to 80 MHz 244 fs OC-192, 4 MHz to 80 MHz... -

Page 133: Figure 82. 78.125 Mhz In; 690.569 Mhz Out

S i5 3 x x - R M Figure 82. 78.125 MHz In; 690.569 MHz Out Table 55. Jitter Values for Figure 75 Jitter Bandwidth 690.569 MHz Jitter (RMS) Broadband, 1 kHz to 10 MHz 244 fs OC-48, 12 kHz to 20 MHz 260 fs OC-192, 20 kHz to 80 MHz 261 fs... -

Page 134: Figure 83. 78.125 Mhz In; 693.493 Mhz Out

Si 53 xx -RM Figure 83. 78.125 MHz In; 693.493 MHz Out Table 56. Jitter Values for Figure 76 Jitter Bandwidth 693.493 MHz Jitter (RMS) Broadband, 1 kHz to 10 MHz 243 fs OC-48, 12 kHz to 20 MHz 265 fs OC-192, 20 kHz to 80 MHz 264 fs OC-192, 4 MHz to 80 MHz... -

Page 135: Figure 84. 86.685 Mhz In; 173.371 Mhz And 693.493 Mhz Out

S i5 3 x x - R M 86.685 MHz in, 173.371 MHz and 693.493 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 -1.80E+02 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Red = 693.493 MHz Blue = 173.371 MHz Figure 84. -

Page 136: Figure 85. 86.685 Mhz In; 173.371 Mhz Out

Si 53 xx -RM Figure 85. 86.685 MHz In; 173.371 MHz Out Rev. 1.3... -

Page 137: Appendix D-Alarm Structure

S i5 3 x x - R M Figure 86. 86.685 MHz In; 693.493 MHz Out Rev. 1.3... -

Page 138: Figure 87. 155.52 Mhz And 156.25 Mhz In; 622.08 Mhz Out

Si 53 xx -RM 155.52 MHz and 156.25MHz in, 622.08 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 6.00E 01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Blue = 155.52 MHz Red = 156.25 MHz Blue = 155.52 MHz input Red = 156.25 MHz input Figure 87. -

Page 139: Figure 88. 10 Mhz In; 1 Ghz Out

S i5 3 x x - R M Figure 88. 10 MHz In; 1 GHz Out Rev. 1.3... -

Page 140: Appendix E-Internal Pullup, Pulldown By Pin

Si 53 xx -RM Digital Video (HD-SDI) Jitter Band Jitter Brick Wall, 10 Hz to 20 MHz 2.42 ps, RMS Peak-to-peak 14.0 ps Phase noise equipment: Agilent model JS500. Rev. 1.3... -

Page 141: Figure 89. Si5324, Si5326, And Si5328 Alarm Diagram

S i5 3 x x - R M D—A PPENDIX LARM TRUCTURE Figure 89. Si5324, Si5326, and Si5328 Alarm Diagram Rev. 1.3... -

Page 142: Figure 90. Si5368 And Si5369 Alarm Diagram (1 Of 2)

Si 53 xx -RM Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky Write 0 to clear Sticky... -

Page 143: Figure 91. Si5368 And Si5369 Alarm Diagram (2 Of 2)

S i5 3 x x - R M Figure 91. Si5368 and Si5369 Alarm Diagram (2 of 2) Rev. 1.3... - Page 144 Si 53 xx -RM E—I PPENDIX NTERNAL ULLUP ULLDOWN BY Tables 59–70 show which 2-Level CMOS pins have pullups or pulldowns. Note the value of the pullup/pulldown resistor is typically 75 k. Table 59. Si5316 Pullup/Down Pin # Si5316 Pull? RATE0 U, D DBL2_BY...

- Page 145 FRQSEL0 U, D FRQSEL1 U, D FRQSEL2 U, D FRQSEL3 U, D SFOUT1 U, D SFOUT0 U, D Table 62. Si5319, Si5324, Si5328 Pullup/Down Pin # Si5326 Pull? RATE0 U, D RATE1 U, D CS_CA U, D A2_SS CMODE U, D...

- Page 146 Si 53 xx -RM Table 63. Si5325 Pullup/Down Pin # Si5325 Pull? CS_CA U, D A2_SS CMODE U, D Table 64. Si5326 Pullup/Down Pin # Si5326 Pull? RATE0 U, D RATE1 U, D CS_CA U, D A2_SS CMODE U, D Rev.

- Page 147 S i5 3 x x - R M Table 65. Si5327 Pullup/Down Table 67. Si5366 Pullup/Down Pin # Si5327 Pull? Pin # Si5366 Pull? RATE U, D FRQTBL U, D CKSEL U, D CS0_C3A FS_SW FS_ALIGN AUTOSEL U, D A2_SS RATE0 U, D DBL2_BY...

- Page 148 Si 53 xx -RM Table 68. Si5367 Pullup/Down Pin # Si5367 Pull? CS0_C3A CS1_C4A U, D A2_SSB CMODE U, D Table 69. Si5368 Pullup/Down Pin # Si5368 Pull? CS0_C3A FS_ALIGN RATE0 U, D RATE1 U, D CS1_C4A U, D A2_SSB CMODE U, D Rev.

- Page 149 S i5 3 x x - R M Table 70. Si5369 Pullup/Down Pin # Si5368 Pull? CS0_C3A FS_ALIGN RATE0 U, D RATE1 U, D CS1_C4A U, D A2_SSB CMODE U, D Table 71. Si5374/75/76 Pullup/Down Pin # Si5374/75/76 Pull? RSTL_A RSTL_B RSTL_C RSTL_D...

-

Page 150: Appendix F-Typical Performance: Bypass Mode, Psrr

Si 53 xx -RM F—T PSRR, PPENDIX YPICAL ERFORMANCE YPASS ROSSTALK UTPUT ORMAT ITTER This appendix is divided into the following four sections: Bypass Mode Performance Power Supply Noise Rejection Crosstalk Output Format Jitter Bypass: 622.08 MHz In, 622.08 MHz Out Dark blue —... - Page 151 S i5 3 x x - R M Power Supply Noise Rejection 38.88 MHz in, 155.52 MHz out; Bandwidth = 110 Hz Rev. 1.3...

- Page 152 Si 53 xx -RM Clock Input Crosstalk Results: Test Conditions Jitter Band 155.52 MHz in, 155.521 MHz in, 155.521 MHz in, 155.521 MHz in, 155.521 MHz in, 622 MHz out, 622.084 MHz 622.084 MHz 622.084 MHz 622.084 MHz For reference, out, out, out,...

- Page 153 S i5 3 x x - R M Clock Input Crosstalk: Phase Noise Plots Dark blue — No crosstalk Light blue — With crosstalk, low bandwidth Yellow — With crosstalk, high bandwidth Red — With crosstalk, in digital hold Rev. 1.3...

- Page 154 Si 53 xx -RM Clock Input Crosstalk: Detail View Dark blue — No crosstalk Light blue — With crosstalk, low bandwidth Yellow — With crosstalk, high bandwidth Red — With crosstalk, in digital hold Rev. 1.3...

- Page 155 S i5 3 x x - R M Clock Input Crosstalk: Wideband Comparison Dark blue — Bandwidth = 6.72 kHz; no Xtalk Light blue — Bandwidth = 6.72 kHz; with Xtalk Jitter Band Jitter, w/ Xtlk Jitter, no Xtlk OC-48, 12 kHz to 20 MHz 303 fs RMS 422 fs RMS OC-192, 20 kHz to 80 MHz...

- Page 156 Si 53 xx -RM Clock Input Crosstalk: Output of Rohde and Schwartz RF Rev. 1.3...

- Page 157 S i5 3 x x - R M Jitter vs. Output Format: 19.44 MHz In, 622.08 MHz Out Spectrum Analyzer: Agilent Model E444OA Table 72. Output Format vs. Jitter Bandwidth LVPECL Jitter LVDS Jitter CML Jitter (RMS) Low Swing LVDS (RMS) (RMS) Jitter (RMS)

-

Page 158: Appendix G-Near Integer Ratios

Si 53 xx -RM G—N PPENDIX NTEGER ATIOS To provide more details and to provide boundaries with respect to the “Reference vs. Output Frequency” issue described in Appendix B on page 116, the following study was performed and is presented below. Test Conditions ... -

Page 159: Figure 93. ±200 Ppm, 10 Ppm Steps

S i5 3 x x - R M 38.88 MHz External XA-XB Reference 1200 1000 155.49 155.5 155.51 155.52 155.53 155.54 155.55 Input Frequency (MHz) Input Frequency Variation = ±200 ppm Figure 93. ±200 ppm, 10 ppm Steps 38.88 MHz External XA-XB Reference 1200 1000 155.2 155.3 155.3 155.4 155.4 155.5 155.5 155.6 155.6 155.7 155.7 155.8 155.8 155.9 155.9... -

Page 160: Appendix H-Jitter Attenuation And Loop Bw

Si 53 xx -RM H—J PPENDIX ITTER TTENUATION AND The following illustrates the effects of different loop BW values on the jitter attenuation of the Any-Frequency devices. The jitter consists of sine wave modulation at varying frequencies. The RMS jitter values of the modulated sine wave input is compared to the output jitter of an Si5326 and an Si5324. -

Page 161: Figure 95. Rf Generator, Si5326, Si5324; No Jitter (For Reference)

S i5 3 x x - R M 622.08 MHz in, 622.08 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 -1.80E+02 1.00E+01 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Blue = RF Generator Green = Si5326 Red = Si5324 Figure 95. -

Page 162: Figure 97. Rf Generator, Si5326, Si5324 (100 Hz Jitter)

Si 53 xx -RM 622.08 MHz in, 622.08 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 -1.80E+02 1.00E+01 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Blue = RF Generator Green = Si5326 Red = Si5324 Figure 97. -

Page 163: Figure 99. Rf Generator, Si5326, Si5324 (1 Khz Jitter)

S i5 3 x x - R M 622.08 MHz in, 622.08 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 -1.80E+02 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Blue = RF Generator Green = Si5326 Red = Si5324 Figure 99. -

Page 164: Figure 101. Rf Generator, Si5326, Si5324 (10 Khz Jitter)

Si 53 xx -RM 622.08 MHz in, 622.08 MHz out 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 -8.00E+01 -1.00E+02 -1.20E+02 -1.40E+02 -1.60E+02 -1.80E+02 1.00E+02 1.00E+03 1.00E+04 1.00E+05 1.00E+06 1.00E+07 1.00E+08 Offset Frequency (Hz) Blue = RF Generator Green = Si5326 Red = Si5324 Figure 101. -

Page 165: Appendix I-Response To A Frequency Step Function

S i5 3 x x - R M I—R PPENDIX ESPONSE TO A REQUENCY UNCTION When an input clock is switched between two clocks that differ in frequency, the PLL will adjust to the new clock frequency at a rate that depends on the PLL's loop bandwidth value. This process is the same if a single clock input abruptly changes frequency. -

Page 166: Appendix J-Si5374, Si5375, Si5376 Pcb Layout Recommendations

Si 53 xx -RM J—Si5374, Si5375, Si5376 PCB L PPENDIX AYOUT ECOMMENDATIONS The following is a set of recommendations and guidelines for printed circuit board layout with the Si5374, Si5375, and Si5376 devices. Because the four DSPLLs are in close physical and electrical proximity to one another, PCB layout is critical to achieving the highest levels of jitter performance. -

Page 167: Figure 104. Ground Plane And Reset

S i5 3 x x - R M Figure 104. Ground Plane and Reset RSTL_x Pins It is highly recommended that the four RSTL_x pins (RSTL_A, RSTL_B, RSTL_C and RSTL_D) be logically connected to one another so that the four DSPLLs are always either all in reset or are all out of reset. While in reset, the DSPLLs VCO will continue to run, and, because the VCOs will not be locked to any signal, they will drift and can be any frequency value within the VCO range. -

Page 168: Figure 105. Output Clock Routing

Si 53 xx -RM The following is a set of recommendations and guidelines for printed circuit board layout with the Si5374, Si5375, and Si5376 devices. Because the four DSPLLs are in close physical and electrical proximity to one another, PCB layout is critical to achieving the highest levels of jitter performance. - Page 169 S i5 3 x x - R M Figure 106. OSC_P, OSC_N Routing Rev. 1.3...

-

Page 170: Appendix K-Si5374, Si5375, And Si5376 Crosstalk

Si 53 xx -RM K—Si5374, Si5375, Si5376 C PPENDIX ROSSTALK While the four DSPLLs of the Si5374, Si5375, and Si5376 are in close physical and electrical proximity to one another, crosstalk interference between the DSPLLs is minimal. The following measurements show typical performance levels that can be expected for the Si5374, Si5375, and Si5376 when all four of their DSPLLs are operating at frequencies that are close in value to one another, but not exactly the same. -

Page 171: Figure 107. Si5374, Si5375, And Si5376 Dspll A

S i5 3 x x - R M Figure 107. Si5374, Si5375, and Si5376 DSPLL A Rev. 1.3... -

Page 172: Figure 108. Si5374, Si5375, And Si5376 Dspll B

Si 53 xx -RM Figure 108. Si5374, Si5375, and Si5376 DSPLL B Rev. 1.3... -

Page 173: Figure 109. Si5374, Si5375, And Si5376 Dspll C

S i5 3 x x - R M Figure 109. Si5374, Si5375, and Si5376 DSPLL C Rev. 1.3... -

Page 174: Figure 110. Si5374, Si5375, And Si5376 Dspll D

Si 53 xx -RM Figure 110. Si5374, Si5375, and Si5376 DSPLL D Because they contain four different and independent DSPLLs, the Si5374, Si5375, and Si5376 are supported by a different software called Si537xDSLLsim. Noting that applications may be plesiochronous, the VCOs of the DSPLLs can be very close in frequency to one another, which results in crosstalk susceptibility. -

Page 175: Figure 111. Example Frequency Plan Sources

S i5 3 x x - R M Si5374/75/76 Register Map Partition Example In a typical line card application, an Si5374/75/76 will supply four clocks to four different channels that might need to support any combination of services. For example, say that each of the four DSPLLs (A, B, C or D) can be programmed for either a SONET, OTN/OTU or Ethernet frequency plan in any combination. -

Page 176: Figure 112. Run Time Frequency Plan Examples

Si 53 xx -RM Figure 112. Run Time Frequency Plan Examples Rev. 1.3... -

Page 177: Appendix L-Jitter Transfer And Peaking

S i5 3 x x - R M L—J PPENDIX ITTER RANSFER AND EAKING The follow set of curves show the jitter transfer versus frequency with a loop bandwidth value of 60 Hz. The clock input and output frequencies were both 10.24 MHz. The four curves all use the same data but are graphed at different scales to illustrate typical gain vs. -

Page 178: Contact Information

Si 53 xx -RM Jitter Transfer 2.000 0.000 -2.000 -4.000 -6.000 -8.000 -10.000 1000 Offset Frequency, Hz Figure 114. Zoomed View of Jitter Transfer Jitter Transfer 0.500 0.000 -0.500 -1.000 -1.500 -2.000 Offset Frequency, Hz Figure 115. Zoomed Again View of Jitter Transfer (Showing Peaking) Rev. -

Page 179: Figure 116. Maximum Zoomed View Of Jitter Peaking

S i5 3 x x - R M Jitter Transfer 0.100 0.050 0.000 -0.050 -0.100 -0.150 -0.200 Offset Frequency, Hz Figure 116. Maximum Zoomed View of Jitter Peaking Rev. 1.3... -

Page 180: Document Change List

Si 53 xx -RM OCUMENT HANGE Revision 0.3 to Revision 0.4 Updated AC Specifications in Table 8, “AC Characteristics—All Devices” Added Si5365, Si5366, Si5367, and Si5368 operation at 3.3 V Updated Section “6.8. Frame Synchronization Realignment (Si5368 and CK_CONFIG_REG = 1)” ... - Page 181 Added warning about MEMS reference oscillators to “ Appendix A—Narrowband References”. Expanded Figure 45 title. Revision 1.1 to Revision 1.2 Added Si5328. Updated Table 50 on page 108 to include Connor Winfield CS-023E crystal. Revision 1.2 to Revision 1.3 ...

- Page 182 Trademark Information Silicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®...

Need help?

Do you have a question about the Si5328 and is the answer not in the manual?

Questions and answers