Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for NXP Semiconductors LPC2880

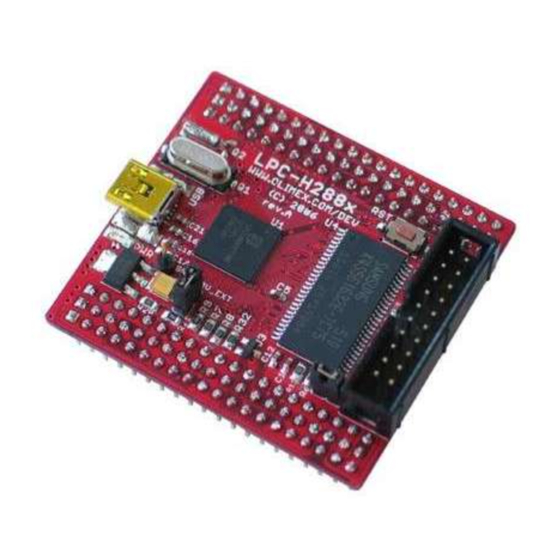

- Page 1 UM10208 LPC2880/LPC2888 User manual Rev. 02 — 1 June 2007 User manual Document information Info Content Keywords LPC2880, LPC2888, LPC288x, ARM, ARM7, embedded, 32-bit, microcontroller, USB 2.0, USB HS Abstract LPC288x User manual...

- Page 2 Various editorial and content updates to the following chapters: • The format of this user manual has been redesigned to comply with the new identity guidelines of NXP Semiconductors. • Legal texts have been adapted to the new company name where appropriate.

-

Page 3: Chapter 1: Introductory Information

UM10208 Chapter 1: Introductory information Rev. 02 — 1 June 2007 User manual 1. Introduction The LPC288x is an ARM7-based microcontroller for portable applications requiring low power and high performance. It includes a USB 2.0 High Speed device interface, an external memory interface that can interface to SDRAM and Flash, an MMC/SD memory card interface, A/D and D/A converters, and serial interfaces including UART, I C, and I... -

Page 4: Applications

UM10208 NXP Semiconductors Chapter 1: LPC2800 Introductory information • 180 pin TFBGA package 3. Applications • Portable, battery powered devices • USB devices 4. Architectural overview The LPC288x includes an ARM7TDMI CPU with an 8kB cache, an AMBA Advanced High-performance Bus (AHB) interfacing to high speed on-chip peripherals and internal and external memory, and four AMBA Advanced Peripheral Buses (APBs) for connection to other on-chip peripheral functions. -

Page 5: On-Chip Flash Memory System

UM10208 NXP Semiconductors Chapter 1: LPC2800 Introductory information THUMB code be as little as 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16 bit memory system. The ARM7TDMI processor is described in detail on the ARM website. -

Page 6: Block Diagram

UM10208 NXP Semiconductors Chapter 1: LPC2800 Introductory information 9. Block diagram A[20:0], D[15:0], DP, DM, VBUS, RREF, CONNECT etc. LPC2880/2888 EXTERNAL HS USB JTAG DEBUG MEMORY WITH DMA INTERFACE CONTROLLER 1 MB 64 kB BOOT FLASH SRAM ARM7TDMI-S VECTORED INTERRUPT... -

Page 7: Chapter 2: Lpc2800 Memory Addressing

Includes AHB Peripherals and 4 APBs 0x8FFF FFFF 1.1 Memory map The LPC2880/2888 memory map incorporates several distinct regions, as shown in Figure 2–2. When an application is running, the CPU interrupt vectors are remapped to allow them to reside in on-chip SRAM. - Page 8 UM10208 NXP Semiconductors Chapter 2: LPC2800 Memory mapping 4.0 GB 0xFFFF FFFF reserved 0x9000 0000 to 0xFFFF FFFF 0x9000 0000 0x8FFF FFFF peripherals includes AHB and 4 APB buses 0x8000 0000 to 0x8FFF FFFF 0x8000 0000 2.0 GB 0x7FFF FFFF...

-

Page 9: Peripheral Addressing

UM10208 NXP Semiconductors Chapter 2: LPC2800 Memory mapping 2. Peripheral addressing Peripheral devices on the LPC288x are distributed among the ARM High-speed Bus (AHB) and four ARM Peripheral Buses (APBs). The following table indicates which bus each device is connected to. Addresses not shown in this table are not used. -

Page 10: Chapter 3: Boot Process

UM10208 Chapter 3: Boot process Rev. 02 — 1 June 2007 User manual 1. Introduction Upon reset, the LPC288x executes code from an internal ROM. This code allows four possible types of startup. These are: • Execute code from internal flash memory. •... -

Page 11: Mode 1: Execute User Program From External

UM10208 NXP Semiconductors Chapter 3: LPC2800 Boot process Mode 1: Execute user program from external memory on static memory bank 0 Static bank 0 of external memory controller is used in a default configuration to execute a user program. The configuration of static bank 0 following reset is for a bus width of 16 bits and an active low chip select. -

Page 12: 0X8000 507C)

UM10208 NXP Semiconductors Chapter 3: LPC2800 Boot process Reset Basic Initialization - disable interrupts - disable cache - initialize CGU Mode = 3? - Continuously toggle pin P2.1 Initialize exception modes Initialize external memory controller Initialize internal memory systems Mode = 1? - Branch to first bank 0 address. - Page 13 UM10208 NXP Semiconductors Chapter 3: LPC2800 Boot process Part Identification register (SYS_PARTID - 0x8000 507C) Table 4: Symbol Description Reset value 31:0 PART_ID This value distinguishes this device type. 0x0102 100A UM10208_2 © NXP B.V. 2007. All rights reserved. User manual Rev.

-

Page 14: Chapter 4: Processor Cache And Memory Mapping

UM10208 Chapter 4: Processor cache and memory mapping Rev. 02 — 1 June 2007 User manual 1. Introduction The ARM CPU in the LPC288x has been extended with a 2-way set-associative cache controller. The cache is 8 kB in size and can store both data and instruction code. The biggest benefit of this cache is that if code is run from non-zero-wait state memory, for instance the internal FLASH controller, these memories can still behave almost as if they are zero-wait state memory. -

Page 15: Description

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache • A cache hit is defined as a read or write by the CPU to an address in memory which is currently in cache. • A cache flush is the act of writing a dirty cache line back to memory. - Page 16 UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Memory Way_0 Way_1 4K bytes 4K bytes line 0 line 0 Word 0 line 1 line 1 Word 1 Read into cache line 0 Word 7 Word 8 128 * 8 Read into...

- Page 17 UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Figure 4–5, page 2 of the lower 32 megabytes of address space has been mapped to an address in the external static memory space by placing a value of 0x104 in the PAGE_ADDRESS_2 register. Details of this remapping may be found in the descriptions of the PAGE_ADDRESS registers later in this chapter.

-

Page 18: Cache Enabling And Function

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache 4.1 Cache enabling and function Following reset, the cache is disabled. The address, data, and control signals of the CPU AHB bus is routed directly to the multilayer AHB matrix. The response from whichever functional block is targeted by the address is routed directly to the CPU. -

Page 19: Cache Reset Status Register (Cache_Rst_Stat, 0X8010 4000)

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Table 5. Cache and memory mapping registers Address Register name Description Reset Access value 0x8010 4010 C_FLUSHES If cache performance analysis is enabled in the CACHE_SETTINGS register, this register indicates the number of times that a dirty cache line has been written back to memory (cache flushes). -

Page 20: Cache Settings Register

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Table 6. Cache Reset Status register (CACHE_RST_STAT, 0x8010 4000) Symbol Description Reset value CACHE_STATUS 0: Cache reset is complete. 1: Cache reset is ongoing. When the cache is reset, software should poll CACHE_STATUS until it is 0. -

Page 21: Cache Page Enable Control Register (Cache_Page_Ctrl, 0X8010 4008)

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Table 7. Cache Settings register (CACHE_SETTINGS, 0x8010 4004) Symbol Description Reset value PERF_ANAL_RST Allows a software reset of the cache performance analysis counters in the registers C_RD_MISSES, C_FLUSHES, and C_WR_MISSES. 0 : Allow performance analysis counters to run, if enabled. -

Page 22: Cache Read Misses Counter

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Table 8. Cache Page Enable Control register (CACHE_PAGE_CTRL, 0x8010 4008) Symbol Description Reset value PAGE_14_ENA This bit enables caching for page 14, as described for bit 0. PAGE_15_ENA This bit enables caching for page 15, as described for bit 0. -

Page 23: Cpu Clock Gate Control

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Original address: 0121_4A90 = 0000 0001 0010 0001 _ 0100 1010 1001 0000 Top 11 address bits removed: 0000 0000 0000 0001 _ 0100 1010 1001 0000 Address bits from PAGE_ADDRESS9 ( 082) =... -

Page 24: Cache Programming Procedures

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Table 11. CPU Clock Gate control (CPU_CLK_GATE, 0x8010 4058) Symbol Description Reset value CPU_CLK_GATE This bit controls clock gating to the CPU. When clock gating is enabled, power is saved by not clocking the CPU when it is stalled waiting for bus access. -

Page 25: Cache Flushing

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache Enable the cache by setting the DATA_ENABLE and/or INSTRUCTION_ENABLE bits in the CACHE_SETTINGS register. For enabling cache functions, these two bits apply to all cache pages that are enabled via the CACHE_PAGE_CTRL register. For disabling cache functions, these bits apply to all 16 cache pages, regardless of the setting of the CACHE_PAGE_CTRL register. -

Page 26: Avoiding Cache Flushing

UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache 1. When data caching is enabled for a page, and another bus master such as the GPMA uses this data as well. 2. When data caching is enabled for a page, and caching for this page is about to be disabled. - Page 27 UM10208 NXP Semiconductors Chapter 4: LPC2800 Cache 2. CPU clock gating off, fractional divider set to 1/7. In this case, the AHB fractional divider has been set to generate a bus clock once every 7 base clock cycles. 3. CPU clock gating enabled, fractional divider set to 1/7.

-

Page 28: Introduction

User manual 1. Introduction The LPC2888 includes one megabyte of flash memory. This memory is located on the AHB and is accessible by all AHB masters. In contrast, the LPC2880 does not include any on-chip flash memory. 2. Features •... - Page 29 UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash • Chip initialization • An access to a flash configuration register • Data latch reading (described in Section 5–4 “In-Application flash programming” on page 8KB small sector # 7 0x104F_E000 to 0x104F_FFFF 8KB small sector # 6...

-

Page 30: Wait State Programming

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash 3.3 Wait state programming The Flash controller takes data from the memory after a predefined number of clock cycles. These clock cycles are called wait states and can be programmed in the WAIT_STATES field of the F_WAIT register. The optimal number of wait states depends on the clock frequency of the AHB clock. - Page 31 UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Un-Protect sector(s) Erase sector(s) Preset data latches Write Word Flash Word complete? (auto) Load Flash Page complete? Last Flash Word complete? Load Flash Word Program Flash Page Sector(s) complete? Protect sector(s) Fig 8. Flash AHB programming flow chart Flash programming includes the following steps: 1.

-

Page 32: Sector Protection And Un-Protection

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash 7. Restoring protection to sectors that have been operated upon These steps are described in more detail in the following sections. 4.2 Sector protection and un-protection A sector is unprotected by writing an even value to its base address (the starting address of the sector), followed by writing the unprotect trigger value to the F_CTRL register. -

Page 33: Presetting Data Latches

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash 4.4 Presetting data latches The Flash memory has data latches to store the data that is to be programmed into the Flash array. When only a part of a Flash page (512 bytes) has to be programmed, the data latches for the rest of the page must be preset to logical ones. -

Page 34: Program/Erase Timer

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash For programming and erase operations, the Flash module needs a 66 kHz clock. This clock is derived from the AHB clock, dividing it by a factor programmed in the CLK_DIV field of the F_CLK_TIME register. A value of zero in this field inactivates the FLASH PROGRAMMING clock. -

Page 35: Flash Control Register (F_Ctrl-0X8010 2000)

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 12. Flash memory controller registers Offset Register name Description Access Reset value 0x8010 2FEC F_INT_SET Set interrupt status bits 0x8000 5030 FLASH_PD Allows turning off the Flash memory for power savings. 0x8000 5034... -

Page 36: Flash Status Register (F_Stat - 0X8010 2004)

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 13. Flash Control register (F_CTRL-0x8010 2000) Bits Name Description Access Reset value FC_PROG_REQ Request Flash programming. 0: no effect. 1 : request for programming. Reserved, user software should not write ones to reserved bits. -

Page 37: Flash Program Time Register

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash 5.3 Flash Program Time register (F_PROG_TIME - 0x8010 2008) The Flash Program Time register controls the timer for all Flash programming tasks. It also allows to read the remaining program or erase time. The fields in the F_PROG_TIME... -

Page 38: Interrupt Registers

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 17. Flash Clock Divider register (F_CLK_TIME - 0x8010 201C) Bits Name Description Access Reset value 11:0 CLK_DIV Clock divider setting. 0x000 : no programming clock is available to the Flash memory. Other : a programming clock is applied to Flash memory. The frequency is the AHB clock frequency divided by (CLK_DIV ×... -

Page 39: 0X8010 2Fe8)

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 19. Flash Interrupt Set register (F_INT_SET - 0x8010 2FEC) Bits Name Description Access Reset value SET_INT These bits allow software setting of interrupt flag bits in the F_INT_STAT register. 0 : leave the corresponding bit unchanged. -

Page 40: Flash Interrupt Enable Clear Register

UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 22. Flash Interrupt Enable Set register (F_INTEN_SET - 0x8010 2FDC) Bits Name Description Access Reset value SET_ENABLE These bits allow software setting of interrupt enable bits in the F_INT_STAT register. 0 : leave the corresponding bit unchanged. - Page 41 UM10208 NXP Semiconductors Chapter 5: LPC2800 Flash Table 25. Flash Initialization register (FLASH_INIT - 0x8000 5034) Bits Name Description Access Reset value FLASH_INIT Flash initialization status bit. 0: If the Flash is not in Power Down mode, it is ready for use.

-

Page 42: Chapter 6: Dc-To-Dc Converter

UM10208 Chapter 6: DC-to-DC converter Rev. 02 — 1 June 2007 User manual 1. Overview The LPC288x includes an on-chip power system which allows the device to be powered by a standard single cell battery (AA or AAA for example), as well as from a USB port or other power source. -

Page 43: General Operation

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter 2. General operation The basic connections within the DC-DC converter are shown in Figure 6–9. Depicted are two inductive DC-DC converters, which are used when the chip is operated from a battery supply. -

Page 44: Unused Dc-Dc Converter

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter LPC288x STOP STOP START START 1.8V DCDC_V BAT54C DDO(1v8) DCDC_LX2 DCDC_V DCDC_V DCDC_LX1 3.3V DCDC_V DDO(3v3) DCDC_V DDI(3v3) USB_VBUS DCDC_V DCDC_V BATTERY 22µF 10V DCDC_GND DCDC_CLEAN Fig 10. Example application hookup for battery and USB power 2.4 Unused DC-DC converter... -

Page 45: Dc-Dc Converter Timing

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter LPC288x External regulator 3.3V or DC-DC 3.3V Power Pins converter External power source External regulator 1.8V or DC-DC 1.8V Power Pins converter DCDC_LX2 DCDC_LX1 STOP START DCDC_V DDO(1v8) DCDC_V DCDC_V DCDC_V DDO(3v3) -

Page 46: Start And Stop From Usb Power

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter A positive edge on the STOP signal causes the DC-DC converter to shut off and the internal reset to be asserted. DCDC_V DDO(3v3) DCDC_V DC-DC enable START STOP Supply_OK ~1ms (internal reset_n) Fig 12. - Page 47 UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter DCDC_V DCDC_V DCDC_V DDO(1V8), DCDC_V DDO(3V3) Supply_OK ~1ms (internal reset_n) STOP Fig 13. Internal DC-DC(2) USB powered (no battery present) 3.3 Switching from battery power to USB power Figure 6–14 shows the timing of the DC-DC Converter when powered by a battery supply, and USB power is cycled.

-

Page 48: Switching From Battery Power To Usb Power . 47 Dc-Dc Registers

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter DCDC_V DC-DC enable DCDC_V DCDC_V DDO(1V8) DCDC_V DDO(3v3) Supply_OK (internal reset_n) STOP START * DC-DC output voltage may vary during the change from DC-DC output to LDO output. ** Between Stop and Start, the device is in the idle mode, supplies DCDC_V... -

Page 49: Dcdc Converter 1 Adjustment Register (Dcdcadjust1 - Address 0X8000 5004)

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter 4.1 DCDC converter 1 Adjustment register (DCDCADJUST1 - address 0x8000 5004) This register allows adjustment of the output voltage of DCDC converter 1, the 3.3 V converter. Table 27. DCDC converter 1 Adjustment register (DCDCADJUST1 - address 0x8000 5004) -

Page 50: Dcdc Clock Select Register (Dcdcclksel - Address 0X8000 500C)

UM10208 NXP Semiconductors Chapter 6: LPC2800 DC-DC converter Table 30. Adjustment range for DCDC converter 2 DCDCADJUST1 bits Low threshold Typical High threshold 1.352 1.380 1.408 1.247 1.300 1.327 1.196 1.221 1.246 4.3 DCDC Clock Select register (DCDCCLKSEL - address 0x8000 500C) The DC-DC converter may be operated from the Ring oscillator contained in the DC-DC converter block or from the 12 MHz clock source from the CGU. -

Page 51: Chapter 7: Clock Generation Unit (Cgu) And Power Control

UM10208 Chapter 7: Clock Generation Unit (CGU) and power control Rev. 02 — 1 June 2007 User manual 1. Features • Two oscillators, 12 MHz main clock and the optional 32.768 kHz “RTC” clock. • Two clock-multiplying phase-locked loops (PLLs). •... - Page 52 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU X32I SLOW fslow X32O OSCILLATOR XTALI ffast FAST XTALO OSCILLATOR MCLK BCKI clocks SWITCHBOX resets FAST MAIN Fig 15. Clock generation unit block diagram The following points bear noting about Figure 7–15: •...

-

Page 53: Register Descriptions

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU module clock. More typically, a selection stage and base clock serve multiple spreading stages and module clocks, which can also use the output(s) of one or more fractional dividers. Fractional dividers multiply their base clock input by an integer “n” and divide it by another integer “m”. - Page 54 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 33. Power Mode Register (PMODE-0x8000 4C00) Symbol Description Reset value CGUMode When this bit is 01, as it is after a reset, modules that have been selected for “wakeup” operation receive clocks. When software writes 11 to this field, clocking to those modules is disabled until a rising edge on the Event Router’s Wakeup output.

-

Page 55: Main Pll

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 3.2 Main PLL The main PLL typically uses the fast (12 MHz) oscillator as its input and multiplies it up to a clock rate at which the processor and core peripherals can operate. -

Page 56: Main Pll Example

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 37. Main PLL registers Name Description Access Reset Address value LPDBYP Divisor Bypass Register. When bit 0 of this register 0x8000 4CF4 is 1, the Post Divider is not used. LPMSEL Multiplication Factor. If LPMBYP is 0, program this... -

Page 57: High Speed Pll Overview

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 3.4 High speed PLL overview The high speed PLL includes an optional initial divider stage, a multiplier stage, and an optional final divider stage. Any of 5 input clocks can be selected as the input to the initial divider. -

Page 58: Memory Table Mapping

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 3.5.1 Memory Table Mapping In this method, the application must include three tables called NTAB, MTAB, and PTAB in memory, the contents of which were calculated by a standalone program as part of the development of the LPC288x. -

Page 59: High Speed Pll Registers

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 3.6 High speed PLL registers The high speed PLL is controlled by the registers listed in Table 7–42. They are described in greater detail thereafter. Table 42. High speed PLL registers Name Description... - Page 60 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 44. Initial Divider Control Register (HPNDEC - 0x8000 4CB4) Symbol Description Reset value NDEC If bit 4 of the HPMODE register is 0, the HS PLL first divides its input clock by 1 through 256 inclusive. The value written to this register...

- Page 61 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 48. Status Register (HPSTAT - 0x8000 4CC0) Symbol Description Reset value HPLOCK Lock Status. A 1 in this bit indicates that the HS PLL has achieved synchronization lock, so that its output can be used for clocking. At slow input frequencies this bit is not reliable: a timeout of 500 uS should be applied to waiting for it to be set.

-

Page 62: High Speed Pll Programming And Operation

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 52. I Bandwidth Register (HPSELI - 0x8000 4CDC) Symbol Description Reset value SELI The value to be written to this field depends on the multiplication factor, and can be determined as described in Section 7–3.5. -

Page 63: Lock Time-Outs

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU c. write a 1 to the appropriate bit of the HPREQ register, d. read the HPACK register repeatedly until the corresponding bit is 1, e. write a 0 to the appropriate bit of the HPREQ register, f. - Page 64 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 55. Switch Configuration Registers (SYSSCR-DAISCR; 0x8000 4000-4024) Symbol Description Reset value ENF1 A 1 in this bit enables side 1 of the stage. ENF2 A 1 in this bit enables side 2 of the stage. Don’t set both ENF1 and ENF2.

-

Page 65: Selection Stage Programming

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 59. Base Control Registers (SYSBCR-DAIOBCR; 0x8000 43F0-43F8) Symbol Description Reset value FDRUN Write a 0 to this bit to disable operation of all the Fractional Dividers connected to this selection stage, overriding their individual RUN bits. -

Page 66: Fractional Divider Programming

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 60. Fractional divider configuration registers Names Symbol Description Reset Addresses value SYSFDCR0, FDRUN A 1 in this bit enables the fractional divider 0X8000 43FC, SYSFDCR1, 0X8000 4400, FDRES Writing 1 to this bit resets the fractional divider. -

Page 67: Power Control Registers

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 61. Spreading stage registers Description Access Power Control Registers. These 5-bit registers control whether and when the clock runs. Power Status Registers. These 2-bit read-only registers indicate whether the clock is running and its wakeup status. -

Page 68: Power Status Registers

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 63. Power control register bit descriptions Symbol Description Reset value PCRUN A 0 in this bit disables the output clock of the spreading stage. PCAUTO A 0 in this bit overrules bits 2 and 3, so that the clock output is controlled only by the RUN bit and (if applicable) the selected fractional divider. -

Page 69: Enable Select Registers

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 65. Power status registers Name Address Name Address Name Address APB0PSR0 0x8000 41CC APB1PSR0 0x8000 41D0 APB2PSR 0x8000 41D4 APB3PSR0 0x8000 41D8 MMIOPSR0 0x8000 41DC AHB0PSR 0x8000 41E0 MCIPSR0 0x8000 41E4 MCIPSR1... - Page 70 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 67. Enable select registers Name Address Name Address Name Address APB0ESR0 0x8000 42E8 APB1ESR0 0x8000 42EC APB2ESR 0x8000 42F0 APB3ESR0 0x8000 42F4 MMIOESR0 0x8000 42F8 AHB0ESR 0x8000 42FC MCIESR0 0x8000 4300 MCIESR1...

-

Page 71: Software Reset Registers

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 69. ESRs with ESR_SEL fields ESRs with 3-bit fields ESRs with 1-bit fields APB0ESR0 APB1ESR0 APB0ESR1 APB2ESR APB3ESR0 EVRTESR MMIOESR0 AHB0ESR0 RTCESR MCIESR0 MCIESR1 ADCESR0 UARTESR0 FLSHESR0 ADCESR1 FLSHESR1 FLSHESR2 WDTESR LCDESR0... -

Page 72: Tabular Representation Of The Cgu

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 70. Software reset registers Name Address Module(s) or Submodule MCIRES 0x8000 4C44 MCI/FD interface MCIRES2 0x8000 4C48 MCI/FD interface UARTRES 0x8000 4C4C UART I2CRES 0x8000 4C50 I C interface SCONRES 0x8000 4C58 Streaming Configuration block... - Page 73 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 71. Structure of the CGU Main Selection Fractional Spreading Clock name Clock description clocks stages divider stage registers registers 32 kHz Osc SYSFDCR0 APB0xxx0 APB0_CLK 12 MHz Osc SYSFDCR1 APB1xxx0 APB1_CLK MCLK pin...

- Page 74 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Table 71. Structure of the CGU Main Selection Fractional Spreading Clock name Clock description clocks stages divider stage registers registers 32 kHz Osc APB0 APB0FDCR0 APB0xxx1 APB0_PCLK 12 MHz Osc APB0FDCR1 EVRTxxx EVRT_PCLK...

-

Page 75: Cgu Usage Notes

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 5. CGU usage notes 5.1 Example 1: Programming the MCI and the LCD interface using the In this example, the main PLL uses the fast (12 MHz) oscillator as input and multiplies it up to 60 MHz. -

Page 76: Code Example

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU 5/12 of the SYS base clock by the fractional divider (SYSFDCR1), i.e. 25 MHz. The LCD_CLK (LCD bus clock for LCD interface) is programmed as 1/10 of the SYS base clock by the fractional divider (SYSFDCR3), i.e. 6 MHz. -

Page 77: Example 2: Programming The Usb, Sdram, Mci, And Lcd Interfaces Using The Cgu

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU /* LCD_CLK, LCD bus clock of LCD interface = (1/10) * SYS base clock */ SYSFDCR3 &= ~CGU_FDCR_FDRUN; /* Stop the fractional divider */ SYSFDCR3 = ((SYSFDCR3_MSUB << 11) /* Set MSUB = -n */ | (SYSFDCR3_MADD <<... - Page 78 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU • Using SDRAM with the external memory controller requires that the EMC_CLK (External memory controller) and the EMC_CLK2 (External memory controller) are the same frequency. The SDRAM also requires that the EMC_CLK (External memory controller) and the EMC_CLK2 (External memory controller) are not higher than 33 MHz.

-

Page 79: Code Example

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU interface) is programmed as 5/12 of the SYS base clock by the fractional divider (SYSFDCR1), i.e. 25 MHz. The LCD_CLK (LCD bus clock for LCD interface) is programmed as 1/10 of the SYS base clock by the fractional divider (SYSFDCR3), i.e. - Page 80 UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU /* AHB clock = (1/2) * SYS base clock */ SYSFDCR0 &= ~CGU_FDCR_FDRUN; /* Stop the fractional divider */ SYSFDCR0 = ((SYSFDCR0_MSUB << 11) /* Set MSUB = -n */ | (SYSFDCR0_MADD << 3) /* Set MADD = m - n */ | CGU_FDCR_FDSTRCH /* Enable stretch */ | CGU_FDCR_FDRES);...

-

Page 81: Low Power Operations

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU EMCESR1 = CGU_ESR_FD0; /* Select spreading stage EMC_CLK2, external memory controller */ MMIOESR1 = CGU_ESR_FD0; /* Select spreading stage MMIO_CLK, main clock for interrupt controller */ MCIESR1 = CGU_ESR_FD1; /* Select spreading stage MCI_MCLK, MCI clock for SD/MCI interface */ LCDESR1 = CGU_ESR_FD3;... -

Page 82: Flash Interface And Programming

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Bit 4 (PERF_ANAL_ENA) of this register controls the cache performance analysis counters in the registers C_RD_MISSES, C_FLUSHES, and C_WR_MISSES. Performance analysis should be disabled when not needed in order to save power. 2. CPU Clock Gate Control register (CPU_CLK_GATE - address 0x8010 4058): Bit 0 (CPU_CLK_GATE) controls clock gating to the CPU. -

Page 83: Dual-Channel 16-Bit Analog-To-Digital Converter

UM10208 NXP Semiconductors Chapter 7: LPC2800 CGU Dual-channel 16-bit analog-to-digital converter 1. Dual Analog In Control register (DAINCTRL - 0x802003A4): – A one in the bit 0 (RSD_PD) of this register powers down the right single-to-differential converter. – A one in the bit 1 (LSD_PD) powers down the left single-to-differential converter. -

Page 84: Chapter 8: External Memory Controller (Emc)

UM10208 Chapter 8: External Memory Controller (EMC) Rev. 02 — 1 June 2007 User manual 1. Introduction The LPC288x External Memory Controller (EMC) is a multi-port memory controller that supports asynchronous static memory devices such as RAM, ROM and Flash, as well as dynamic memories such as Single Data Rate SDRAM. - Page 85 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 74. Examples of compatible SDRAM devices Manufacturer Part number Size Organization Samsung K4S280432 128 MB 32 M x 4 Samsung K4S280832 128 MB 16 M x 8 Samsung K4S281632 128 MB 8 M x 16...

-

Page 86: Supported Static Memory Devices

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 4. Supported static memory devices This section provides examples of static memory devices that are supported by the EMC: • Examples of ROM devices. • Examples of SRAM devices. • Examples of page mode flash devices. -

Page 87: Data Buffers

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 5.3 Data buffers The AHB interface reads and writes via buffers to improve memory bandwidth and reduce transaction latency. The EMC contains four 16-word buffers. The buffers can be used as read buffers, write buffers, or a combination of both. The buffers are allocated automatically. -

Page 88: Low-Power Operation

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC • If the buffers are enabled and the read data is contained in one of the buffers, the read data is provided directly from the buffer. • If the read data is not contained in a buffer, the LRU buffer is selected. If the buffer is dirty (contains write data), the write data is flushed to memory. -

Page 89: Reset

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 75. Memory bank selection Chip select pin Address range Memory type Size of range STCS0 0x2000 0000 - 0x201F FFFF and Static 2 MB 0x4000 0000 - 0x401F FFFF STCS1 0x2400 0000 - 0x241F FFFF and... -

Page 90: Register Description

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 76. Pad interface and control signal descriptions Name Type Value on Value during Description POR reset self-refresh MCLKO Output Follows Follows CCLK SDRAM clock. CCLK Output High SDRAM clock enable. DQM[1:0] Output High High Data mask outputs. - Page 91 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 77. EMC register summary Address Register Name Description Warm Type Reset Reset Value value 0x8000 8208 EMCStaticWaitOen0 Selects the delay from chip select 0 or address change, whichever is later, to output enable.

-

Page 92: Emc Control Register (Emccontrol - 0X8000 8000)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.1 EMC Control Register (EMCControl - 0x8000 8000) The EMCControl Register is a read/write register that controls operation of the memory controller. The control bits can be altered during normal operation. Table 8–78 shows the EMCControl Register. -

Page 93: Emc Status Register (Emcstatus - 0X8000 8004)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.2 EMC Status Register (EMCStatus - 0x8000 8004) The read-only EMCStatus Register provides EMC status information. Table 8–79 shows the bit assignments for the EMCStatus Register. Table 79. EMC Status Register (EMCStatus - address 0x8000 8004) -

Page 94: Dynamic Memory Control Register (Emcdynamiccontrol - 0X8000 8020)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.4 Dynamic Memory Control Register (EMCDynamicControl - 0x8000 8020) The EMCDynamicControl Register controls dynamic memory operation. The control bits can be altered during normal operation. Table 8–81 shows the EMCDynamicControl Register. Table 81. -

Page 95: Dynamic Memory Refresh Timer Register (Emcdynamicrefresh - 0X8000 8024)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 81. Dynamic Control Register (EMCDynamicControl - address 0x8000 8020) Symbol Description Reset Value Write a 1 to this bit to enter SDRAM deep power down mode. See “Low-power SDRAM Deep-sleep mode” on page 88 for more information. -

Page 96: Dynamic Memory Read Configuration Register (Emcdynamicreadconfig - 0X8000 8028)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.6 Dynamic Memory Read Configuration Register (EMCDynamicReadConfig - 0x8000 8028) The EMCDynamicReadConfig Register controls the dynamic memory read strategy. This register must only be modified during system initialization. This register is accessed with one wait state. -

Page 97: Dynamic Memory Active To Precharge Command Period Register (Emcdynamictras - 0X8000 8034)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.8 Dynamic Memory Active to Precharge Command Period Register (EMCDynamictRAS - 0x8000 8034) The EMCDynamicTRAS Register controls the active-to-precharge command period, t This register should only be modified during system initialization, or when there are no current or outstanding transactions. -

Page 98: Dynamic Memory Last Data Out To Active Time Register (Emcdynamictapr - 0X8000 803C)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.10 Dynamic Memory Last Data Out to Active Time Register (EMCDynamictAPR - 0x8000 803C) The EMCDynamicTAPR Register controls the last-data-out to active command time, t This register should only be modified during system initialization, or when there are no current or outstanding transactions. -

Page 99: Dynamic Memory Write Recovery Time Register (Emcdynamictwr - 0X8000 8044)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 10.12 Dynamic Memory Write Recovery Time Register (EMCDynamictWR - 0x8000 8044) The EMCDynamicTWR Register controls the write recovery time, t . This register should only be modified during system initialization, or when there are no current or outstanding transactions. -

Page 100: Dynamic Memory Exit Self-Refresh Register (Emcdynamictxsr - 0X8000 8050)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC ensured by waiting until the EMC is idle, and then entering low-power or disabled mode. This value is normally found in SDRAM data sheets as t , or sometimes as t . This register is accessed with one wait state. -

Page 101: Dynamic Memory Load Mode Register To Active Command Time (Emcdynamictmrd - 0X8000 8058)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 93. Dynamic Memory Active Bank A to Active Bank B Time Register (EMCDynamictRRD - address 0x8000 8054) Symbol Description POR Reset Value Active bank A to SDRAM initialization code should write this field with one... - Page 102 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 95. Dynamic Memory Configuration Register (EMCDynamicConfig - address 0x8000 8100) Symbol Description POR Reset Value Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.

-

Page 103: Dynamic Memory Ras & Cas Delay Register (Emcdynamicrascas - 0X8000 8104)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 96. Address mapping addr addr bits bits 14 12 11:9 8:7 Description 16Mx16, 4 banks, row length=13, col length=9 22:10 24:12 23 100 01 32Mx16, 4 banks, row length=13, col length=10 23:11 25:13 25... -

Page 104: Static Memory Configuration Registers

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 97. Dynamic Memory RAS/CAS Delay Register (EMCDynamicRasCas - 0x8000 8104) Symbol Description POR Reset Value Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined. -

Page 105: Static Memory Write Enable Delay Registers (Emcstaticwaitwen0-2 - 0X8000 8204,24,44)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 98. Static Memory Configuration Registers (EMCStaticConfig0-2 - addresses 0x8000 8200, 0x8000 8220, 0x8000 8240) Symbol Description Reset Value BLS state for If this bit is zero, as it is after a power-on reset, the BLSn[1:0] reads outputs are high during reads. -

Page 106: Static Memory Output Enable Delay Registers

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 99. Static Memory Write Enable Delay registers (EMCStaticWaitWen0-2 - addresses 0x8000 8204, 0x8000 8224, 0x8000 8244) Symbol Description POR Reset Value WAITWEN Controls the delay from chip select assertion to write enable assertion, in AHB HCLK clock cycles. -

Page 107: Static Memory Page Mode Read Delay Registers (Emcstaticwaitpage0-2 - 0X8000 8210,30,50)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 101. Static Memory Read Delay Registers (EMCStaticWaitRd0-2 - addresses 0x8000 820C, 0x8000 822C, 0x8000 824C) Symbol Description Reset Value WAITRD Static memory initialization code should write this field with one less 0x1F... -

Page 108: Static Memory Turnaround Delay Registers (Emcstaticwaitturn0-2 - 0X8000 8218,38,58)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 103. Static Memory Write Delay Registers 0-2 (EMCStaticWaitWr0-2 - addresses 0x8000 8214, 0x8000 8234, 0x8000 8254) Symbol Description Reset Value WAITWR This field controls the length of write cycles. WE and BLS[1:0]... -

Page 109: Emc Miscellaneous Control Register (Emcmisc - 0X8000 5064)

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 105. Static Memory Extended Wait Register (EMCStaticExtendedWait - address 0x8000 8080) Symbol Value Description Reset Value EXTENDEDWAIT If the ExtendedWait bit in the EMCStaticConfig Register is 1, this fields controls the length of the assertion of OE, WE, and BLS in read and write cycles. -

Page 110: Sdram Initialization

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 11. SDRAM initialization Follow the following steps to initialize the EMC and one or more connected SDRAM(s) after power-on reset: 1. Wait 100 ms after power is applied and the system clocks have stabilized. -

Page 111: Sdram Usage Notes

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC 12. Some SDRAMs also have an Extended Mode Register. To set this register, again read an address containing the value for the Extended Mode Register in the row address bits, but set address bit BA1 to 1 to load the Extended Mode Register. The location of BA1 in the memory address is shown in the rightmost 2 columns of Table 96 on page 102. - Page 112 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 109. Micron MT48LC8M16A2 MODE register Address MODE MODE Value Value register register programmed in description example Burst Length 0 0 0 (A3 = 0 and A3 = 1) - burst 0 1 1...

-

Page 113: Mapping The Mode Register Value

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Mapping the MODE register value The Micron MT48LC8M16A2 (8 M x 16) is a BRC type SDRAM. According to Table 8–96, it has the following address mapping: Table 110. Address mapping control bits in EMCDynamicConfig for Micron MT48LC8M16A2... -

Page 114: 16-Bit Memory Data-Bus Width

UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 112. 32-bit memory bus width SDRAM address mapping: 4 K rows, 256/512/1025/2048 columns Table 113. 32-bit memory bus width SDRAM address mapping: 8 K rows, 256/512/1025/2048 columns 12.1.2 16-bit memory data-bus width Table 114. - Page 115 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC Table 115. 16-bit memory bus width SDRAM address mapping: 4 K rows, 256/512/1025/2048 columns Table 116. 16-bit memory bus width SDRAM address mapping: 8 K rows, 256/512/1025/2048 columns UM10208_2 © NXP B.V. 2007. All rights reserved.

- Page 116 UM10208 NXP Semiconductors Chapter 8: LPC2800 EMC UM10208_2 © NXP B.V. 2007. All rights reserved. User manual Rev. 02 — 1 June 2007 116 of 362...

-

Page 117: Chapter 9: Interrupt Controller

UM10208 Chapter 9: Interrupt controller Rev. 02 — 1 June 2007 User manual 1. Features • Maps all LPC288x interrupt sources to processor FIQ and IRQ • Level sensitive sources (see Section 12–2 for edge detect capability) • Programmable priority among sources •... - Page 118 UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller Table 117. LPC288x interrupt sources Bit #/ Register # Interrupt source Timer 0 zero count Timer 1 zero count Real Time Clock Counter Increment Real Time Clock Alarm ADC conversion complete MCI interrupt 1 from Secure Digital and Multimedia Card Interface (see Section 9–3.1)

-

Page 119: Peripherals That Supply Multiple Interrupts

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller INT_PRIOMASK0, INT_PRIOMASK1 registers 29 Input stages TARGET Input stage 1 target Output Prioritization Selection ENABLE PRIO interrupt Interrupt Request 29 Interrupt Request 1 PENDING flag Interrupt vector INT_PENDING Software Interrupt index computation... -

Page 120: Register Description

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller 4. Register description The Interrupt Controller includes the registers shown in Table 9–118. More detailed descriptions follow. Table 118. Interrupt controller register map Name Description Access Reset Address value INT_PRIOMASK0 Priority Mask 0. Determines the priority value that is allowed to 0x8030 0000 interrupt IRQ service routines. -

Page 121: Interrupt Request Registers

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller 5.1 Interrupt Request Registers (INT_REQ1:29, 0x8030 0404 - 0x8030 0474) There is one of these registers for each interrupt source shown in Table 9–117 Table 119. Interrupt Request Registers (INT_REQ1:19, 0x8030 0404 - 0x8030 0474) -

Page 122: 0X8030 0200)

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller 5.2 Interrupt Pending Register (INT_PENDING - 0x8030 0200) Table 120. Interrupt Pending Register (INT_PENDING - 0x8030 0200) Bits Name Description Reset value This bit will always read as 0. 29:1 PENDINGS Each of these bits is 1 if the interrupt request signal from this bit number is asserted, or a software interrupt has been requested for this bit number. -

Page 123: Priority Mask Registers (Int_Priomask0:1, 0X8030 0000 - 0X8030 0004)

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller 5.4 Priority Mask Registers (INT_PRIOMASK0:1, 0x8030 0000 - 0x8030 0004) Table 122. Priority Mask Registers (INT_PRIOMASK0:1, 0x8030 0000 - 0x8030 0004) Bits Name Description Reset value Priority Limit (INT_PRIOMASK0 applies to IRQ ISRs, INT_PRIOMASK1 to FIQ ISRs.) This register defines the current interrupt priority, and allows... -

Page 124: Case Studies On Spurious Interrupts

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller 3. Processing continues for a few cycles due to pipelining. 4. The interrupt occurs, and the interrupt service routine reads the INT_VECTOR register from the interrupt controller. A problem arises if the interrupt controller state changes during step 3. For example, the interrupt that triggered the sequence starting with step 1) may be negated: perhaps the interrupt was disabled in the code executed in step 3. -

Page 125: Workaround

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller SUBS pc, lr, #4 the SPSR_IRQ is restored to the CPSR with the I bit and F bit set, and therefore execution will continue with all interrupts disabled. However, this can cause problems in the... -

Page 126: Solution 3: Re-Enable Fiqs At The Beginning Of The Irq Handler

UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller This is the best workaround where the maximum time for which FIQs are disabled is critical (it does not increase this time at all). However, it does not solve problem one, and requires extra instructions at every point where IRQs and FIQs are disabled together. - Page 127 UM10208 NXP Semiconductors Chapter 9: LPC2800 Interrupt controller The specific interrupt service routine typically reads the status of the interrupting device, and negates the request from the interrupting device, by means like reading data from the device, writing data to the device, or simply disabling the device from requesting further interrupts.

-

Page 128: Features

UM10208 Chapter 10: Timer Rev. 02 — 1 June 2007 User manual 1. Features • Two general purpose timers, each with a 32-bit down counter. • The CGU provides a separate clock to each. • The CGU clock can be used directly, or prescale-divided by 16 or 256. •... -

Page 129: Load Registers

UM10208 NXP Semiconductors Chapter 10: LPC2800 Timer 3.2 Load registers Load registers (T0LOAD, T1LOAD - 0x8002 0000, 0x8002 0400) Table 125: Symbol Description Reset value 31:0 Software can write to this address at any time, to immediately load the undef... -

Page 130: Features

UM10208 Chapter 11: WatchDog Timer (WDT) Rev. 02 — 1 June 2007 User manual 1. Features • Optionally resets chip (via Clock Generation Unit) if not periodically reloaded. • Optional interrupt via Event Router (preceding or instead of Reset) • 32-bit Prescaler and 32-bit Counter allow extended watchdog period 2. -

Page 131: 0X8000 2800)

UM10208 NXP Semiconductors Chapter 11: LPC2800 WDT Table 129. Watchdog register map Name Description Access Reset Address Value WDT_SR Status Register. Bits in this register can be set 0x8000 2800 when the Timer Counter matches MR0 or MR1 The bits can be cleared by writing to this register. -

Page 132: 0X8000 2804)

UM10208 NXP Semiconductors Chapter 11: LPC2800 WDT 4.2 Watchdog Timer Control Register (WDT_TCR - 0x8000 2804) The WDT_TCR controls whether the Timer Counter is enabled or cleared. Table 131. Watchdog Timer Control Register (WDT_TCR - 0x8000 2804) Function Description Reset... -

Page 133: Watchdog Match Control Register

UM10208 NXP Semiconductors Chapter 11: LPC2800 WDT 4.5 Watchdog Match Control Register (WDT_MCR - 0x8000 2814) This register controls what happens when the Timer Counter is equal to Match Control Register 0 at a WDT clock edge. Table 134: Watchdog Match Control Register (WDT_MCR - 0x8000 2814) -

Page 134: 0X8000 283C)

UM10208 NXP Semiconductors Chapter 11: LPC2800 WDT 4.8 Watchdog External Match Register (WDT_EMR - 0x8000 283C) If the Watchdog interrupt or reset function is used, this register must be programmed to signal the Event Router or CGU when a TC match occurs. -

Page 135: Block Diagram

UM10208 NXP Semiconductors Chapter 11: LPC2800 WDT Table 138. Sample setup Module Register Value Result Event Router EVIOMS[0][2] 0x2000 Table 12–139 on page 137, our m0 signal is 0000 connected to bit 29 of Event Router Register Group 2. Set an Interrupt Output Mask bit, so that Event Router interrupt output 0 will be asserted if m0 goes high. -

Page 136: Features

UM10208 Chapter 12: Event router Rev. 02 — 1 June 2007 User manual 1. Features • Allows any of 88 LPC288x pads and 11 internal signals to act as interrupt sources and/or module activators. • Programmable level vs. edge detection and polarity for each signal. •... - Page 137 UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router Table 139. Event router inputs Signal Signal Signal Signal Name Group Name Group Name Group Name Group START A14/P0.30 LD0/P4.4 reserved reserved A15/P0.31 LD1/P4.5 D0/P0.0 A16/P1.0 LD2/P4.6 P2.0 D1/P0.1 A17/P1.1 LD3/P4.7 P2.1 D2/P0.2...

-

Page 138: Register Descriptions

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4. Register descriptions The following table is arranged in the order than the various registers apply to the signal flow through the Event Router. That is, the outputs of the first register are applied to the input signals, and one of the last registers can be read to sense the state of the five outputs of the Event Router block. - Page 139 UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router Table 140. Event router register descriptions Names Description Access Address = Reset value EVIOMK[0:4][0:3] Interrupt Output Mask Registers. There are 20 of 0x8000 1400 = 0 these registers. The first digit in the register names...

-

Page 140: Input Group 0 Registers

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4.1 Input Group 0 Registers The registers listed in Table 12–141 have the bit assignments shown in Table 12–142. Table 141. Registers related to Input Group 0 Register(s) Address(es) EVAPR0 0x8000 0CC0... -

Page 141: Input Group 1 Registers

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4.2 Input Group 1 Registers The registers listed in Table 12–143 have the bit assignments shown in Table 12–144. Table 143. Registers related to Input Group 1 Register(s) Address(es) EVAPR1 0x8000 0CC4... -

Page 142: Input Group 2 Registers

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4.3 Input Group 2 Registers The registers listed in Table 12–145 have the bit assignments shown in Table 12–146. Table 145. Registers related to Input Group 2 Register(s) Address(es) EVAPR2 0x8000 0CC8... -

Page 143: Input Group 3 Registers

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4.4 Input Group 3 Registers The registers listed in Table 12–147 have the bit assignments shown in Table 12–148. Table 147. Registers related to Input Group 3 Register(s) Address(es) EVAPR3 0x8000 0CCC... -

Page 144: Features Register (Evfeatures - 0X8000 0E00)

UM10208 NXP Semiconductors Chapter 12: LPC2800 Event router 4.6 Features Register (EVFEATURES - 0x8000 0E00) This constant read-only register allows general-purpose software to determine how many inputs and outputs the Event Router includes. Table 150. Features Register (EVFEATURES - 0x8000 0E00) -

Page 145: Chapter 13: Real-Time Clock (Rtc)

UM10208 Chapter 13: Real-Time Clock (RTC) Rev. 02 — 1 June 2007 User manual 1. Features • Measures the passage of time to maintain a calendar and clock. • Ultra Low Power design to support battery powered systems. • Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year. -

Page 146: Register Description

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC date and time for an interrupt to be generated. The AMR provides a mechanism to mask alarm compares. If all non-masked alarm registers match the value in their corresponding time counter, then an interrupt is generated. -

Page 147: Miscellaneous Register Group

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC Registers in the RTC other than those that are part of the Prescaler are not affected by chip Reset. These registers must be initialized by software if the RTC is enabled. Reset Value reflects the data stored in used bits only. -

Page 148: Clock Tick Counter Register (Ctcr - 0X8000 2004)

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC Table 154. Interrupt Location Register (ILR - address 0x8000 2000) Symbol Description Reset value RTCCIF When one, the Counter Increment Interrupt block generated an interrupt. Writing a one to this bit location clears the counter increment interrupt. -

Page 149: Alarm Mask Register (Amr - 0X8000 2010) 149 Consolidated Time Registers

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC Table 157. Counter Increment Interrupt Register (CIIR - address 0x8000 200C) Symbol Description Reset value IMDOM When 1, an increment of the Day of Month value generates an interrupt. IMDOW When 1, an increment of the Day of Week value generates an interrupt. NA IMDOY When 1, an increment of the Day of Year value generates an interrupt. -

Page 150: Consolidated Time Register 0 (Ctime0 - 0X8000 2014)

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC 6.2.1 Consolidated Time Register 0 (CTIME0 - 0x8000 2014) Consolidated Time Register 0 contains the low order time values: Seconds, Minutes, Hours, and Day of Week. Table 159. Consolidated Time register 0 (CTIME0 - address 0x8000 2014) -

Page 151: Time Counter Group

UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC 6.3 Time counter group The time value consists of the eight counters shown in Table 13–162 Table 13–163. These counters can be read or written at the locations shown in Table 13–163. Table 162. Time Counter relationships and values... - Page 152 UM10208 NXP Semiconductors Chapter 13: LPC2800 RTC Table 164. Alarm registers Name Size Description Access Address ALSEC Alarm value for Seconds 0x8000 2060 ALMIN Alarm value for Minutes 0x8000 2064 ALHOUR Alarm value for Hours 0x8000 2068 ALDOM Alarm value for Day of Month...

-

Page 153: Chapter 14: Universal Asynchronous Receiver-Transmitter (Uart)

UM10208 Chapter 14: Universal Asynchronous Receiver-Transmitter (UART) Rev. 02 — 1 June 2007 User manual 1. Features • 32 byte Receive and Transmit FIFOs • Superset of the ’650 industry standard. • Receiver FIFO trigger points at 1, 16, 24, and 28 bytes •... - Page 154 UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Table 166. UART Register map Acronym Name Access Reset value Address Line Control 0x00 0x8010 100C Register Modem Control 0x00 0x8010 1010 Register Line Status 0x60 0x8010 1014 Register Modem Status 0x?0 0x8010 1018...

-

Page 155: Receiver Buffer Register (Rbr - 0X8010 1000 When Dlab=0, Read Only)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.1 Receiver Buffer Register (RBR - 0x8010 1000 when DLAB=0, Read Only) The oldest received character in the Rx FIFO can be read from the RBR. The first received data bit is in the LSB (bit 0). If the character received contains less than 8 bits, the unused MSBs are padded with zeroes. -

Page 156: Interrupt Enable Register (Ier - 0X8010 1004 When Dlab=0)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Table 169. Divisor Latch LSB Register (DLL - 0x8010 1000 when DLAB=1) Symbol Description Reset Value The Divisor Latch LSB Register, along with the DLM register, determines 0x01 the baud rate of the UART. -

Page 157: Interrupt Identification Register (Iir - 0X8010 1008, Read Only)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.6 Interrupt Identification Register (IIR - 0x8010 1008, Read Only) The IIR provides a status code that denotes the priority and source of a pending interrupt. The interrupts are frozen during an IIR access. If an interrupt occurs during an IIR access, the interrupt is recorded for the next IIR access. - Page 158 UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Table 173. Interrupt identification and priorities IIR[3:0] Priority Interrupt type Interrupt source Interrupt reset value 0001 None None 0110 Highest RX Line Status or PE or FE or BI LSR Read / Error...

-

Page 159: Fifo Control Register (Fcr - 0X8010 1008)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.7 FIFO Control Register (FCR - 0x8010 1008) The write-only FCR controls the operation of the Rx and Tx FIFOs. Table 174. FIFO Control Register (FCR - 0x8010 1008) Name Value Description Reset... -

Page 160: Line Control Register (Lcr - 0X8010 100C)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.8 Line Control Register (LCR - 0x8010 100C) The LCR controls the format of the data characters that are to be transmitted or received. Table 175. Line Control Register (LCR - 0x8010 100C) -

Page 161: Modem Control Register (Mcr - 0X8010 1010)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.9 Modem Control Register (MCR - 0x8010 1010) The MCR enables the modem loopback mode and controls the RTS output signal. Table 176. Modem Control Register (MCR - address 0x8010 1010) Name Description... -

Page 162: Auto Cts

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART If Auto RTS mode is disabled, the RTS bit (MCR1) controls the RTS output. If Auto RTS mode is enabled, the Rx FIFO controls the RTS output, and software can read the state of RTS in the RTS bit (MCR1). -

Page 163: Line Status Register (Lsr - 0X8010 1014, Read Only)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART UART TX start bits0..7 stop start bits0..7 stop start bits0..7 stop CTS pin Fig 22. Auto CTS functional timing Data is sent as long it’s available and CTS is low. Transmission stalls when CTS goes high and the current Tx character is complete. -

Page 164: Modem Status Register (Msr - 0X8010 1018, Read Only)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Table 178. Line Status Register (LSR - 0x8010 1014, read only) Name Description Reset Value Transmitter In ’450 mode this bit is 1 when both the THR and Transmit shift Empty (TEMT) register are empty. In FIFO mode it is 1 when both the Tx FIFO and the transmit shift register are empty. -

Page 165: Auto-Baud Control Register (Acr - 0X8010 1020)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.15 Auto-baud Control Register (ACR - 0x8010 1020) The Auto-baud Control Register (ACR) controls the process of measuring the incoming clock/data rate for baud rate generation. Table 181. Auto-baud Control Register (ACR - 0x8010 1020) -

Page 166: Auto-Baud Modes

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART The auto-baud interrupts have to be cleared by writing a 1 to the corresponding ACR ABTOIntClr and ABEOIntEn bits. Typically the fractional baud rate generator is disabled (DIVADDVAL = 0) during auto-baud. However, if the fractional baud rate generator is enabled (DIVADDVAL > 0), it does impact the measuring of the RXD pin baud rate, but the value of the FDR is not modified after rate measurement. - Page 167 UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 'A' (0x41) or 'a' (0x61) stop start bit0 bit1 bit2 bit3 bit4 bit5 bit6 bit7 parity UART RX start bit LSB of 'A' or 'a' ACR start rate counter 16xbaud_rate 16 cycles 16 cycles a.

-

Page 168: Irda Control Register (Icr - 0X8010 1024)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.16 IrDA Control Register (ICR - 0x8010 1024) The IrDA Control Register enables and configures the IrDA mode. The value of the ICR should not be changed while transmitting or receiving data, or data loss or corruption may occur. -

Page 169: Baud Rate Calculation

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART This register controls the clock pre-scaler for the baud rate generation. The clock can be pre-scaled by the following factor: MulVal ----------------------------------------------------------- - MulVal DivAddVal The UART baud rate is then: UART_CLK UARTn... - Page 170 UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Additional examples of Baud Rate Vales: Table 14–185 shows additional examples of baud rates for UART_CLK = 20 MHz Table 185. Baud rates available when using 20 MHz peripheral clock (UART_CLK = 20 MHz)

-

Page 171: Nhp Mode Register (Mode - 0X8010 1034)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.19 NHP Mode Register (MODE - 0x8010 1034) The NHP Mode Register controls how data is removed from the receive FIFO, and how UART interrupts are enabled and requested. NHP stands for Nexperia Home Platform. -

Page 172: Interrupt Clear Status Register (Intcs - 0X8010 1Fe8)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART Table 188. Interrupt Status Register (INTS - 0x8010 1FE0) Name Description Reset value WakeUpInt This bit is set whenever a character is received, and is cleared by writing a 1 to bit 7 of the INTCS register. -

Page 173: Interrupt Set Status Register (Intss - 0X8010 1Fec)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.23 Interrupt Set Status Register (INTSS - 0x8010 1FEC) Writing a 1 to certain bits in this write-only register sets the corresponding bit in the INTS register, which may cause a UART interrupt request. Zero bits written to this register have no effect. -

Page 174: Interrupt Clear Enable Register (Intce - 0X8010 1Fd8)

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 3.25 Interrupt Clear Enable Register (INTCE - 0x8010 1FD8) Writing a 1 to certain bits in this write-only register clears the corresponding bit in INTE, thus disabling the corresponding bit in the INTS register from causing a UART interrupt request. -

Page 175: Architecture

UM10208 NXP Semiconductors Chapter 14: LPC2800 UART 4. Architecture The architecture of the UART is shown in Figure 14–24. The receiver block, RX, monitors the serial input line, RXD, for valid input. The RX Shift Register (RSR) assembles characters from RXD. After a valid character is assembled in the RSR, it is passed to the RX Buffer Register FIFO. - Page 176 UM10208 NXP Semiconductors Chapter 14: LPC2800 UART MODEM TRANSMITTER NBAUDOUT INTERRUPT UART interrupt RECEIVER INTERFACE Fig 24. UART block diagram UM10208_2 © NXP B.V. 2007. All rights reserved. User manual Rev. 02 — 1 June 2007 176 of 362...

-

Page 177: Chapter 15: General Purpose Dma Controller (Gpdma)

UM10208 Chapter 15: General Purpose DMA controller (GPDMA) Rev. 02 — 1 June 2007 User manual 1. Introduction The General Purpose DMA Controller (GPDMA) is an AMBA AHB compliant master that provides DMA support to selected LPC288x peripherals. Peripherals that can be serviced by the GPDMA channels include the MCI/SD card interface, UART Tx and/or Rx, the I interface, the Streaming Analog Out (SAO) front-ends to the I S/DAO and 16-bit dual... -

Page 178: Gpdma Functional Description

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 3.1 GPDMA functional description The GPDMA enables peripheral-to-memory, memory-to-peripheral, peripheral-to- peripheral, and memory-to-memory transactions. Each DMA channel can provide unidirectional DMA transfers for a single source and destination. For example, a bidirectional peripheral may need one channel for transmit and one for receive. The... -

Page 179: Dma Request Priority

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 3.1.5 DMA request priority DMA channel priority rotates. The GPDMA central logic continually scans the eight channels and associated flow control signals, for channels that are ready to transfer data. This means that each channel has equal opportunity to transfer data, and helps prevent memory-to-memory transfers from “starving”... -

Page 180: Gpdma Registers

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA MPMC_A19/17 must be updated in a timely manner as the external memory location is read or written. In addition to these possible external request pads, the GPDMA facility includes two possible Enable signals for particular GPDMA channels, as shown in Table 15–195. -

Page 181: Gpdma Register Descriptions

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA Table 196. GPDMA register map Name Description Access Reset Address value DMA0AltSource Channel 0 Alternate Source Address 0x8010 3A00 Register DMA0AltDest Channel 0 Alternate Destination Address 0x8010 3A04 Register DMA0AltLength Channel 0 Alternate Transfer Length... -

Page 182: Destination Address Registers (Dma[0

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.2 Destination Address Registers (DMA[0..7]Dest - 0x8010 3804..38E4) Table 198. Destination Address Registers (DMA[0..7]Dest - 0x8010 3804..38E4) Symbol Description Reset Value 31:0 For a destination peripheral, the address of the destination register. For a destination memory buffer, the address of the start of the buffer. -

Page 183: Channel Configuration Registers (Dma[0

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.4 Channel Configuration Registers (DMA[0..7]Config - 0x8010 380C..38EC) Table 200. Channel Configuration Registers (DMA[0..7]Config - 0x8010 380C..38EC) Symbol Description Reset Value DestID Write 0 to this field if the destination is a memory buffer. In this case the DMA channel increments the address used for each write operation, by 1, 2, or 4 depending on the Size field in this register. -

Page 184: Channel Enable Registers (Dma[0

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.5 Channel Enable Registers (DMA[0..7]Enab - 0x8010 3810..38F0) Table 201. Channel Enable Registers (DMA[0..7]Enab - 0x8010 3810..38F0) Symbol Description Reset Value Writing a 1 to this bit enables a channel, and writing a 0 to this bit disables it. -

Page 185: 0X8010 3C00)

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.9 Alternate Transfer Length Registers (DMA[0..7]AltLength - 0x8010 3A08..3A78) Table 205. Alternate Transfer Length Registers (DMA[0..7]AltLength - 0x8010 3A08..3A78) Symbol Description Reset Value 11:0 This write-only register can be used to set a channel’s transfer length, just like the main Transfer Length Register. -

Page 186: 0X8010 3C04)

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.12 Global Status and Clear Register (DMA_Stat - 0x8010 3C04) Each DMA channel has two status bits in this register: it sets the one of them when it has completed transferring half of a buffer, and sets the other when it has completed a buffer. -

Page 187: 0X8010 3C08)

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.13 IRQ Mask Register (DMA_IRQMask - 0x8010 3C08) 1 bits in this read/write register prevent the corresponding bit in the DMA_Stat register from causing an interrupt. Table 15–209 shows the DMA_IRQMask Register. Table 209. IRQ Mask Register (DMA_IRQMask - 0x8010 3C08) -

Page 188: 0X8010 3C10)

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 4.2.14 DMA Software Interrupt Register (DMA_SoftInt - 0x8010 3C10) Table 210. DMA Software Interrupt Register (DMA_SoftInt - 0x8010 3C10) Symbol Description Reset Value 31:0 The GPDMA sets bit 30 in the DMA_Stat Register when this write-only register is written. - Page 189 UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA When a DMA interrupt occurs, the Interrupt Service Routine (ISR) needs to: 1. Read the DMA_Stat Register to determine which channel(s) have encountered potentially interrupting events. A good tactic at this point is to simply write the value read back to the same register, to clear all of the conditions identified by 1s.

-

Page 190: Scatter/Gather

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA 6. Scatter/Gather Scatter/gather is supported through the use of linked lists. This means that the source and destination data do not have to occupy contiguous areas in memory. This capability requires two consecutively-numbered GPDMA channels. The lower-numbered (“block handling”) channel handles the actual data transfer, and the higher numbered... -

Page 191: Starting Linked List Operation

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA If a linked list isn’t circular, it should have a last entry consisting of any readable word address in word 0, the address of a writable word in word 1, a Transfer Count of 0 (indicating 1 transfer) in word 2, and a Configuration value indicating 32-bit size but PairedChannel Enab=0 in word 3. -

Page 192: For A Last Entry

UM10208 NXP Semiconductors Chapter 15: LPC2800 GPDMA bit is 1, when it completes the buffer the list-following channel (identified by the block-handling channel’s Paired Channel field) is enabled. Return to “Operation of the List-Following channel” on page 191. 6.4.2 For a last entry When the block-transfer channel is enabled for the last entry of a linked list, it reads a word from the Source address and writes it to the Destination address. -

Page 193: Chapter 16: I 2 C Controller

UM10208 Chapter 16: I C controller Rev. 02 — 1 June 2007 User manual 1. Features • Standard I C bus interface, configurable as Master, Slave, or Master/Slave. • Arbitration between simultaneously transmitting masters without corruption of serial data on the bus. •... -

Page 194: Pin Description

UM10208 NXP Semiconductors Chapter 16: LPC2800 I pull-up pull-up resistor resistor C bus OTHER DEVICE WITH OTHER DEVICE WITH LPC288x C INTERFACE C INTERFACE Fig 26. I C bus configuration 4. Pin description Table 214. I C Pin Description Type... -

Page 195: Master Receive Mode

UM10208 NXP Semiconductors Chapter 16: LPC2800 I Section 16–8.3 “Master Transmit mode” describes the software steps to use this mode. 5.2 Master Receive mode In the master receive mode, the I C interface receives data from a slave transmitter. Software initiates the transfer by writing a byte to the Tx FIFO containing the slave address with a 1 in the data direction bit. - Page 196 UM10208 NXP Semiconductors Chapter 16: LPC2800 I Table 215. I C Register Map Name Description Access Reset Address value I2RX Receive Register. Software or a DMA channel can 0x8002 0800 read received bytes from the I C interface’s Receive FIFO by reading this register.

-

Page 197: I 2 C Receive Register (I2Rx - 0X8002 0800)

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 6.1 I C Receive Register (I2RX - 0x8002 0800) Table 216. I C Receive Register (I2RX - 0x8002 0800) Bits Description Reset value If the Receive FIFO is not empty, software or a DMA channel can read the oldest byte in the Receive FIFO from this read-only register, which removes the byte from the FIFO. -

Page 198: C Status Register (I2Sts - 0X8002 0804)

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 6.3 I C Status Register (I2STS - 0x8002 0804) Most of the bits in this register are read-only, but some can be cleared by writing a 1 to that bit position. For the latter kind of bits, writing a 0 has no effect. -

Page 199: I 2 C Control Register (I2Ctl - 0X8002 0808)

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 6.4 I C Control Register (I2CTL - 0x8002 0808) Table 219. I C Control Register (I2CON - 0x8002 0808) Symbol Description Reset value OCIE A 1 in this bit enables an interrupt request when the Operation Complete (OCI) bit in I2STS is 1. -

Page 200: C Clock Divisor Low Register (I2Clklo - 0X8002 0810)

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 6.6 I C Clock Divisor Low Register (I2CLKLO - 0x8002 0810) Table 221. I C Clock Divisor Low Register (I2CLKLO - 0x8002 0810) Bits Description Reset value 14:0 Clock Divisor Low: when the I... -

Page 201: C Tx Byte Count Register (I2Txb - 0X8002 0824)

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 6.11 I C Tx Byte Count Register (I2TXB - 0x8002 0824) Table 226: I C Tx Byte Count Register (I2TXB - 0x8002 0824) Description Reset value This read-only register is cleared whenever the I C interface becomes active as a transmitter, and is incremented by 1 for each byte sent. -

Page 202: Selecting The Appropriate I C Data Rate And Duty

UM10208 NXP Semiconductors Chapter 16: LPC2800 I Table 229. Example I C clock rates I2CLKHI + C bit frequency (kHz) at PCLK (MHz) I2CLKLO 6.25 31.25 62.5 12.5 1.25 6.25 12.5 8. Details of I C operating modes 8.1 Initialization... -

Page 203: Master Transmit Mode

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 8.3 Master Transmit mode Software should initiate Master Transmit mode first calling “set_IEs” with OCIE, DRMIE, and NAIE, plus AFIE if there’s another master in the application. Then software or a DMA channel should write an address/direction byte to the I2TX register, with the direction bit 0 for master-to-slave transmission and bit 8=1 indicating that a Start condition should be sent before the byte. -

Page 204: Master Receive Mode

UM10208 NXP Semiconductors Chapter 16: LPC2800 I If NAI is 1 but TFE (also in I2STS) is 0, unused entries remain in the Tx FIFO, and the ISR should write a 1 to the SoftReset bit in I2CTL, to flush the Tx FIFO in preparation for resuming I C activity. -

Page 205: Slave Mode

UM10208 NXP Semiconductors Chapter 16: LPC2800 I Assuming that the ISR reloaded the Tx FIFO for the Master Receive operation when arbitration was lost, it can use this fact to differentiate these two cases. It should read the number of bytes in the Tx FIFO from the I2TFL register and compare this value to the variable that it saved when it loaded up the Tx FIFO. -

Page 206: Slave Receive Mode

UM10208 NXP Semiconductors Chapter 16: LPC2800 I 8.6 Slave Receive mode If the direction bit is 0, the ISR should set the central state variable to “slave receive”. Then it should read the I2RX register until RFE in I2STS is 1, and store the data in the slave receive buffer. -

Page 207: Chapter 17: Usb Device Controller

UM10208 Chapter 17: USB Device controller Rev. 02 — 1 June 2007 User manual 1. Introduction This chapter describes the USB 2.0 High Speed Device interface. The USB is a 4 wire bus that supports communication between a host and a number (127 max.) of peripherals. -

Page 208: Features

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device Table 230. USB related acronyms, abbreviations, and definitions used in this chapter Acronym/abbreviation Description DD pointer Direct Memory Access End of packet End Point Full Speed HREADY High indicates that a transfer has finished on the AHB. Low extends a transfer. -

Page 209: Usb Pin Description

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 4. USB pin description Table 231. USB interface pad description Pin name Type Description USB D+ pin. USB D- pin. VBUS Input USB VB+ sense. This pad acts as a voltage sensor rather than a power pad. -

Page 210: Data Flow

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 6. Data flow USB is a host controlled protocol, i.e., regardless of whether the data transfer is from the host to the device or device to the host, it is always initiated by the host. During data transfer from a device to the host, the host sends an IN token to the device, after which the device responds with the data. -

Page 211: Dma Mode Transfer

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device been "validated"; otherwise, an empty packet will be sent. Like OUT isochronous endpoints, no interrupt is requested for IN isochronous endpoints other than the frame interrupt. 6.4 DMA mode transfer In DMA mode, the DMA Engine acts as a master on the AHB and transfers data between ARM memory and the local buffer. -

Page 212: Endpoint Configuration

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device interrupt. The length of the data packets transferred is equal to the MaxPacketSize defined for the corresponding endpoint, except for the last packet. The last packet will be communicated from the DMA engine to the USB core through the ‘end_of _transfer’... -

Page 213: Usb Controller Register Descriptions

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device Table 233. USB controller registers Name Description Address USBDevAdr USB Device Address Register 0x8004 1000 USBEMaxSize USB Endpoint Max Packet Size Register 0x8004 1004 USBEType USB Endpoint Type Register 0x8004 1008 USBMode... -

Page 214: Usb Mode Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device Table 234. USB Device Address Register (USBDevAdr - 0x8004 1000) Symbol Value Description Master Reset Reset value value DEVAD Each USB packet contains a 7-bit address. This value controls the address which the USB controller recognizes and responds to. It is reset to zero by both a master reset and a bus reset. -

Page 215: Usb Interrupt Enable Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device The USB controller drives four interrupt request lines (26-29) to the interrupt controller (see Table 9–117), line 26 being the lower priority interrupt. Any USB interrupt configured as a 0 in the USB Interrupt Priority Register (see Section 17–8.10... -

Page 216: Usb Interrupt Status Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 8.7 USB Interrupt Status Register (USBIntStat - 0x8004 1094) This read-only register indicates the interrupt status of various “global” USB conditions. Table 237. USB Interrupt Status Register (USBIntStat - 0x8004 1094) Symbol... -

Page 217: Usb Interrupt Clear Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 8.8 USB Interrupt Clear Register (USBIntClr - 0x8004 10AC) This register allows an interrupt service routine to clear the interrupt requests for various “global” USB conditions. This is a write-only register. Zero bits written to this register have no effect. - Page 218 UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device Table 240. USB Interrupt Priority Register (USBIntP - 0x8004 10B4) Symbol Description Master Reset Reset value value BRESET1 When this bit is 0, as it is after either Reset, an enabled Bus Reset interrupt sets request 0 to the interrupt controller.

-

Page 219: Usb Interrupt Configuration Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 8.11 USB Interrupt Configuration Register (USBIntCfg - 0x8004 1010) Table 241. USB Interrupt Configuration Register (USBIntCfg - 0x8004 1010) Symbol Description Master Reset Reset value value INTPOL A 1 in this bit configures the IRQ and FIQ outputs to the interrupt controller as active low, a 0 as active high. -

Page 220: Usb Frame Number Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 8.12 USB Frame Number Register (USBFN - 0x8004 1074) This read-only register contains the frame number of the last successfully received SOF. To ensure correct and consistent values, read 16 or 32 bits from this register rather than reading bytes. -

Page 221: Usb Endpoint Index Register

UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device 8.15 USB Endpoint Index Register (USBEIX - 0x8004 102C) The contents of this read/write register determine which endpoint is selected for reads from, and writes to, the 5 registers described hereafter, namely the Endpoint Type Register, the Endpoint Control Register, the Endpoint MaxPacketSize Register, the Data Count Register, and the Data Port Register. - Page 222 UM10208 NXP Semiconductors Chapter 17: LPC2800 USB Device Table 246. USB Endpoint Type Register (USBEType - 0x8004 1008) Symbol Description Master Reset Reset value value TYPE Write these bits to tell the USB controller the type of the endpoint selected by the USBEIX register:...

-

Page 223: Usb Endpoint Control Register