Summary of Contents for Texas Instruments DS90UB913A-CXEVM

- Page 1 DS90UB913A-CXEVM & DS90UB914A-CXEVM User's Guide Literature Number: SNLU135B June 2013 – Revised April 2016...

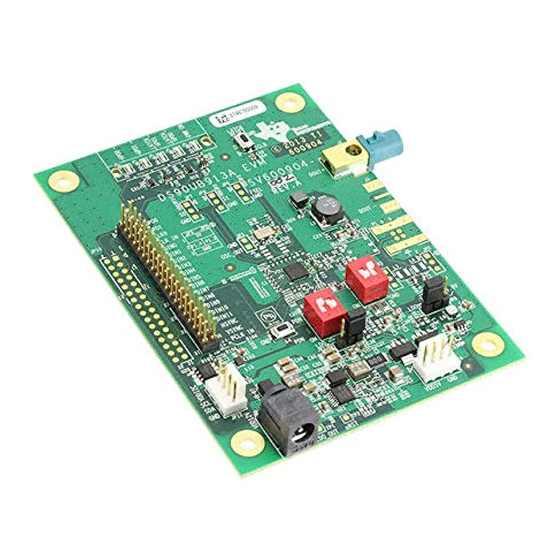

- Page 2 SNLU135B – June 2013 – Revised April 2016 Introduction Overview The Texas Instruments DS90UB913A-CXEVM & DS90UB914A-CXEVM REV A Evaluation Modules (EVM) provides an easy way to evaluate the operation and performance of the DS90UB913AQ / DS90UB914AQ FPD-Link III Serializer/Deserializer. (A) The DS90UB913A-CXEVM REV A contains the DS90UB913AQ Evaluation board.

- Page 3 Quick Setup of EVM www.ti.com Quick Setup of EVM Figure 1-2. DS90UB913A-CXEVM REV A Serializer Board (Default Settings) SNLU135B – June 2013 – Revised April 2016 Introduction Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 4 Quick Setup of EVM www.ti.com Figure 1-3. DS90UB914A-CXEVM REV A Deserializer Board (Default Settings) Introduction SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 5 25 MHz 12 bit high frequency mode 37.5 MHz 6. Go back to Figure 1-2 & Figure 1-3 to double check factory settings. SNLU135B – June 2013 – Revised April 2016 Introduction Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 6 4. Since boards are configured to transmit power over coax cable (PoC), it is not required to connect external power to Serializer, unless PoC is not used. Figure 2-1. Powering DS90UB913A-CXEVM and DS90UB914A-CXEVM Boards Board Setup Details SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright ©...

- Page 7 VSS. Refer to Figure 2-3 below. JP10 and JP1 pins are not connected. Figure 2-3. Parallel Input Connector on Serializer Board SNLU135B – June 2013 – Revised April 2016 Board Setup Details Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 8 JP8 – GPIO0, GPIO1, GPIO2, GPIO3 are the access points for DS90UB914AQ GPIO data. Refer to Figure 2-4 below. JP1 and JP7 pins are not connected. Figure 2-4. Parallel Output Connector on Deserializer Board Board Setup Details SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 9 1.8V VDD and from U3 for 3.3V VDDIO respectively. A power down and power up sequence through switch S1.2 is required, for the mode change to be effective. SNLU135B – June 2013 – Revised April 2016 Board Setup Details Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 10 Low: RIN0+/- input is selected as the active channel on the Deserializer. S1.6-RES Reserved and must be set Low always. S1.7-RES Board Setup Details SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 11 5. On JP6 and JP12, a 2-pin jumper is factory placed as shown in Figure 1-3. This selects power from U4 and U3 LDOs for 1.8V VDD and 3.3V VDDIO respectively. SNLU135B – June 2013 – Revised April 2016 Board Setup Details Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 12 Figure 3-1. USB2ANY Refer to Figure 1-2 Figure 1-3 for these connections. Any I C controller which support clock stretching can be used. SNLU135B – June 2013 – Revised April 2016 Using I Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 13 Here is the USB2ANY pinout with the I C pins highlighted. We typically use jumper wires to connect these to the 913/914 EVMs. SNLU135B – June 2013 – Revised April 2016 Using I Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 14 USB2ANY…’under Devices. Expand the Tools panel and select USB2ANY/Aardvark Setup. SNLU135B – June 2013 – Revised April 2016 Using I Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 15 Once it has been removed (or if there wasn’t one to begin with), select the EVM name from the list on the right and click Add. SNLU135B – June 2013 – Revised April 2016 Using I Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 16 Differential Operation Over a Pair of Coax Cables For differential operation, 1. On DS90UB913A-CXEVM board, change C19 to 0.1 µF, remove R80 and mount J3. 2. On DS90UB914A-CXEVM board, change C7 to 0.1 µF, remove R74 and mount J2. Additional Features SNLU135B –...

- Page 17 Put jumpers on JP3 and JP4 to match the polarity of supply (check on pin2 of each header) Refer Schematic and BOM section for specification. SNLU135B – June 2013 – Revised April 2016 Additional Features Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 18 Use of Optional Rosenberger HSD Connector with STP Cable www.ti.com Figure 4-2. Power Over STP: SER Configuration Additional Features SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 19 2. On Deserializer board, populate JP7, R70, R71, R72, R73, R75, R76, R77, R78, R79, R80, R81, R82, R84, R85, R86. It is recommended to remove JP1. SNLU135B – June 2013 – Revised April 2016 Additional Features Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 20 Appendix A SNLU135B – June 2013 – Revised April 2016 Schematics Schematics SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 21 VDD1P8 Imager Header DS90UB913_Pg3.SchDoc TSW-104-07-G-S GPO0/1 = GPIO0/1 from DES set to static high 4.70k 4.70k Copyright © 2016, Texas Instruments Incorporated SNLU135B – June 2013 – Revised April 2016 Schematics Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 22 VDD3P3 XTAL: SSC-GEN 25MHz: CY25812, x2 = 50MHz 25MHz: CY25814, x4 = 100MHz TSW-103-07-T-S TSW-103-07-T-S TSW-103-07-T-S Copyright © 2016, Texas Instruments Incorporated Schematics SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 23 S_PCLK PCLK R101 PCLK_OUT_FREQ_ M ULT R106 PCLK_U20 PCLK OUT2 PCLK_U20 R102 S_PCLK OUT1 S_PCLK CY2302SXI-1 Copyright © 2016, Texas Instruments Incorporated SNLU135B – June 2013 – Revised April 2016 Schematics Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 24 VDD3P3 JP13 12pF 53.0k Sgnd U3_PIN3 U3_PIN3 34.0k 10µF 0.1µF 0.1µF TSW-103-07-T-S TPS65320QPWPRQ1 0.082µF 20.0k Copyright © 2016, Texas Instruments Incorporated NO-STUFF Schematics SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 25 SDA_A TSW-102-07-G-D GND_A GND_A 0022112042 C11 DNP VDD1P8_A Green Orange 4.70k 4.70k GND_A GND_A Copyright © 2016, Texas Instruments Incorporated GND_A GND_A SNLU135B – June 2013 – Revised April 2016 Schematics Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 26 GND_A VDD3P3_A LOCK LOCK 10pF VDD3P3_A NC7SP04P5X GND_A GND_A ERR_LOCK GND_A Orange 0.1µF NC7SZ175P6X 0.1µF Copyright © 2016, Texas Instruments Incorporated GND_A Schematics SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 27 ROUT7 ROUT6 ROUT9 ROUT8 SDA_A HSYNC SCL_A VSYNC PCLKO ROUT1 ROUT0 TSW-116-07-G-D GND_A NO-STUFF: JP7,R70-73,R75-82, R84-86 Copyright © 2016, Texas Instruments Incorporated SNLU135B – June 2013 – Revised April 2016 Schematics Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 28 R102 U3_PIN3 U3_PIN3 34.0k 10µF 0.1µF 0.1µF GND_A TSW-103-07-G-S TPS65320QPWPRQ1 0.082µF R103 GND_A 20.0k GND_A Copyright © 2016, Texas Instruments Incorporated GND_A Schematics SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 29 SNLU135B – June 2013 – Revised April 2016 Schematics Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 30 Appendix B SNLU135B – June 2013 – Revised April 2016 PCB Layout DS90UB913A-CXEVM Serializer Board Layout 1. DS90UB913A-CXEVM Stackup & FAB Notes PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 31 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 2. Layer 1 - TOP SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 32 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 3. Layer 2 - GND-1 PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 33 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 4. Layer 3 - VCC SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 34 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 5. Layer 4 - GND-2 PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 35 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 6. Layer 5 - SIGNAL SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 36 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 7. Layer 6 - BOTTOM PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 37 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 8. BOTTOM MASK SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 38 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 9. BOTTOM PASTE PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 39 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 10. BOTTOM SILK SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 40 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 11. TOP MASK PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 41 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 12. TOP PASTE SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 42 DS90UB913A-CXEVM Serializer Board Layout www.ti.com 13. TOP SILK PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 43 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com DS90UB914A-CXEVM Deserializer Board Layout 1. DS90UB914A-CXEVM Stackup & FAB Notes SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 44 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 2. Layer 1 - TOP PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 45 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 3. Layer 2 - GND-1 SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 46 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 4. Layer 3 - VCC PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 47 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 5. Layer 4 - GND-2 SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 48 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 6. Layer 5 - SIGNAL PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 49 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 7. Layer 6 - BOTTOM SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 50 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 8. BOTTOM MASK PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 51 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 9. BOTTOM PASTE SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 52 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 10. BOTTOM SILK PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 53 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 11. TOP MASK SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 54 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 12. TOP PASTE PCB Layout SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 55 DS90UB914A-CXEVM Deserializer Board Layout www.ti.com 13. TOP SILK SNLU135B – June 2013 – Revised April 2016 PCB Layout Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 56 Samtec TSW-119-07-T-D Header, 2.54mm, 19x2, Tin, TH JP2, JP3, JP6, JP7, JP8, JP9, Header Samtec TSW-103-07-T-S Header, 2.54 mm, 3x1, Tin, TH JP13 Bill of Materials SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 57 DS90UB913A-CXEVM Serializer Board BOM www.ti.com Table C-1. DS90UB913A-CXEVM BOM (continued) Qty. Reference Part MFR and Part# Footprint Molex 0022112042 Header (friction lock), 100mil, 4x1, Gold, Header Header Samtec TSW-102-07-T-S Header, 2.54 mm, 2x1, Tin, TH Power Switchcraft RAPC722X Power Jack, mini, 2.1mm OD, R/A,...

- Page 58 R102 22Ω 0402 Panasonic ERJ-2GEJ220X RES, 22, 5%, 0.1 W Texas Instruments TPD2E001DRLR Low-Capacitance + / - SOT (DRL) 15 kV ESD-Protection Array for High-Speed Data Interfaces, 2 Channels, -40 to +85 degC, Green (RoHS & no Sb/Br) ON Semiconductor P3P25814AG-08SR Spread Spectrum...

- Page 59 100 MHz MHz, 0.4 A Coilcraft LPS3015-222MLB Inductor, Shielded Drum Core, 2.2µH Ferrite, 2.2 µH, 1.4 A, 0.11 ohm, SMD SNLU135B – June 2013 – Revised April 2016 Bill of Materials Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 60 C1, C11 0402 +/- 5%, C0G/NP0 MuRata GRM188R72A104KA35D CAP, CERM, 0.1 µF, 100 C4, C5 0.1µF 0603 V, +/- 10%, X7R Bill of Materials SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 61 R101 1kΩ 0603 Vishay-Dale CRCW06031K00FKEA RES, 1.00 k, 1%, 0.1 W Texas Instruments TPD2E001DRLR Low-Capacitance + / - SOT (DRL) 15 kV ESD-Protection Array for High-Speed Data Interfaces, 2 Channels, -40 to +85 degC, Green (RoHS & no Sb/Br) Texas Instruments TPS65320QPWPRQ1 40-V Step-Down...

- Page 62 Added PCB layout images and stackup information for both devices............• Revised both 913A and 914A BOM tables to match updated schematics. Revision History SNLU135B – June 2013 – Revised April 2016 Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated...

- Page 63 STANDARD TERMS AND CONDITIONS FOR EVALUATION MODULES Delivery: TI delivers TI evaluation boards, kits, or modules, including any accompanying demonstration software, components, or documentation (collectively, an “EVM” or “EVMs”) to the User (“User”) in accordance with the terms and conditions set forth herein. Acceptance of the EVM is expressly subject to the following terms and conditions.

- Page 64 FCC Interference Statement for Class B EVM devices NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

- Page 65 【無線電波を送信する製品の開発キットをお使いになる際の注意事項】 開発キットの中には技術基準適合証明を受けて いないものがあります。 技術適合証明を受けていないもののご使用に際しては、電波法遵守のため、以下のいずれかの 措置を取っていただく必要がありますのでご注意ください。 1. 電波法施行規則第6条第1項第1号に基づく平成18年3月28日総務省告示第173号で定められた電波暗室等の試験設備でご使用 いただく。 2. 実験局の免許を取得後ご使用いただく。 3. 技術基準適合証明を取得後ご使用いただく。 なお、本製品は、上記の「ご使用にあたっての注意」を譲渡先、移転先に通知しない限り、譲渡、移転できないものとします。 上記を遵守頂けない場合は、電波法の罰則が適用される可能性があることをご留意ください。 日本テキサス・イ ンスツルメンツ株式会社 東京都新宿区西新宿6丁目24番1号 西新宿三井ビル 3.3.3 Notice for EVMs for Power Line Communication: Please see http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page 電力線搬送波通信についての開発キットをお使いになる際の注意事項については、次のところをご覧くださ い。http://www.tij.co.jp/lsds/ti_ja/general/eStore/notice_02.page SPACER EVM Use Restrictions and Warnings: 4.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS.

- Page 66 Notwithstanding the foregoing, any judgment may be enforced in any United States or foreign court, and TI may seek injunctive relief in any United States or foreign court. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated...

- Page 67 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue.

Need help?

Do you have a question about the DS90UB913A-CXEVM and is the answer not in the manual?

Questions and answers