Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for ADLINK Technology SMARC NXP LEC-IMX8M

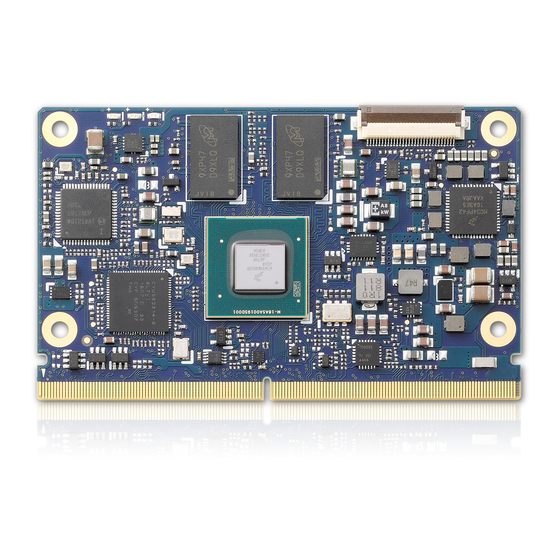

- Page 1 LEC-IMX8M 01/12/2021...

- Page 2 Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies. © Copyright 2017 ADLINK Technology, Incorporated This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

- Page 3 Caution: This information indicates the possibility of minor physical injury, component damage, data loss, and/or program corruption. Warning: This information warns of possible serious physical injury, component damage, data loss, and/or program corruption. Page 3 copyright © 2021 ADLINK Technology Inc.

- Page 4 ADLINK Technology Inc. LEC-iMX8M User’s Guide Revision History Revision Description Date dd/mm/yyyy Author Preliminary engineering version 06/09/2019 Preliminary engineering version updated 05/04/2020 Preliminary engineering version updated 30/07/2020 Release version 12/01/2021 Page 4 copyright © 2021 ADLINK Technology Inc.

-

Page 5: Table Of Contents

LAN ports ..................................................................35 4.3.9 SDIO ....................................................................37 4.3.10 SPI & ESPI ..................................................................38 4.3.11 SPI0 ....................................................................38 4.3.12 ESPI ....................................................................39 General Purpose I2C ................................................................40 4.4.1 GPIO....................................................................41 4.4.2 UART ....................................................................42 Page 5 copyright © 2021 ADLINK Technology Inc. - Page 6 Power ..................................................................... 47 SMARC pin to controller mapping ..........................................................48 5. Software Support ............................................................. 60 5.1.1 Yocto ....................................................................60 5.1.2 Ubuntu ................................................................... 60 6. Mechanical ..............................................................62 7. Thermal Solutions ............................................................ 63 Page 6 copyright © 2021 ADLINK Technology Inc.

- Page 7 LEC-iMX8M User’s Guide SGET SMARC Rev 2.1 List of Figures Figure 1 – Module function diagram ...................................................... 15 Figure 2 – Module top/botom side pin numbering ................................................. 17 Page 7 copyright © 2021 ADLINK Technology Inc.

-

Page 8: Introduction

Carrier Boards that implement other features such as audio CODECs, touch controllers, wireless devices, etc. The modular approach allows scalability, fast time to market and upgradability while still maintaining low costs, low power and small physical size. SMARC module and carrier specifications are available online at: https://www.sget.org/standards/smarc.html Page 8 copyright © 2021 ADLINK Technology Inc. -

Page 9: Specifications

ECDH: FIPS SP800-56A Elliptic Curve Diffie-Hellman NIST standard P256 elliptic curve support SHA-256 & HMAC hash including off-chip context save/restore AES-128: encrypt/decrypt, galois field multiply for GCM Page 9 copyright © 2021 ADLINK Technology Inc. -

Page 10: Video

DSI 4 lanes at max. 1080p@60fps display output (build option multiplexed with LVDS signal) Camera support - Compatible with the MIPI Alliance Interface specification v2.1 - Two MIPI-CSI2 camera inputs, one 4-lane and one 2-lane Page 10 copyright © 2021 ADLINK Technology Inc. -

Page 11: Audio

Intel i210 GbE controller with IEEE-1588 PTP (Precision Time Protocol) support (build option over PCIe ) Supports 10/100/1000-Mbps data transfer rates, both full-duplex and half-duplex 2.5 Extension busses PCIe Two PCI Express GEN2 x1 interfaces 2x USB 3.0/2.0, 2x USB 2.0 and , 1x USB2.0 OTG Page 11 copyright © 2021 ADLINK Technology Inc. - Page 12 - Support for 7-bit and 10-bit address mode - Software programmable clock frequency of 100 kbit/s in Standard-mode, 400 kbit/s in the Fast-mode or 1 Mbit/s in Fast-mode Plus GPIO 12x GPIO with interrupt Page 12 copyright © 2021 ADLINK Technology Inc.

-

Page 13: System Storage

30-pin multipurpose flat cable connector for use with optional DB-30 debug module Provides JTAG, BMC access; UART, power test points; diagnostic LEDs, Power, Reset, Boot configuration 2.9 Boot Modes eMMC and SD-Card boot modes are supported Page 13 copyright © 2021 ADLINK Technology Inc. -

Page 14: Power

5-90% RH operating, non-condensing 5-95% RH storage (and operating with conformal coating) Shock and Vibration IEC 60068-2-64 and IEC-60068-2-27, MIL-STD-202 F, Method 213B, Table 213-I, Condition A and Method 214A, Table 214-I, Condition D Page 14 copyright © 2021 ADLINK Technology Inc. -

Page 15: Block Diagram

UART0 32/64GB UART1 UART3 I2S0 I2S1 SDIO SDMMC GPIO GPIO Expander Crypto Auth. ATECC608A I2C_GP I2C_PM PMIC Board Watchdog / Boot Select, Power Control Management Controller Figure 1 – Module function diagram Page 15 copyright © 2021 ADLINK Technology Inc. -

Page 16: Pinout And Signal Descriptions

The below table is a comprehensible list of all signal pins on the MXM 3 connector in the standard specification SMARC 2.1. Those signals not supported on LEC-iMX8M are strikethrough STRIKETHROUGH TOP Side BOTTOM Side P156 S156 Page 16 copyright © 2021 ADLINK Technology Inc. - Page 17 ESPI_IO_0 / SPI1_DO USB5+ GBE0_MDI1+ GBE1_CTREF note 1 USB5- GBE0_CTREF PCIE_D_TX+ / SERDES_1_TX+ USB0+ GBE0_MDI0- PCIE_D_TX- / SERDES_1_TX- USB0- USB3_SSTX+ GBE0_MDI0+ GBE1_LINK_ACT# note 1 USB0_EN_OC# USB3_SSTX- SPI0_CS1# PCIE_D_RX+ / SERDES_1_RX+ USB0_VBUS_DET note 2 Page 17 copyright © 2021 ADLINK Technology Inc.

- Page 18 RESET_IN# S128 LVDS0_1+ / eDP0_TX1+ / DSI0_D1+ HDMI_D2- / DP1_LANE0- DP0_LANE0- P128 POWER_BTN# S129 LVDS0_1- / eDP0_TX1- / DSI0_D1- DP0_AUX_SEL P129 SER0_TX S130 HDMI_D1+ / DP1_LANE1+ DP0_LANE1+ P130 SER0_RX S131 LVDS0_2+/eDP0_TX2+/ DSI0_D2+ Page 18 copyright © 2021 ADLINK Technology Inc.

- Page 19 Note 2: SPI0 is occupied by CAN+FD controller, SPI0 can be freed up by build option losing CAN+FD function, only CS0 available Note 3: DSI0 is occupied by a DSI to LVDS0/1 bridge, DSI0 can be freed up by build option losing LVDS function Page 19 copyright © 2021 ADLINK Technology Inc.

-

Page 20: Signal Terminology Descriptions

1.8V Power Domain: Active while CARRIER_PWRON is high and CARRIER_SBY# is NOT active (i.e. both signals are high) 3.3Vsb 3.3V Power Domain: Active while CARRIER_PWRON is high (regardless of CARRIER_SBY#) 1.8Vsb 1.8V Power Domain: Active while CARRIER_PWRON is high (regardless of CARRIER_SBY#) Page 20 copyright © 2021 ADLINK Technology Inc. -

Page 21: Signal Description By Function

I2C_LCD_DAT I2C_LCD_DAT I2C_LCD_DAT Note : LVDS0/LVDS1 are standard supported through a DSI to LVDS bridge on the module Note : DSI0 can be freed up by build option, disabling the LVDS0/LVDS1 ports Page 21 copyright © 2021 ADLINK Technology Inc. - Page 22 Secondary panel power enable, active 1.8V Runtime high CMOS LCD1_BKLT_EN S107 Secondary panel backlight enable, active 1.8V Runtime high CMOS LCD1_BKLT_PWM S122 Secondary panel brightness control 1.8V Runtime through pulse width modulation (PWM) CMOS Page 22 copyright © 2021 ADLINK Technology Inc.

- Page 23 DDC data line used for flat panel detection and I/O OD 1.8V Runtime PU 2k2 control CMOS I2C_LCD_CK S139 DDC clock line used for flat panel detection and O OD 1.8V Runtime PU 2k2 control CMOS Page 23 copyright © 2021 ADLINK Technology Inc.

-

Page 24: Second & Third Display Interface

DP0_LANE3- S105 HDMI_CTRL_CK DP1_AUX+ S105 DP0_AUX+ S106 HDMI_CTRL_DAT DP1_AUX- S106 DP0_AUX- P104 HDMI_HPD DP1_HPD P104 DP0_HPD P107 DP1_AUX_SEL P107 DP0_AUX_SEL Note: DisplayPort is not supported on both second and third display interface Page 24 copyright © 2021 ADLINK Technology Inc. - Page 25 HDMI connector. HDMI_HPD P104 HDMI Hot plug active high detection 1.8V Standby Module must tolerate high level in stand-by mode signal that serves as an interrupt CMOS request Page 25 copyright © 2021 ADLINK Technology Inc.

-

Page 26: Mipi Camera Support

CAM0_RST# / P110 Camera 0 reset, active low output O CMOS 1.8V Runtime GPIO2 CAM_MCK Master clock output O CMOS 1.8V Runtime This signal is used by both CSI0 and CSI1 Page 26 copyright © 2021 ADLINK Technology Inc. - Page 27 Camera 0 reset, active low output O CMOS 1.8V Runtime CAM1_PWR# is default, GPIO3 can be enabled GPIO3 through DVT CAM_MCK Master clock output O CMOS 1.8V Runtime This signal is used by both CSI0 and CSI1 Page 27 copyright © 2021 ADLINK Technology Inc.

-

Page 28: I2S (Audio)

Module Input if CPU acts in Slave Mode AUDIO_MCK Master clock output to I2S 1.8V Runtime codec(s) CMOS Note: support for I2S1 signalling pins has been removed during update to SMARC 2.0 specification Page 28 copyright © 2021 ADLINK Technology Inc. -

Page 29: Usb Ports

LEC-iMX8M User’s Guide SGET SMARC Rev 2.1 4.3.5 USB ports Page 29 copyright © 2021 ADLINK Technology Inc. - Page 30 Carrier OD driver to indicate over-current situation. USB3+ USB differential data pairs for port 3 Runtime From USB HUB USB3- USB3_SSRX+ Receive signal differential pairs for USB SS Runtime USB3_SSRX- SuperSpeed on port 3 USB SS Page 30 copyright © 2021 ADLINK Technology Inc.

- Page 31 Pulled low by Module OD driver to disable USB0 power. Pulled CMOS 3.3V low by Carrier OD driver to indicate over-current situation. Note: USB0 is directly connected to the SOC, USB1/2/3/4 have shared bandwidth through a HUB, USB5 is not supported Page 31 copyright © 2021 ADLINK Technology Inc.

-

Page 32: Pcie Ports

I LVDS Runtime Series AC coupled off module PCIE_C_RX- PCIE PCIE_C_REFCK+ Differential PCIe Link C reference clock O LVDS Runtime PCIE_C_REFCK- output PCIE PCIE_C_RST# PCIe Port C reset output 3.3V Runtime CMOS Page 32 copyright © 2021 ADLINK Technology Inc. - Page 33 Note: Module provides PCIe clock generators for PCIE_A and PCIE_B so no external clock source on the carrier is needed Note: Second LAN is a build option and will occupy PCIe_B port Page 33 copyright © 2021 ADLINK Technology Inc.

-

Page 34: Sata Ports

ADLINK Technology Inc. LEC-iMX8M User’s Guide 4.3.7 SATA Ports This design does not support SATA ports Page 34 copyright © 2021 ADLINK Technology Inc. -

Page 35: Lan Ports

Center-Tap reference voltage for Carrier board Ethernet Analog 0 to Runtime magnetic (if required by the Module GBE PHY) 3.3V max GBE0_SDP IEEE 1588 Trigger Signal. For hardware implementation 3.3V Runtime of PTP (precision time protocol) CMOS Page 35 copyright © 2021 ADLINK Technology Inc. - Page 36 Center-Tap reference voltage for Carrier board Ethernet Analog 0 to 3.3V Runtime magnetic `(if required by the Module GBE PHY)` GBE1_SDP IEEE 1588 Trigger Signal. For hardware implementation 3.3V Runtime of PTP (precision time protocol) CMOS Page 36 copyright © 2021 ADLINK Technology Inc.

-

Page 37: Sdio

SDIO_PWR_EN SDIO Power Enable. This signal is used to 3.3V Runtime should be driven low in STB Mode by the enable the power being supplied to a SD/MMC card CMOS module device. Page 37 copyright © 2021 ADLINK Technology Inc. -

Page 38: Spi & Espi

Note: SPI0 is free to use on the carrier but support only one device through CS0 SPI1 supports a CAN bus controller on the module through CS0, that leaves CS1 free for a device on the carrier Page 38 copyright © 2021 ADLINK Technology Inc. -

Page 39: Espi

In Single I/O mode, ESPI_IO_0 is the eSPI master output / eSPI slave input (MOSI) whereas ESPI_IO_1 is the SPI master input / eSPI slave output (MISO). Note: On NXP i.MX8M parts ECSPI is used (Enhanced Configurable Serial Peripheral Interface) Page 39 copyright © 2021 ADLINK Technology Inc. -

Page 40: General Purpose I2C

I2C clock for serial camera data support link MIPI CSI table I2C_PM_DAT P122 Power management I2C bus DATA (SMBus for x86) Power and System Management I2C_PM_CK P121 Power management I2C bus CLK (SMBus for x86) Power and System Management Page 40 copyright © 2021 ADLINK Technology Inc. -

Page 41: Gpio

PU 470K on the CMOS Module GPIO12 S142 General purpose I/O pin 1.8V Runtime PU 470K on the CMOS Module GPIO13 S123 General purpose I/O pin 1.8V Runtime PU 470K on the CMOS Module Page 41 copyright © 2021 ADLINK Technology Inc. -

Page 42: Uart

"Clear to Send" handshake line for port 2 1.8V Runtime CMOS SER3_TX P140 Asynchronous serial data output port 3 1.8V Runtime CMOS SER3_RX P141 Asynchronous serial data input port 3 1.8V Runtime CMOS Page 42 copyright © 2021 ADLINK Technology Inc. -

Page 43: Can Bus

Driven by OD depended on particular module design. Carrier function(s). on Carrier Board should leave this pin floating for normal operation WDT_TIME_OUT# S145 Watch-Dog-Timer Output, low 1.8V Runtime Driven only during runtime active. CMOS Page 43 copyright © 2021 ADLINK Technology Inc. -

Page 44: Power And System Management

Active low, level CMOS Pulled up on module. sensitive. Should be debounced on the Module. RESET_OUT# P126 General purpose reset output to Carrier board. 1.8V Runtime CMOS Page 44 copyright © 2021 ADLINK Technology Inc. -

Page 45: Db30 Multipurpose Connector

4.4.6 DB30 Multipurpose Connector FPC Connector type : HIROSE,FH12-30S-0.5SH(55) DB30 connector brings out the following type of signals SPI0 bus JTAG to SOC Boot Select strap pins BMC programming interface Serial port Page 45 copyright © 2021 ADLINK Technology Inc. -

Page 46: Boot Select

SOC native Force Recovery mode – such as over a Serial Port. For x86 systems this signal may be used to load BIOS defaults. Pulled up on Module. Driven by OD part on Carrier. Page 46 copyright © 2021 ADLINK Technology Inc. -

Page 47: Power

P Not defined within Signal [2 to 3.25] / 3.25V power – 3.0V nominal. May be Terminolgy Descriptions. sourced from a Carrier based Should we define a specific Lithium cell or Super Cap. rail? Page 47 copyright © 2021 ADLINK Technology Inc. -

Page 48: Smarc Pin To Controller Mapping

ADLINK Technology Inc. LEC-iMX8M User’s Guide 4.5 SMARC pin to controller mapping Page 48 copyright © 2021 ADLINK Technology Inc. - Page 49 GBE0_MDI1- Bi-Dir GBE MDI DP83867 TD_M_B VDDIO GBE0_MDI1+ Bi-Dir GBE MDI DP83867 TD_P_B VDDIO GBE0_CTREF GBE0_MDI0- Bi-Dir GBE MDI DP83867 TD_M_A VDDIO GBE0_MDI0+ Bi-Dir GBE MDI DP83867 TD_P_A VDDIO SPI0_CS1# N.C. N.C. Page 49 copyright © 2021 ADLINK Technology Inc.

- Page 50 ESPI_IO_0 / SPI1_DO SPI / 1.8V i.MX8M ECSPI1_MOSI NVCC_ECSPI ALT0 USB0+ Bi-Dir i.MX8M USB1_DP USB1_VDD33 USB0- Bi-Dir i.MX8M USB1_DN USB1_VDD33 USB0_EN_OC# PU-10K GPIO / 3.3V i.MX8M GPIO1_IO13 NVCC_GPIO1 ALT0 USB0_VBUS_DET i.MX8M USB1_VBUS USB1_VDD33 Page 50 copyright © 2021 ADLINK Technology Inc.

- Page 51 PCIe i.MX8M PCIE2_TXN_N PCIE_VPH HDMI_D2+ / DP1_LANE0+ HDMI i.MX8M HDMI_TX_P_LN_2 HDMI_AVDDIO HDMI_D2- / DP1_LANE0- HDMI i.MX8M HDMI_TX_N_LN_2 HDMI_AVDDIO HDMI_D1+ / DP1_LANE1+ HDMI i.MX8M HDMI_TX_P_LN_1 HDMI_AVDDIO HDMI_D1- / DP1_LANE1- HDMI i.MX8M HDMI_TX_N_LN_1 HDMI_AVDDIO Page 51 copyright © 2021 ADLINK Technology Inc.

- Page 52 GPIO / 1.8V +1V8SMC P124 BOOT_SEL1# PU-4k7 GPIO / 1.8V +1V8SMC P125 BOOT_SEL2# PU-4k7 GPIO / 1.8V +1V8SMC P126 RESET_OUT# GPIO / 1.8V PB15 +1V8SMC P127 RESET_IN# PU-4K7 GPIO / 1.8V PB14 +1V8SMC Page 52 copyright © 2021 ADLINK Technology Inc.

- Page 53 VDD_IN 3 ~ 5.25 V P156 VDD_IN 3 ~ 5.25 V CSI1_TX+ / I2C_CAM1_CK PU-2k2 I2C3 i.MX8M I2C3_SCL NVCC_I2C ALT0 CSI1_TX- / I2C_CAM1_DAT PU-2k2 I2C3 i.MX8M I2C3_SDA NVCC_I2C ALT0 RSVD N.C. N.C. Page 53 copyright © 2021 ADLINK Technology Inc.

- Page 54 GBE1_LINK_ACT# GPIO / 3.3V I210 LED1 VDD3P3 PCIE_D_RX+ / SERDES_1_RX+ N.C. N.C. PCIE_D_RX- / SERDES_1_RX- N.C. N.C. USB4+ Bi-Dir USB Hub (CYUSB3314) DS4_DP - AVDD33 USB4- Bi-Dir USB Hub (CYUSB3314) DS4_DM AVDD33 Page 54 copyright © 2021 ADLINK Technology Inc.

- Page 55 DS1_TXM AVDD33 USB3_SSRX+ USB SS USB Hub (CYUSB3314) DS1_RXP AVDD33 USB3_SSRX- USB SS USB Hub (CYUSB3314) DS1_RXM AVDD33 USB3+ Bi-Dir USB Hub (CYUSB3314) DS1_DP AVDD33 USB3- Bi-Dir USB Hub (CYUSB3314) DS1_DM AVDD33 Page 55 copyright © 2021 ADLINK Technology Inc.

- Page 56 PCIE_B_TX- Serial-0.1uF PCIe i.MX8M PCIE1_TXN_N PCIE_VPH DP0_LANE0+ N.C. N.C. DP0_LANE0- N.C. N.C. DP0_AUX_SEL N.C. N.C. DP0_LANE1+ N.C. N.C. DP0_LANE1- N.C. N.C. DP0_HPD N.C. N.C. DP0_LANE2+ N.C. N.C. S100 DP0_LANE2- N.C. N.C. S101 Page 56 copyright © 2021 ADLINK Technology Inc.

- Page 57 SN65DSI84 B_Y3P DSI1_D3+ S121 LVDS1_3- / eDP1_TX3- / Serial-0R LVDS SN65DSI84 B_Y3N DSI1_D3- S122 LCD1_BKLT_PWM N.C. N.C. S123 GPIO13 N.C. N.C. S124 S125 LVDS0_0+ / eDP0_TX0+ / Serial-0R LVDS SN65DSI84 A_Y0P DSI0_D0+ Page 57 copyright © 2021 ADLINK Technology Inc.

- Page 58 GPIO / 1.8V i.MX8M SAI5_MCLK NVCC_SAI5 ALT5 S149 SLEEP# PU-4.7K GPIO / 1.8V i.MX8M SAI5_RXFS NVCC_SAI5 ALT5 S150 VIN_PWR_BAD# PU-10K GPIO / 1.8V +1V8SMC S151 CHARGING# PU-68K GPIO / 1.8V i.MX8M SAI5_RXC NVCC_SAI5 ALT5 Page 58 copyright © 2021 ADLINK Technology Inc.

- Page 59 GPIO / 1.8V +1V8SMC S155 FORCE_RECOV# PU-10K GPIO /3.3V 74LVC1G04 VDD_3V3 S156 BATLOW# PU-4.7K GPIO / 1.8V i.MX8M SAI5_RXD2 NVCC_SAI5 ALT5 S157 TEST# PU-4.7K GPIO / 1.8V i.MX8M SAI5_RXD1 NVCC_SAI5 ALT5 S158 Page 59 copyright © 2021 ADLINK Technology Inc.

-

Page 60: Software Support

Goto : https://github.com/adlink Yocto source-code and compiling instructions are available 5.1.2 Ubuntu Build instruction from source, are available on Github 5.1.3 Android Goto : https://github.com/adlink Android source-code and compiling instructions are available Page 60 copyright © 2021 ADLINK Technology Inc. - Page 61 LEC-iMX8M User’s Guide SGET SMARC Rev 2.1 Page 61 copyright © 2021 ADLINK Technology Inc.

-

Page 62: Mechanical

ADLINK Technology Inc. LEC-iMX8M User’s Guide 6. Mechanical Page 62 copyright © 2021 ADLINK Technology Inc. -

Page 63: Thermal Solutions

SGET SMARC Rev 2.1 7. Thermal Solutions LEC-IMX8M has to be cooled by a passive Heatsink / Heat-spreader optionally available for ordering HTS-sIMX8M Heatspreader for LEC-iMX8M THS-sIMX8M Low profile heatsink for LEC-iMX8M Page 63 copyright © 2021 ADLINK Technology Inc.

Need help?

Do you have a question about the SMARC NXP LEC-IMX8M and is the answer not in the manual?

Questions and answers