Xilinx MicroBlaze ML605 Hardware Tutorial

Axi interface based processor subsystem

Hide thumbs

Also See for MicroBlaze ML605:

- User manual (92 pages) ,

- Hardware user's manual (88 pages) ,

- Manual (22 pages)

Summary of Contents for Xilinx MicroBlaze ML605

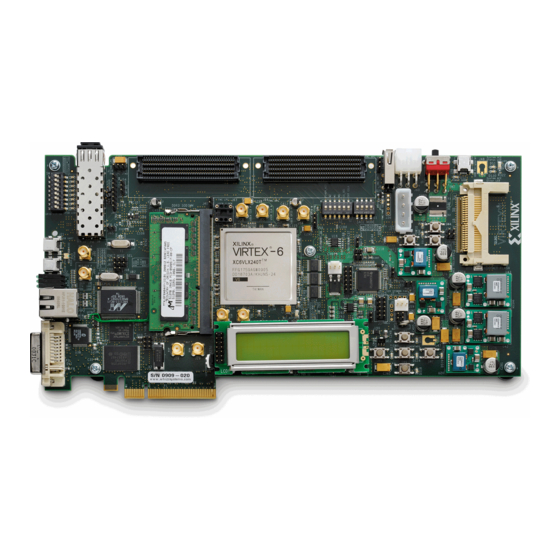

- Page 1 AXI Interface Based ML605/SP605 MicroBlaze Processor Subsystem Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 2: Revision History

Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. -

Page 3: Table Of Contents

........26 Adding IP from the Xilinx IP Catalog . - Page 4 ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 5: Introduction

Hardware Tutorial Introduction This tutorial provides the steps required to build and modify the Xilinx® ML605 MicroBlaze™ Processor Subsystem or the Xilinx SP605 MicroBlaze Processor Subsystem. The tutorial starts with steps in building the basic subsystem. The basic subsystem is then modified by adding the cores necessary to measure throughput on AXI Central DMA (AXI_CDMA). -

Page 6: Prerequisites

Sheet [Ref 5] • Familiarity with UG683, EDK Concepts, Tools, and Techniques, Chapter 1 (Introduction), Chapter 3 (Using Xilinx Platform Studio), and Chapter 4 (Working with the Embedded Platform) [Ref 1] • General knowledge of FPGAs, digital design concepts, and microprocessors •... -

Page 7: Included Files And Systems

MicroBlaze_ProcessorSubSystem (XPS Project) SDK_Export board_test_app board_test_platform SDK_Workspace hw_platform BenchmarkDemo BenchmarkDemo.elf ise_top.bit (contains no bootloop) system.xml pcores edkBmmFile_bd.bmm perf_axi_v1_00_a data system.ucf UG669_01_021711 Figure 1: Tutorial Sandbox Directory Structure ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... - Page 8 (XPS Project) SDK_Export board_test_app board_test_platform SDK_Workspace hw_platform pcores board_test_app board_test_platform perf_axi_v1_00_a ise_top.bit (contains no bootloop) hello_world_0 hello_world_bsp_0 system.xml BenchmarkDemo edkBmmFile_bd.bmm hw_platform BenchmarkDemo.elf data system.ucf UG669_02_021711 Figure 2: Completed Tutorial Directory Structure www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 9: Executing The System

The Port setting (COM1, COM2, COM3, COM4) can vary based on the system setup and might be set up differently than shown in Figure 3. It should be set appropriately for the user’s system. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... - Page 10 Microprocessor Debugger (XMD). Open a command shell with the proper ISE Design tool and EDK environment settings. Note: To set environment variables, run the settings32.bat file located in the Xilinx installation area. At the command prompt, type C:\Xilinx\13.1\ISE_DS\settings32.bat and press Enter.

- Page 11 UG111, Embedded System Tools Reference Manual, Chapter 10. [Ref 6] To download and execute the test software application, enter these commands at the XMD command prompt: XMD% dow board_test_app.elf XMD% con ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

- Page 12 The Ethernet Loopback Test (option 6) takes 30 seconds to complete after displaying the initial setup message. (The Ethernet Loopback Test hangs if jumpers are not set for GMII.) The External Memory Test (option 8) takes approximately 25 minutes to complete. www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 13 Execute the chosen tests and then select 0 to exit. Details about the test options can be found in the UG670, AXI Interface Based ML605/SP605 MicroBlaze Processor Subsystem Software Tutorial [Ref 10. When software execution is completed, enter these commands: XMD% stop XMD% rst XMD% exit ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

-

Page 14: System Design Flow

Hardware Platform Creation Opening the Project Start ISE. On a Windows XP host, select Start All Programs Xilinx ISE Design Suite • 13.1 ISE Design Tools Project Navigator. • On a Linux host, enter ise at a command prompt. -

Page 15: Examining The System

MicroBlaze to interface to the local BRAM memory for the processor. These bus interfaces on MicroBlaze are seen by clicking the + to the left of the microblaze_0 component. (See Figure ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... - Page 16 System Design Flow X-Ref Target - Figure 6 UG669_06_021611 Figure 6: Bus Interfaces View of the MicroBlaze Processor Subsystem www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 17 The visibility of the port connections for the system are controlled by the Port Filters window shown in Figure 8. Many of the peripherals have only default port connections to the AXI interconnect, and these connections are not shown unless Defaults is checked. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

- Page 18 Address Map to expand the address map as shown in Figure 9. This workspace is used to modify the addresses of peripherals in the system. X-Ref Target - Figure 9 UG669_09_021611 Figure 9: Addresses View of the MicroBlaze Processor Subsystem www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 19 With the Bus Interfaces tab selected in the System Assembly view, right-click on the IP core of interest, as shown in Figure X-Ref Target - Figure 10 UG669_10_021611 Figure 10: Menu Option to Configure IP ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

- Page 20 Figure 11: Dual Timer Counter - AXI_Timer Configuration GUI Click Cancel to return to the System Assembly View because no changes are needed to the cores in the system at this time. www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 21: Generating The Hardware Platform

In the Processes window, right-click Generate Programming File and select Run, as shown in Figure X-Ref Target - Figure 12 UG669_12_021611 Figure 12: Generating the Hardware Bitstream Note: This step takes about 1 hour and 30 minutes to complete. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... -

Page 22: Exporting The Base Hardware Platform To Sdk

UG670, AXI Interface Based ML605/SP605 MicroBlaze Processor Subsystem Software Tutorial [Ref 7]. The directory that already exists can be overwritten. • For ML605: Copy ML605_Embedded_Kit\Tutorial_Sandbox\HW\MicroBlaze_Processor_ Subsystem\SDK\SDK_Export ML605_Embedded_Kit\Tutorial_Sandbox\SW\standalone • For SP605: Copy SP605_Embedded_Kit\Tutorial_Sandbox\HW\MicroBlaze_Processor_ Subsystem\SDK\SDK_Export SP605_Embedded_Kit\Tutorial_Sandbox\SW\standalone www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011... -

Page 23: Downloading And Verifying The Design

In the ISE project, under Hierarchy, expand ise_top - STRUCTURE and double click system_i - system (system.xmp). This invokes XPS for the XPS subsystem. In XPS, invoke a Xilinx shell by selecting Project > Launch Xilinx Bash Shell. In the shell, enter xmd and press Enter to invoke XMD. -

Page 24: Customizing The Embedded Hardware Platform

Benchmark Graph is doubled for the total throughput or aggregate throughput (both read and write). The steps to customize the MicroBlaze Processor Subsystem include: Adding IP from the Xilinx IP Catalog, page 26 Connecting the Bus Interfaces, page 29 Connecting Ports, page 33 www.xilinx.com... - Page 25 (512 MB) Controller (64 KB) AXI Interface AXI Interface PERF Monitor Interrupt CDMA Configurable User Logic XC6VLX240T UG669_14_092910 Figure 13: MicroBlaze Processor Subsystem with AXI_CDMA Note: Figure 13 shows the ML605 system. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

-

Page 26: Adding Ip From The Xilinx Ip Catalog

System Design Flow Adding IP from the Xilinx IP Catalog Adding the AXI Central DMA Core The XPS project should already be opened (from the previous section of this document). In the Project Information area of the XPS GUI, click the IP Catalog tab. - Page 27 In the Instantiate and Connect IP dialog, which is automatically invoked, select User will make necessary connections and settings and click OK. (Connecting bus interfaces are discussed later in this tutorial.) ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

-

Page 28: Adding The Perf_Axi Core

Set C_MSTID to 2 and C_MSTID_WIDTH to 3. Click OK. In the Instantiate and Connect IP dialog box, select User will make necessary connections and settings and click OK. (Connecting bus interfaces are discussed later in this tutorial.) www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011... -

Page 29: Connecting The Bus Interfaces

Click the axi_cdma_0 name of the core and wait until the text becomes editable. Enter AXI_Central_DMA and then click Enter. Click the perf_axi_0 name of the core and wait until the text becomes editable. Enter PERF_AXI_Central_DMA and then click Enter. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... - Page 30 • For ML605: Connect the M_AXI connection to the AXI_MM from the pull-down menu as shown in Figure X-Ref Target - Figure 17 UG669_18_021711 Figure 17: Connecting AXI_Central_DMA Interfaces for ML605 www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 31 • For SP605: Connect the M_AXI connection to the AXI_DMA_MM from the pull-down menu as shown in Figure X-Ref Target - Figure 18 UG669_19_021711 Figure 18: Connecting AXI_Central_DMA Interfaces for SP605 ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

- Page 32 For S_AXI, click on the row under the Bus Name column. The Connection Dialog box appears. In the left column select the AXI_MM interconnect. In the right column select the box for AXI_Central_DMA.M_AXI. www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 33: Connecting Ports

Click on the Net column for the Intr row. This brings up the Interrupt Connection Dialog box. In the left column select AXI_Central_DMA:cdma_introut and click the right arrow (see Figure 20). X-Ref Target - Figure 20 UG669_21_021611 Figure 20: Adding the AXI_Central_DMA Interrupt ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011... - Page 34 In Name column for arready, enter the net name AXI_MM_S_ARREADY. • For SP605: In Name column for arvalid, enter the net name AXI_DMA_MM_S_ARVALID. In Name column for arready, enter the net name AXI_DMA_MM_S_ARREADY. • For both: www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

-

Page 35: Implementing And Downloading The Design

System Design Flow In Name column for Intr, enter the net name AXI_Central_DMA_cdma_introut. At this point in the tutorial, additional IP from the Xilinx IP Catalog has successfully been added to the ML605 or SP605 MicroBlaze Processor Subsystem. Implementing and Downloading the Design The design is ready to be synthesized, mapped, placed, and routed in the chosen FPGA architecture. - Page 36 Note: If the browser is an Internet Explorer browser, the Adobe SVG viewer plugin or a similar plugin that enables viewing of SVG files must be installed to view the graph. www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 37 System Design Flow X-Ref Target - Figure 23 UG669_24_110410 Figure 23: Initial Benchmarking Demonstration Web Page ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

- Page 38 An example of the page with benchmarking data is shown in Figure X-Ref Target - Figure 24 UG669_25_110410 Figure 24: Benchmarking Demonstration Web Page with Data Plotted www.xilinx.com ML605/SP605 Hardware Tutorial UG669 (v3.0) March 15, 2011...

- Page 39 12. When finished, in the XMD window enter: XMD% stop XMD% rst XMD% exit Adding the AXI_CDMA with benchmarking cores to analyze performance from the base MicroBlaze Processor Subsystem is completed. ML605/SP605 Hardware Tutorial www.xilinx.com UG669 (v3.0) March 15, 2011...

-

Page 40: Summary

• Loading and executing a design from a pre-built bitstream and ELF • Rebuilding a design • Adding IP from the Xilinx IP catalog to an embedded system • Adding user IP to an embedded system Next Steps Next Step...

Need help?

Do you have a question about the MicroBlaze ML605 and is the answer not in the manual?

Questions and answers