Table of Contents

Advertisement

Quick Links

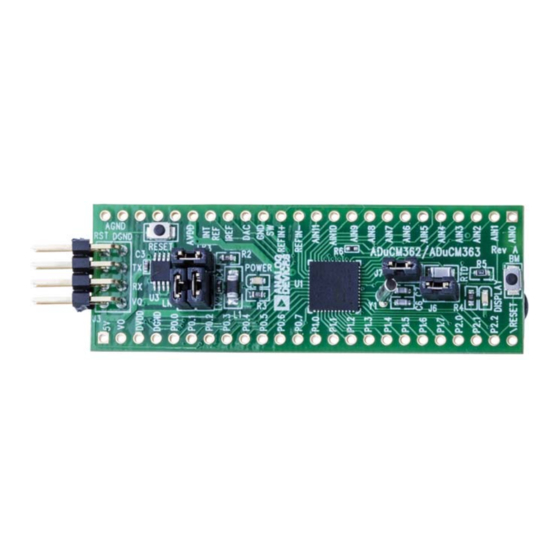

Using the ADuCM362/ADuCM363 Low Power, Precision Analog Microcontroller with Dual

SCOPE

This user guide provides a detailed description of the ADuCM362/ADuCM363 functionality and features.

Note that, throughout this reference manual, multifunction pins, such as P1.0/IRQ3/PWMSYNC/EXTCLK, are referred to either by the entire pin

name or by a single function of the pin, for example, P1.0, when only that function is relevant.

DISCLAIMER

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices

for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without

notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered

trademarks are the property of their respective owners.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process

with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

analog.com

Figure 1. ADuCM362 Block Diagram

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND

LEGAL TERMS AND CONDITIONS.

Hardware Reference Manual

ADuCM362/ADuCM363

Sigma-Delta ADCs, ARM Cortex-M3

Rev. B | 1 of 170

Advertisement

Table of Contents

Summary of Contents for Analog Devices ADuCM362

-

Page 1: Scope

Figure 1. ADuCM362 Block Diagram Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience. -

Page 2: Table Of Contents

Register Access Conventions......4 Control Data Configuration.......63 Acronyms and Abbreviations......4 DMA Transfer Types (CHNL_CFG[2:0])...64 Introduction to the ADuCM362/ADuCM363...5 Address Calculation......... 66 Main Features of ADuCM362/ADuCM363..6 DMA Memory Mapped Registers..... 68 Memory Organization......... 7 Flash Controller........... 83 Clocking Architecture..........9 Flash Controller Features.........83 Clocking Architecture Features...... - Page 3 Hardware Reference Manual ADuCM362/ADuCM363 TABLE OF CONTENTS SPI and Power-Down Modes......126 Wake-Up Timer Overview......147 SPI Memory Mapped Registers..... 126 Wake-Up Timer Operation......147 UART Serial Interface........132 Wake-Up Timer Memory Mapped Registers.. 149 UART Features..........132 Watchdog Timer..........154 UART Overview..........132 Watchdog Timer Features......

-

Page 4: Using The Aducm362/Aducm363 Hardware User Guide

Hardware Reference Manual ADuCM362/ADuCM363 USING THE ADUCM362/ADUCM363 HARDWARE USER GUIDE NUMBER NOTATIONS Table 1. Number Notations Notation Description Bit N Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0. -

Page 5: Introduction To The Aducm362/Aducm363

An option to buffer the external reference inputs is also provided on chip. A single-channel buffered voltage output DAC is also provided on chip. The ADuCM362/ADuCM363 also integrates a range of on-chip peripherals that can be configured under microcontroller software control as required in the application. These peripherals include UART, I and dual SPI serial input/output (I/O) communication controllers, 19-pin GPIO ports, two general-purpose timers, wake-up timer, and system watchdog timer. -

Page 6: Main Features Of Aducm362/Aducm363

► 10 μA/50 μA/100 μA/150 μA/200 μA/250 μA/300 μA/400 μA/450 μA/500 μA/600 μA/750 μA/800 μA and 1 mA current source options ► On-chip precision voltage reference (see the ADuCM362/ADuCM363 data sheet for more details) ► Single 12-Bit Voltage Output DAC Voltage output DAC ►... -

Page 7: Memory Organization

4 mA to 20 mA loop powered smart sensor systems ► MEMORY ORGANIZATION The ADuCM362/ADuCM363 memory organization is described in this section. Three separate blocks of memory are accessible to the user: 24 kB of SRAM from 0x20000000 to 0x20005FFF ►... - Page 8 Hardware Reference Manual ADuCM362/ADuCM363 INTRODUCTION TO THE ADUCM362/ADUCM363 Figure 3. ADuCM362/ADuCM363 Cortex-M3 Memory Map Diagram analog.com Rev. B | 8 of 170...

-

Page 9: Clocking Architecture

► CLOCKING ARCHITECTURE BLOCK DIAGRAM Figure 4. ADuCM362 Clocking Architecture Block Diagram (the ADuCM363 Clocking Architecture Block Diagram is Identical, Except ADC0 Is Removed) CLOCKING ARCHITECTURE OVERVIEW Three of the clock sources—LFOSC, HFOSC, and LFXTAL—can be used as system clocks. An external clock on P1.0 can also be used for test purposes. -

Page 10: Clocking Architecture Operation

Hardware Reference Manual ADuCM362/ADuCM363 CLOCKING ARCHITECTURE Figure 4 shows all the clocks available and includes clock gates for power management. For more information about the clock gates, see the Power Management Unit section. CLOCKING ARCHITECTURE OPERATION At power-up, the processor executes from the 16 MHz internal oscillator divided down to 1 MHz. User code can select the clock source for the system clock and can divide the clock by a factor of 2 , where CD is the clock divider bits (CLKCON0[2:0]). - Page 11 Hardware Reference Manual ADuCM362/ADuCM363 CLOCKING ARCHITECTURE Table 5. CLKCON0 Register Bit Descriptions (Continued) Bits Name Description 100: DIV16: UCLK/16 101: DIV32: UCLK/32 110: DIV64: UCLK/64 111: DIV128: UCLK/128 UCLK is the 16 MHz system clock divided by the CLKSYSDIV (Bits[1:0]) bit setting.

- Page 12 Hardware Reference Manual ADuCM362/ADuCM363 CLOCKING ARCHITECTURE Table 6. CLKCON1 Register Bit Descriptions (Continued) Bits Name Description 111: UCLK/128 = 125 kHz [2:0] SPI0CD Clock divide bits for SPI0 system clock 000: UCLK/1 = 16 MHz 001: UCLK/2 = 8 MHz...

- Page 13 Hardware Reference Manual ADuCM362/ADuCM363 CLOCKING ARCHITECTURE Clocking Architecture Control Register 2 Address: 0x4000203C, Reset: 0x7F07, Name: CLKCON2 Table 8. CLKCON2 Register Bit Descriptions Bits Name Description Reserved These bits are reserved and must be written 0. Clock divide bits for DAC system clock.

- Page 14 Hardware Reference Manual ADuCM362/ADuCM363 CLOCKING ARCHITECTURE Table 10. CLKSYSDIV Register Bit Descriptions (Continued) Bits Name Description 11: the ADC is clocked from an 8 MHz clock (default). [3:2] Reserved These bits are reserved and must be written 0. [1:0] UCLKCD Clock divide bits for UCLK system clock.

-

Page 15: Power Management Unit

Cortex-M3 processor into sleep mode; it is independent of the power mode settings of the PMU. When the ADuCM362/ADuCM363 wake up from any of the low power mode, the devices return to Mode 0. Power Mode: MCUHALT Mode, Mode 1 The system gates HCLK at an early stage, after the Cortex-M3 processor enters sleep mode. -

Page 16: Power Management Unit Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 POWER MANAGEMENT UNIT Power Mode: PERHALT Mode, Mode 2 The system gates PCLK at an early stage, after the Cortex-M3 processor enters sleep mode. The PCLK is the clock to user peripherals. The gating of this clock stops all clocks to these peripherals. The Cortex-M3 processor FCLK is active and the device wakes up using the NVIC. If ADC0, ADC1, or sinc2 DMA channels are enabled in the DAMENSET register, the clock remains active to the DMA block and the SRAM. - Page 17 Hardware Reference Manual ADuCM362/ADuCM363 POWER MANAGEMENT UNIT Table 13. PWRMOD Register Bit Descriptions (Continued) Bits Name Description Other: reserved. To place the cortex in deep sleep mode when the device is in Mode 4 or Mode 5, the Cortex-M3 processor system control register (Address 0xE000ED10) must be configured to 1 in Bit 2 (SCR[2]).

-

Page 18: Cortex-M3 Processor

Several Cortex-M3 components are flexible in their implementation. This section details the actual implementation of these components in the ADuCM362/ADuCM363. Serial Wire Debug (SW/JTAG-DP) The ADuCM362/ADuCM363 only supports the serial wire interface via the SWCLK and SWDIO pins. It does not support the 5-wire JTAG interface. analog.com... -

Page 19: Related Documents

System Exceptions and Peripheral Interrupts section. Wake-Up Interrupt Controller (WIC) The ADuCM362/ADuCM363 has a modified WIC, which provides the lowest possible power-down current. This feature is transparent to the user, and more details are available in the Power Management Unit section. -

Page 20: Adc Circuit

Figure 5. ADC Block Diagram ADC CIRCUIT OVERVIEW The ADuCM362 incorporates two independent multichannel Σ-Δ ADCs (ADC0 and ADC1). The ADuCM363 incorporates one multichannel Σ-Δ ADC (ADC1). Both ADCs are connected to a common input multiplexer of six fully differential inputs or 11 single-ended inputs. The device also contains a low noise, low drift internal band gap reference. -

Page 21: Adc Circuit Operation

See the specifications in the ADuCM362/ADuCM363 data sheet for further details. The ADuCM362 supports a mode of operation in which the PGA on both ADCs can drive the ADC modulator directly regardless of the gain setting, allowing the input buffers to be bypassed and powered down. Because each positive and negative input buffer consumes typically 35 μA, this represents an I... - Page 22 ±250 mV; when using a gain of 8, the maximum input voltage that can be applied is ±125 mV. For the full list of valid input voltage ranges for all ADCs, refer to the ADuCM362/ADuCM363 data sheet. To determine if the ADC input is about to exceed the 1 V PGA output threshold, the ADC comparator can be used.

- Page 23 Bipolar/Unipolar Configuration The analog inputs to the ADuCM362/ADuCM363 can accept either unipolar or bipolar input voltage ranges. A bipolar voltage does not imply that the device can handle negative voltages with respect to ground. It simply means that the input range can vary above or below the common-mode voltage by the value of V as long as the absolute input voltage range is not exceeded.

- Page 24 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT Fully Differential and Single-Ended Inputs Both ADCs support two voltage input types. In fully differential mode, the user can select from any input pair to both ADCs. The external circuit determines the common-mode voltage; therefore, the external circuit must be configured to ensure that the differential signal does not exceed the minimum/maximum absolute input voltage for that input.

-

Page 25: Other Adc Support Circuits

Four reference sources are supported by the ADuCM362/ADuCM363: internal reference, External Reference 1, External Reference 2, and AVDD. Internal Reference The internal reference is a precision 1.2 V band gap, low noise, low drift reference. See the ADuCM362/ADuCM363 data sheet for more information. External Reference 1 External Reference 1 is connected to the VREF+ and VREF−... - Page 26 256/512/768/1024 × ADC clocks, resulting in sampling periods of 2 ms/4 ms/6 ms/8 ms, respectively, by setting DETCON[1:0]. Figure 7. ADuCM362/ADuCM363 Step Detection Timing Diagram Figure 8 shows, the difference between Level 1 and Level 2 is greater than the selected threshold level: If Output 4 −...

- Page 27 Diagnostic Current Sources To detect a connection failure to an external sensor, the ADuCM362/ADuCM363 incorporates a 50 µA constant (burnout) current source on the selected analog input channels to both ADCs. These can be switched on or off via the ADCxCON[11:10] bits. Diagnostic current sources are accurate to ±10%.

-

Page 28: Other Adc Details

OTHER ADC DETAILS Digital Filter Option The ADuCM362/ADuCM363 main ADC digital filter settings are controlled by the ADC0FLT and ADC1FLT registers. The decimation factor of the sinc3 or sinc4 filter is set using ADCxFLT[6:0]. See Table 17 Table 18 for further details on the decimation factor values. - Page 29 The noise resolution figures of both ADCs are available in the ADuCM362/ADuCM363 data sheet. Simultaneous Sampling The ADuCM362 has two identical ADCs. These can be configured for simultaneous sampling. The filter settings of ADC1 (in ADC1FLT) are then automatically applied to ADC0.

- Page 30 Temperature Sensor Settings The ADuCM362/ADuCM363 provides a voltage output from an on-chip band gap reference that is proportional to the absolute temperature on ADC1. This voltage output can also be routed through the front end of the ADC1 multiplexer (effectively, an additional ADC channel input), facilitating an internal temperature sensor channel that measures die temperature.

- Page 31 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT pADI_ADC1 > CON = 0xBC18F, AIN+ = DAC, AIN− = AGND ► AVDD/4 Settings The AVDD/4 settings are as follows: Select DAC as AIN− and set the DAC output to 600 mV ► pADI_DAC > DACCON = 0x210 ►...

- Page 32 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT void ADC0DMAREAD(unsigned long *pucRX_DMA, unsigned int iNumRX) DmaDesc Desc; // Common configuration of all the descriptors used here Desc.ctrlCfg.bits.cycle_ctrl = cyclectrl_basic; desc.ctrlcfg.bits.next_useburst = 0x0; desc.ctrlcfg.bits.r_power = 0; Desc.ctrlCfg.Bits.src_prot_ctrl = 0x0; Desc.ctrlCfg.Bits.dst_prot_ctrl = 0x0; Desc.ctrlCfg.Bits.src_size = SRCSIZE_WORD;...

- Page 33 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT 0x00, // ADCxCFG 0x3, // ADC0FLT 0x113}; // ADC0MDE - G = 4 ucDMA_ADC0_COMPLETE = 0; // Flag to indicate DMA complete - set in IRQ handler pADI_ADC0->MDE; // Allow writing to the calibration registers by plac►...

- Page 34 There is still significant space at the bottom end if the noise performance improves or if additional filtering is applied. The ADC does not write new data into the ADCxDAT MMRs if the relevant RDY bits are set; however, this does not apply if the ADuCM362/ ADuCM363 is in power-down mode with DMA enabled, in which case ADCxDAT always contains the most recent ADC data.

-

Page 35: Adc Circuit Memory Mapped Registers

Holds the threshold value for the accumulator comparator 0x00000000 0x40030044 ADC0PRO Configuration register for postprocessing of ADC0 results 0x00 0x40030048 ADC0DAT Conversion result register 0x00000000 Table 20. ADC1 Register Summary (ADuCM362 and ADuCM363) Address Name Description Access Default 0x40030080 ADC1STA ADC status register 0x00... - Page 36 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT Table 20. ADC1 Register Summary (ADuCM362 and ADuCM363) (Continued) Address Name Description Access Default 0x400300B8 ADC1THV 8-bit threshold exceeded counter register 0x00 0x400300BC ADC1ACC 32-bit accumulator register 0x00000000 0x400300C0 ADC1ATH Holds the threshold value for the accumulator comparator...

- Page 37 ADCxRCR register. Cleared to 0 after reading ADCDAT. Interrupt Control Registers Address: 0x40030004, Reset: 0x00, Name: ADC0MSKI (ADuCM362 Only) Address: 0x40030084, Reset: 0x00, Name: ADC1MSKI (ADuCM362 and ADuCM363) Table 24. Bit Descriptions for ADCxMSKI Bits Name Description...

- Page 38 /49150 = 48.8 µV) and the offset must be adjusted when changing gain settings. Address: 0x4003000C, Reset: Factory defined, Name: ADC0OF (ADuCM362 Only) Address: 0x4003008C, Reset: Factory defined, Name: ADC1OF (ADuCM362 and ADuCM363) analog.com Rev. B | 38 of 170...

- Page 39 ADCxVDDGN before using the device. Gain Calibration Registers When Using Internal Reference Register Address: 0x40030010, Default: Factory Defined, Name: ADC0INTGN (ADuCM362 Only) Address: 0x40030090, Default: Factory Defined, Name: ADC1INTGN (ADuCM362 and ADuCM363) Table 27. Bit Descriptions for ADCxINTGN Bits Name...

- Page 40 Table 30. Bit Descriptions for ADCxCFG Bits Name Description SIMU (valid for 0: enable simultaneous sampling. ADC1FLT settings are used for both ADCs (valid for ADuCM362 only). ADuCM362 only). 1: independent ADC sampling. (Valid for ADuCM362 only). Reserved for ADuCM363. Reserved Reserved.

- Page 41 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT Filter Configuration Registers Address: 0x40030020, Reset: 0x007D, Name: ADC0FLT (ADuCM362 Only) Address: 0x400300A0, Reset: 0x007D, Name: ADC1FLT (ADuCM362 and ADuCM363) Table 31. Bit Descriptions for ADCxFLT Bits Name Description CHOP Enables system chopping. Enabling system chopping results in very low offset errors and drift.

- Page 42 However, a software delay is required between writing to ADCMDE and writing to the offset or gain register. Address: 0x40030024, Reset: 0x0003, Name: ADC0MDE (ADuCM362 Only) Address: 0x400300A4, Reset: 0x0003, Name: ADC1MDE (ADuCM362 and ADuCM363) Table 32. Bit Descriptions for ADCxMDE...

- Page 43 ADCxRCV holds the current number of ADC conversion results. The value of the counter is masks ADC interrupts, resulting in lower frequency interrupts to the ADuCM362/ADuCM363. This value is also important where a number of samples must be accumulated in the ADCxACC. The number of samples accumulated must be read from this MMR to calculate the average result.

- Page 44 ADCxTH controls the comparator on the ADC output. The MMR holds the threshold value against which the absolute value of the ADC conversion result is compared. The comparison is performed at F , allowing the ADuCM362/ADuCM363 to be interrupted during a high input event, even if the ADC RDY interrupts are masked using the ADCxRC counters.

- Page 45 ADC CIRCUIT Address: 0x40030040, Reset: 0x00000000, Name: ADC0ATH (ADuCM362 Only) Address: 0x400300C0, Reset: 0x00000000, Name: ADC1ATH (ADuCM362 and ADuCM363) ADCxATH controls the accumulator comparator on the ADC output. The MMR holds the threshold value against which the absolute value of the accumulated ADC conversion result is compared.

- Page 46 Reserved. Always set to 0. ADCSEL Select ADC for the ADuCM362. This bit allows the user to choose the step detection filter that is enabled for ADC0 or ADC1. For the ADuCM363, this bit is reserved and must be set to 1.

- Page 47 DMA enable for ADC0 registers—ADC0CON, ADC0FLT, ADC0CP, ADC0CN, ADC0GN, and ADC0OF. For this bit to take effect, ADC0DMAEN must be set to 1. 0: the ADC0 registers are written from user memory with DMA (valid for ADuCM362 only). 1: ADC0DAT is read to user memory with DMA (valid for ADuCM362 only).

- Page 48 Table 47. Bit Descriptions for ADCDMACON (Continued) Bits Name Description 0: disable ADC0 DMA accesses (valid for ADuCM362 only). 1: enable ADC0 DMA accesses (valid for ADuCM362 only). Internal Reference Control Register Address: 0x40008840, Reset: 0x0000, Name: REFCTRL Table 48. Bit Descriptions for REFCTRL...

- Page 49 Hardware Reference Manual ADuCM362/ADuCM363 ADC CIRCUIT Table 50. Bit Descriptions for IEXCDAT Bits Name Description [7:6] Reserved Reserved. [5:1] IDAT Output current. These five bits set the output current on each pin. See Table 51 for further details. IDAT0 10 μA enable.

-

Page 50: Dac

DAC OVERVIEW The ADuCM362/ADuCM363 incorporates a voltage output DAC. In normal mode, the DAC resolution is 12-bits. In interpolation mode, the DAC resolution is 16 bits with 14 effective bits. The DAC has a rail-to-rail voltage output buffer capable of driving a 5 kΩ||100 pF load. The DAC can also be configured for an NPN-transistor driver mode. - Page 51 18). Figure 18. DAC NPN Mode: Typical Operation The 4 mA to 20 mA feedback circuit is controlled by the ADuCM362/ADuCM363 12-bit DAC output. The DAC output controls the voltage across the 47 Ω resistor marked as R in the circuit. By controlling the voltage across this resistor, the feedback current to the 4 mA to 20 mA host can be accurately set.

-

Page 52: Dac Dma Operation

Hardware Reference Manual ADuCM362/ADuCM363 VR12 = (V + INT_VREF) × R2/(R1 + R2) − V R LOOP R LOOP With the loop settled, V = VR12. Because R1 = R2, = (V + INT_VREF)/2 − V = INT_VREF/2 − V... -

Page 53: Dac Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 DAC MEMORY MAPPED REGISTERS Table 52. DAC Memory Mapped Registers Address (Base Address: 0x40020000) Offset Name Description Access Default 0x0000 DACCON Control register 0x0200 0x0004 DACDAT Data register 0x00000000 DAC Control Register Address: 0x40020000, Reset: 0x200, Name: DACCON Table 53. -

Page 54: System Exceptions And Peripheral Interrupts

Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS CORTEX-M3 AND FAULT MANAGEMENT The ADuCM362/ADuCM363 integrates a Cortex-M3 processor, which supports a number of system exceptions and interrupts generated by peripherals. Table 55 lists the Cortex-M3 processor system exceptions. Table 55. System Exceptions... - Page 55 Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS Table 56. Interrupt Vector Table (Continued) Wake-Up Processor from Mode 2 or Wake-Up Processor from Position Number Vector Wake-Up Processor from Mode 1 Mode 3 Mode 4 or Mode 5 UART...

- Page 56 Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS Table 57. NVIC Registers Address Analog Devices Header File Name Description Access 0xE000E004 ICTR Shows the number of interrupt lines that the NVIC supports. 0xE000E010 STCSR SYSTICK control and status register.

-

Page 57: External Interrupt Configuration

Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS EXTERNAL INTERRUPT CONFIGURATION Eight external interrupts are implemented. These eight external interrupts can be separately configured to detect any combination of the following type of events: Edge: rising edge, falling edge, or both rising and falling edges. An interrupt signal (pulse) is sent to the NVIC upon detecting a transition ►... - Page 58 Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS Table 59. EI0CFG Register Bit Descriptions (Continued) Bits Name Description 0: External Interrupt 1 disabled 1: External Interrupt 1 enabled [6:4] IRQ1MDE External Interrupt 1 mode registers 000: rising edge 001: falling edge...

- Page 59 Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS Table 60. EI1CFG Register Bit Descriptions (Continued) Bits Name Description 011: high level 100: low level 101: falling edge (same as 001) 110: rising and falling edges (same as 010) 111: high level (same as 011)

- Page 60 Hardware Reference Manual ADuCM362/ADuCM363 SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS Table 61. EICLR Register Bit Descriptions (Continued) Bits Name Description IRQ1 External Interrupt 1 clear bit. 1: clear an internal interrupt flag. Cleared automatically by hardware. IRQ0 External Interrupt 0 clear bit.

-

Page 61: Dma Controller

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER DMA FEATURES 16 dedicated DMA channels ► DMA OVERVIEW Direct memory access (DMA) provides high speed data transfer between peripherals and memory. Data can be moved quickly by DMA without any processor actions, which keeps processor resources free for other operations. -

Page 62: Interrupts

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER INTERRUPTS An interrupt can be produced when a transfer is complete for each DMA channel. Separate interrupt enable bits are available in the NVIC for each of the DMA channels. The DMA controller fetches channel control data structures located in the SRAM memory to perform data transfers. When enabled to use DMA operation, the DMA-capable peripherals request the DMA controller for transfer. -

Page 63: Control Data Configuration

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Each register for each DMA channel is then at the offset address, as specified in Table 65, plus the value in the DMAPDBPTR register. Example Code: Define DMA Structures memset(dmaChanDesc,0x0,sizeof(dmaChanDesc)); // Setup the DMA base address pointer register. -

Page 64: Dma Transfer Types (Chnl_Cfg[2:0])

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 66. Control Data Configuration (Continued) Bits Name Description No increment. Address remains set to the value that the SRC_END_PTR memory location contains. [25:24] SRC_SIZE Size of the source data. Must always be the same as DST_SIZE. - Page 65 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER b. If the peripheral or software signals a request to the controller, then it continues at Step 1. 3. At the end of the transfer, the controller generates the corresponding DMA channel interrupt in the NVIC.

-

Page 66: Address Calculation

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 67. CHNL_CFG for Primary Data Structure in Memory Scatter-Gather Mode, CHNL_CFG[2:0] = 100 (Continued) Bits Name Description [17:14] R_POWER 0010: indicates that the DMA controller is to perform four transfers. [13: 4] N_MINUS_1 Configures the controller to perform N DMA transfers, where N is a multiple of 4. - Page 67 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Example Code to Configure Setup the DMA Controller typedef struct unsigned int cycle_ctrl unsigned int next_useburst :1; unsigned int n_minus_1 :10; unsigned int r_power unsigned int src_prot_ctrl :3; unsigned int dst_prot_ctrl :3; unsigned int src_size...

-

Page 68: Dma Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER pADI_DMA->DMAENSET = 0x100; // Select DAC channel in DMA controller pADI_TM1->LD = 0x00000088; // the min clock number are 0x17 – Timer 1 over► flow to trigger DAC write pADI_TM1->CON = 0x00000018; void DACDMAWRITE(unsigned long *pucTX_DMA, unsigned int iNumRX) DmaDesc Desc;... - Page 69 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 70. DMASTA Register Bit Descriptions (Continued) Bits Name Description [15:8] Reserved Reserved. Undefined. [7:4] STATE Current state of DMA controller state machine. Provides insight into the operation performed by the DMA at the time this register is read.

- Page 70 1: generates a DMA request for ADC1. ADC0 0: does not create a DMA request for ADC0 (valid for ADuCM362 only). 1: generates a DMA request for ADC0 (valid for ADuCM362 only). 0: does not create a DMA request for DAC DMA output.

- Page 71 1: requests are disabled for ADC0 (valid for ADuCM362 only). When written, 0: no effect. Use the DMARMSKCLR register to enable DMA requests (valid for ADuCM362 only). 1: disables peripheral associated with ADC0 from generating DMA requests (valid for ADuCM362 only).

- Page 72 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 75. DMARMSKSET Register Bit Descriptions (Continued) Bits Name Description 1: disables peripheral associated with DAC from generating DMA requests. I2CMRX When read, 0: requests are enabled for I2CMRX. 1: requests are disabled for I2CMRX.

- Page 73 1: enables peripheral associated with ADC1 to generate DMA requests. ADC0 0: no effect. Use the DMARMSKSET register to disable DMA requests (valid for ADuCM362 only). 1: enables peripheral associated with ADC0 to generate DMA requests (valid for ADuCM362 only).

- Page 74 1: enables ADC1 DMA channel. ADC0 0: no effect. Use the DMAENCLR register to disable the channel (valid for ADuCM362 only). 1: enables ADC0 DMA channel (valid for ADuCM362 only). 0: no effect. Use the DMAENCLR register to disable the channel.

- Page 75 0: no effect. Use the DMAENSET register to enable the channel. 1: disables ADC1DMA channel. ADC0 0: no effect. Use the DMAENSET register to enable the channel (valid for ADuCM362 only). 1: disables ADC0DMA channel (valid for ADuCM362 only). 0: no effect. Use the DMAENSET register to enable the channel.

- Page 76 1: DMA ADC0 is using the alternate data structure (valid for ADuCM362 only). When written, 0: no effect. Use the DMAALTCLR register to set ADC0 to 0 (valid for ADuCM362 only). 1: selects the alternate data structure for ADC0 (valid for ADuCM362 only).

- Page 77 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 79. DMAALTSET Register Bit Descriptions (Continued) Bits Name Description 1: DMA I2CMRX is using the alternate data structure. When written, 0: no effect. Use the DMAALTCLR register to set I2CMRX to 0. 1: selects the alternate data structure for I2CMRX.

- Page 78 1: selects the primary data structure for ADC1. ADC0 0: no effect. Use the DMAALTSET register to select the alternate data structure (valid for ADuCM362 only). 1: selects the primary data structure for ADC0 (valid for ADuCM362 only). 0: no effect. Use the DMAALTSET register to select the alternate data structure.

- Page 79 1: DMA ADC0 is using a high priority level (valid for ADuCM362 only). When written, 0: no effect. Use the DMAPRICLR register to set ADC0 to the default priority level (valid for ADuCM362 only). 1: ADC0 uses the high priority level (valid for ADuCM362 only).

- Page 80 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER Table 81. DMAPRISET Register Bit Descriptions (Continued) Bits Name Description 0: DMA DAC is using the default priority level. 1: DMA DAC is using a high priority level. When written, 0: no effect. Use the DMAPRICLR register to set DAC to the default priority level.

- Page 81 1: ADC1 uses the default priority level. ADC0 0: no effect. Use the DMAPRISET register to set ADC0 to the high priority level (valid for ADuCM362 only). 1: ADC0 uses the default priority level (valid for ADuCM362 only). 0: no effect. Use the DMAPRISET register to set DAC to the high priority level.

- Page 82 Hardware Reference Manual ADuCM362/ADuCM363 DMA CONTROLLER DMA Bus Error Clear Register Address: 0x4001004C, Reset: 0x00000000, Name: DMAERRCLR Table 83. DMAERRCLR Register Bit Descriptions Bits Name Description [31:1] Reserved Reserved. ERROR Bus error status. This bit is used to read and clear the DMA bus error status. The error status is set if the controller encounters a bus error while performing a transfer.

-

Page 83: Flash Controller

FLASH CONTROLLER OVERVIEW The ADuCM362/ADuCM363 includes 256 kB of Flash/EE memory, 2 kB of information space, and a flash controller. Read and write to flash are executed by direct access. The commands supported by the flash controller are as follows: Mass erase and page erase. -

Page 84: Writing To Flash/Ee Memory

Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER Figure 20. Uppermost Page of User Memory Kernel Space The kernel space is reserved for test data and the serial downloader and is read protected. WRITING TO FLASH/EE MEMORY Flash is written directly—similarly to SRAM. To enable writes to the flash memory, user code must first set FEECON0[2] to 1. When the flash write sequence is complete, as indicated by FEESTA[3], the user code then clears FEECON0[2]. -

Page 85: Erasing Flash/Ee Memory

Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER ERASING FLASH/EE MEMORY User code can call two flash erase commands, as follows: Mass erase. This command erases the entire user flash memory. After entering the user protection key into the FEEKEY register, write the ►... -

Page 86: Flash Controller Failure Analysis Key

20. It is used to gain access to user code if the serial wire interface is locked. It is the responsibility of the user to program this key to a value. The key must be given to Analog Devices to enable access to user code. -

Page 87: Integrity Of The Kernel

Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER The user must run the CRC polynomial in user code first to generate the CRC value, and must then write this user code to the upper four bytes of the uppermost page of a block. When this operation is complete, any call of the signature feature compares this 4-byte value to the result of the signature check function. - Page 88 Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER Flash Memory Status Register Address: 40002800, Reset: 0x0000, Name: FEESTA Table 87. FEESTA Register Bit Descriptions Bits Name Description [15:7] Reserved These bits return 0 when read. SIGNERR Kernel space signature check on reset error.

- Page 89 Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER Table 88. FEECON0 Register Bit Descriptions (Continued) Bits Name Description 1: enable. Flash Memory Command Register Address: 0x40002808, Reset: 0x0000, Name: FEECMD Table 89. FEECMD Register Bit Descriptions Bits Name Description [15:4] Reserved These bits return 0 when read.

- Page 90 Returns 0x0 if read. Upper Page Address Register Address: 0x40002814, Reset: 0x0000, Name: FEEADR0H FEEADR0H is two bits wide to allow access to the information space on the ADuCM362/ADuCM363. Table 92. FEEADR0H Register Bit Descriptions Bits...

- Page 91 Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER Table 96. FEEPROH Register Bit Descriptions Bits Name Description [15:0] VALUE Write protection register. This register is read only if the write protection in flash is programmed. 0: protect a section of flash. 1: leave a flash block unprotected.

- Page 92 1: enable. SINC2 interrupt abort enabled. ADC1 ADC1 interrupt abort enable bit. 0: disable. ADC1 interrupt abort disabled. 1: enable. ADC1 interrupt abort enabled. ADC0 (ADuCM362), ADC0 interrupt abort enable bit. reserved (ADuCM363) 0: disable. ADC0 interrupt abort disabled. 1: enable. ADC0 interrupt abort enabled.

- Page 93 Hardware Reference Manual ADuCM362/ADuCM363 FLASH CONTROLLER Table 102. FEEAEN0 Register Bit Descriptions (Continued) Bits Bit Name Description Reset Access 0: disable. External Interrupt 0 abort disabled. 1: enable. External Interrupt 0 abort enabled. Timer 2 (wake-up timer) interrupt abort enable bit.

- Page 94 DMAADC1 ADC1 DMA interrupt abort enable bit. 0: disable. ADC1 DMA interrupt abort disabled. 1: enable. ADC1 DMA interrupt abort enabled. DMAADC0 (ADuCM362), ADC0 DMA interrupt abort enable bit. reserved (ADuCM363) 0: disable. ADC0 DMA interrupt abort disabled. 1: enable. ADC0 DMA interrupt abort enabled.

-

Page 95: Reset

Hardware Reference Manual ADuCM362/ADuCM363 RESET RESET FEATURES There are four types of resets: External reset ► Power-on reset ► Watchdog timeout ► Software system reset ► RESET OPERATION The software system reset is provided as part of the Cortex-M3 processor. To generate a software system reset, the application interrupt/ reset control register must be written to 0x05FA0004. - Page 96 Hardware Reference Manual ADuCM362/ADuCM363 RESET Table 107. RSTSTA/RSTCLR Register Bit Descriptions (Continued) Bits Name Description EXTRST External reset. 0: cleared by setting the corresponding bit in RSTCLR. 1: set automatically to 1 when an external reset occurs. Power-on reset. 0: cleared by setting the corresponding bit in RSTCLR.

-

Page 97: Digital I/Os

The absolute maximum input voltage is IOVDD + 0.3 V, and the typical leakage current of the GPIOs configured as input or open circuit is 50 nA per GPIO. When the ADuCM362/ADuCM363 enters a power saving mode, the GPIO pins retain their states. Note that a driving peripheral cannot drive the pin. - Page 98 Hardware Reference Manual ADuCM362/ADuCM363 DIGITAL I/OS Figure 22. GPIO Pull-Up Resistor Value I/O Data In When configured as an input (by default), the GPIO input levels are available in GPxIN. Open-Circuit Enable Open-circuit enable disables the input paths if the pin is set as an output. To disable the input and not drive the pin, set the open circuit and drive Logic 1.

-

Page 99: Digital Port Multiplex

Hardware Reference Manual ADuCM362/ADuCM363 DIGITAL I/OS DIGITAL PORT MULTIPLEX The digital port multiplex block provides control over the GPIO functionality of specified pins because some of the pins have a choice to work as GPIO or to have other specific functions. -

Page 100: Gpio Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 DIGITAL I/OS GPIO MEMORY MAPPED REGISTERS Table 110. TGPIO Interface Memory Address Table Base (Address: 0x40006000) Offset Name Description Access Default 0x0000 GP0CON GPIO Port 0 configuration 0x0000 0x0004 GP0OEN GPIO Port 0 output enable 0x00... - Page 101 Hardware Reference Manual ADuCM362/ADuCM363 DIGITAL I/OS Table 112. GPxOEN Register Bit Descriptions (GP0OEN Address: 0x40006004, GP1OEN Address: 0x40006034, GP2OEN Address: 0x40006064) (Continued) Bits Name Description 0: disables the output on corresponding GPIO on Port x. 1: enables the output on corresponding GPIO on Port x.

- Page 102 Hardware Reference Manual ADuCM362/ADuCM363 DIGITAL I/OS GPIO Toggle Pin Register Table 119. GPxTGL Register Bit Descriptions (GP0TGL Address: 0x40006024, GP1TGL Address: 0x40006054, GP2TGL Address: 0x40006084) Bits Name Description [7:0] TGL[7:0] Toggle pin. 0: cleared by user code; has no effect.

-

Page 103: I 2 C Serial Interface

Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE C FEATURES The I C interface has the following features: Master or slave mode with 2-byte transmit and receive FIFOs ► Support for ► 7-bit and 10-bit addressing modes ► Four 7-bit device addresses or one 10-bit address and two 7-bit addresses in the slave ►... - Page 104 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 120. GPIO Multiplex GPIO Pin Configuration Mode P0.1, P2.0 P0.2, P1.4, P2.1 Addressing Modes 7-Bit Addressing The I2CID0, I2CID1, I2CID2, and I2CID3 registers contain the slave device IDs. The device compares the four I2CIDx registers to the address byte.

-

Page 105: I 2 C Operating Modes

Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Similarly, if a transaction involving a read, repeated start, and then read/write is required, write to the first master address byte register, I2CADR1, either after the state machine starts to transmit the device address or after the first RXREQ interrupt is received. When the requested receive count is reached, a repeated start is generated. - Page 106 If valid data in the Rx FIFO is overwritten by the Rx shifter, the receive overflow status bit (RXOF) is asserted (I2CMSTA[9] or I2CSSTA[4]). Automatic Clock Stretching The ADuCM362/ADuCM363 supports automatic clock stretching in both master and slave modes. It is recommended that automatic clock stretching be enabled, especially in slave mode. A timeout feature is added to ensure that the I C block never erroneously holds the SCL pin low indefinitely.

- Page 107 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Master No Acknowledge When receiving data, the master responds with a no acknowledge if its FIFO is full and an attempt is made to write another byte to the FIFO. This last byte received is not written to the FIFO and is lost.

- Page 108 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE DMA Requests Four DMA channels are required to service the I C master and slave. DMA enable bits are provided in the slave control register and in the master control register. The following is example code showing how to configure the DMA controller for the four different configurations.

- Page 109 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Example Code: I C Slave Read DMA Cycles void I2CSLAVERXDMAINIT(void) pADI_GP0->GPCON = 0x28; // Configure P0.[1:2] as I2C pins pADI_CLKCTL-> CLKCON1&= 0xFF0F; // Enable clock to I2C block pADI_I2C->I2CSCON = I2CSCON_SLV // Enable Slave mode...

- Page 110 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE pADI_GP0->GPCON = 0x28; // Configure P0.[1:2] as I2C pins pADI_CLKCTL-> CLKCON1&= 0xFF0F; // Enable clock to I2C block // Enable I2C master, IRQ on byte Received // Enable IRQ on Transmit complete, Arbitration lost, NACK received, Complete transaction (Stop detect►...

-

Page 111: I 2 C Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE // Decrement Tx FIFO status on byte full transmitted. pADI_I2C->I2CMCON = I2CMCON_MASEN + I2CMCON_IENRX + I2CMCON_IENTX + I2CMCON_IENALOST + I2CMCON_IENNACK + I2CMCON_IENCMP + 0x400; // Enable Rx DMA pADI_I2C->I2CMRXCNT = ucNumBytes; Dma_Init(); I2CMASTERDMAREAD(uxI2CRXData, ucNumBytes);... - Page 112 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE C Register Map Slave Registers Table 122. I C Interface Memory Address Table Slave Registers (Base Address: 0x40003000) Offset Name Description Access Default 0x0028 I2CSCON Slave control register. 0x0000 0x002C I2CSSTA Slave status, error, and IRQ register.

- Page 113 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 124. I2CMCON Register Bit Descriptions (Continued) Bits Name Description Reserved Reserved. Write a value of 0 to this bit. LOOPBACK Internal loopback enable. SCL and SDA out of the device are multiplexed onto their corresponding inputs. Note that it is also possible for the master to loopback a transfer to the slave as long as the device address corresponds, that is, external loopback.

- Page 114 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 125. I2CMSTA Register Bit Descriptions (Continued) Bits Name Description ALOST Arbitration lost. (Can drive an interrupt.) Set to 1 if the master loses arbitration. If IENALOST is 1 (I2CMCON [6]), an interrupt is generated when this bit asserts.

- Page 115 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 128. I2CMRXCNT Register Bit Descriptions (Continued) Bits Name Description 1: enable extended read. For example, to receive 412 bytes, write 0x100 (EXTEND = 1) to this register (I2CMRXCNT). Wait for the first byte to be received, and then check the I2CMCRXCNT register for every byte received thereafter. When I2CMCRXCNT returns to 0, 256 bytes have been received.

- Page 116 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 133. I2CSCON Register Bit Descriptions Bits Name Description Reserved Reserved bit. TXDMA Enable slave Tx DMA request. 0: disable DMA mode. 1: enable I C slave DMA requests. RXDMA Enable slave Rx DMA request.

- Page 117 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 133. I2CSCON Register Bit Descriptions (Continued) Bits Name Description 0: disable the slave, and all slave state machine flops are held in reset. 1: enable slave. C Slave Status Register Address: 0x4000302C, Reset: 0x0001, Name: I2CSSTA Table 134.

- Page 118 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Table 134. I2CSSTA Register Bit Descriptions (Continued) Bits Name Description RXREQ Receive request. (Can drive an interrupt.) Set on the falling edge of the SCL clock pulse that clocks in the last data bit of a byte.

- Page 119 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE C Slave ID Registers Table 138. I2CIDx Register Bit Descriptions (I2CID0 Address: 0x4000303C, I2CID1 Address: 0x40003040, I2CID2 Address: 0x40003044, I2CID3 Address: 0x40003048) Bits Name Description [15:8] Reserved Reserved bit. Returns 0 when read.

- Page 120 Hardware Reference Manual ADuCM362/ADuCM363 C SERIAL INTERFACE Automatic Stretch Control Register Address: 0x40003058, Reset: 0x0000, Name: I2C0ASSCL Table 141. I2C0ASSCL Register Bit Descriptions Bits Name Description [15:10] Reserved Reserved. SSRTSTA Stretch timeout status bit for slave. Asserts when slave automatic stretch mode has timed out. Cleared when this bit is read.

-

Page 121: Serial Peripheral Interfaces (Spis)

The two SPIs implemented on the ADuCM362/ADuCM363 can operate to a maximum bit rate of 8 Mbps in both master and slave mode. -

Page 122: Spi Transfer Initiation

Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) CLKCON1[2:0] and CLKDIS[0] control UCLK/DIV to SPI0. ► CLKCON1[5:3] and CLKDIS[1] control UCLK/DIV to SPI1. ► By reducing the clock rate to the SPI blocks, it is possible to reduce the power consumption of the SPI block. - Page 123 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) The SPI transfer protocol diagrams (see Figure 27 Figure 28) show the data transfer protocol for the SPI and the effects of CPHA and CPOL bits in the control register on that protocol.

-

Page 124: Spi Interrupts

Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) SPI INTERRUPTS There is one interrupt line per SPI and four sources of interrupts. SPIxSTA[0] reflects the state of the interrupt line, and SPIxSTA[7:4] reflects the state of the four sources. The SPI generates either TIRQ or RIRQ. Both interrupts cannot be enabled at the same time. The appropriate interrupt is enabled using the TIM bit, SPIxCON[6]. -

Page 125: Wire-Or'ed Mode (Wom)

Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) All interrupts are cleared either by a read of the status register or if SPIxCON[0] is deasserted. The Rx and Tx interrupts are also cleared if the relevant flush bits are asserted. Otherwise, the interrupts stay active even if the SPI is reconfigured. -

Page 126: Spi And Power-Down Modes

Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) DMA Master Receive Configuration The SPIxCNT register is available in DMA receive master mode only. It sets the number of receive bytes required by the SPI master, or the number of clocks that the master must generate. When the required number of bytes is received, no more transfers are initiated. To initiate a DMA master receive transfer, the user code completes a dummy read. - Page 127 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) Table 144. SPIxSTA Register Bit Descriptions (Continued) Bits Name Description Set to 1 when the CSx line is deasserted abruptly, even before the full byte of data was transmitted completely. This bit causes an interrupt.

- Page 128 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) Table 145. SPIxRX Register Bit Descriptions Bits Name Description [15:8] DMA_DATA_BYTE_2 Eight-bit receive buffer. These 8 bits are used only in the DMA mode, where all FIFO accesses occur as half word access.

- Page 129 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) Table 148. SPIxCON Register Bit Descriptions Bits Name Description [15:14] SPI IRQ mode bits. If TIM is set, these bits are configured when the Tx/Rx interrupts occur in a transfer. If SPI1 DMA mode is used, these bits must be 00.

- Page 130 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) Table 148. SPIxCON Register Bit Descriptions (Continued) Bits Name Description When a 0 is being transmitted on the MOSIx pin, the output driver is enabled. When a 1 is being transmitted on the MOSIx pin, the output driver is disabled and an external pull-up resister is required to pull the pin high.

- Page 131 Hardware Reference Manual ADuCM362/ADuCM363 SERIAL PERIPHERAL INTERFACES (SPIS) When ENABLE (SPIxDMA[0]) = 1, Tx (SPIxSTA[5]) and Rx (SPIxSTA[6]) interrupts are automatically disabled. However, the TXUR ► (SPIxSTA[4]) and RXOF (SPIxSTA[7]) interrupts are still available to indicate a Tx FIFO underrun and a Rx FIFO overflow, respectively.

-

Page 132: Uart Serial Interface

Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE UART FEATURES The ADuCM362/ADuCM363 integrate two complete UART serial interfaces with the following features: Industry standard, 16450 UART peripheral ► Support for DMA ► UART OVERVIEW The UART peripherals are a full duplex universal asynchronous receiver/transmitter (UART), compatible with the industry standard, 16450. The UARTs are responsible for converting data between serial and parallel formats. -

Page 133: Enable/Disable Bit

ENABLE/DISABLE BIT Before the ADuCM362/ADuCM363 enters power-down mode, it is recommended to disable the serial interfaces. A bit is provided in the UART control registers to disable the UART serial peripherals. These bits disable the clocks to the peripherals. When setting either one of these bits, care must be taken in software that no data is being transmitted or received. - Page 134 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE ble DMA mode in DMA controller pADI_DMA->DMAENSET = 0x8; // Ena► ble UART_RX_DMA Channel // UART Rx DMA interrupt sources - M360 void UARTDMAREAD(unsigned char *pucRX_DMA, unsigned int iNumRX) DmaDesc Desc; // Common configuration of all the descriptors used here Desc.ctrlCfg.bits.cycle_ctrl...

-

Page 135: Uart Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE Desc.ctrlCfg.Bits.src_prot_ctrl = 0x0; Desc.ctrlCfg.Bits.dst_prot_ctrl = 0x0; Desc.ctrlCfg.Bits.src_size = SRCSIZE_BYTE; Desc.ctrlCfg.Bits.dst_size = DSTSIZE_BYTE; // TX Primary Descriptor Desc.srcEndPtr = (unsigned int)(pucTX_DMA + iNumRX - 0x1); Desc.destEndPtr = (unsigned int)&COMTX; Desc.ctrlCfg.Bits.n_minus_1 = iNumRX - 0x1;... - Page 136 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE COMxTX This is an 8-bit register to which the user can write the data to be sent. If the ETBEI bit is set in the COMxIEN register, an interrupt is generated when COMxTX is empty.

- Page 137 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE Table 155. Interrupt Identification Table Bits[2:1], STA Bit 0, NIRQ Priority Definition Clearing Operation Not applicable No interrupt Not applicable Receive line status interrupt Read COMxLSR register Receive buffer full interrupt Read COMxRX register...

- Page 138 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE Table 157. COMxMCR Register Bit Descriptions (Continued) Bits Name Description 0: normal mode. 1: enable loopback mode. In loopback mode, the UARTx TXD is forced high. The modem signals are also directly connected to the status inputs (RTS to CTS).

- Page 139 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE Table 159. COMxMSR Register Bit Descriptions Bits Name Description Data carrier detect. Set to 1 if DCD is currently logic low. Cleared to 0 if DCD is currently logic high. Ring indicator. Set to 1 if RI is currently logic low.

- Page 140 Hardware Reference Manual ADuCM362/ADuCM363 UART SERIAL INTERFACE Table 161. Baud Rate Examples—UCLK/DIV = 16 MHz for All Examples (Continued) Baud Rates COMDIV DIVM DIVN Actual % Error 38,400 38,398.08 −0.0050% 57,600 57,605.76 +0.0100% 115,200 115,211.5 +0.0100% 230,400 230,423 +0.0100% 460,800 460,846.1...

-

Page 141: General-Purpose Timers

GENERAL-PURPOSE TIMERS GENERAL-PURPOSE TIMERS FEATURES The ADuCM362/ADuCM363 feature two identical, general-purpose, 16-bit count up/count down timers, Timer 0 and Timer 1, with the following features: Clocked from four different clock sources (can be scaled down using a prescalar of 1, 16, 256, or 32,768) ►... - Page 142 Hardware Reference Manual ADuCM362/ADuCM363 GENERAL-PURPOSE TIMERS zero scale), a timeout interrupt occurs and TxSTA[0] is set. To clear it, user code must write 1 to TxCLRI[0]. If TxCON[7] is set, the timer keeps counting and reloads when the TxCLRI register is written.

-

Page 143: Registers

External Interrupt 6 DMA done, any of the DMA channels External Interrupt 7 External Interrupt 1 Watchdog timer External Interrupt 2 Timer 1 External Interrupt 3 ADC0 (ADuCM362)/reserved (ADuCM363) PWMTRIP ADC1 PWM0 Step detection PWM1 DMA done—any of the DMA channels PWM2 Flash controller Reserved. - Page 144 Hardware Reference Manual ADuCM362/ADuCM363 GENERAL-PURPOSE TIMERS General-Purpose Timers Load Registers Address: 0x40000000, Reset: 0x0000, Name: T0LD Address: 0x40000400, Reset: 0x0000, Name: T1LD Table 167. T0LD and T1LD Register Bit Descriptions Bits Name Description [15:0] VALUE Load value, 0 by default.

- Page 145 Hardware Reference Manual ADuCM362/ADuCM363 GENERAL-PURPOSE TIMERS Table 169. T0CON and T1CON Register Bit Descriptions (Continued) Bits Name Description 00: DIV1: source clock/1. 01: DIV16: source clock/16. 10: DIV256: source clock/256. 11: DIV32768: source clock/32,768. General-Purpose Timers Clear Interrupt Registers Address: 0x4000000C, Reset: 0x0000, Name: T0CLRI Address: 0x4000040C, Reset: 0x0000, Name: T1CLRI Table 170.

- Page 146 Hardware Reference Manual ADuCM362/ADuCM363 GENERAL-PURPOSE TIMERS Table 172. T0STA and T1STA Register Bit Descriptions Bits Name Description [15:8] Reserved Reserved. Write 0 to these bits. PDOK T0CLRI/T1CLRI synchronization. Set to 1 automatically when the T0CLRI/T1CLRI value is being updated in the timer clock domain, indicating that the timer configuration is not yet valid.

-

Page 147: Wake-Up Timer Overview

Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER WAKE-UP TIMER FEATURES The wake-up timer features include the following: 32-bit counter (count down or count up) ► Four clock sources with programmable prescaler (1, 16, 256, or 32,768) ► Peripheral clock (PCLK) ►... - Page 148 Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Compare Field Registers Hardware Updated Field T2INC is a 12-bit interval register that is used to update the compare value in T2WUFAx by hardware. When a new value is written in T2INC, Bits[16:5] of the internal 32-bit compare register (T2WUFAx) are loaded with the new T2INC value. If the new compare value is less than the T2WUFD value in periodic mode or less than 0xFFFFFFFF in free running mode, this 32-bit compare register is automatically incremented with the contents of T2INC (shifted by five) each time the wake-up counter reaches the value in this compare register.

-

Page 149: Wake-Up Timer Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Interrupts/Wake-Up Signals An interrupt is generated when the counter value corresponds to any of the compare points or full scale in free running mode. The timer continues counting or is reset to 0. The wake-up timer generates five maskable interrupts. They are enabled in the T2IEN register. Interrupts can be cleared by setting the corresponding bit in the T2CLRI register. - Page 150 Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Table 175. T2VAL1 Register Bit Descriptions (T2VAL1 Address: 0x40002504) Bits Name Description [15:0] VALUE Upper 16 bits of current wake-up timer value Wake-Up Timer Control Register Address: 0x40002508, Reset: 0x0040, Name: T2CON Table 176. T2CON Register Bit Descriptions...

- Page 151 Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Wake-Up Timer Wake-Up Field Register B Address: 0x40002510, Reset: 0x1FFF, Name: T2WUFB0 Address: 0x40002514, Reset: 0x0000, Name: T2WUFB1 The T2WUFBx registers can be written to at any time, but the corresponding interrupt enable (T2IEN[1]) must be disabled. After the register is updated, the interrupt can be reenabled.

- Page 152 Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Table 184. T2IEN Register Bit Descriptions (Continued) Bits Name Description ROLL Interrupt enable bit when the counter rolls over. Only occurs in free running mode. 0: disable the rollover interrupt (default). 1: generate an interrupt when Timer 2 rolls over.

- Page 153 Hardware Reference Manual ADuCM362/ADuCM363 WAKE-UP TIMER Wake-Up Timer Clear Interrupt Register Address: 0x40002530, Reset: Not Applicable, Name: T2CLRI Table 186. T2CLRI Register Bit Descriptions Bits Name Description [15:5] Reserved Unused bit locations. ROLL Interrupt clear bit for when counter rolls over. Only occurs in free running mode.

-

Page 154: Watchdog Timer

Hardware Reference Manual ADuCM362/ADuCM363 WATCHDOG TIMER WATCHDOG TIMER FEATURES The watchdog features include the following: 16-bit count down timer, which can be used to recover from an invalid software state. ► Clocked by the 32 kHz internal oscillator (LFOSC) with a programmable prescaler (1, 16, 256, or 4096). -

Page 155: Watchdog Timer Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 WATCHDOG TIMER The interrupt or reset can be prevented by writing T3CLRI with 0xCCCC before the expiration period. A write to T3CLRI causes the watchdog timer to reload with the T3LD (or 0x1000 if in free running mode) immediately to begin a new timeout period and restart counting. If any value other than 0xCCCC is written, an interrupt or reset is generated (as selected by T3CON[1]). - Page 156 Hardware Reference Manual ADuCM362/ADuCM363 WATCHDOG TIMER Table 192. T3CON Register Bit Descriptions (Continued) Bits Name Description 11: DIV4096: source clock/4096. Timer interrupt. 0: generate a reset on a timeout (default). 1: generate an interrupt when the timer times out. This feature is provided for debug purposes and is only available in active mode.

- Page 157 Hardware Reference Manual ADuCM362/ADuCM363 WATCHDOG TIMER Table 194. T3STA Register Bit Descriptions (Continued) Bits Name Description Set to 1 when a T3 interrupt is pending. Cleared to 0 when a T3 interrupt is not pending. analog.com Rev. B | 157 of 170...

-

Page 158: Pwm

PWM OVERVIEW The ADuCM362/ADuCM363 integrate a 6-channel PWM interface. The six outputs are grouped as three pairs (0 to 2). Pair 0 and Pair 1 can be configured in standard mode or to drive an H-bridge. Pair 2 and Pair 3 can be configured in standard mode only. The PWM pairs and modes... - Page 159 Hardware Reference Manual ADuCM362/ADuCM363 Figure 35. Waveform of PWM Channel Pair in Standard Mode Note that the high-side PWM output for each channel must have a high duration period greater than or equal to the high period duration of the low-side output.

- Page 160 Hardware Reference Manual ADuCM362/ADuCM363 Table 197. Compare Register Descriptions in Standard Mode (Base Address: 0x40001000) (Continued) Pair Name Description PWM1COM0 PWM2 output goes high when the PWM timer reaches the count value stored in this register. PWM1COM1 PWM2 output goes low when the PWM timer reaches the count value stored in this register.

-

Page 161: Pwm Interrupt Generation

Hardware Reference Manual ADuCM362/ADuCM363 H-Bridge Mode In H-bridge mode, the period and duty cycle of the 4 outputs are controlled using the Pair 0 registers: PWM0COM0, PWM0COM1, PWM0COM2, and PWM0LEN. In addition, the state of the output is controlled by PWMCON0 Bit 9, Bit 5, Bit 4, and Bit 2 as summarized in Table 198. -

Page 162: Pwm Memory Mapped Registers

Hardware Reference Manual ADuCM362/ADuCM363 When the interrupt generation is enabled (PWMCON0[10]) and the counter value for Pair 2 changes from PWM2LEN to 0, it also generates the IRQPWM2 interrupt. The interrupt is cleared by setting PWMCLRI[2]. In H-bridge mode, Pair 0 and Pair 1 are used in the bridge configuration and generate 1 interrupt only, IRQPWM0. While Pair 0 and Pair 1 are in H-bridge mode, Pair 2 can be used in standard mode and it generates the IRQPWM2 interrupt. - Page 163 Hardware Reference Manual ADuCM362/ADuCM363 Table 200. PWMCON0 Register Bit Descriptions (Continued) Bit Position Name Description 000: UCLK/2. 001: UCLK/4. 010: UCLK/8. 011: UCLK/16. 100: UCLK/32. 101: UCLK/64. 110: UCLK/128. 111: UCLK/256. POINV PWM polarity. Available in H-bridge mode only. 0: PWM outputs as normal.

- Page 164 Hardware Reference Manual ADuCM362/ADuCM363 Table 202. PWMCLRI Register Bit Descriptions (Continued) Bits Name Description TRIP 1: clear the latched TRIPIRQPWM interrupt. This bit always reads 0. Reserved This bit always reads 0. PWM2 1: clear the latched IRQPWM2 interrupt. This bit always reads 0.

-

Page 165: Power Supply Support Circuits

POWER SUPPLY SUPPORT CIRCUITS FEATURES Low Dropout Regulators The ADuCM362/ADuCM363 integrates an on-chip regulator (AVDD_REG-based LDO) that is driven directly from the AVDD supply to generate a 1.8 V internal supply. This regulated supply is then used as the supply voltage for the ARM Cortex-M3 and peripherals, including the precision analog circuits on chip. -

Page 166: General-Purpose Timers Memory Mapped Hardware Design Considerations

Hardware Reference Manual ADuCM362/ADuCM363 HARDWARE DESIGN CONSIDERATIONS PIN CONFIGURATION AND FUNCTION DESCRIPTIONS Figure 39. Pin Configuration Table 203. Pin Function Descriptions Pin No. Mnemonic Description RESET Reset Pin, Active Low Input. An internal pull-up is provided. P2.1/SDA/UART1DCD/UARTDCD General-Purpose Input/Output P2.1/I C Serial Data Pin/UART1 Data Carrier Detect Pin/UART Data Carrier Detect Pin. - Page 167 Hardware Reference Manual ADuCM362/ADuCM363 HARDWARE DESIGN CONSIDERATIONS Table 203. Pin Function Descriptions (Continued) Pin No. Mnemonic Description DAC Voltage Output. INT_REF Internal Reference. This pin must be connected to ground via a 470 nF decoupling capacitor. IREF Optional Reference Current Resistor Connection for the Excitation Current Sources. The reference current used for the excitation current sources is set by a low drift (5 ppm/°C) external resistor connected to this pin.

-

Page 168: Typical System Configuration

Figure 40 shows a typical ADuCM362/ADuCM363 configuration. This figure shows some of the hardware considerations. The bottom of the LFCSP package has an exposed pad that must be soldered to a metal plate on the PCB for mechanical reasons and to DGND. The metal plate of the PCB can be connected to ground. -

Page 169: Serial Wire Debug Interface

Hardware Reference Manual ADuCM362/ADuCM363 HARDWARE DESIGN CONSIDERATIONS SERIAL WIRE DEBUG INTERFACE Serial wire debug (SWD) provides a debug port for pin limited packages. SWD replaces the 5-pin JTAG port with a clock (SWDCLK) and a single bidirectional data pin (SWDIO), providing all the normal JTAG debug and test functionality. SWDIO and SWCLK are overlaid on the TMS and TCK pins on the ARM 20-pin JTAG interface. -

Page 170: Related Links

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Need help?

Do you have a question about the ADuCM362 and is the answer not in the manual?

Questions and answers