Table of Contents

Advertisement

Quick Links

SN8P1700 Series

USER'S MANUAL

General Release Specification

SN8P1702

SN8P1704

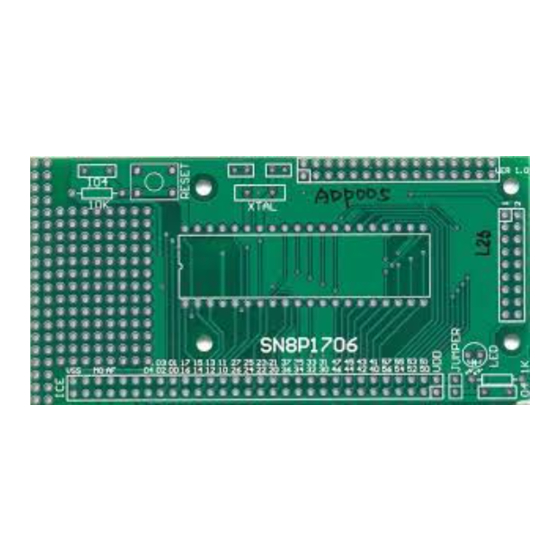

SN8P1706

SN8P1707

SN8P1708

S

O

N

i

X

S

O

N

i

X

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not

assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent

rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical

implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product

could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or

unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against

all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of

the part.

SONiX TECHNOLOGY CO., LTD

8

-

B

i

t

M

i

8

-

B

i

t

M

c

r

o

-

C

o

i

c

r

o

-

C

o

8-bit micro-controller build-in 12-bit ADC

n

t

r

o

l

l

e

r

n

t

r

o

l

l

e

r

SN8P1700

Revision 1.93

Advertisement

Table of Contents

Summary of Contents for SONIX SN8P1700 Series

- Page 1 SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur.

-

Page 2: Amendent History

“b0bset FWDRST”. P180 16. Add a notice about OSCM register access cycle. P185 17. SN8P1702/SN8A1702 don’t provide “MUL, PUSH, POP” instruction. P185 18. Add a notice about OSCM register access cycle. P185 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 2... -

Page 3: Table Of Contents

DATA MEMORY (RAM) ......................31 OVERVIEW ..........................31 RAM BANK SELECTION ......................33 WORKING REGISTERS......................34 H, L REGISTERS ........................34 Y, Z REGISTERS ........................35 X REGISTERS ........................36 R REGISTERS ........................36 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 3... - Page 4 H – Working Register ......................54 R – Working Register ......................55 Z – Working Register....................... 56 Y – Working Register....................... 57 X – Working Register....................... 58 PFLAG – Working Register ..................... 59 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 4...

- Page 5 TC0C – TC0 Timer’s Counting Register .................. 92 TC1M – TC1 Timer Counter Register..................93 TC1C – TC1 Timer’s Counting Register .................. 94 TC1R – TC1 Reload Data Register ..................95 STKP – Stack Pointer Register ....................96 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 5...

- Page 6 POWER DOWN MODE......................108 SYSTEM MODE CONTROL ..................... 109 SN8P1700 SYSTEM MODE BLOCK DIAGRAM ..............109 SYSTEM MODE SWITCHING ....................110 WAKEUP TIME......................... 111 OVERVIEW ........................... 111 HARDWARE WAKEUP ......................111 TIMERS COUNTERS..................... 112 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 6...

- Page 7 INT0 (P0.0) INTERRUPT OPERATION ................137 INT1 (P0.1) INTERRUPT OPERATION ................137 INT2 (P0.2) INTERRUPT OPERATION ................138 T0 INTERRUPT OPERATION....................139 TC0 INTERRUPT OPERATION .................... 140 TC1 INTERRUPT OPERATION .................... 141 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 7...

- Page 8 I/O PORT FUNCTION TABLE ....................159 PULL-UP RESISTERS......................160 I/O PORT DATA REGISTER ....................163 8-CHANNEL ANALOG TO DIGITAL CONVERTER........... 165 OVERVIEW..........................165 ADM REGISTER........................166 ADR REGISTERS........................166 ADB REGISTERS ........................166 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 8...

- Page 9 RC Type Oscillator Circuit ..................... 176 EXTERNAL RESET CIRCUIT....................177 CODE OPTION TABLE..................178 CODING ISSUE ....................179 TEMPLATE CODE........................179 CHIP DECLARATION IN ASSEMBLER..................184 PROGRAM CHECK LIST ......................184 INSTRUCTION SET TABLE ................185 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 9...

- Page 10 SOP18 PIN ..........................188 SSOP20 PIN ..........................189 S-DIP28 PIN ..........................190 SOP28 PIN ..........................191 QFP 44 PIN..........................192 SSOP 48 PIN ..........................193 P-DIP 48 PIN ..........................194 P-DIP 40 PIN ..........................195 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 10...

-

Page 11: Product Overview

Besides, the user can choose desired oscillator configurations for the controller. There are four oscillator configurations to select for generating system clock, including High/Low Speed crystal, ceramic resonator or cost-saving RC. SN8P1700 series also includes an internal RC oscillator for slow mode controlled by programming. FEATURES SELECTION TABLE... -

Page 12: Sn8P1702 Features

SOP 18 pins / SSOP20 (MASK type only) Notice: Declare “CHIP SN8P1702” in assembler. Use @SET_PUR macro to control pull-up resister. Refer I/O chapter for detailed information Call @SET_PUR macro at least one time to avoid sleep mode fail. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 12... -

Page 13: Sn8P1704 Features

SKDIP 28 pins Notice: Declare “CHIP SN8P1704” in assembler. Use @SET_PUR macro to control pull-up resister. Refer I/O chapter for detailed information Call @SET_PUR macro at least one time to avoid sleep mode fail. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 13... - Page 14 All ROM area lookup table function (MOVC) ♦ Support hardware multiplier (MUL). Package (Chip form support) P-DIP 40 pins Notice: Declare “CHIP SN8P1706” in assembler. Use @SET_PUR macro to control pull-up resister. Refer I/O chapter for detailed information Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 14...

-

Page 15: Sn8P1707/Sn8P1708 Features

PDIP 48 pins (SN8P1708) Notice: Declare “CHIP SN8P1707” for SN8P1707 in assembler. Declare “CHIP SN8P1708” for SN8P1708 in assembler. Use @SET_PUR macro to control pull-up resister. Refer I/O chapter for detailed information Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 15... -

Page 16: System Block Diagram

TIMER & COUNTER CONTROL CONTROL TX/RX TX/RX PORT 0 PORT 0 PORT 1 PORT 1 PORT 2 PORT 2 PORT 4 PORT 4 PORT 5 PORT 5 Figure 1-1.Simplified System Block Diagram Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 16... -

Page 17: Pin Assignment

P 5 . 3 9 12 P 5 . 1 P 5 . 2 10 11 P 5 . 4 / T C 0 / P W M 0 SN8A1702AX Only MASK type support SSOP20 package Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 17... - Page 18 22 XOUT P4.4/AIN4 8 21 VSS P4.3/AIN3 9 20 P5.0/SCK P4.2/AIN2 10 19 P5.1/SI P4.1/AIN1 11 18 P5.2/SO P4.0/AIN0 12 17 P5.3/BZ1/PWM1 AVREFH 13 16 P5.4/BZ0/PWM0 VDD 14 15 DAO SN8A1704AK SN8A1704AS Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 18...

- Page 19 For OTP type (SN8P1706) compatible issue, please connect AVREFL pin of MASK type (SN8A1706A) to the analog ground of PCB. The voltage level of AVREFL pin is the valid lowest ADC input voltage. By the way, the AVREFH is the valid highest ADC input voltage. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 19...

- Page 20 For OTP type (SN8P1707) compatible issue, please connect AVREFL pin of MASK type (SN8A1707A) to the analog ground of PCB. The voltage level of AVREFL pin is the valid lowest ADC input voltage. By the way, the AVREFH is the valid highest ADC input voltage. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 20...

- Page 21 For OTP type (SN8P1708) compatible issue, please connect AVREFL pin of MASK type (SN8A1708A) to the analog ground of PCB. The voltage level of AVREFL pin is the valid lowest ADC input voltage. By the way, the AVREFH is the valid highest ADC input voltage. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 21...

-

Page 22: Pin Descriptions

Port1, 2, 4, 5 structure Port0 structure Port0 structure Latch Latch Int. bus Int. bus Int. bus Int. bus Figure 1-2. Pin Circuit Diagram Note: All of the latch output circuits are push-pull structures. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 22... -

Page 23: Address Spaces

0005H Reserved 0006H 0007H Interrupt vector 0008H User interrupt vector 0009H User program 000FH General purpose area 0010H 0011H 03FEH End of user program Reserved 03FFH Figure 2-1. ROM Address Structure (SN8P1702) Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 23... - Page 24 0005H Reserved 0006H 0007H Interrupt vector 0008H User interrupt vector 0009H User program 000FH General purpose area 0010H 0011H 0FFEH End of user program Reserved 0FFFH Figure 2-3. ROM Address Structure (SN8P1706/SN8P1707/SN8P1708) Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 24...

-

Page 25: User Reset Vector Address (0000H)

; Pop 80H ~ 87H system registers B0XCH A, ACCBUF RETI ; End of interrupt service routine START: ; The head of user program. ; User program START ; End of user program ENDP ; End of program Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 25... - Page 26 ENDP ; End of program Remark: It is easy to get the rules of SONIX program from demo programs given above. These points are as following. 1. The address 0000H is a “JMP” instruction to make the program go to general-purpose ROM area. The 0004H~0007H are reserved.

-

Page 27: General Purpose Program Memory Area

Note: Because the program counter (PC) is only 12-bit, the X register is useless in the application. Users can omit “B0MOV X, #TABLE1$H”. SONiX ICE support more larger program memory addressing capability. So make sure X register is “0” to avoid unpredicted error in loop-up table operation. - Page 28 ; If BUF = 1, data is 0x5105 ; If BUF = 2, data is 0x2012 TABLE1: 0035H ; To define a word (16 bits) data. 5105H ; “ 2012H ; “ Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 28...

-

Page 29: Jump Table Description

When carry flag occurs after executing of “ADD PCL, A”, it will not affect PCH register. Users have to check if the jump table leaps over the ROM page boundary or the listing file generated by SONIX assembly software. If the jump table leaps over the ROM page boundary (e.g. - Page 30 SN8P1700 8-bit micro-controller build-in 12-bit ADC Example: “@JMP_A” application in SONIX macro file called “MACRO3.H”. B0MOV A, BUF0 ; “BUF0” is from 0 to 4. @JMP_A ; The number of the jump table listing is five. A0POINT ; If ACC = 0, jump to A0POINT A1POINT ;...

-

Page 31: Data Memory (Ram)

BANK 0 080h 080h~0FFh of Bank 0 = To store system “ registers (128 bytes). “ System register “ “ “ End of bank 0 area 0FFh Figure 2-4. RAM Location of SN8P1702 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 31... - Page 32 End of bank 1 area Bank 1 has 128 bytes RAM. 17Fh Figure 2-6 RAM Location of SN8P1706/SN8P1707/SN8P1708 Note: The undefined locations of system register area are logic “high” after executing read instruction “MOV A, M”. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 32...

-

Page 33: Ram Bank Selection

; Operate the bank 0 special register by the b0mov instruction ; while the RAM system in the bank1. B0MOV A, P0 ; Read P0 data in the Bank 0 and store into BUF1 in the bank 1. BUF1, A Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 33... -

Page 34: Working Registers

; Clear @HL to be zero DECMS ; L – 1, if L = 0, finish the routine CLR_HL_BUF ; Not zero END_CLR: ; End of clear general purpose data memory area of bank 0 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 34... -

Page 35: Y, Z Registers

; Y – 1, if Y= 0, finish the routine CLR_YZ_BUF ; Not zero END_CLR: ; End of clear general purpose data memory area of bank 0 Note: Please consult the “LOOK-UP TABLE DESCRIPTION” about Y, Z register look-up table application. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 35... -

Page 36: Registers

Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0 Note: Please consult the “LOOK-UP TABLE DESCRIPTION” about R register look-up table application. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 36... -

Page 37: Program Flag

DC = 0: If executed arithmetic addition without occurring carry signal from low nibble or executed arithmetic subtraction with borrow signal from high nibble. ZERO FLAG Z = 1: After operation, the content of ACC is zero. Z = 0: After operation, the content of ACC is not zero. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 37... -

Page 38: Accumulator

B0XCH A, ACCBUF ; Re-load ACC RETI ; Exit interrupt service vector Notice: To save and re-load ACC data must be used “B0XCH” instruction, or the PLAGE value maybe modified by ACC. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 38... -

Page 39: Stack Operations

STKP = 1 STKP = 1 STK6L STK6L STK6L STK6H STK6H STK6H STKP = 0 STKP = 0 STKP = 0 STK7H STK7H STK7H STK7L STK7L STK7L Figure 2-7 Stack-Save and Stack-Restore Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 39... -

Page 40: Stack Registers

SnPC3 SnPC2 SnPC1 SnPC0 STKnH: Store PCH data as interrupt or call executing. The n expressed 0 ~7. STKnL: Store PCL data as interrupt or call executing. The n expressed 0 ~7. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 40... -

Page 41: Stack Operation Example

STKPB1 STKPB0 High Byte Low Byte STK7H STK7L STK6H STK6L STK5H STK5L STK4H STK4L STK3H STK3L STK2H STK2L STK1H STK1L STK0H STK0L Table 2-2. STKP, STKnH and STKnL relative of Stack-Restore Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 41... -

Page 42: Program Counter

Bit 3 Bit 2 Bit 1 Bit 0 PC11 PC10 PCL Initial value = 0000 0000 0CEH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 42... -

Page 43: One Address Skipping

; Skip next instruction, if BUF0 = 0XFFH. DECS C0STEP ; Else jump to C0STEP. C0STEP: DECMS instruction: DECMS BUF0 ; Skip next instruction, if BUF0 = 0XFFH. C0STEP ; Else jump to C0STEP. C0STEP: Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 43... -

Page 44: Multi-Address Jumping

; If ACC = 0, jump to A0POINT A1POINT ; ACC = 1, jump to A1POINT A2POINT ; ACC = 2, jump to A2POINT A3POINT ; ACC = 3, jump to A3POINT Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 44... -

Page 45: Addressing Mode

; To set Y = 15 for accessing RAM bank 15. B0MOV Z, #12H ; To set an immediate data 12H into Z register. B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location 012H ; Into ACC. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 45... -

Page 46: To Access Data In Ram Bank 0

; To set Y = 1 for accessing RAM bank 1. B0MOV Z, #12H ; To set an immediate data 12H into Z register. B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location ; 012H into ACC. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 46... -

Page 47: System Register

INTRQ INTEN OSCM TC0R TC0M TC0C TC1M TC1C TC1R STKP STK7 STK7 STK6 STK6 STK5 STK5 STK4 STK4 STK3 STK3 STK2 STK2 STK1 STK1 STK0 STK0 Table 4-2. System Register Arrangement of SN8P1704 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 47... - Page 48 All of register names had been declared in SONiX 8-bit MCU assembler. b). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code. c). It will get logic “H” data, when use instruction to check empty location.

-

Page 49: Bits Of System Register

To avoid system error, please be sure to put all the “0” as it indicates in the above table b). All of register name had been declared in SONiX 8-bit MCU assembler. c). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code. d). “b0bset”, “b0bclr”, ”bset”, ”bclr” instructions only support “R/W” registers. - Page 50 To avoid system error, please be sure to put all the “0” as it indicates in the above table b). All of register name had been declared in SONiX 8-bit MCU assembler. c). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code. d). “b0bset”, “b0bclr”, ”bset”, ”bclr” instructions only support “R/W” registers.

- Page 51 To avoid system error, please be sure to put all the “0” as it indicates in the above table b). All of register name had been declared in SONiX 8-bit MCU assembler. c). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code. d). “b0bset”, “b0bclr”, ”bset”, ”bclr” instructions only support “R/W” registers.

- Page 52 To avoid system error, please be sure to put all the “0” as it indicates in the above table b). All of register name had been declared in SONiX 8-bit MCU assembler. c). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code. d). “b0bset”, “b0bclr”, ”bset”, ”bclr” instructions only support “R/W” registers.

-

Page 53: System Register Description

Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name LBIT7 LBIT6 LBIT5 LBIT4 LBIT3 LBIT2 LBIT1 LBIT0 Read/Write Initial Value Function: 1. Working register. 2. Index pointer addressing low byte address. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 53... -

Page 54: H - Working Register

Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name HBIT7 HBIT6 HBIT5 HBIT4 HBIT3 HBIT2 HBIT1 HBIT0 Read/Write Initial Value Function: 1. Working register. 2. Index pointer addressing middle byte address. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 54... -

Page 55: R - Working Register

Bit 1 Bit 0 Bit’s Name RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0 Read/Write Initial Value Function: 1. Working register. 2. Look-up table to store high byte data after MOVC instruction executing. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 55... -

Page 56: Z - Working Register

Bit’s Name ZBIT7 ZBIT6 ZBIT5 ZBIT4 ZBIT3 ZBIT2 ZBIT1 ZBIT0 Read/Write Initial Value Function: 1. Working register. 2. Index pointer addressing low byte address. 3. Look-up table function to address low byte address. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 56... -

Page 57: Y - Working Register

Bit’s Name YBIT7 YBIT6 YBIT5 YBIT4 YBIT3 YBIT2 YBIT1 YBIT0 Read/Write Initial Value Function: 1. Working register. 2. Index pointer addressing middle byte address. 3. Look-up table function to address middle byte address. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 57... -

Page 58: Working Register

Bit’s Name XBIT7 XBIT6 XBIT5 XBIT4 XBIT3 XBIT2 XBIT1 XBIT0 Read/Write Initial Value Function: 1. Working register. 2. Index pointer addressing high byte address. 3. Look-up table function to address high byte address. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 58... -

Page 59: Pflag - Working Register

Executed arithmetic addition with occurring signal from low nibble. Executed arithmetic subtraction without borrow signal from high nibble. Zero Flag After operation, the content of ACC is not zero. After operation, the content of ACC is zero. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 59... -

Page 60: Rbank - Ram Bank Selection

Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name RBNKS0 Read/Write Initial Value Undefined Bit1~Bit7 RAM Bank Control Bit RBNKS0 RAM bank 0. RAM bank 1. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 60... -

Page 61: Dam - Dac Converter Register

Output = 1 x Idac 1111111 Output = 127 x Idac Note: Idac=I / (2 : Full-scale Output Current) The DAC need a loading resistor that the value is about 150 ohm. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 61... -

Page 62: Adm - Adc Converter Mode Register

End of ADC converting and reset ADS bit. ADC processing. Global Channel Select Bit GCHS Disable AIN (AD input) channel. Enable AIN (AD input) channel. ADC Input Channel (AIN) Selection CHS1,CHS0 AIN0. AIN1. AIN2. AIN3. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 62... -

Page 63: Adm - Adc Converter Mode Register

End of ADC converting and reset ADS bit. ADC processing. Global Channel Select Bit GCHS Disable AIN (AD input) channel. Enable AIN (AD input) channel. ADC Input Channel (AIN) Selection CHS2,CHS1,CHS0 AIN0. AIN1. AIN2. AIN3. AIN4. AIN5. AIN6. AIN7. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 63... -

Page 64: Adb - Adc Data Buffer (Bit4~Bit11)

ADB11 ADB10 ADB9 ADB8 ADB7 ADB6 ADB5 ADB4 Read/Write Initial Value Function: 1. Store 8-bit ADC data in 8-bit ADC resolution. 2. Store bit4~bit11 of 12-bit ADC data in 12-bit ADC resolution. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 64... -

Page 65: Adr - Adc Converter Register

ADC’s Resolution Select Bit ADLEN 8-bit resolution. 12-bit resolution. ADC’s Clock Source Select Bit for 2-Stage ADCKS Fosc/16 Fosc ADC Data Buffer ADB0~ADB3 xxxx Store bit0~bit3 of 12-bit ADC data in 12-bit ADC resolution. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 65... -

Page 66: Siom - Sio Transceiver Mode Register

SCKMD SIO’s Clock Source Select Bit Internal clock External clock. SIO’s Transfer Clock Edge Select Bit SEDGE Falling edge. Rising edge. SIO’s Transfer Direction Select Bit TXRX Receiver only. Transmitter/receiver full duplex. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 66... -

Page 67: Sior - Sio Clock Counter Reload Value

Function: 1. Store SIO counter reload value for transfer clock. The equation of SIOR is as following. SIOR = 256 - ( 1 / ( SCK frequency ) * SIO rate ) Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 67... -

Page 68: Siob - Sio's Data Buffer

Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name SIOB7 SIOB6 SIOB5 SIOB4 SIOB3 SIOB2 SIOB1 SIOB0 Read/Write Initial Value Function: 1. Store SIO transmitter and receiver 8-bit data. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 68... -

Page 69: P1W - Port 1 Wakeup Function Register

Bit’s Name P15W P14W P13W P12W P11W P10W Read/Write Initial Value Always write zero. Bit6,Bit7 Bit 5~Bit0 of Port 1 Wakeup Function Control Bit P15W~P10W Disable P1.5~P1.0 wakeup function. Enable P1.5~P1.0 wakeup function. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 69... -

Page 70: P1M - Port 1 Input/Output Direction Register

P14M P13M P12M P11M P10M Read/Write Initial Value Always write zero. Bit6,Bit7 Bit 5~Bit0 of Port 1 Input/Output Direction Control Bit P15M~P10M Set P1.5~P1.0 to input direction. Set P1.5~P1.0 to output direction. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 70... -

Page 71: P2M - Port 2 Input/Output Direction Register

Bit’s Name P27M P26M P25M P24M P23M P22M P21M P20M Read/Write Initial Value Bit 7~Bit0 of Port 2 Input/Output Direction Control Bit P27M~P20M Set P2.7~P2.0 to input direction. Set P2.7~P2.0 to output direction. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 71... -

Page 72: P4M - Port 4 Input/Output Direction Register

Bit’s Name P47M P46M P45M P44M P43M P42M P41M P40M Read/Write Initial Value Bit 7~Bit0 of Port 4 Input/Output Direction Control Bit P47M~P40M Set P4.7~P4.0 to input direction. Set P4.7~P4.0 to output direction. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 72... -

Page 73: P5M - Port 5 Input/Output Direction Register

Bit’s Name P57M P56M P55M P54M P53M P52M P51M P50M Read/Write Initial Value Bit 7~Bit0 of Port 5 Input/Output Direction Control Bit P57M~P50M Set P5.7~P5.0 to input direction. Set P5.7~P5.0 to output direction. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 73... -

Page 74: Intrq - Interrupt Request Flag Register

TC0IRQ P00IRQ Read/Write Initial Value Always write zero. Bit4~Bit1,Bit6,Bit7 TC0 Interrupt Request Flag TC0IRQ No interrupt Request. Occur Interrupt Request. P0.0 (INT0) Interrupt Request Flag P00IRQ No interrupt Request. Occur Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 74... -

Page 75: Intrq - Interrupt Request Flag Register

P0.2 (INT2) Interrupt Request Flag P02IRQ No interrupt Request. Occur Interrupt Request. P0.1 (INT1) Interrupt Request Flag P01IRQ No interrupt Request. Occur Interrupt Request. P0.0 (INT0) Interrupt Request Flag P00IRQ No interrupt Request. Occur Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 75... -

Page 76: Intrq - Interrupt Request Flag Register

P0.2 (INT2) Interrupt Request Flag P02IRQ No interrupt Request. Occur Interrupt Request. P0.1 (INT1) Interrupt Request Flag P01IRQ No interrupt Request. Occur Interrupt Request. P0.0 (INT0) Interrupt Request Flag P00IRQ No interrupt Request. Occur Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 76... -

Page 77: Inten - Interrupt Request Control Register

Read/Write Initial Value Undefined Bit4~Bit1,Bit6,Bit7 Always write zero. TC0 Interrupt Request Control Bit TC0IEN Disable interrupt Request. Enable Interrupt Request. P00 Interrupt Request Control Bit P00IEN Disable interrupt Request. Enable Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 77... -

Page 78: Inten - Interrupt Request Control Register

P02 Interrupt Request Control Bit P02IEN Disable interrupt Request. Enable Interrupt Request. P01 Interrupt Request Control Bit P01IEN Disable interrupt Request. Enable Interrupt Request. P00 Interrupt Request Control Bit P00IEN Disable interrupt Request. Enable Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 78... -

Page 79: Inten - Interrupt Request Control Register

P02 Interrupt Request Control Bit P02IEN Disable interrupt Request. Enable Interrupt Request. P01 Interrupt Request Control Bit P01IEN Disable interrupt Request. Enable Interrupt Request. P00 Interrupt Request Control Bit P00IEN Disable interrupt Request. Enable Interrupt Request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 79... -

Page 80: Oscm - Oscillator Register

System High/Low Speed Mode Select Bit CLKMD Normal mode. (dual clock). Internal low clock. (RC 16KHz, 3V) External High Oscillator Control Bit STPHX External high oscillator free run. Stop External high oscillator. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 80... -

Page 81: Tc0R - Tc0 Reload Data Register

Example : B0mov a,temp B0mov tc0r,a a,#0aah B0mov tc0r,a ; write aaH into TC0R Error Example : Incms TC0R ; the incms is a read-modify-wirte instruction. This instruction will result an error. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 81... -

Page 82: Pcl - Program Counter Low Byte Register

Address 0CEH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name Read/Write Initial Value Function: 1. Store program counter (PC) low byte data. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 82... -

Page 83: Pch - Program Counter High Byte Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit’s Name PC11 PC10 Read/Write Initial Value Function: 1. Store program counter (PC) high byte data. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 83... -

Page 84: P0 - Port 0 Data Register

Data 0. Data 1. Note: Port 0 is input only port. The P0 register is read only register. Using write instruction to write data into P0 register will occur error message as compiling. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 84... -

Page 85: P1 - Port 1 Data Register

Note: In input direction, the read instructions get P1 data from external condition and the write instructions put data into the latch buffer of P1. In output direction, the read and write instructions access P1 data through P1 latch buffer. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 85... -

Page 86: P2 - Port 2 Data Register

Note: In input direction, the read instructions get P2 data from external condition and the write instructions put data into the latch buffer of P2. In output direction, the read and write instructions access P2 data through P2 latch buffer. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 86... -

Page 87: P4 - Port 4 Data Register

Note: In input direction, the read instructions get P4 data from external condition and the write instructions put data into the latch buffer of P4. In output direction, the read and write instructions access P4 data through P4 latch buffer. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 87... -

Page 88: P5 - Port 5 Data Register

Note: In input direction, the read instructions get P5 data from external condition and the write instructions put data into the latch buffer of P5. In output direction, the read and write instructions access P5 data through P5 latch buffer. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 88... -

Page 89: T0M - T0 Basic Timer Register

T0 Timer Control Bit T0ENB Disable T0 and T0 timer stop counting. Enable T0 and T0 timer start to count. T0’s Clock Source Select Bits T0rate2~T0rate0 Fcpu/256. Fcpu/128. Fcpu/64. Fcpu/32. Fcpu/16. Fcpu/8. Fcpu/4. Fcpu/2. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 89... -

Page 90: T0C - T0 Timer's Counting Register

One step = max/256 fcpu/256 73.2 ms 286us fcpu/128 36.6 ms 143us fcpu/64 18.3 ms 71.5us fcpu/32 9.15 ms 35.8us fcpu/16 4.57ms 17.9us fcpu/8 2.28ms 8.94us fcpu/4 1.14ms 4.47us fcpu/2 0.57ms 2.23us Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 90... -

Page 91: Tc0M - Tc0 Timer Counter Register

PWM0 Output Control Bit PWM0OUT Disable PWM0 output function and enable P5.4’s I/O function. Enable PWM0 output function and disable P5.4’s I/O function. Note: The TC0OUT must be set to “0” before the PWM0OUT enable. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 91... -

Page 92: Tc0C - Tc0 Timer's Counting Register

One step = max/256 fcpu/256 73.2 ms 286us fcpu/128 36.6 ms 143us fcpu/64 18.3 ms 71.5us fcpu/32 9.15 ms 35.8us fcpu/16 4.57ms 17.9us fcpu/8 2.28ms 8.94us fcpu/4 1.14ms 4.47us fcpu/2 0.57ms 2.23us Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 92... -

Page 93: Tc1M - Tc1 Timer Counter Register

PWM1 Output Control Bit PWM1OUT Disable PWM1 output function and enable P5.3’s I/O function. Enable PWM1 output function and disable P5.3’s I/O function. Note: The TC1OUT must be set to “0” before the PWM1OUT enable. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 93... -

Page 94: Tc1C - Tc1 Timer's Counting Register

One step = max/256 fcpu/256 73.2 ms 286us fcpu/128 36.6 ms 143us fcpu/64 18.3 ms 71.5us fcpu/32 9.15 ms 35.8us fcpu/16 4.57ms 17.9us fcpu/8 2.28ms 8.94us fcpu/4 1.14ms 4.47us fcpu/2 0.57ms 2.23us Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 94... -

Page 95: Tc1R - Tc1 Reload Data Register

The equation of TC1R initial value is like TC1C as following: TC1R initial value = 256 - (TC1 interrupt interval time * input clock) Note: The TC1R is write-only register can’t be process by INCMS, DECMS instructions. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 95... -

Page 96: Stkp - Stack Pointer Register

Stack level 3. 1011 Stack level 4. 1010 Stack level 5. 1001 Stack level 6. 1000 Stack level 7. 0111 Stack level 8. Note: The stack pointer initial value is “1111b” (STKPB0~STKPB3). Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 96... -

Page 97: Hl - Index Data Buffer Register

@HL3 @HL2 @HL1 @HL0 Read/Write Initial Value Function: 1. @HL data buffer is for Indirectly addressing mode to access data. @HL content is the RAM data indexed by H, L working registers. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 97... -

Page 98: Yz - Index Data Buffer Register

@YZ3 @YZ2 @YZ1 @YZ0 Read/Write Initial Value Function: 1. @YZ data buffer is for Indirectly addressing mode to access data. @YZ content is the RAM data indexed by Y, Z working registers. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 98... -

Page 99: Power On Reset

External Reset Detect Level End of LVD Reset Internal Reset Signal End of External Reset Figure 5-1 Power on Reset Timing Diagram Notice : The working current of the LVD is about 100uA. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 99... -

Page 100: External Reset Description

Users must to be sure the VDD stable earlier than external reset (Figure 5-2) or the external reset will fail. The external reset circuit is a simple RC circuit as following. 20K ohm 0.1uF Figure 5-3. External Reset Circuit Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 100... -

Page 101: Low Voltage Detector (Lvd) Description

The LVD can protect system to work well under brownout reset. But it is a high consumptive circuit. In 3V condition, the LVD consumes about 100uA. It is a very large consumption for battery system. So the LVD supports AC system well. Notice: LVD is selected by code option. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 101... -

Page 102: Oscillators

1 : Disable -- System Default 0 : Enable 0 : Enable LXOSC. LXOSC. LXOSC. CPUM0 CPUM0 CPUM0 Figure 6-1. Clock Block Diagram HXOSC: External high-speed clock. LXOSC: Internal low-speed clock. OSG: Oscillator safe guard. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 102... -

Page 103: Oscm Register Description

CPUM0: CPU operating mode control bit. 0 = normal, 1 = sleep (power down) mode to turn off both high/low clock. Notice: The bit 7 of OSCM register must be “0”, or the system will be error. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 103... -

Page 104: External High-Speed Oscillator

SN8P1700 builds in an oscillator safe guard (OSG) to make oscillator more stable. It is a low-pass filter circuit and stops high frequency noise into system from external oscillator circuit. This function makes system to work better under AC noisy conditions. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 104... -

Page 105: System Oscillator Circuits

Note3: In RC type oscillator code option situation, the external clock’s frequency is divided by 2. Note4: The power and ground of external oscillator circuit must be connected from the micro-controller’s VDD and VSS. It is necessary to step up the performance of the whole system. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 105... -

Page 106: External Rc Oscillator Frequency Measurement

; Set P1.0 to be output mode for outputting Fcpu toggle signal. B0BSET P1.0 ; Output Fcpu toggle signal in low-speed clock mode. B0BCLR P1.0 ; Measure the Fcpu frequency by oscilloscope. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 106... -

Page 107: Internal Low-Speed Oscillator

B0BSET FCLKMD ; Switch the system clock to internal low-speed clock mode. B0BSET P1.0 ; Output Fcpu toggle signal in low-speed clock mode. B0BCLR P1.0 ; Measure the Fcpu frequency by oscilloscope. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 107... -

Page 108: System Mode Description

To set CUPM0 = 1, the system gets into power down mode. The external high-speed and low-speed oscillators are turned off. The system can be waked up by P0, P1 trigger signal. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 108... -

Page 109: System Mode Control

Inactive Watchdog timer Active Active Inactive Internal interrupt All active All active All inactive External interrupt All active All active All inactive Wakeup source P0, P1, Reset Table 6-1. Operating Mode Description Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 109... -

Page 110: System Mode Switching

; If VDD = 5V, internal RC=32KHz (typical) will delay DECMS ; 0.125ms X 81 = 10.125ms for external clock stable B0BCLR FCLKMD ; Change the system back to the normal mode Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 110... -

Page 111: Wakeup Time

P10W~P15W: Port 1 wakeup function control bits. 0 = none wakeup function, 1 = Enable each pin of Port 1 wakeup function. Note: For SN8P1702 the P1W register only obtains P10W and P11W. For SN8P1704 the P1W register only obtain P10W~P14W. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 111... -

Page 112: Timers Counters

Example: An operation of watch-dog timer is as following. To clear the watchdog timer’s counter in the top of the main routine of the program. Main: B0BSET FWDRST ; Clear the watchdog timer’s counter. CALL SUB1 CALL SUB2 MAIN Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 112... -

Page 113: Basic Timer 0 (T0)

T0ENB: T0 timer control bit. 0 = disable, 1 = enable. T0RATE2~T0RATE0: The T0 timer’s clock source select bits. 000 = fcpu/256, 001 = fcpu/128, … , 110 = fcpu/4, 111 = fcpu/2. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 113... -

Page 114: T0C Counting Register

T0C initial value = 256 - (T0 interrupt interval time * input clock) = 256 - (10ms * 3.58 * 10 / 4 / 64) = 256 - (10 * 3.58 * 10 / 4 / 64) = 116 = 74H Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 114... -

Page 115: T0 Basic Timer Operation Sequence

; Reload T0C B0MOV T0C,A ; T0 interrupt service routine EXIT_INT ; End of T0 interrupt service routine and exit interrupt vector EXIT_INT: B0XCH A, ACCBUF PUSH ; Push RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 115... -

Page 116: Timer Counter 0 (Tc0)

Arbitrary frequency output (Buzzer output): Outputs selectable clock frequencies to the BZ0 pin (P5.4). PWM function: PWM output can be generated by the PWM1OUT bit and output to PWM0OUT pin (P5.4). Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 116... -

Page 117: Tc0M Mode Register

Note: Bit3 must set to 0.. Note: The ICE S8KC do not support the PWM0OUT and TC0OUT Function. The PWM0OUT and TC0OUT must use the S8KD ICE (or later) to verify the function. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 117... -

Page 118: Tc0C Counting Register

TC0C initial value = 256 - (TC0 interrupt interval time * input clock) = 256 - (10ms * 3.58 * 10 / 4 / 64) = 256 - (10 * 3.58 * 10 / 4 / 64) = 116 = 74H Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 118... -

Page 119: Tc0R Auto-Load Register

The equation of TC0R initial value is like TC0C as following. TC0R initial value = 256 - (TC0 interrupt interval time * input clock) Note: The TC0R is write-only register can’t be process by INCMS, DECMS instructions. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 119... -

Page 120: Tc0 Timer Counter Operation Sequence

; To set TC0R auto-reload register B0BSET FTC0IEN ; To enable TC0 interrupt service B0BCLR FTC0IRQ ; To clear TC0 interrupt request B0BSET FTC0ENB ; To enable TC0 timer B0BSET ALOAD0 ; To enable TC0 auto-reload function. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 120... - Page 121 ; TC0 interrupt service routine EXIT_INT ; End of TC0 interrupt service routine and exit interrupt vector EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 121...

-

Page 122: Tc0 Clock Frequency Output (Buzzer)

; Set the auto-reload reference value B0MOV TC0C,A B0MOV TC0R,A B0BSET FTC0OUT ; Enable TC0 output to P5.4 and disable P5.4 I/O function B0BSET FALOAD0 ; Enable TC0 auto-reload function B0BSET FTC0ENB ; Enable TC0 timer Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 122... -

Page 123: Tc0Out Frequency Table

0.4195 0.6720 1.6892 0.3064 0.4223 0.6793 1.7361 0.3079 0.4252 0.6868 1.7857 0.3094 0.4281 0.6944 1.8382 0.3109 0.4310 0.7022 1.8939 Table 7-2. TC0OUT Frequency Table for Fosc = 4MHz, TC0 Rate = Fcpu/8 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 123... - Page 124 1.6779 2.6882 6.7568 1.2255 1.6892 2.7174 6.9444 1.2315 1.7007 2.7473 7.1429 1.2376 1.7123 2.7778 7.3529 1.2438 1.7241 2.8090 7.5758 Table 7-3. TC0OUT Frequency Table for Fosc = 16MHz, TC0 Rate = Fcpu/8 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 124...

-

Page 125: Timer Counter 1 (Tc1)

Arbitrary frequency output (Buzzer output): Outputs selectable clock frequencies to the BZ1 pin (P5.3). PWM function: PWM output can be generated by the PWM1OUT bit and output to PWM1OUT pin (P5.3). Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 125... -

Page 126: Tc1M Mode Register

Note: Bit3 must set to 0.. Note: The S8KC ICE do not support the PWM1OUT and TC1OUT Function. The PWM1OUT and TC1OUT must use the S8KD ICE (or later) to verify the function. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 126... -

Page 127: Tc1C Counting Register

TC1C initial value = 256 - (TC1 interrupt interval time * input clock) = 256 - (10ms * 3.58 * 10 / 4 / 64) = 256 - (10 * 3.58 * 10 / 4 / 64) = 116 = 74H Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 127... -

Page 128: Tc1R Auto-Load Register

The equation of TC1R initial value is like TC1C as following. TC1R initial value = 256 - (TC1 interrupt interval time * input clock) Note: The TC1R is write-only register can’t be process by INCMS, DECMS instructions. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 128... -

Page 129: Tc1 Timer Counter Operation Sequence

; To set TC1R auto-reload register B0BSET FTC1IEN ; To enable TC1 interrupt service B0BCLR FTC1IRQ ; To clear TC1 interrupt request B0BSET FTC1ENB ; To enable TC1 timer B0BSET ALOAD1 ; To enable TC1 auto-reload function. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 129... - Page 130 ; TC1 interrupt service routine EXIT_INT ; End of TC1 interrupt service routine and exit interrupt vector EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 130...

-

Page 131: Tc1 Clock Frequency Output (Buzzer)

; Enable TC1 output to P5.3 and disable P5.3 I/O function B0BSET FALOAD1 ; Enable TC1 auto-reload function B0BSET FTC1ENB ; Enable TC1 timer Note: The TC1OUT frequency table is as TC0OUT frequency table. Please consult TC0OUT frequency table. (Table 7-2~7-5) Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 131... -

Page 132: Pwm Function Description

TC0R/TC1R = 01H TC0R/TC1R = 01H High High TC0R/TC1R = 80H TC0R/TC1R = 80H High High High TC0R/TC1R = FFH TC0R/TC1R = FFH Figure 7-8 The Output of PWM with different TC0R/TC1R. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 132... -

Page 133: Pwm Program Description

PWM1 duty modified. It protects the PWM1 signal no glitch as PWM1 duty changing. Note3: The TC0OUT function must be set “0” when PWM0 output enable. The TC1OUT function must be set “0” when PWM1 output enable. Note4: The PWM can work with interrupt request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 133... -

Page 134: Interrupt

Figure 8-1. The 7 Interrupts of SN8P1700 Note: 1.For SN8P1702 only obtain one internal interrupt P00 and one external interrupt TC0. Note: 2.The GIE bit must enable and all interrupt operations work. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 134... -

Page 135: Inten Interrupt Enable Register

T0IRQ : T0 timer interrupt request control bit. 0 = non request, 1 = request. TC0IRQ : TC0 timer interrupt request controls bit. 0 = non request, 1 = request. TC1IRQ : TC1 timer interrupt request controls bit. 0 = non request, 1 = request. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 135... -

Page 136: Interrupt Operation Description

GIE: Global interrupt control bit. 0 = disable, 1 = enable. Example: Set global interrupt control bit (GIE). B0BSET FGIE ; Enable GIE Note: The GIE bit must enable and all interrupt operations work. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 136... -

Page 137: Int0 (P0.0) Interrupt Operation

Users need to care for the operation under multi-interrupt situation. Example: INT1 interrupt request setup. B0BSET FP01IEN ; Enable INT1 interrupt service B0BCLR FP01IRQ ; Clear INT1 interrupt request flag B0BSET FGIE ; Enable GIE Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 137... -

Page 138: Int2 (P0.2) Interrupt Operation

; P02IRQ = 0, exit interrupt vector B0BCLR FP02IRQ ; Reset P02IRQ ; INT2 interrupt service routine EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 138... -

Page 139: T0 Interrupt Operation

FT0IRQ ; Reset T0IRQ A, #74H B0MOV T0C, A ; Reset T0C. ; T0 interrupt service routine EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 139... -

Page 140: Tc0 Interrupt Operation

FTC0IRQ ; Reset TC0IRQ A, #74H B0MOV TC0C, A ; Reset TC0C. ; TC0 interrupt service routine EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 140... -

Page 141: Tc1 Interrupt Operation

FTC1IRQ ; Reset TC1IRQ A, #74H B0MOV TC1C, A ; Reset TC1C. ; TC1 interrupt service routine EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 141... -

Page 142: Sio Interrupt Operation

; SIOIRQ = 0, exit interrupt vector B0BCLR FSIOIRQ ; Reset SIOIRQ ; SIO interrupt service routine EXIT_INT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 142... -

Page 143: Multi-Interrupt Operation

IEN and IRQ flags to decide executing interrupt service routine or not. Users have to check interrupt control bit and interrupt request flag in interrupt vector. There is a simple routine as following. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 143... - Page 144 ; Jump to exit of IRQ B0BTS0 FSIOIRQ ; Check SIOIRQ INTSIO ; Jump to SIO interrupt service routine INT_EXIT: ; Pop B0XCH A, ACCBUF ; Restore ACC value. RETI ; Exit interrupt vector Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 144...

-

Page 145: Serial Input/Output Transceiver (Sio)

SIOC SIOC reset reset 8-bit binary counter 8-bit binary counter Sckmd Sckmd Sedge Sedge Senb Senb Senb Senb Auto_reload Auto_reload Srate Srate SIOR register SIOR register Figure 9-1. SIO Interface Circuit Diagram Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 145... -

Page 146: Siom Mode Register

Note 1: If SCKMD=1 for external clock, the SIO is in SLAVE mode. If SCKMD=0 for internal clock, the SIO is in MASTER mode. Note 2: Don’t set SENB and START bits in the same time. That makes the SIO function error. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 146... -

Page 147: Siob Data Buffer

Example: Setup the SIO clock to be 5KHz. Fosc = 3.58MHz. SIO’s rate = Fcpu = Fosc/4. SIOR = 256 – (1/(5KHz) * 3.58MHz/4) = 256 – (0.0002*895000) = 256 – 179 = 77 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 147... -

Page 148: Sio Master Operating Description

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A TX/RX data Figure 9-4. The Rising Edge Timing Diagram of Master Transfer and Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 148... -

Page 149: Falling Edge Transmitter/Receiver Mode

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A TX/RX data Figure 9-5. The Falling Edge Timing Diagram of Master Transfer and Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 149... -

Page 150: Rising Edge Receiver Mode

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A RX data Normal I/O Application Figure 9-6. The Rising Edge Timing Diagram of Master Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 150... -

Page 151: Falling Edge Receiver Mode

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A RX data Normal I/O Application Figure 9-7. The Falling Edge Timing Diagram of Master Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 151... -

Page 152: Sio Slave Operating Description

8-bit micro-controller build-in 12-bit ADC SIO SLAVE OPERATING DESCRIPTION Under slave-receiver situation, the SCK has four phases as following. SCK1 SCK2 SCK3 SCK4 Figure 9-8. The Four Phases SCK clock of SIO Slave Operation. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 152... -

Page 153: Rising Edge Transmitter/Receiver Mode

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A TX/RX data SCK1 TX/RX data SCK2 Figure 9-9. The Rising Edge Timing Diagram of Slave Transfer and Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 153... -

Page 154: Falling Edge Transmitter/Receiver Mode

; Wait the end of SIO operation. CHK_END B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A TX/RX data SCK3 TX/RX data SCK4 Figure 9-10. The Falling Edge Timing Diagram of Slave Transfer and Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 154... -

Page 155: Rising Edge Receiver Mode

A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A RX data SCK3 Normal I/O Application RX data SCK4 Normal I/O Application Figure 9-11. The Rising Edge Timing Diagram of Slave Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 155... -

Page 156: Falling Edge Receiver Mode

A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A RX data SCK1 Normal I/O Application RX data SCK2 Normal I/O Application Figure 9-12. The Falling Edge Timing Diagram of Slave Receiving Operation Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 156... -

Page 157: Sio Interrupt Operation Description

; Interrupt vector B0XCH A, ACCBUF PUSH B0BTS1 FSIOIRQ INT_EXIT B0MOV A,SIOB ; Save SIOB data into RXDATA buffer. RXDATA,A B0BCLR FSIOIRQ ; Clear SIO interrupt request flag. INT_EXIT: B0XCH A, ACCBUF Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 157... -

Page 158: I/O Port

Port0 structure Port0 structure Latch Latch Int. bus Int. bus Int. bus Int. bus Figure 10-1. The I/O Port Block Diagram Note : All of the latch output circuits are push-pull structures. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 158... -

Page 159: I/O Port Function Table

P5.1 P5M.1 must be set “0” SIO data input pin. General-purpose input/output function P5.2 P5M.1 must be set “1” SIO data output pin. P5.3~P5.7 General-purpose input/output function Table 10-1. I/O Function Table Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 159... -

Page 160: Pull-Up Resisters

8-bit micro-controller build-in 12-bit ADC PULL-UP RESISTERS SN8P1700 series chips built-in pull-up resisters in port 0, port 1, port4 and port 5. For MASK type compatible issues, SONIX 8-bit MCU assembler provide a @SET_PUR macro to control pull-up resisters. @SET_PUR macro only allows enable or disable pull-up resisters as a whole port. - Page 161 Input mode is with pull-up resistor controlled by setting @SET_UP macro. The output mode disables the pull-up resistors no matter pull-up resistors is set or not. The PnM registers are read/write bi-direction registers. Users can program them by bit control instructions (B0BSET, B0BCLR). Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 161...

- Page 162 ; Set all ports to be output mode. B0MOV P1M, A B0MOV P2M, A B0MOV P4M, A B0MOV P5M, A B0BCLR P1M.5 ; Set P1.5 to be input mode. B0BSET P1M.5 ; Set P1.5 to be output mode. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 162...

-

Page 163: I/O Port Data Register

Example: Write data to output port. A, #55H ; Write data 55H to Port 1, Port2, Port 4, Port 5 B0MOV P1, A B0MOV P2, A B0MOV P4, A B0MOV P5, A Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 163... - Page 164 B0BCLR P2.3 ; Set P2.3 and P5.5 to be “0”. B0BCLR P5.5 Example: Port bit test. B0BTS1 P0.0 ; Bit test 1 for P0.0 B0BTS0 P1.5 ; Bit test 0 for P1.5 Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 164...

-

Page 165: 8-Channel Analog To Digital Converter

For 12-bit resolution the conversion time is 16 steps. Note: The analog input level must be between the AVREFH and AVSS. Note: The AVREFH level must be between the AVDD and AVSS. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 165... -

Page 166: Adm Register

ADB register and the low-nibble of ADR will get full 12-bit ADC data buffer. The ADC buffer is a read-only register. In 8-bit ADC mode, the ADC data is stored in ADB register. In 12-bit ADC mode, the ADC data is stored in ADB and ADR registers. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 166... - Page 167 ADC converter routine. Then delete the LSB of ADC data and get the new resolution result. The table is as following. Resolution ADB11 ADB10 ADB9 ADB8 ADB7 ADB6 ADB5 ADB4 ADB3 ADB2 ADB1 ADB0 8-bit 9-bit 10-bit 11-bit 12-bit O = Selected, x = Delete Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 167...

-

Page 168: Adc Converting Time

; To get AIN0 input data ADC1: A,#91H B0MOV ADM,A ; To enable ADC and set AIN1 input B0BSET FADS ; To start conversion QEXADC: B0BCLR FGCHS ; To release AINx input channel Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 168... -

Page 169: Adc Circuit

Figure 11-2. The AINx and AVREFH Circuit of AD Converter Note: The capacitor between AIN and GND is a bypass capacitor. It is helpful to stable the analog signal. Users can omit it. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 169... -

Page 170: 7-Bit Digital To Analog Converter

Bit 3 Bit 2 Bit 1 Bit 0 DAENB DAB6 DAB5 DAB4 DAB3 DAB2 DAB1 DAB0 DAENB: Digital to Analog converter control bit. 0 = disable, 1 = enable. DABn: Digital input data. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 170... -

Page 171: D/A Converter Operation

Idac 2 * Idac 3 * Idac 126 * Idac 127 * Idac Table 12-1. DAB and DAO Relative Table Note: Idac = I / (2 -1) (I : Full-scale Output Current) Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 171... -

Page 172: Pcb Layout Notice

The distance between bypass capacitors and power pin of MCU should be as close as possible.. It’s useless to just put the bypass capacitors on power supply side and far away the VDD pin of MCU. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 172... -

Page 173: The Right Placement Of Bypass Capacitors In Multiple Vdd Case

Don’t set the bypass capacitors on power source terminal directly. That is useless. Some SONIX micro-controllers have multi-power pins. These micro-controllers have more than one VDD and VSS. For external circuit application, VDDs should been connected together like one VDD dot and the VSSs also should been connected together like a VSS dot. -

Page 174: General Pcb Power Layout

The PCB board separates to three areas. There is one power source into the PCB and separate three channels into each area. One area just only looks like within a single power. This way can get a good and unique power of each area. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 174... -

Page 175: External Oscillator Circuit

Don’t connect the VSS of the bypass capacitor to the power source individually. That makes the oscillator to been affected by the power ground easily. The external oscillator circuit must approach to the micro-controller as closely as possible. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 175... -

Page 176: Rc Type Oscillator Circuit

It is necessary to get a stable oscillator output. Don’t connect the VSS of the bypass capacitor to the power source individually. That makes the oscillator to been affected by the power ground easily. The external oscillator circuit must approach to the micro-controller as closely as possible. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 176... -

Page 177: External Reset Circuit

VDD and VSS pins of the micro-controller. It makes the reset status more stable. Don’t connect the VDD and VSS of the reset circuit to the power source individually. The external reset circuit must approach to the micro-controller as closely as possible. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 177... -

Page 178: Code Option Table

Turn on the OSG will improve the EMI performance. But the side effect is an increase in the working voltage. OSC. Freq.(Mhz) OSG ON (Volt) OSG OFF(Volt) Notice : The system working frequency is only warranty under 16Mhz. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 178... -

Page 179: Coding Issue

: TEMPLATE.ASM ; AUTHOR : SONiX ; PURPOSE : Template Code for SN8X17XX ; REVISION : 09/01/2002 V1.0 First issue ;******************************************************************************* ;* (c) Copyright 2002, SONiX TECHNOLOGY CO., LTD. ;******************************************************************************* CHIP SN8P1708 ; Select the CHIP ;------------------------------------------------------------------------------- Include Files ;------------------------------------------------------------------------------- .nolist ;... - Page 180 ;------------------------------------------------------------------------------- MnApp: ; Put your main program here ;----------------------------------- Jump table routine ;----------------------------------- 0x0100 ;The jump table should start from the head ;of boundary. b0mov A,Wk00 A,#3 PCL,A JmpSub0 JmpSub1 JmpSub2 ;----------------------------------- Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 180...

- Page 181 ;Modify this line for another interrupt b0bts0 FP00IRQ P00isr ;If necessary, insert another interrupt checking here IntTc0Chk: b0bts1 FTC0IEN IsrExit ;Suppose TC0 is the last interrupt which you b0bts0 FTC0IRQ ;want to check TC0isr Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 181...

- Page 182 FP00IRQ ;Process P0.0 external interrupt here IsrExit ;------------------------------------------------------------------------------- TC0 interrupt service routine ;------------------------------------------------------------------------------- TC0isr: b0bclr FTC0IRQ ;Process TC0 timer interrupt here IsrExit ;------------------------------------------------------------------------------- SysInit Initialize I/O, Timer, Interrupt, etc. ;------------------------------------------------------------------------------- SysInit: Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 182...

- Page 183 ;Select bank 1 b0mov Z,#0x7f ;Set @YZ address from 17fh ClrRAM20: ;Clear @YZ content decms ;z = z – 1 , skip next if z=0 ClrRAM20 ;Clear address 0x100 ;------------------------------------------------------------------------------- ENDP Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 183...

-

Page 184: Chip Declaration In Assembler

4. Constantly refresh important system registers and variables in RAM to avoid system crash by a high electrical fast transient noise. 5. Enable the LVD option to improve the power on reset or brown-out reset performance Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 184... -

Page 185: Instruction Set Table

Enable or disable pull-up resisters. Bit N of VAL: “0” disable port N pull-up, “1” enable port N pull-up Table 16-1. Instruction Set Table of SN8P1700 Note 1: Any instruction that read/write from 0SCM, will add an extra cycle.) Note 2: SN8P1702/SN8A1702 don’t provide “MUL, PUSH, POP” instruction. Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 185... -

Page 186: Electrical Characteristic

Supply Current Vdd= 5V Internal mode Idd2 (16KHz) Vdd= 3V Vdd= 5V Idd3 Sleep mode Vdd= 3V Voltage detector current Ivdet LVD enable operating current DAC Full-scale Output Current Vdd=5V, RL =150ohm Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 186... -

Page 187: Package Information

PACKAGE INFORMATION P-DIP18 PIN Symbols MIN. NOR. MAX. 0.210 0.015 0.125 0.130 0.135 0.880 0.900 0.920 0.300BSC. 0.245 0.250 0.255 0.115 0.130 0.150 eB 0.335 0.355 0.375 θ ° UNIT : INCH Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 187... -

Page 188: Sop18 Pin

SN8P1700 8-bit micro-controller build-in 12-bit ADC SOP18 PIN Symbols MIN. MAX. 0.093 0.104 0.004 0.012 0.447 0.463 0.291 0.299 0.394 0.419 0.016 0.050 θ ° UNIT : INCH Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 188... -

Page 189: Ssop20 Pin

8.66 8.74 5.80 6.00 6.20 3.80 3.90 4.00 0.635 BSC 25 BSC 0.25 0.42 0.50 0.40 0.635 1.27 1.00 1.05 1.10 1.50 REF 58 REF 0.10 θ ° 0° 8° 0° 8° Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 189... -

Page 190: S-Dip28 Pin

8-bit micro-controller build-in 12-bit ADC S-DIP28 PIN Symbols MIN. NOR. MAX. 0.210 0.015 0.114 0.130 0.135 1.390 1.390 1.400 0.310BSC. 0.283 0.288 0.293 0.115 0.130 0.150 e 0.330 0.350 0.370 θ ° UNIT : INCH Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 190... -

Page 191: Sop28 Pin

SN8P1700 8-bit micro-controller build-in 12-bit ADC SOP28 PIN Symbols MIN. MAX. 0.093 0.104 0.004 0.012 0.697 0.713 0.291 0.299 0.394 0.419 0.016 0.050 θ ° UNIT : INCH Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 191... -

Page 192: Qfp 44 Pin

13.400 0.390 0.394 0.398 9.900 10.000 10.100 0.512 0.520 0.528 13.000 13.200 13.400 0.390 0.394 0.398 9.900 10.000 10.100 0.029 0.035 0.037 0.730 0.880 0.930 0.031 0.800 θ° 0° 7° 0° 7° Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 192... -

Page 193: Ssop 48 Pin

15.748 15.875 16.002 0.291 0.295 0.299 7.391 7.493 7.595 0.025 0.635 0.396 0.406 0.416 10.058 10.312 10.566 0.020 0.030 0.040 0.508 0.762 1.016 0.056 1.422 0.003 0.076 θ° 0° 8° 0° 8° Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 193... -

Page 194: P-Dip 48 Pin

60.960 62.230 64.770 0.600 15.240 0.540 0.545 0.550 13.716 13.843 13.970 0.115 0.130 0.150 2.921 3.302 3.810 e B 0.630 0.650 0.067 16.002 16.510 1.702 θ° 0° 7° 15° 0° 7° 15° Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 194... -

Page 195: P-Dip 40 Pin

52.197 52.324 52.578 0.600 15.240 0.540 0.545 0.550 13.716 13.843 13.970 0.115 0.130 0.150 2.921 3.302 3.810 e B 0.630 0.650 0.067 16.002 16.510 1.702 θ° 0° 7° 15° 0° 7° 15° Revision 1.93 SONiX TECHNOLOGY CO., LTD Page 195... - Page 196 SN8P1700 8-bit micro-controller build-in 12-bit ADC SONiX MASK APPROVAL SHEET MASK SN8A170X by SN8P170X Code 1. Company (Customer) : Date : 2. MCU Part Number : Code number : 3. Filename : .SN8 Checksum : (EPROM) 4. Approved by : ICE Version (e.g.

- Page 197 3. Special issues for QTP (Quick Time Factory OTP Program) : a. Enough ROM size for QTP test code Note: In SONiX assembler software menu, click “Output .RPT” to check above item. b. Does customer’s code implement ROM code checksum? 4.

- Page 198 SONIX product could create a situation where personal injury or death may occur.

Need help?

Do you have a question about the SN8P1700 Series and is the answer not in the manual?

Questions and answers