Table of Contents

Advertisement

Quick Links

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 •

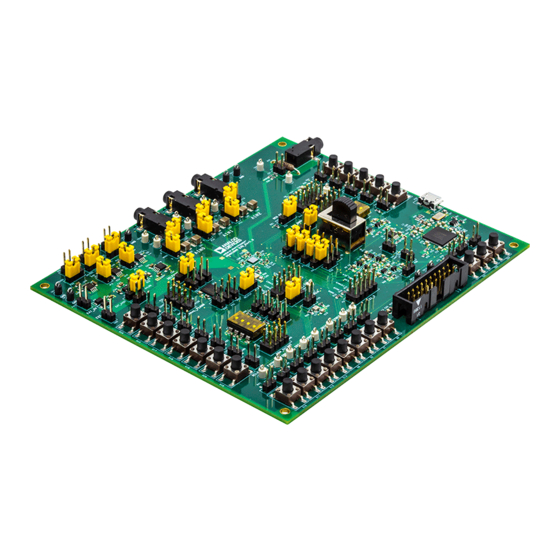

Evaluating the ADAU186x Three ADCs, One DAC, Low Power Codec with Audio DSPs

SCOPE

This user guide provides a detailed description of the ADAU186x functionality and features, includes

Note: the HPVDD pin in ADAU1860 is same as the AVDD pin in the ADAU1861. Package differences information referred to it their

relative data sheets.

DISCLAIMER

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to

change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks

and registered trademarks are the property of their respective owners.

LDO

AINP0

PGA

AINN0

AINP1

PGA

AINN1

AINP2

PGA

AINN2

DMIC_CLK/MP0

Microphone

DMIC01/MP1

Decimation

8kHz to 768kHz

DMIC23/MP2

IRQ/MP20

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

CM

Generator

SAI_0

SAI_1

ADC

ADC

Decimation

DMIC

8kHz To

3

ADC

768kHz

ASRCI

ADC

Output

EQ

FDSP

ADC

SAI_0

Digital

SAI_1

Route

8

DMIC

Route

Output

Serial Audio Port 0

IRQ

Master or Slave

Figure 1. ADAU186x Block Diagram

ADAU186x Hardware Reference Manual

www.analog.com

BCLK_0

BCLK_1

MCLK

CLK

PLL

OSC

FSYNC_0

FSYNC_1

SAI_0

Debug/Trace

SAI_1

ADC

Tensilica

FastDSP

DMIC

16

HiFi-3z

ASRCI

DSP

Instructions

TDSP

EQ

Memories

TDSP

Input

4

Asychronous

4

Equalizer

Sample Rate

ASRCI

Converter

Route

Serial Audio Port 1

I2C/SPI/UART

Master or Slave

Control Port

Rev. 0 | Page 1 of 337

ADAU1860

System

Control

LDO

HPVDD

SAI_0

SAI_1

ADC

DMIC

16

96

DAC

Route

ASRCI

FDSP

EQ

TDSP

FDSP

Output

Asychronous

4

Route

Sample Rate

Converter

QSPI

UART for

Control Port Master

Communication

UG-2257

and ADAU1861.

HPAMP

HPOUTP

HP

HPOUTN

4

ASRCO

PDM

JTAG

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Analog Devices ADAU186x

-

Page 1: Scope

Devices for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. -

Page 2: Table Of Contents

Disclaimer ..................1 Instructions ................. 26 Revision History ................9 Filter Precision ................26 Using the ADAU186x Hardware User Guide ......10 Flags and Conditional Execution ..........26 Number Notations ..............10 Input Sources ................26 Register Access Conventions ............ 10 Power and Run Control ............. - Page 3 Layout ................... 45 Delay Register ................67 Grounding ..................45 Slave Select Register ..............68 Instance table: ADAU186x ............. 46 Received Word Count Register ..........70 Register Summary: DMA ............... 47 Received Word Count Reload Register ........70 Register Details: DMA ..............48 Transmitted Word Count Register ...........

- Page 4 ADAU186x Hardware Reference Manual UG-2257 Modem Control Register ............90 Serial Port, PDM Output, and DMIC CLK Power Controls Register ..................112 Line Status Register ..............90 DSP Power Controls Register ..........113 Modem Status Register .............. 91 ASRC Power Controls Register ..........113 Scratch Buffer Register ..............

- Page 5 UG-2257 ADAU186x Hardware Reference Manual PGA Channel 1 Gain Control LSBs, Mute, Boost, Slew CM Control Register ..............142 Register ..................126 IRQ Wakeup Control Register ..........142 PGA Channel 1 Gain Control MSBs Register ...... 126 IRQ Wakeup Control Register ..........142 PGA Channel 2 Gain Control LSBs, Mute, Boost, Slew DLDO Control Register ............

- Page 6 ADAU186x Hardware Reference Manual UG-2257 Slow to Fast Interpolator Channel 7 Input Routing Register FastDSP Safeload Parameter 4 Value Register ...... 185 ..................... 168 FastDSP Safeload Parameter 4 Value Register ...... 185 Input ASRC Control, Source, and Rate Selection Register . 170 FastDSP Safeload Parameter 4 Value Register ......

- Page 7 UG-2257 ADAU186x Hardware Reference Manual Serial Port 1 Control 2 Register ..........212 General-Purpose Outputs Control Pin 0 to Pin 7 Register . 251 Serial Port 1 Control 2 Register ..........213 General-Purpose Outputs Control Pin 8 to Pin 15 Register .....................

- Page 8 ADAU186x Hardware Reference Manual UG-2257 IRQ2 Masking Register ............269 Power Mode Status, DLDO Scale Busy, CM Delay Counter Done Register ................284 IRQ2 Masking Register ............270 Memory Retention Status Register ........284 IRQ2 Masking Register ............270 ADP Memory Shutdown Status Register ......285 IRQ2 Masking Register ............

-

Page 9: Revision History

UG-2257 ADAU186x Hardware Reference Manual Multipurpose IRQ2 Status 2 Register ........298 DAC Noise Control 1 Register ..........302 Multipurpose IRQ2 Status 3 Register ........298 Register Summary: FIFOSRAM0_CONFIGURATION ..303 Multipurpose IRQ1 Status 3 Register ........298 Register Details: FIFOSRAM0_CONFIGURATION ....304 Multipurpose IRQ3 Status 1 Register ........ -

Page 10: Using The Adau186X Hardware User Guide

ADAU186x Hardware Reference Manual UG-2257 USING THE ADAU186x HARDWARE USER GUIDE NUMBER NOTATIONS Table 1. Number Notations Notation Description Bit N Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0. -

Page 11: Introdcution To The Adau186X

UG-2257 ADAU186x Hardware Reference Manual INTRODCUTION TO THE ADAU186X The ADAU186x is a low power audio codec with an optimized RAMs can be loaded with custom audio processing signal flow audio processing core, making it ideal for noise cancelling built using the Lark Studio. The values stored in the parameter applications that require high quality audio, low power, small RAM control individual signal processing blocks. -

Page 12: System Clocking And Power-Up

It’s impossible to The IRQx_POWER_ UP_COMPLETE bit indicates the power communicate with the ADAU186x when the PD pin is low. up complete event. If the IRQs are used to request an interrupt By default, out of reset, the chip is in its lowest power state after POWER_UP_ COMPLETE, the IRQs must be unmasked. -

Page 13: Dvdd Ldo Regulator

CLOCK INITIALIZATION Set CM_STARUP_OVER=1 for power saving if need. The master clock of the ADAU186x can be generated from the Configure the master clock and other frequencies in the PLL, the frequency multiplier or directly from the input source ADAU186x through the CLK_CTRLx registers and set the frequency. - Page 14 AON_CLK_RATE bits determine the clock for the always MCLK_FREQ_INDEX setting matches with the master clock. If on blocks in the ADAU186x. It recommends setting the the master clock is not in the four options, all internal sampling AON_CLK_RATE as 0.

-

Page 15: Pll

The PLL output frequency can be set between 24 MHz and 100 N/M ≤ 0.9 range to ensure correct operation of the PLL. MHz, but the ADAU186x recommends the output frequency of the PLL be set at an integer multiple of 24.576MHz like When used in fractional mode, the input to the PLL after the 24.576MHz, 49.152MHz, 73.728MHz or 98.304MHz. -

Page 16: Multichip Phase Syncronization

When transition from the PLL mode to the frequency multiplier mode, below procedures should be followed: Multiple ADAU186x devices can be ensured to remain in phase synchronization across the respective audio channels of the Configure the PLL_FM_BYPASS=1 to bypass the PLL and devices by setting the SYNC_SOURCE bits to use the same frequency multiplier. -

Page 17: Signal Routing

UG-2257 ADAU186x Hardware Reference Manual SIGNAL ROUTING Figure 5. Input and Output Signal Routing Rev. 0 | Page 17 of 337... -

Page 18: Input Signal Paths

ANALOG INPUTS error. However, the exact value of the resistors depends on The ADAU186x can accept both line level and microphone various conditions in the silicon manufacturing process and can inputs. Each of the three analog input channels can be vary by as much as ±20%. - Page 19 Precharge amplifiers are enabled by default to quickly charge The PGAx in the ADAU186x also support different power large series capacitors on the analog inputs. Precharging these mode to tradeoff the performance and power, which can be capacitors prevents pops in the audio signal.

-

Page 20: Digital Microphone Inputs

ANALOG-TO-DIGITAL CONVERTERS controls that determine the sampling ratio. These controls are The ADAU186x includes three 24-bit Σ-Δ analog-to-digital con- set via the DMICxx_FS bits. The output sample rate can be set verters (ADCs) with a selectable sample rate of 8 kHz to 768 kHz. - Page 21 UG-2257 ADAU186x Hardware Reference Manual Filtering The ADCx can work in voice wake up mode to further reduce The ADCx_DEC_ORDER bit controls the order of the power consumption. Set the ADC_VOC_WKUP bit to enable decimation filter. Low order decimation filter gets low delay the voice wake up mode.

-

Page 22: Output Signal Paths

Headphone Output Power Supply automatically transition to the normal voltage mode. If HP_LVMODE_AUTOSW_MODE=0: User need The headphone output stage of the ADAU186x can be powered to mute the DAC output before setting the by either HPVDD or HPVDD_L. HP_LVMODE_SWITCH=0. After setting the... -

Page 23: Digital-To-Analog Converters

DAC. Pop and Click Suppression PDM OUTPUTS The ADAU186x includes two channels of high performance, 1- To avoid clicks and pops, mute all analog outputs that are in use bit PDM outputs suitable for driving an external amplifier or while changing any register settings that may affect the signal other peripheral with low latency. -

Page 24: Asynchronous Sample Rate Converters

Additional filtering options are available to further customize the ASRCs to any application. Each ASRC has an The ADAU186x includes ASRCs to enable asynchronous full- ASRCx_VFILT bit that can enable a voice band filter that duplex operation of the serial ports. Four channels of ASRC are... -

Page 25: Equalizer (Eq)

UG-2257 ADAU186x Hardware Reference Manual EQUALIZER (EQ) MEMORY ADDRESS ALLOCATION The ADAU1850 integrates a MAC (Multiply Accumulate) Engine which supports following features: When FDSP_MODE in Turbo Mode, the program memory and • Single cycle double precision MAC operation parameter memory address are shown in the Table 8. When •... -

Page 26: Fastdsp Core

ADAU186x Hardware Reference Manual UG-2257 FASTDSP CORE The ADAU186x FastDSP core is optimized for ANC processing. • Output is greater than or equal to zero The processing capabilities of the core include biquad filters, • Output is less than or equal to zero limiters, expanders, multipliers, bit wise operations, clippers, •... -

Page 27: Data Memory

Parameters in banks that are actively ramping do not change during a bank switch. The ADAU186x FastDSP datapath is 28 bits (5.23 format) and It is possible to stop the linear ramp of parameters between the up to 24 dBFS is allowed. All inputs and outputs to FastDSP are two values in the previous and current bank. -

Page 28: Fastdsp Parameter Safeload

ADAU186x Hardware Reference Manual UG-2257 cycle, the control port has priority, and the write from the FDSP_SL_ADDR register, set the parameter values in the Tensilica DSP does not occur. FDSP_SL_Py_x registers, and write a 1 to the FDSP_SL_UPDATE register. After these settings and write... -

Page 29: Digital Turbo Mode

UG-2257 ADAU186x Hardware Reference Manual DIGITAL TURBO MODE In digital block, to provide more powerful digital function, TURBO MODE Turbo Mode can be enabled through setting FDSP_MODE[0] • Serial Audio Ports supporting I2S, Left justified, Right to 1. Default mode is Normal Mode. All the register description justified, or up to TDM12. -

Page 30: Tensilica Dsp

JTAG. And make sure that the voltage level from the UART JTAG is 1.8V since the ADAU186x uses 1.8V as the IO voltage. The ADAU186x has a standard UART serial interface that provides a simple mechanism to communicate with other serial... -

Page 31: Memory Mapping

UG-2257 ADAU186x Hardware Reference Manual MEMORY MAPPING The memory of the ADAU186x is shown in Figure 11. 0x 68FF FFFF QSPI Flash (16MB) An internal 4kB read only memory (ROM) contains boot code 0x 67FF FFFF Reserved and the boot ROM executes at system reset. -

Page 32: Power Saving Options

ADAU186x Hardware Reference Manual UG-2257 POWER SAVING OPTIONS The ADAU186x offers multiple options to balance the Playback Path Working Mode Control performance and power in some of the blocks. The Playback path (DAC and headphone driver) provides a mechanism to tradeoff between performance and power ADC BIAS CURRENT CONTROL consumption options for the user. - Page 33 UG-2257 ADAU186x Hardware Reference Manual Tensilica DSP Clock Speed Control Asynchronous Sample Rate Converters Low Power Modes The core and bus clock of the Tensilica DSP can be The ASRCs offer two separate, selectable low power operating programmed through the TDSP_CLK_RATE and modes.

-

Page 34: Control Port

CONTROL PORT program, or parameter data. The exact formats for specific The ADAU186x has a 4-wire SPI control port, a 2-wire I types of writing are shown in Figure 14 and Figure 15. control port and an UART control port. These three types control port share four pins. -

Page 35: Reading And Writing To Memories

C address condition, one stop condition, or a single stop condition (see Table 21). Therefore, each ADAU186x can be set to one of followed by a single start condition. A no-acknowledge four unique addresses, allowing multiple ICs to exist on the... - Page 36 Figure 17 shows the timing of a burst mode read sequence register or memory area with a 4-byte word length. where the target read words are four bytes. The ADAU186x The timing of a single word read operation is shown in increments its subaddress every four bytes because the Figure 16.

- Page 37 UG-2257 ADAU186x Hardware Reference Manual decodes the subaddress and sets the auto-increment circuit so that the address increments after the appropriate number of • S is the start bit. bytes. • P is the stop bit. • AM is acknowledge by master.

-

Page 38: Spi Control Port

UG-2257 SPI CONTROL PORT written MSB first. The ADAU186x can only be taken out of SPI mode by pulling the PD pin low or by powering down the IC. By default, the ADAU186x is in I2C mode, but the device can... -

Page 39: Uart Control Port

ID and Status (See Figure 20). For a read frame, the one byte be wrote to ADAU186x, N bytes of data, one byte of CRC, and CRC generated by the microprocessor covers the content from one byte of Tail. - Page 40 If any abnormity happens when the microprocess writes a write performed during the UART frame between Head and Tail if or read frame to ADAU186x, the microprocess can send one the data is same with the Head or Tail. The escape formats are byte of Head and then follow another byte of Head to start a shown in below.

-

Page 41: Self Boot

UG-2257 ADAU186x Hardware Reference Manual SELF BOOT There are two boot mode in the ADAU186x: self-boot mode, or operation. If the SELFBOOT pin is not used for a multipurpose non-self-boot mode. pin function, tie the pin to either IOVDD or DGND. -

Page 42: Multipurpose Pins

ADAU186x Hardware Reference Manual UG-2257 MULTIPURPOSE PINS The ADAU186x has twenty-six multipurpose (MPx) pins that MPx Pin Function Direction can be used for general purpose input, general purpose output, DMIC_CLK0_INV clock outputs, interrupts out, interrupts input and PDM DMIC_CLK1 outputs. Each pin can be individually set to either its default or Interrupts MPx setting. -

Page 43: Serial Data Ports

SERIAL DATA PORTS ignored. The serial port can operate with an arbitrary number The serial data input and output ports of the ADAU186x can be of bit clock BCLK_x transitions in each frame clock frame. set to accept or transmit data in a 2-channel format such as I2S or up to 12 channels in a time division multiplexing (TDM) When using a high bit clock rate (12.288 MHz or higher), it is... - Page 44 ADAU186x Hardware Reference Manual UG-2257 Figure 24. Stereo Modes : I S, Left Justified, Right Justified Modes, 16 Bits to 24 Bits per Channel, any number of BCLKs are allowed Figure 25. 8-Channel TDM Mode, default settings, except SPTx_SAI_MODE=1 Rev. 0 | Page 44 of 337...

-

Page 45: Applications Information

UG-2257 ADAU186x Hardware Reference Manual APPLICATIONS INFORMATION POWER SUPPLY BYPASS CAPACITORS LAYOUT Each analog and digital power supply pin should be bypassed to The HPVDD, HPVDD_L supply is for the headphone its nearest appropriate ground pin with a single 0.1 μF capacitor. -

Page 46: Instance Table: Adau186X

ADAU186x Hardware Reference Manual UG-2257 INSTANCE TABLE: ADAU186X Table 27. Instance Summary Name Module Address 0x40000000 QSPI QSPI 0x40001000 TENSILICA DSP 0x40002000 0x40004000 UART UART 0x40004800 0x40006000 0x40006800 CONTROL_REGs 0x4000C000 FFSRAM0_CFG FIFO_SRAM 0x40010000 FFSRAM1_CFG FIFO_SRAM 0x40020000 FFSRAM2_CFG FIFO_SRAM 0x40030000 DTSYNC... -

Page 47: Register Summary: Dma

UG-2257 ADAU186x Hardware Reference Manual REGISTER SUMMARY: DMA Table 28. DMA(DMA) Register Summary Address Name Description Reset Access 0x40000000 DMA_STATUS DMA Status. 0x00130000 0x40000004 DMA_CTRL DMA Configuration. 0x00000000 0x40000008 DMA_PRI_BASE_PTR DMA Channel Primary Control Data Base Pointer. 0x00000000 0x4000000C DMA_ALT_BASE_PTR DMA Channel Alternate Control Data Base Pointer. -

Page 48: Register Details: Dma

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: DMA DMA STATUS REGISTER Address: 0x40000000, Reset: 0x00130000, Name: DMA_STATUS Table 29. Bit Descriptions for DMA_STATUS Bits Bit Name Settings Description Reset Access [31:21] RESERVED Reserved. [20:16] DMA_STATUS_CHNL_NUM Number of Available DMA Channels Minus 1. With 20 channels 0x13 available, the register will read back 0x13. -

Page 49: Dma Channel Request Mask Set Register

UG-2257 ADAU186x Hardware Reference Manual Table 33. Bit Descriptions for DMA_SW_REQ Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_SW_REQ_IDX Generate Software Request. Set the appropriate bit to generate a software DMA request on the corresponding DMA channel. -

Page 50: Dma Channel Request Mask Clear Register

ADAU186x Hardware Reference Manual UG-2257 DMA CHANNEL REQUEST MASK CLEAR REGISTER Address: 0x40000024, Reset: 0x00000000, Name: DMA_REQ_MASK_CLR Table 35. Bit Descriptions for DMA_REQ_MASK_CLR Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_REQ_MASK_CLR Clear REQ_MASK_SET Bits in DMA_REQ_MASK_SET. This register enables DMA requests from peripherals by clearing the mask set in DMA_DMA_REQ_MASK_SET register. -

Page 51: Dma Channel Enable Clear Register

UG-2257 ADAU186x Hardware Reference Manual DMA CHANNEL ENABLE CLEAR REGISTER Address: 0x4000002C, Reset: 0x00000000, Name: DMA_CHNL_EN_CLR Table 37. Bit Descriptions for DMA_CHNL_EN_CLR Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_CHNL_EN_CLR Disable DMA Channels. This register allows for the disabling of DMA channels. -

Page 52: Dma Channel Priority Set Register

ADAU186x Hardware Reference Manual UG-2257 Table 39. Bit Descriptions for DMA_PRI_ALT_CLR Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_PRI_ALT_CLR Select Primary Data Structure. Set the appropriate bit to select the primary data structure for the corresponding DMA channel. -

Page 53: Dma Channel Priority Clear Register

UG-2257 ADAU186x Hardware Reference Manual DMA CHANNEL PRIORITY CLEAR REGISTER Address: 0x4000003C, Reset: 0x00000000, Name: DMA_PRIORITY_CLR Table 41. Bit Descriptions for DMA_PRIORITY_CLR Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_PRIORITY_CLR Configure Channel for Default Priority Level. The DMA_DMA_PRIORITY_CLR write-only register enables the user to configure a DMA channel to use the default priority level. -

Page 54: Dma Interrupt Enable Clear Register

ADAU186x Hardware Reference Manual UG-2257 DMA INTERRUPT ENABLE CLEAR REGISTER Address: 0x40000044, Reset: 0x00000000, Name: DMA_INT_EN_CLR The DMA_DMA_INT_EN_CLR register enables the user to configure the appropriate DMA channel to use the alternate control data structure. Reading the register returns the status of which data structure is in use for the corresponding DMA channel. Each bit of the register represents the corresponding channel number in the DMA controller. -

Page 55: Dma Per Channel Error Clear Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access [19:0] DMA_DONE_INT_CLR DMA Transfer Done Interrupt Status Clear. This register is used to R/W1C read and clear the DMA transfer done status. This status is set if the corresponding channel's DMA transfer is done.Write one to clear bits. -

Page 56: Dma Channel Bytes Swap Enable Set Register

ADAU186x Hardware Reference Manual UG-2257 DMA CHANNEL BYTES SWAP ENABLE SET REGISTER Address: 0x40000800, Reset: 0x00000000, Name: DMA_BYTE_SWAP_SET Table 47. Bit Descriptions for DMA_BYTE_SWAP_SET Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_BYTE_SWAP_SET Byte Swap Status. This register is used to configure a DMA channel to use byte swap. -

Page 57: Dma Channel Source Address Decrement Enable Set Register

UG-2257 ADAU186x Hardware Reference Manual DMA CHANNEL SOURCE ADDRESS DECREMENT ENABLE SET REGISTER Address: 0x40000810, Reset: 0x00000000, Name: DMA_SRCADR_DEC_SET Table 49. Bit Descriptions for DMA_SRCADR_DEC_SET Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_SRCADR_DEC_SET Source Address Decrement Status / Configure. The... -

Page 58: Dma Channel Destination Address Decrement Enable Set Register

ADAU186x Hardware Reference Manual UG-2257 DMA CHANNEL DESTINATION ADDRESS DECREMENT ENABLE SET REGISTER Address: 0x40000818, Reset: 0x00000000, Name: DMA_DSTADR_DEC_SET Table 51. Bit Descriptions for DMA_DSTADR_DEC_SET Bits Bit Name Settings Description Reset Access [31:20] RESERVED Reserved. [19:0] DMA_DSTADR_DEC_SET Destination Address Decrement Status. The... -

Page 59: Register Summary: Serial Peripheral Interface Qspi

UG-2257 ADAU186x Hardware Reference Manual REGISTER SUMMARY: SERIAL PERIPHERAL INTERFACE QSPI Table 54. QSPI(QSPI) Register Summary Address Name Description Reset Access 0x40001004 QSPI_CTRL Control Register. 0x00000040 0x40001008 QSPI_RX_CTRL Receive Control Register. 0x00000000 0x4000100C QSPI_TX_CTRL Transmit Control Register. 0x00000000 0x40001010 QSPI_CLK_CTRL Clock Rate Register. -

Page 60: Register Details: Serial Peripheral Interface

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: SERIAL PERIPHERAL INTERFACE CONTROL REGISTER Address: 0x40001004, Reset: 0x00000040, Name: QSPI_CTRL The QSPI_QSPI_CTRL register enables the QSPI and configures settings for operating modes, communication protocols, and buffer operations. Table 55. Bit Descriptions for QSPI_CTRL... - Page 61 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access QSPI_MULTI_IO_ORDER Start on MOSI. The QSPI_QSPI_CTRL.QSPI_MULTI_IO_ORDER bit is valid only when ?.:.:MIOM? is enabled for either DIOM or QIOM, and this bit selects the starting pin and the bit placement on pins for these modes.

- Page 62 ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access QSPI_FLOW_CTRL_CHSEL Flow Control Channel Selection. The QSPI_QSPI_CTRL.QSPI_FLOW_CTRL_CHSEL bit selects whether the QSPI applies flow control to the transmit channel (QSPI_QSPI_TX_FIFO buffer) or receive channel (QSPI_QSPI_RX_FIFO buffer). This bit is applicable only when the QSPI is a slave and flow control is enabled.

- Page 63 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access QSPI_CS_CTRL Slave Select Pin Control. The QSPI_QSPI_CTRL.QSPI_CS_CTRL bit selects whether the QSPI hardware sets the SS_QMSTn pin output value (ignoring the slave select ?.:QSPI_SLV_SEL:SSEL1? - ?.:QSPI_SLV_SEL:SSEL7? bits) or whether software control of the slave select bits set the SS_QMSTn pin output value.

-

Page 64: Receive Control Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access QSPI_CS_PROT_EN Protected Slave Select Enable. The QSPI_QSPI_CTRL.QSPI_CS_PROT_EN bit enables the SS_QMSTn pin to provide error detection input in a multi- master environment when the QSPI is in master mode. If... - Page 65 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access [13:12] QSPI_RXFF_REG_WM Receive FIFO Regular Watermark. The QSPI_QSPI_RX_CTRL.QSPI_RXFF_REG_WM bits select the receive FIFO (QSPI_QSPI_RX_FIFO) watermark level for regular data bus requests. When an urgent QSPI_QSPI_RX_FIFO watermark is enabled with ?.:.:RUWM?, the QSPI_QSPI_RX_CTRL.QSPI_RXFF_REG_WM...

-

Page 66: Transmit Control Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access RESERVED Reserved. Receive Enable. The QSPI_QSPI_RX_CTRL.QSPI_RX_EN bit enables QSPI_RX_EN QSPI receive channel operation. Disable. Enable. TRANSMIT CONTROL REGISTER Address: 0x4000100C, Reset: 0x00000000, Name: QSPI_TX_CTRL The QSPI_QSPI_TX_CTRL register enables the QSPI transmit channel, initiates transmit transfers, and configures QSPI_QSPI_TX_FIFO buffer watermark settings. -

Page 67: Clock Rate Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access [6:4] QSPI_TXD_REQ Transmit Data Request. The QSPI_QSPI_TX_CTRL.QSPI_TXD_REQ bits select transmit FIFO (QSPI_QSPI_TX_FIFO) watermark conditions that direct the QSPI to generate a transmit status interrupt. Disabled. Not full TFIFO. -

Page 68: Slave Select Register

ADAU186x Hardware Reference Manual UG-2257 Table 59. Bit Descriptions for QSPI_DLY Bits Bit Name Settings Description Reset Access [31:10] RESERVED Reserved. QSPI_EXT_LAG_EN Extended SPI Clock Lag Control. The QSPI_QSPI_DLY.QSPI_EXT_LAG_EN bit enables insertion of a 1-SPI_CLK cycle lag (extend lag) in the timing between the slave select (SS_QMSTn) assertion and first SPI Clock edge. - Page 69 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access QSPI_SSEL2 Slave Select 2 Input. The QSPI_QSPI_SLV_SEL.QSPI_SSEL2 bit state indicates the value on the related SS_QMSTn pin. Low. High. QSPI_SSEL1 Slave Select 1 Input. The QSPI_QSPI_SLV_SEL.QSPI_SSEL1 bit state indicates the value on the related SS_QMSTn pin.

-

Page 70: Received Word Count Register

ADAU186x Hardware Reference Manual UG-2257 RECEIVED WORD COUNT REGISTER Address: 0x4000101C, Reset: 0x00000000, Name: QSPI_RX_CNT The QSPI_QSPI_RX_CNT register holds a count of the number of words remaining to be received by the QSPI. To start the decrement of the word count in QSPI_QSPI_RX_CNT, enable the receive word counter (?.:QSPI_RX_CTRL:RWCEN? =1). The QSPI uses the word count to control the duration of transfers and to signal the completion of a burst of transfers with the receive finish interrupt (?.:QSPI_INT_LATCH:RF?). -

Page 71: Transmitted Word Count Reload Register

UG-2257 ADAU186x Hardware Reference Manual TRANSMITTED WORD COUNT RELOAD REGISTER Address: 0x40001028, Reset: 0x00000000, Name: QSPI_TX_RLD_CNT The QSPI_QSPI_TX_RLD_CNT register holds the transmit word count value that the QSPI loads into the QSPI_QSPI_TX_CNT register when the transfer count decrements to zero. To prevent the QSPI from reloading the counter, use zero for the reload count value. The QSPI_QSPI_TX_RLD_CNT should only be changed when the counter is disabled. -

Page 72: Interrupt Mask Clear Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access QSPI_RX_URGWM_INTMASK Receive Urgent Watermark Interrupt Mask. Disable (mask) interrupt. Enable (unmask) interrupt. RESERVED Reserved. INTERRUPT MASK CLEAR REGISTER Address: 0x40001034, Reset: 0x00000000, Name: QSPI_INT_MASK_CLR The QSPI_QSPI_INT_MASK_CLR register permits clearing individual mask bits in the QSPI_QSPI_INT_MASK register without affecting other bits in the register. -

Page 73: Status Register

UG-2257 ADAU186x Hardware Reference Manual STATUS REGISTER Address: 0x40001040, Reset: 0x00440001, Name: QSPI_STATUS The QSPI_QSPI_STATUS register indicates QSPI status including FIFO status, error conditions, and interrupt conditions. When an interrupt condition from this register is unmasked (enabled) by the corresponding bit in the QSPI_QSPI_INT_MASK register, the interrupt is latched into the corresponding bit in the QSPI_QSPI_INT_LATCH register. - Page 74 ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access [18:16] QSPI_TX_FF_STATUS SPI_TFIFO Status. The QSPI_QSPI_STATUS.QSPI_TX_FF_STATUS bits indicate the status of the QSPI_QSPI_TX_FIFO. The QSPI uses this status when evaluating transmit watermark conditions. Full TFIFO. 25% empty TFIFO.

-

Page 75: Masked Interrupt Condition Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access QSPI_TX_COL Transmit Collision Indication. The R/W1C QSPI_QSPI_STATUS.QSPI_TX_COL bit, when QSPI is a slave, indicates that the load of data into the shift register has occurred too close to the first transmitting edge of the SPI Clock. -

Page 76: Masked Interrupt Clear Register

ADAU186x Hardware Reference Manual UG-2257 Table 69. Bit Descriptions for QSPI_INT_LATCH Bits Bit Name Settings Description Reset Access [31:12] RESERVED Reserved. QSPI_TX_DONE_LATCH Transmit Finish Interrupt Latch. No interrupt. Latched interrupt. QSPI_RX_DONE_LATCH Receive Finish Interrupt Latch. No interrupt. Latched interrupt. QSPI_TX_START_LATCH Transmit Start Interrupt Latch. -

Page 77: Receive Fifo Data Register

UG-2257 ADAU186x Hardware Reference Manual Table 70. Bit Descriptions for QSPI_INT_LATCH_CLR Bits Bit Name Settings Description Reset Access [31:15] RESERVED Reserved. [14:12] QSPI_RX_FF_STATUS SPI_RFIFO Status. The QSPI_QSPI_INT_LATCH_CLR.QSPI_RX_FF_STATUS bits indicate the status of the QSPI_QSPI_RX_FIFO. The QSPI uses this status when evaluating receive watermark conditions. -

Page 78: Memory Mapped Read Header Register

ADAU186x Hardware Reference Manual UG-2257 Both masters and slaves may stop or stall transmit transfers based on FIFO status. When the transmit FIFO is empty, the QSPI master stops initiating new transfers on the QSPI if ?.:QSPI_TX_CTRL:TTI? is enabled. A slave may stall the QSPI interface when the content of the FIFO crosses the selected watermark. - Page 79 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access QSPI_MMRD_WRAP SPI Memory Wrap Indicator. The QSPI_QSPI_MMRD_HDR.QSPI_MMRD_WRAP bit must be set by software if software places a connected SPI memory device into a 8-byte, 16-byte or 32-byte wrap mode based on the ILINE and DLINE field setting of the cache configuration register address wrap mode.

-

Page 80: Spi Memory Top Address Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access 5 Bytes. 6 Bytes. 7 Bytes. QSPI_MMRD_ADR_PINS Pins Used for Address. This bit specifies the number of pins to be used for address transmission. This bit must be set consistent with expectations established by read opcode. -

Page 81: Register Summary: Tensilica Dsp (Soc)

UG-2257 ADAU186x Hardware Reference Manual REGISTER SUMMARY: TENSILICA DSP (SOC) Table 75. SOC Register Summary Address Name Description Reset Access 0x40002000 SOC_CLKEN SOC Clock Enable. 0x001F002F 0x40002004 SOC_DUMMY1 SOC Dummy Register 1. 0x00000000 0x40002008 SOC_DUMMY2 SOC Dummy Register 2. 0x00000000... -

Page 82: Register Details: Tensilica Dsp (Soc)

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: TENSILICA DSP (SOC) SOC CLOCK ENABLE REGISTER Address: 0x40002000, Reset: 0x001F002F, Name: SOC_CLKEN This register is used to enable or disable SOC sub-block clocks. Table 76. Bit Descriptions for SOC_CLKEN Bits Bit Name... -

Page 83: Soc Low Priority Level Trigger Interrupt Connection Register

UG-2257 ADAU186x Hardware Reference Manual SOC LOW PRIORITY LEVEL TRIGGER INTERRUPT CONNECTION REGISTER Address: 0x40002010, Reset: 0x0000FFFF, Name: SOC_LOPRI_LVLINT_CON In default, 'Level triggered' peripherals' interrupt sources are connected with TDSP input interrupt pin 0~14. All these interrupt are low priority interrupt from TDSP perspective. User is able to disconnect the connection by clearing these registers bits Table 80. -

Page 84: Soc Low Priority Edge Trigger Interrupt Connection Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access [27:24] TDSP_INT22_SEL TDSP Interrupt 22 Input Select 4'h0: FFSRAM0 4'h1: FFSRAM1 4'h2: FFSRAM2 4'h3: QSPI 4'h4: Data_Sync 4'h5: DMA 4'h6: AON_IRQ1 4'h7: AON_IRQ2 4'h8: AON_IRQ3 4'h9: AON_IRQ4 4'ha: MPI_IRQ1 4'hb: MPI_IRQ2 4'hc: MPI_IRQ3 4'hd: Tie Low... -

Page 85: Soc High Priority Edge Trigger Interrupt Connection Register

UG-2257 ADAU186x Hardware Reference Manual SOC HIGH PRIORITY EDGE TRIGGER INTERRUPT CONNECTION REGISTER Address: 0x4000201C, Reset: 0x000000FF, Name: SOC_HIPRI_EDGINT_CON This register is used for user to re-configure or update 'Edge Sensitive' peripherals' interrupt priority levels. In default, 'Edge Sensitive' peripherals' interrupts are connected at TDSP interrupt input pin 24~25, which are 'low priority' interrupt from TDSP perspective. TDSP input interrupt pin 26~27 are 'high priority' interrupt and are available to be connected with specific block interrupt sources. -

Page 86: Soc Memory Light-Sleep Register

ADAU186x Hardware Reference Manual UG-2257 SOC MEMORY LIGHT-SLEEP REGISTER Address: 0x40002040, Reset: 0x00000000, Name: SOC_MEM_LIGHT_SLEEP User can control memories 'LS' input pin values by writing this register. Table 86. Bit Descriptions for SOC_MEM_LIGHT_SLEEP Bits Bit Name Settings Description Reset Access... -

Page 87: Register Summary: Universal Asynchronous Receiver/Transmitter

UG-2257 ADAU186x Hardware Reference Manual REGISTER SUMMARY: UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER Table 87. UART(UART) Register Summary Address Name Description Reset Access 0x40004800 UART_RXTX Receive/transfer Buffer Register. 0x0000 0x40004804 UART_IEN Interrupt Enable. 0x0000 0x40004808 UART_IIR Interrupt ID. 0x0001 0x4000480C UART_LCR Line Control. -

Page 88: Register Details: Universal Asynchronous Receiver/Transmitter

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER RECEIVE/TRANSFER BUFFER REGISTER Address: 0x40004800, Reset: 0x0000, Name: UART_RXTX Table 88. Bit Descriptions for UART_RXTX Bits Bit Name Settings Description Reset Access [15:8] RESERVED Reserved. [7:0] UART_RBR Receive Buffer Register. -

Page 89: Line Control Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access [3:1] STAT Interrupt Status. When UART_UART_IIR.UART_NIRQ is low (active-low), this indicates an interrupt and the UART_UART_IIR.STAT bit decoding below is used. Modem Status Interrupt (Read MSR Register to Clear). -

Page 90: Modem Control Register

ADAU186x Hardware Reference Manual UG-2257 MODEM CONTROL REGISTER Address: 0x40004810, Reset: 0x0000, Name: UART_MCR Table 92. Bit Descriptions for UART_MCR Bits Bit Name Settings Description Reset Access [15:5] RESERVED Reserved. UART_LOOPBACK Loop Back Mode. In loop back mode, the SOUT is forced high. The modem signals are also directly connected to the status inputs (UART_UART_MCR.UART_RTS to UART_UART_MSR.UART_CTS,... -

Page 91: Modem Status Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access UART_PE Parity Error. If set, this bit will self clear after UART_UART_LSR is read. No Parity Error Was Detected. A Parity Error Occurred on a Received Word. UART_OE Overrun Error. -

Page 92: Scratch Buffer Register

ADAU186x Hardware Reference Manual UG-2257 SCRATCH BUFFER REGISTER Address: 0x4000481C, Reset: 0x0000, Name: UART_SCR Table 95. Bit Descriptions for UART_SCR Bits Bit Name Settings Description Reset Access [15:8] RESERVED Reserved. [7:0] UART_SCR Scratch. The scratch register is an 8-bit register used to store intermediate results. -

Page 93: Fractional Baud Rate Register

UG-2257 ADAU186x Hardware Reference Manual FRACTIONAL BAUD RATE REGISTER Address: 0x40004824, Reset: 0x0000, Name: UART_FBR Table 97. Bit Descriptions for UART_FBR Bits Bit Name Settings Description Reset Access Fractional Baud Rate Generator Enable. The generating of fractional baud rate UART_FBEN... -

Page 94: Rx Fifo Byte Count Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access FORCECLK Force UCLK on. UCLK Automatically Gated. UCLK Always Working. RESERVED Reserved. RX FIFO BYTE COUNT REGISTER Address: 0x40004834, Reset: 0x0000, Name: UART_RFC Table 101. Bit Descriptions for UART_RFC... -

Page 95: Auto Baud Status (Low) Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access 0100 Fifth Edge. 0101 Sixth Edge. 0110 Seventh Edge. 0111 Eighth Edge. 1000 Ninth Edge. RESERVED Reserved. [6:4] UART_SEC Starting Edge Count. First Edge (Always the Falling Edge of START Bit). -

Page 96: Register Summary: Gpt

ADAU186x Hardware Reference Manual UG-2257 REGISTER SUMMARY: GPT Table 107. GPT(TMR) Register Summary Address Name Description Reset Access 0x40006000 GPT_LD_VAL 16-bit Load Value Register. 0x0000 0x40006004 GPT_CURR_VAL 16-bit Current Timer Value Register. 0x0000 0x40006008 GPT_CTRL Control Register. 0x000A 0x4000600C GPT_INT_CLR Clear Interrupt Register. -

Page 97: Register Details: Gpt

UG-2257 ADAU186x Hardware Reference Manual REGISTER DETAILS: GPT 16-BIT LOAD VALUE REGISTER Address: 0x40006000, Reset: 0x0000, Name: GPT_LD_VAL Table 108. Bit Descriptions for GPT_LD_VAL Bits Bit Name Settings Description Reset Access [15:0] GPT_LD_VAL Load Value. The Up/Down counter is periodically loaded with this value if periodic mode is selected (GPT_CTRL[3]=1). -

Page 98: Clear Interrupt Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access [1:0] GPT_PRE_SCALER Prescaler. Controls the prescaler division factor applied to the timer's selected clock. If CLK source 0 or CLK Source 1 are selected then Prescaler value 0 means divide by 4, else it means divide by 1. -

Page 99: Register Summary: Watchdog Timer Register Map Wdt

UG-2257 ADAU186x Hardware Reference Manual REGISTER SUMMARY: WATCHDOG TIMER REGISTER MAP WDT Table 113. WDT(WDT) Register Summary Address Name Description Reset Access 0x40006800 Watchdog Timer Load Value. 0x1000 0x40006804 VALS Current Count Value. 0x1000 0x40006808 Watchdog Timer Control Register. 0x00C9... -

Page 100: Register Details: Watchdog Timer

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: WATCHDOG TIMER WATCHDOG TIMER LOAD VALUE REGISTER Address: 0x40006800, Reset: 0x1000, Name: LD Load value. Table 114. Bit Descriptions for LD Bits Bit Name Settings Description Reset Access [15:0] WDT_LD_VAL WDT Load Value. User programmable value. This is the value that the 0x1000 counter will start from and count down to 0. -

Page 101: Refresh Watchdog Register

UG-2257 ADAU186x Hardware Reference Manual REFRESH WATCHDOG REGISTER Address: 0x4000680C, Reset: 0x0000, Name: CLRI Clear Watchdog Table 117. Bit Descriptions for CLRI Bits Bit Name Settings Description Reset Access [15:0] WDT_CLR Refresh Register. User writes 0xCCCC to reset/reload/restart the counter or clear IRQ. -

Page 102: Register Summary: Audio Data Path

ADAU186x Hardware Reference Manual UG-2257 REGISTER SUMMARY: AUDIO DATA PATH Table 120. Audio data path Register Summary Address Name Description Reset Access 0x4000C000 VENDOR_ID ADI Vendor ID. 0x41 0x4000C001 DEVICE_ID1 Device ID. 0x60 0x4000C002 DEVICE_ID2 Device ID. 0x18 0x4000C003 REVISION Revision Code. - Page 103 UG-2257 ADAU186x Hardware Reference Manual Address Name Description Reset Access 0x4000C034 PGA2_CTRL1 PGA Channel 2 Gain Control LSB's, Mute, Boost, Slew. 0x00 0x4000C035 PGA2_CTRL2 PGA Channel 2 Gain Control MSB's. 0x00 0x4000C036 PGA_CTRL1 PGA Slew Rate and Gain Link. 0x00...

- Page 104 ADAU186x Hardware Reference Manual UG-2257 Address Name Description Reset Access 0x4000C08B FDEC_ROUTE7 Fast to Slow Decimator Channel 7 Input Routing. 0x00 0x4000C090 FINT_CTRL1 Slow to Fast Interpolator Sample Rates Channels 0/1. 0x52 0x4000C091 FINT_CTRL2 Slow to Fast Interpolator Sample Rates Channels 2/3.

- Page 105 UG-2257 ADAU186x Hardware Reference Manual Address Name Description Reset Access 0x4000C0CC FDSP_SL_P4_2 FastDSP Safeload Parameter 4 Value. 0x00 0x4000C0CD FDSP_SL_P4_3 FastDSP Safeload Parameter 4 Value. 0x00 0x4000C0CE FDSP_SL_UPDATE FastDSP Safeload Update. 0x00 0x4000C0CF FDSP_ONZ_MASK0 FastDSP Safeload Parameter 0 Value. 0x00...

- Page 106 ADAU186x Hardware Reference Manual UG-2257 Address Name Description Reset Access 0x4000C103 SPT1_ROUTE13 Serial Port 1 Output Routing Slot 13. 0x3F 0x4000C104 SPT1_ROUTE14 Serial Port 1 Output Routing Slot 14. 0x3F 0x4000C105 SPT1_ROUTE15 Serial Port 1 Output Routing Slot 15. 0x3F...

- Page 107 UG-2257 ADAU186x Hardware Reference Manual Address Name Description Reset Access 0x4000C149 ROM_BOOT_MODE_CTRL SELFBOOT Pin Controls. 0x05 0x4000C14A TCK_CTRL SELFBOOT Pin Controls. 0x15 0x4000C14B TMS_CTRL SELFBOOT Pin Controls. 0x35 0x4000C14C TDO_CTRL SELFBOOT Pin Controls. 0x05 0x4000C14D TDI_CTRL SELFBOOT Pin Controls. 0x35...

- Page 108 ADAU186x Hardware Reference Manual UG-2257 Address Name Description Reset Access 0x4000C406 PMU_STATUS1 Power Mode Status, DLDO Scale Busy, CM Delay Counter 0x00 Done. 0x4000C407 PMU_STATUS2 Memory Retention Status. 0x00 0x4000C408 PMU_STATUS3 ADP Memory Shutdown Status. 0x00 0x4000C409 PMU_STATUS4 SOC Memory Shutdown Status.

- Page 109 UG-2257 ADAU186x Hardware Reference Manual Address Name Description Reset Access 0x4000C437 GPI4 General Purpose Input Read 16-20. 0x00 0x4000C438 CTRL_PORT_MODE Control Port Mode. 0x00 0x4000CC04 DAC_NOISE_CTRL2 DAC/PLL Test Modes. 0x00 0x4000CC12 DAC_NOISE_CTRL1 DAC Noise Control1. 0x00 Rev. 0 | Page 109 of 337...

-

Page 110: Register Details: Audio Data Path

ADAU186x Hardware Reference Manual UG-2257 REGISTER DETAILS: AUDIO DATA PATH ADI VENDOR ID REGISTER Address: 0x4000C000, Reset: 0x41, Name: VENDOR_ID Table 121. Bit Descriptions for VENDOR_ID Bits Bit Name Settings Description Reset Access [7:0] VENDOR ADI Vendor ID. 0x41 DEVICE ID REGISTER Address: 0x4000C001, Reset: 0x60, Name: DEVICE_ID1 Table 122. -

Page 111: Pll And Pga Power Controls Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access ADC1_EN ADC Channel 1 Enable. ADC Channel 1 Powered Off. ADC Channel 1 Powered On. ADC0_EN ADC Channel 0 Enable. ADC Channel 0 Powered Off. ADC Channel 0 Powered On. -

Page 112: Serial Port, Pdm Output, And Dmic Clk Power Controls Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access DMIC3_EN Digital Mic Channel 3 Enable. Digital Mic Channel 3 Powered Off. Digital Mic Channel 3 Powered On. DMIC2_EN Digital Mic Channel 2 Enable. Digital Mic Channel 2 Powered Off. -

Page 113: Dsp Power Controls Register

UG-2257 ADAU186x Hardware Reference Manual DSP POWER CONTROLS REGISTER Address: 0x4000C008, Reset: 0x00, Name: DSP_PWR Table 129. Bit Descriptions for DSP_PWR Bits Bit Name Settings Description Reset Access [7:1] RESERVED Reserved. FDSP_EN FastDSP Enable. FastDSP Powered Off. FastDSP Powered On. -

Page 114: Interpolator Power Controls Register

ADAU186x Hardware Reference Manual UG-2257 INTERPOLATOR POWER CONTROLS REGISTER Address: 0x4000C00A, Reset: 0x00, Name: FINT_PWR Table 131. Bit Descriptions for FINT_PWR Bits Bit Name Settings Description Reset Access FINT7_EN Interpolation Channel 7 Enable. Interpolation Channel 7 Powered Off. Interpolation Channel 7 Powered On. -

Page 115: State Retention Controls Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FDEC2_EN Decimation Channel 2 Enable. Decimator Channel 2 Powered Off. Decimator Channel 2 Powered On. FDEC1_EN Decimation Channel 1 Enable. Decimator Channel 1 Powered Off. Decimator Channel 1 Powered On. -

Page 116: Clock Control Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access MASTER_BLOCK_EN Master block level enable. Gates block level enabling of all blocks except PLL, XTAL, FDSP, and TDSP. All blocks are disabled. All blocks that have their respective block enable set are enabled. -

Page 117: Pll Feedback Integer Divider (Lsbs) Register

UG-2257 ADAU186x Hardware Reference Manual PLL FEEDBACK INTEGER DIVIDER (LSBS) REGISTER Address: 0x4000C012, Reset: 0x04, Name: CLK_CTRL3 Table 138. Bit Descriptions for CLK_CTRL3 Bits Bit Name Settings Description Reset Access [7:0] PLL_INTEGER_DIVIDER[7:0] Feedback divider rate (integer mode). PLL FEEDBACK INTEGER DIVIDER (MSBS) REGISTER Address: 0x4000C013, Reset: 0x00, Name: CLK_CTRL4 Table 139. -

Page 118: Pll Update Register

ADAU186x Hardware Reference Manual UG-2257 PLL UPDATE REGISTER Address: 0x4000C018, Reset: 0x00, Name: CLK_CTRL9 Table 144. Bit Descriptions for CLK_CTRL9 Bits Bit Name Settings Description Reset Access [7:1] RESERVED Reserved. PLL_UPDATE Update PLL configuration. R/W1T Writing of zero will do nothing. -

Page 119: Aon And Uart_Ctrl Clock Rate Register

UG-2257 ADAU186x Hardware Reference Manual AON AND UART_CTRL CLOCK RATE REGISTER Address: 0x4000C01A, Reset: 0x00, Name: CLK_CTRL11 Table 146. Bit Descriptions for CLK_CTRL11 Bits Bit Name Settings Description Reset Access RESERVED Reserved. [6:4] UART_CTRL_CLK_RATE UART (Ctrl_Port) Clock Rate Selection. UART (Ctrl_Port) Clock Rate... -

Page 120: Adp_Clock_Enable, Low Byte Register

ADAU186x Hardware Reference Manual UG-2257 ADP_CLOCK_ENABLE, LOW BYTE REGISTER Address: 0x4000C01D, Reset: 0xFF, Name: CLK_CTRL14 Table 149. Bit Descriptions for CLK_CTRL14 Bits Bit Name Settings Description Reset Access [7:0] ADP_CLOCK_EN[7:0] ADP Clock Enable. Bit[0]:ADP_CLK_EN, ADP overall clock enable. 1'b0: 0xFF Disable;... -

Page 121: Adc Ibias Controls Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access 192kHz Sample Rate. 384kHz Sample Rate. 768kHz Sample Rate. ADC01_DEC_ORDER ADC Channels 0 and 1 Decimation filter order. Lower Order Decimation Filter : Lower Delay. Lower Order Decimation Filter : Higher Delay. -

Page 122: Adc Hpf Control Register

ADAU186x Hardware Reference Manual UG-2257 ADC HPF CONTROL REGISTER Address: 0x4000C023, Reset: 0x00, Name: ADC_CTRL4 Table 154. Bit Descriptions for ADC_CTRL4 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:4] ADC2_HPF_EN ADC Channel 2 enable high-pass filter. ADC High Pass Filter Off. -

Page 123: Analog Input Precharge Time Register

UG-2257 ADAU186x Hardware Reference Manual ANALOG INPUT PRECHARGE TIME REGISTER Address: 0x4000C025, Reset: 0x86, Name: ADC_CTRL6 Table 156. Bit Descriptions for ADC_CTRL6 Bits Bit Name Settings Description Reset Access ADC_CHOP_EN enable chopping in the feedback dac. ADC Chop Off. ADC Chop On. -

Page 124: Adc Channel Mutes Register

ADAU186x Hardware Reference Manual UG-2257 ADC CHANNEL MUTES REGISTER Address: 0x4000C027, Reset: 0x00, Name: ADC_MUTES Table 158. Bit Descriptions for ADC_MUTES Bits Bit Name Settings Description Reset Access [7:3] RESERVED Reserved. ADC2_MUTE ADC Channel 2 Mute Control. ADC Unmuted. ADC Muted. -

Page 125: Adc Channel 2 Volume Control Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access 01000001- -0.375dB to -70.875dB. 11111101 11111110 -71.25dB. 11111111 Mute. ADC CHANNEL 2 VOLUME CONTROL REGISTER Address: 0x4000C02A, Reset: 0x40, Name: ADC2_VOL Table 161. Bit Descriptions for ADC2_VOL Bits... -

Page 126: Pga Channel 0 Gain Control Msbs Register

ADAU186x Hardware Reference Manual UG-2257 PGA CHANNEL 0 GAIN CONTROL MSBS REGISTER Address: 0x4000C031, Reset: 0x00, Name: PGA0_CTRL2 Table 164. Bit Descriptions for PGA0_CTRL2 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] PGA0_GAIN[10:5] PGA Channel 0 Gain Control. -

Page 127: Pga Channel 2 Gain Control Lsbs, Mute, Boost, Slew Register

UG-2257 ADAU186x Hardware Reference Manual PGA CHANNEL 2 GAIN CONTROL LSBS, MUTE, BOOST, SLEW REGISTER Address: 0x4000C034, Reset: 0x00, Name: PGA2_CTRL1 Table 167. Bit Descriptions for PGA2_CTRL1 Bits Bit Name Settings Description Reset Access PGA2_SLEW_DIS PGA Channel 2 Gain Slew Disable. -

Page 128: Pga Rin And Power Mode Register

ADAU186x Hardware Reference Manual UG-2257 PGA RIN AND POWER MODE REGISTER Address: 0x4000C037, Reset: 0x00, Name: PGA_CTRL2 Table 170. Bit Descriptions for PGA_CTRL2 Bits Bit Name Settings Description Reset Access RESERVED Reserved. PGA2_POWER_MODE Select PGA2 Power Mode. PGA Channel 0 is in normal operation mode. -

Page 129: Dmic Channel 0 And Channel 1 Rate, Order, Mapping, And Edge Control Register

UG-2257 ADAU186x Hardware Reference Manual DMIC CHANNEL 0 AND CHANNEL 1 RATE, ORDER, MAPPING, AND EDGE CONTROL REGISTER Address: 0x4000C041, Reset: 0x01, Name: DMIC_CTRL2 Table 172. Bit Descriptions for DMIC_CTRL2 Bits Bit Name Settings Description Reset Access DMIC01_DAT_WIRE Selects DMIC0/1 Share Same Data Wire or Not. -

Page 130: Dmic Volume Options Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access 96kHz Sample Rate. 192kHz Sample Rate. 384kHz Sample Rate. 768kHz Sample Rate. DMIC VOLUME OPTIONS REGISTER Address: 0x4000C043, Reset: 0x04, Name: DMIC_CTRL4 Table 174. Bit Descriptions for DMIC_CTRL4... -

Page 131: Dmic Channel 0 Volume Control Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access DMIC1_MUTE DMIC Channel 1 Mute Control. DMIC Unmuted. DMIC Muted. DMIC0_MUTE DMIC Channel 0 Mute Control. DMIC Unmuted. DMIC Muted. DMIC CHANNEL 0 VOLUME CONTROL REGISTER Address: 0x4000C045, Reset: 0x40, Name: DMIC_VOL0 Table 176. -

Page 132: Dmic Channel 2 Volume Control Register

ADAU186x Hardware Reference Manual UG-2257 DMIC CHANNEL 2 VOLUME CONTROL REGISTER Address: 0x4000C047, Reset: 0x40, Name: DMIC_VOL2 Table 178. Bit Descriptions for DMIC_VOL2 Bits Bit Name Settings Description Reset Access [7:0] DMIC2_VOL Digital Mic Channel 2 Volume Control. 0x40 00000000 +24dB. -

Page 133: Dmic Channel 6 And Channel 7 Rate, Order, Mapping, And Edge Control Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access [4:3] DMIC45_HPF_EN DMIC Channels 4 and 5 High-Pass Filter Enable. High Pass Filter Off. High Pass Filter, Cut Off Freq. 1Hz. High Pass Filter, Cut Off Freq. 4Hz. -

Page 134: Dmic Clock Map, Dmic Clock 1 Source Pin Select Register

ADAU186x Hardware Reference Manual UG-2257 DMIC CLOCK MAP, DMIC CLOCK 1 SOURCE PIN SELECT REGISTER Address: 0x4000C04B, Reset: 0x00, Name: DMIC_CTRL7 Table 182. Bit Descriptions for DMIC_CTRL7 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:4] DMIC_CLK1_PIN_SRC DMIC Clock 1 Pin Source Select. -

Page 135: Dmic Channel 5 Volume Control Register

UG-2257 ADAU186x Hardware Reference Manual DMIC CHANNEL 5 VOLUME CONTROL REGISTER Address: 0x4000C04D, Reset: 0x40, Name: DMIC_VOL5 Table 184. Bit Descriptions for DMIC_VOL5 Bits Bit Name Settings Description Reset Access [7:0] DMIC5_VOL Digital Mic Channel 5 Volume Control. 0x40 00000000 +24dB. -

Page 136: Dac Sample Rate, Filtering, And Power Controls Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access 01000001- -0.375dB to -70.875dB. 11111101 11111110 -71.25dB. 11111111 Mute. DAC SAMPLE RATE, FILTERING, AND POWER CONTROLS REGISTER Address: 0x4000C050, Reset: 0x02, Name: DAC_CTRL1 Table 187. Bit Descriptions for DAC_CTRL1... -

Page 137: Dac Channel 0 Volume Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access DAC_VOL_ZC DAC Volume Zero Cross Control. Volume change occurs at any time. Volume change only occurs at zero crossing. DAC_HARD_VOL DAC Hard Volume. Soft Volume Ramping. Hard/Immediate Volume Change. - Page 138 ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Serial Port 1 Channel 2. Serial Port 1 Channel 3. Serial Port 1 Channel 4. Serial Port 1 Channel 5. Serial Port 1 Channel 6. Serial Port 1 Channel 7.

-

Page 139: Headphone Control Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. EQ0. FINT Channel 0. FINT Channel 1. FINT Channel 2. -

Page 140: Hp Low Voltage Auto Switch Mode, Delay, Cm Delay Register

ADAU186x Hardware Reference Manual UG-2257 HP LOW VOLTAGE AUTO SWITCH MODE, DELAY, CM DELAY REGISTER Address: 0x4000C062, Reset: 0x30, Name: HP_LVMODE_CTRL2 Table 193. Bit Descriptions for HP_LVMODE_CTRL2 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:4] HP_LVMODE_CM_DLY CM voltage ready wait time. -

Page 141: Hpldo Ctrl Register

UG-2257 ADAU186x Hardware Reference Manual HPLDO CTRL REGISTER Address: 0x4000C066, Reset: 0x00, Name: HPLDO_CTRL Table 195. Bit Descriptions for HPLDO_CTRL Bits Bit Name Settings Description Reset Access [7:4] RESERVED Reserved. [3:2] HPLDO_VOUT_SET HPLDO VOUT Value. 1.1V. 1.15V. 1.2V. 1.05V. HPLDO_BYPASS HPLDO Bypass. -

Page 142: Cm Control Register

ADAU186x Hardware Reference Manual UG-2257 CM CONTROL REGISTER Address: 0x4000C071, Reset: 0x00, Name: PMU_CTRL2 Table 198. Bit Descriptions for PMU_CTRL2 Bits Bit Name Settings Description Reset Access [7:5] RESERVED Reserved. TDSP_WAIT_MODE_BYP HiFi3z can enter sleep (wait) mode by WAITI instruction, this gate off the majority of the clocks in the processor. -

Page 143: Dldo Control Register

UG-2257 ADAU186x Hardware Reference Manual DLDO CONTROL REGISTER Address: 0x4000C074, Reset: 0x81, Name: PMU_CTRL5 Table 201. Bit Descriptions for PMU_CTRL5 Bits Bit Name Settings Description Reset Access [7:3] RESERVED Reserved. 0x10 [2:0] DLDO_CTRL DLDO Output Voltage. Digital LDO output is 0.85V. -

Page 144: Fast To Slow Decimator Sample Rates Channel 4 And Channel 5 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access 0101 384kHz Sample Rate. 1000 8kHz Sample Rate. 1001 16kHz Sample Rate. RESERVED Reserved. [2:0] FDEC23_IN_FS Decimator Channels 2/3 Input Sampling Rate. 24kHz Sample Rate. 48kHz Sample Rate. -

Page 145: Fast To Slow Decimator Channel 0 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access RESERVED Reserved. [2:0] FDEC67_IN_FS Decimator Channels 6/7 Input Sampling Rate. 24kHz Sample Rate. 48kHz Sample Rate. 96kHz Sample Rate. 192kHz Sample Rate. 384kHz Sample Rate. 768kHz Sample Rate. -

Page 146: Fast To Slow Decimator Channel 1 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Input ASRC Channel 2. Input ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. -

Page 147: Fast To Slow Decimator Channel 2 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 12. Tensilica DSP Channel 13. Tensilica DSP Channel 14. Tensilica DSP Channel 15. Input ASRC Channel 0. Input ASRC Channel 1. Input ASRC Channel 2. -

Page 148: Fast To Slow Decimator Channel 3 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 6. Tensilica DSP Channel 7. Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. Tensilica DSP Channel 11. Tensilica DSP Channel 12. -

Page 149: Fast To Slow Decimator Channel 4 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 0. Tensilica DSP Channel 1. Tensilica DSP Channel 2. Tensilica DSP Channel 3. Tensilica DSP Channel 4. Tensilica DSP Channel 5. Tensilica DSP Channel 6. -

Page 150: Fast To Slow Decimator Channel 5 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14. FastDSP Channel 15. Tensilica DSP Channel 0. Tensilica DSP Channel 1. Tensilica DSP Channel 2. - Page 151 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 4. FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13.

-

Page 152: Fast To Slow Decimator Channel 6 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 FAST TO SLOW DECIMATOR CHANNEL 6 INPUT ROUTING REGISTER Address: 0x4000C08A, Reset: 0x00, Name: FDEC_ROUTE6 Table 212. Bit Descriptions for FDEC_ROUTE6 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] FDEC0_ROUTE Fast to Slow Decimator Channel 0 Input Routing. -

Page 153: Fast To Slow Decimator Channel 7 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access DMIC Channel 2. DMIC Channel 3. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. FAST TO SLOW DECIMATOR CHANNEL 7 INPUT ROUTING REGISTER Address: 0x4000C08B, Reset: 0x00, Name: FDEC_ROUTE7 Table 213. -

Page 154: Slow To Fast Interpolator Sample Rates Channel 0/Channel 1 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Input ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. EQ0. DMIC Channel 4. -

Page 155: Slow To Fast Interpolator Sample Rates Channel 4/Channel 5 Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access 192kHz Sample Rate. 384kHz Sample Rate. 768kHz Sample Rate. [3:0] FINT23_IN_FS Interpolator Channel 2/Channel 3 Input Sampling Rate. 0000 12kHz Sample Rate. 0001 24kHz Sample Rate. 0010 48kHz Sample Rate. -

Page 156: Slow To Fast Interpolator Channel 0 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access [3:0] FINT67_IN_FS Interpolator Channel 6/Channel 7 Input Sampling Rate. 0000 12kHz Sample Rate. 0001 24kHz Sample Rate. 0010 48kHz Sample Rate. 0011 96kHz Sample Rate. 0100 192kHz Sample Rate. - Page 157 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 1. FastDSP Channel 2. FastDSP Channel 3. FastDSP Channel 4. FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10.

-

Page 158: Slow To Fast Interpolator Channel 1 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 SLOW TO FAST INTERPOLATOR CHANNEL 1 INPUT ROUTING REGISTER Address: 0x4000C095, Reset: 0x00, Name: FINT_ROUTE1 Table 219. Bit Descriptions for FINT_ROUTE1 Bits Bit Name Settings Description Reset Access RESERVED Reserved. [6:0] FINT0_ROUTE Slow to Fast Interpolator Channel 0 Input Routing. -

Page 159: Slow To Fast Interpolator Channel 2 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14. FastDSP Channel 15. Tensilica DSP Channel 0. Tensilica DSP Channel 1. Tensilica DSP Channel 2. Tensilica DSP Channel 3. - Page 160 ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Serial Port 0 Channel 6. Serial Port 0 Channel 7. Serial Port 0 Channel 8. Serial Port 0 Channel 9. Serial Port 0 Channel 10. Serial Port 0 Channel 11.

-

Page 161: Slow To Fast Interpolator Channel 3 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 9. Tensilica DSP Channel 10. Tensilica DSP Channel 11. Tensilica DSP Channel 12. Tensilica DSP Channel 13. Tensilica DSP Channel 14. Tensilica DSP Channel 15. - Page 162 ADAU186x Hardware Reference Manual UG-2257 Serial Port 1 Channel 4. Serial Port 1 Channel 5. Serial Port 1 Channel 6. Serial Port 1 Channel 7. Serial Port 1 Channel 8. Serial Port 1 Channel 9. Serial Port 1 Channel 10.

-

Page 163: Slow To Fast Interpolator Channel 4 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. SLOW TO FAST INTERPOLATOR CHANNEL 4 INPUT ROUTING REGISTER Address: 0x4000C098, Reset: 0x00, Name: FINT_ROUTE4 Table 221. - Page 164 ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access FastDSP Channel 2. FastDSP Channel 3. FastDSP Channel 4. FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11.

-

Page 165: Slow To Fast Interpolator Channel 5 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual SLOW TO FAST INTERPOLATOR CHANNEL 5 INPUT ROUTING REGISTER Address: 0x4000C099, Reset: 0x00, Name: FINT_ROUTE5 Table 222. Bit Descriptions for FINT_ROUTE5 Bits Bit Name Settings Description Reset Access RESERVED Reserved. [6:0] FINT0_ROUTE Slow to Fast Interpolator Channel 0 Input Routing. -

Page 166: Slow To Fast Interpolator Channel 6 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14. FastDSP Channel 15. Tensilica DSP Channel 0. Tensilica DSP Channel 1. Tensilica DSP Channel 2. Tensilica DSP Channel 3. - Page 167 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Serial Port 0 Channel 6. Serial Port 0 Channel 7. Serial Port 0 Channel 8. Serial Port 0 Channel 9. Serial Port 0 Channel 10. Serial Port 0 Channel 11.

-

Page 168: Slow To Fast Interpolator Channel 7 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 9. Tensilica DSP Channel 10. Tensilica DSP Channel 11. Tensilica DSP Channel 12. Tensilica DSP Channel 13. Tensilica DSP Channel 14. Tensilica DSP Channel 15. - Page 169 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Serial Port 1 Channel 3. Serial Port 1 Channel 4. Serial Port 1 Channel 5. Serial Port 1 Channel 6. Serial Port 1 Channel 7. Serial Port 1 Channel 8.

-

Page 170: Input Asrc Control, Source, And Rate Selection Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. -

Page 171: Input Asrc Channel 2 And Channel 3 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Serial Port Channel 3. Serial Port Channel 4. Serial Port Channel 5. Serial Port Channel 6. Serial Port Channel 7. Serial Port Channel 8. Serial Port Channel 9. -

Page 172: Output Asrc Control Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Serial Port Channel 13. Serial Port Channel 14. Serial Port Channel 15. [3:0] ASRCI2_ROUTE Input ASRC Channel 2 routing. Serial Port Channel 0. Serial Port Channel 1. Serial Port Channel 2. -

Page 173: Output Asrc Channel 0 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual OUTPUT ASRC CHANNEL 0 INPUT ROUTING REGISTER Address: 0x4000C0A4, Reset: 0x00, Name: ASRCO_ROUTE0 Table 229. Bit Descriptions for ASRCO_ROUTE0 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] ASRCO0_ROUTE Output ASRC Channel 0 Input Routing. -

Page 174: Output Asrc Channel 1 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 5. Fast to Slow Decimator Channel 6. Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. -

Page 175: Output Asrc Channel 2 Input Routing Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. Fast to Slow Decimator Channel 0. Fast to Slow Decimator Channel 1. Fast to Slow Decimator Channel 2. -

Page 176: Output Asrc Channel 3 Input Routing Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. Tensilica DSP Channel 11. Tensilica DSP Channel 12. Tensilica DSP Channel 13. Tensilica DSP Channel 14. -

Page 177: Fastdsp Run Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 14. FastDSP Channel 15. Tensilica DSP Channel 0. Tensilica DSP Channel 1. Tensilica DSP Channel 2. Tensilica DSP Channel 3. Tensilica DSP Channel 4. Tensilica DSP Channel 5. -

Page 178: Fastdsp Current Bank And Bank Ramping Controls Register

ADAU186x Hardware Reference Manual UG-2257 FASTDSP CURRENT BANK AND BANK RAMPING CONTROLS REGISTER Address: 0x4000C0B1, Reset: 0x70, Name: FDSP_CTRL1 Table 234. Bit Descriptions for FDSP_CTRL1 Bits Bit Name Settings Description Reset Access FastDSP Parameter Bank Ramp Rate of Change. Determines time to... -

Page 179: Fastdsp Bank Ramping Stop Point Register

UG-2257 ADAU186x Hardware Reference Manual FASTDSP BANK RAMPING STOP POINT REGISTER Address: 0x4000C0B2, Reset: 0x3F, Name: FDSP_CTRL2 Table 235. Bit Descriptions for FDSP_CTRL2 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] FDSP_LAMBDA FastDSP Bank Switch Ramp Stop Point. Lambda is a 6-Bit value representing... -

Page 180: Fastdsp Frame Rate Source Register

ADAU186x Hardware Reference Manual UG-2257 FASTDSP FRAME RATE SOURCE REGISTER Address: 0x4000C0B4, Reset: 0x00, Name: FDSP_CTRL4 Table 237. Bit Descriptions for FDSP_CTRL4 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. FDSP_ONZ_SOURCE FastDSP Output Non-zero source. Channel 14. Channel 15. -

Page 181: Fastdsp Modulo N Counter For Lower Rate Conditional Execution Register

UG-2257 ADAU186x Hardware Reference Manual FASTDSP MODULO N COUNTER FOR LOWER RATE CONDITIONAL EXECUTION REGISTER Address: 0x4000C0B7, Reset: 0x00, Name: FDSP_CTRL7 Table 240. Bit Descriptions for FDSP_CTRL7 Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] FDSP_MOD_N FastDSP Modulo N counter reset for conditional execution. -

Page 182: Fast Dsp Safeload Address Register

ADAU186x Hardware Reference Manual UG-2257 FAST DSP SAFELOAD ADDRESS REGISTER Address: 0x4000C0B9, Reset: 0x00, Name: FDSP_SL_ADDR Table 242. Bit Descriptions for FDSP_SL_ADDR Bits Bit Name Settings Description Reset Access [7:6] RESERVED Reserved. [5:0] FDSP_SL_ADDR FastDSP Safeload Instruction Number. FASTDSP SAFELOAD PARAMETER 0 VALUE REGISTER Address: 0x4000C0BA, Reset: 0x00, Name: FDSP_SL_P0_0 Table 243. -

Page 183: Fastdsp Safeload Parameter 1 Value Register

UG-2257 ADAU186x Hardware Reference Manual FASTDSP SAFELOAD PARAMETER 1 VALUE REGISTER Address: 0x4000C0BF, Reset: 0x00, Name: FDSP_SL_P1_1 Table 248. Bit Descriptions for FDSP_SL_P1_1 Bits Bit Name Settings Description Reset Access [7:0] FDSP_SL_P1[15:8] FastDSP Safeload Parameter 1 (B1 coeff ) value to be written. -

Page 184: Fastdsp Safeload Parameter 2 Value Register

ADAU186x Hardware Reference Manual UG-2257 FASTDSP SAFELOAD PARAMETER 2 VALUE REGISTER Address: 0x4000C0C5, Reset: 0x00, Name: FDSP_SL_P2_3 Table 254. Bit Descriptions for FDSP_SL_P2_3 Bits Bit Name Settings Description Reset Access [7:0] FDSP_SL_P2[31:24] FastDSP Safeload Parameter 2 (B2 coeff ) value to be written. -

Page 185: Fastdsp Safeload Parameter 4 Value Register

UG-2257 ADAU186x Hardware Reference Manual FASTDSP SAFELOAD PARAMETER 4 VALUE REGISTER Address: 0x4000C0CB, Reset: 0x00, Name: FDSP_SL_P4_1 Table 260. Bit Descriptions for FDSP_SL_P4_1 Bits Bit Name Settings Description Reset Access [7:0] FDSP_SL_P4[15:8] FastDSP Safeload Parameter 4 (A2 coeff ) value to be written. -

Page 186: Fastdsp Safeload Parameter 0 Value Register

ADAU186x Hardware Reference Manual UG-2257 FASTDSP SAFELOAD PARAMETER 0 VALUE REGISTER Address: 0x4000C0D1, Reset: 0x00, Name: FDSP_ONZ_MASK2 Table 266. Bit Descriptions for FDSP_ONZ_MASK2 Bits Bit Name Settings Description Reset Access [7:0] FDSP_ONZ_MASK[23:16] FastDSP Safeload Parameter 0 (B0 coeff ) value to be written. - Page 187 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Serial Port 1 Channel 2. Serial Port 1 Channel 3. Serial Port 1 Channel 4. Serial Port 1 Channel 5. Serial Port 1 Channel 6. Serial Port 1 Channel 7.

-

Page 188: Tensilica Dsp Software Reset Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. -

Page 189: Tensilica Dsp Alternative Reset Vector Address, Byte 2 Register

UG-2257 ADAU186x Hardware Reference Manual TENSILICA DSP ALTERNATIVE RESET VECTOR ADDRESS, BYTE 2 REGISTER Address: 0x4000C0DA, Reset: 0x00, Name: TDSP_ALTVEC_ADDR2 Table 273. Bit Descriptions for TDSP_ALTVEC_ADDR2 Bits Bit Name Settings Description Reset Access [7:0] TDSP_ALTVEC_ADDR[23:16] This register specifies the boot address when TDSP_ALTVEC_EN=1'b1. -

Page 190: Serial Port 0 Control 2 Register

ADAU186x Hardware Reference Manual UG-2257 SERIAL PORT 0 CONTROL 2 REGISTER Address: 0x4000C0E1, Reset: 0x00, Name: SPT0_CTRL2 Table 277. Bit Descriptions for SPT0_CTRL2 Bits Bit Name Settings Description Reset Access [7:4] RESERVED Reserved. SPT0_BCLK_POL Serial port - selects bclk polarity. - Page 191 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14.

-

Page 192: Serial Port 0 Output Routing Slot 1 (Right) Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. No Output. Slot not used. SERIAL PORT 0 OUTPUT ROUTING SLOT 1 (RIGHT) REGISTER Address: 0x4000C0E4, Reset: 0x11, Name: SPT0_ROUTE1 Table 280. -

Page 193: Serial Port 0 Output Routing Slot 2 Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Output ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. Fast to Slow Decimator Channel 0. -

Page 194: Serial Port 0 Output Routing Slot 3 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 4. Tensilica DSP Channel 5. Tensilica DSP Channel 6. Tensilica DSP Channel 7. Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. - Page 195 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14.

-

Page 196: Serial Port 0 Output Routing Slot 4 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. No Output. Slot not used. SERIAL PORT 0 OUTPUT ROUTING SLOT 4 REGISTER Address: 0x4000C0E7, Reset: 0x3F, Name: SPT0_ROUTE4 Table 283. -

Page 197: Serial Port 0 Output Routing Slot 5 Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Output ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. Fast to Slow Decimator Channel 0. -

Page 198: Serial Port 0 Output Routing Slot 6 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 4. Tensilica DSP Channel 5. Tensilica DSP Channel 6. Tensilica DSP Channel 7. Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. - Page 199 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14.

-

Page 200: Serial Port 0 Output Routing Slot 7 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. No Output. Slot not used. SERIAL PORT 0 OUTPUT ROUTING SLOT 7 REGISTER Address: 0x4000C0EA, Reset: 0x3F, Name: SPT0_ROUTE7 Table 286. -

Page 201: Serial Port 0 Output Routing Slot 8 Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Output ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. Fast to Slow Decimator Channel 0. -

Page 202: Serial Port 0 Output Routing Slot 9 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 4. Tensilica DSP Channel 5. Tensilica DSP Channel 6. Tensilica DSP Channel 7. Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. - Page 203 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14.

-

Page 204: Serial Port 0 Output Routing Slot 10 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. No Output. Slot not used. SERIAL PORT 0 OUTPUT ROUTING SLOT 10 REGISTER Address: 0x4000C0ED, Reset: 0x3F, Name: SPT0_ROUTE10 Table 289. -

Page 205: Serial Port 0 Output Routing Slot 11 Register

UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access Output ASRC Channel 3. ADC Channel 0. ADC Channel 1. ADC Channel 2. DMIC Channel 0. DMIC Channel 1. DMIC Channel 2. DMIC Channel 3. Fast to Slow Decimator Channel 0. -

Page 206: Serial Port 0 Output Routing Slot 12 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Tensilica DSP Channel 4. Tensilica DSP Channel 5. Tensilica DSP Channel 6. Tensilica DSP Channel 7. Tensilica DSP Channel 8. Tensilica DSP Channel 9. Tensilica DSP Channel 10. - Page 207 UG-2257 ADAU186x Hardware Reference Manual Bits Bit Name Settings Description Reset Access FastDSP Channel 5. FastDSP Channel 6. FastDSP Channel 7. FastDSP Channel 8. FastDSP Channel 9. FastDSP Channel 10. FastDSP Channel 11. FastDSP Channel 12. FastDSP Channel 13. FastDSP Channel 14.

-

Page 208: Serial Port 0 Output Routing Slot 13 Register

ADAU186x Hardware Reference Manual UG-2257 Bits Bit Name Settings Description Reset Access Fast to Slow Decimator Channel 7. EQ0. DMIC Channel 4. DMIC Channel 5. DMIC Channel 6. DMIC Channel 7. No Output. Slot not used. SERIAL PORT 0 OUTPUT ROUTING SLOT 13 REGISTER Address: 0x4000C0F0, Reset: 0x3F, Name: SPT0_ROUTE13 Table 292. -