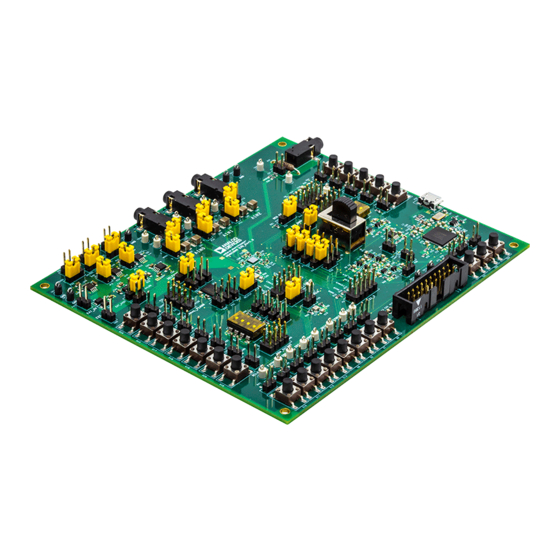

Analog Devices ADAU186x Manuals

Manuals and User Guides for Analog Devices ADAU186x. We have 1 Analog Devices ADAU186x manual available for free PDF download: Hardware Reference Manual

Analog Devices ADAU186x Hardware Reference Manual (337 pages)

Brand: Analog Devices

|

Category: Motherboard

|

Size: 11 MB

Table of Contents

-

Scope1

-

Pll15

-

Clock Output16

-

PDM Outputs23

-

EQ Clear25

-

Fastdsp Core26

-

Instructions26

-

Data Memory27

-

Parameters27

-

Normal Mode29

-

TURBO Mode29

-

Dma30

-

Fifo30

-

Data Sync30

-

Uart30

-

Qspi30

-

Watchdog30

-

Interrupt30

-

Control Port34

-

Self Boot41

-

Layout45

-

Grounding45

Advertisement