Table of Contents

Advertisement

Quick Links

Features

18-Mbit Density (1M x 18, 512K x 36)

■

267 MHz Clock for high Bandwidth

■

2-word Burst for reducing Address Bus Frequency

■

Double Data Rate (DDR) Interfaces

■

(data transferred at 534 MHz) at 267 MHz

Two Input Clocks (K and K) for precise DDR Timing

■

SRAM uses rising edges only

❐

Two Input Clocks for Output Data (C and C) to minimize Clock

■

Skew and Flight Time mismatches

Echo Clocks (CQ and CQ) simplify Data Capture in High Speed

■

Systems

Synchronous internally Self-timed Writes

■

DDR II operates with 1.5 Cycle Read Latency when the DLL is

■

enabled

Operates similar to a DDR I Device with one Cycle Read

■

Latency in DLL Off Mode

1.8V Core Power Supply with HSTL Inputs and Outputs

■

Variable drive HSTL Output Buffers

■

Expanded HSTL Output Voltage (1.4V–V

■

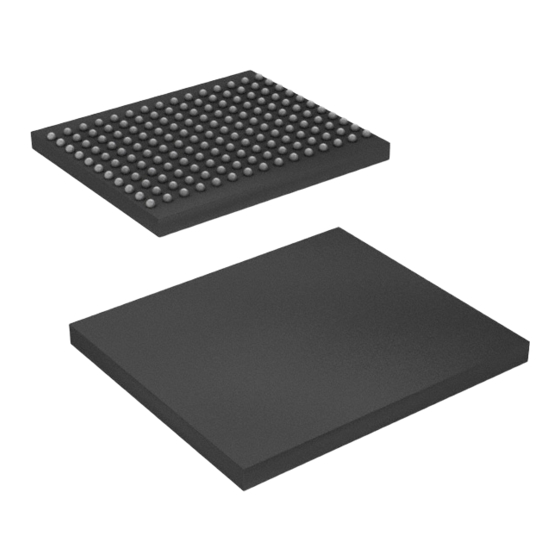

Available in 165-Ball FBGA Package (13 x 15 x 1.4 mm)

■

Offered in both Pb-free and non Pb-free Packages

■

JTAG 1149.1 compatible Test Access Port

■

Delay Lock Loop (DLL) for accurate Data Placement

■

Configurations

CY7C1318CV18 – 1M x 18

CY7C1320CV18 – 512K x 36

Selection Guide

Description

Maximum Operating Frequency

Maximum Operating Current

Cypress Semiconductor Corporation

Document Number: 001-07160 Rev. *F

18-Mbit DDR II SRAM 2-Word

Functional Description

The

Synchronous Pipelined SRAMs equipped with DDR II archi-

tecture. The DDR II consists of an SRAM core with advanced

synchronous peripheral circuitry and a one-bit burst counter.

Addresses for read and write are latched on alternate rising

edges of the input (K) clock. Write data is registered on the rising

edges of both K and K. Read data is driven on the rising edges

of C and C if provided, or on the rising edge of K and K if C/C are

not provided. For CY7C1318CV18 and CY7C1320CV18, the

burst counter takes in the least significant bit of the external

address and bursts two 18-bit words (in the case of

CY7C1318CV18) of two 36-bit words (in the case of

CY7C1320CV18) sequentially into or out of the device.

Asynchronous inputs include an output impedance matching

input (ZQ). Synchronous data outputs (Q, sharing the same

physical pins as the data inputs, D) are tightly matched to the two

output echo clocks CQ/CQ, eliminating the need to capture data

separately from each individual DDR SRAM in the system

design. Output data clocks (C/C) enable maximum system

clocking and data synchronization flexibility.

All synchronous inputs pass through input registers controlled by

the K or K input clocks. All data outputs pass through output

registers controlled by the C or C (or K or K in a single clock

domain) input clocks. Writes are conducted with on-chip

synchronous self-timed write circuitry.

)

DD

267 MHz

267

x18

805

x36

855

•

198 Champion Court

CY7C1318CV18

CY7C1320CV18

Burst Architecture

CY7C1318CV18,

and

CY7C1320CV18

250 MHz

200 MHz

250

200

730

600

775

635

,

•

San Jose

CA 95134-1709

are

1.8V

167 MHz

Unit

167

MHz

510

mA

540

•

408-943-2600

Revised August 24, 2009

[+] Feedback

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Cypress 001-07160

-

Page 1: Functional Description

Selection Guide Description Maximum Operating Frequency Maximum Operating Current Cypress Semiconductor Corporation Document Number: 001-07160 Rev. *F 18-Mbit DDR II SRAM 2-Word Functional Description CY7C1318CV18, Synchronous Pipelined SRAMs equipped with DDR II archi- tecture. The DDR II consists of an SRAM core with advanced synchronous peripheral circuitry and a one-bit burst counter. - Page 2 Control Logic [1:0] Logic Block Diagram (CY7C1320CV18) Burst Logic (18:0) Address (18:1) Register Gen. DOFF Control Logic [3:0] Document Number: 001-07160 Rev. *F Write Write Output Logic Control Read Data Reg. Reg. Reg. Reg. Write Write Output Logic Control Read Data Reg.

-

Page 3: Pin Configuration

DQ26 Note 1. NC/36M, NC/72M, NC/144M, and NC/288M are not connected to the die and can be tied to any voltage level. Document Number: 001-07160 Rev. *F 165-Ball FBGA (13 x 15 x 1.4 mm) Pinout CY7C1318CV18 (1M x 18) -

Page 4: Pin Definitions

CQ, CQ, and Q between ZQ and ground. Alternatively, this pin can be connected directly to V minimum impedance mode. This pin cannot be connected directly to GND or left unconnected. Document Number: 001-07160 Rev. *F Pin Description are automatically tristated. - Page 5 Power Supply Power Supply Inputs to the Core of the Device. Ground Ground for the Device. Power Supply Power Supply Inputs for the Outputs of the Device. Document Number: 001-07160 Rev. *F CY7C1318CV18 CY7C1320CV18 Pin Description Page 5 of 26...

-

Page 6: Functional Overview

[17:0] data register, provided BWS are both asserted active. On the [1:0] Document Number: 001-07160 Rev. *F subsequent rising edge of the negative input clock (K) the infor- mation presented to D register, provided BWS of data are then written into the memory array at the specified location. -

Page 7: Application Example

Source CLK# Echo Clock1/Echo Clock#1 Echo Clock2/Echo Clock#2 Document Number: 001-07160 Rev. *F These chips use a Delay Lock Loop (DLL) that is designed to function between 120 MHz and the specified maximum clock frequency. During power up, when the DOFF is tied HIGH, the DLL is locked after 1024 cycles of stable clock. - Page 8 8. Is based on a write cycle that was initiated in accordance with the of a write cycle, as long as the setup and hold requirements are achieved. Document Number: 001-07160 Rev. *F [2, 3, 4, 5, 6, 7] Stopped...

- Page 9 L–H – L–H – L–H – Document Number: 001-07160 Rev. *F [2, 8] Comments – During the data portion of a write sequence, all four bytes (D the device. L–H During the data portion of a write sequence, all four bytes (D the device.

- Page 10 TDI pin on the rising edge of TCK. Data is output on the TDO pin on the falling edge of TCK. Document Number: 001-07160 Rev. *F Instruction Register Three-bit instructions can be serially loaded into the instruction register.

- Page 11 Once the data is captured, it is possible to shift out the data by putting the TAP into the Shift-DR state. This places the boundary scan register between the TDI and TDO pins. Document Number: 001-07160 Rev. *F CY7C1318CV18 CY7C1320CV18...

-

Page 12: Tap Controller State Diagram

The state diagram for the TAP controller follows. TEST-LOGIC RESET TEST-LOGIC/ IDLE Note 9. The 0/1 next to each state represents the value at TMS at the rising edge of TCK. Document Number: 001-07160 Rev. *F SELECT DR-SCAN CAPTURE-DR SHIFT-DR EXIT1-DR PAUSE-DR... - Page 13 10. These characteristics pertain to the TAP inputs (TMS, TCK, TDI and TDO). Parallel load levels are specified in the 11. Overshoot: V (AC) < V + 0.85V (Pulse width less than t 12. All Voltage referenced to Ground. Document Number: 001-07160 Rev. *F Bypass Register Instruction Register Identification Register Boundary Scan Register...

- Page 14 14. Test conditions are specified using the load in TAP AC Test Conditions. t Document Number: 001-07160 Rev. *F Description [14] Figure 2. TAP Timing and Test Conditions 0.9V...

-

Page 15: Instruction Codes

Do Not Use: This instruction is reserved for future use. RESERVED Do Not Use: This instruction is reserved for future use. BYPASS Places the bypass register between TDI and TDO. This operation does not affect SRAM operation. Document Number: 001-07160 Rev. *F Value CY7C1320CV18 11010100010100101 00000110100 00000110100... - Page 16 Boundary Scan Order Bit # Bump ID Bit # Document Number: 001-07160 Rev. *F Bump ID Bit # Bump ID Internal CY7C1318CV18 CY7C1320CV18 Bit # Bump ID Page 16 of 26 [+] Feedback...

- Page 17 DLL. Unstable Clock Clock Start (Clock Starts after DOFF Document Number: 001-07160 Rev. *F DLL Constraints DLL uses K clock as its synchronizing input. The input must ■ have low phase jitter, which is specified as t The DLL functions at frequencies down to 120 MHz.

-

Page 18: Maximum Ratings

/2)/(RQ/5) for values of 175Ω < RQ < 350Ω. 18. V (min) = 0.68V or 0.46V , whichever is larger, V 19. The operation current is calculated with 50% read cycle and 50% write cycle. Document Number: 001-07160 Rev. *F Neutron Soft Error Immunity Parameter LSBU LMBU + 0.3V... -

Page 19: Thermal Resistance

Note 20. Unless otherwise noted, test conditions assume signal transition time of 2V/ns, timing reference levels of 0.75V, V levels of 0.25V to 1.25V, and output loading of the specified I Document Number: 001-07160 Rev. *F Test Conditions Max V... -

Page 20: Switching Characteristics

21. When a part with a maximum frequency above 167 MHz is operating at a lower clock frequency, it requires the input timings of the frequency range in which it is being operated and outputs data with the output timings of that frequency range. 22. This part has an internal voltage regulator; t POWER Document Number: 001-07160 Rev. *F 267 MHz Description Min Max Min Max Min Max Min Max [22] –... - Page 21 5 pF as in (b) of 25. At any voltage and temperature t is less than t Document Number: 001-07160 Rev. *F 267 MHz Description Min Max Min Max Min Max Min Max –...

-

Page 22: Switching Waveforms

28. In this example, if address A4 = A3, then data Q40 = D30 and Q41 = D31. Write data is forwarded immediately as read results. This note applies to the whole diagram. Document Number: 001-07160 Rev. *F [26, 27, 28]... -

Page 23: Ordering Information

CY7C1320CV18-250BZXC CY7C1320CV18-200BZC CY7C1318CV18-200BZXC CY7C1318CV18-200BZI CY7C1318CV18-167BZC CY7C1320CV18-167BZC Document Number: 001-07160 Rev. *F www.cypress.com Package Diagram Package Type 51-85180 165-Ball Fine Pitch Ball Grid Array (13 x 15 x 1.4 mm) Pb-Free Commercial 51-85180 165-Ball Fine Pitch Ball Grid Array (13 x 15 x 1.4 mm) 51-85180 165-Ball Fine Pitch Ball Grid Array (13 x 15 x 1.4 mm) Pb-Free... -

Page 24: Package Diagram

Package Diagram Figure 6. 165-Ball FBGA (13 x 15 x 1.4 mm), 51-85180 TOP VIEW PIN 1 CORNER 13.00±0.10 SEATING PLANE Document Number: 001-07160 Rev. *F 0.15(4X) CY7C1318CV18 CY7C1320CV18 BOTTOM VIEW PIN 1 CORNER Ø0.08 M C Ø0.25 M C A B -0.06... - Page 25 2518624 See ECN NXR/PYRS Changed JTAG ID (31:29) from 001 to 000 2755838 08/25/2009 VKN/AESA Document Number: 001-07160 Rev. *F Description of Change New data sheet Changed t and t from 40 ns to 20 ns, changed t from 10 ns to 5 ns and changed t...

- Page 26 Use may be limited by and subject to the applicable Cypress software license agreement. Document Number: 001-07160 Rev. *F QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress, IDT, NEC, Renesas, and Samsung. All product and company names mentioned in this document are the trademarks of their respective holders.

Need help?

Do you have a question about the 001-07160 and is the answer not in the manual?

Questions and answers