Summary of Contents for iWave iW-RainboW-G21M

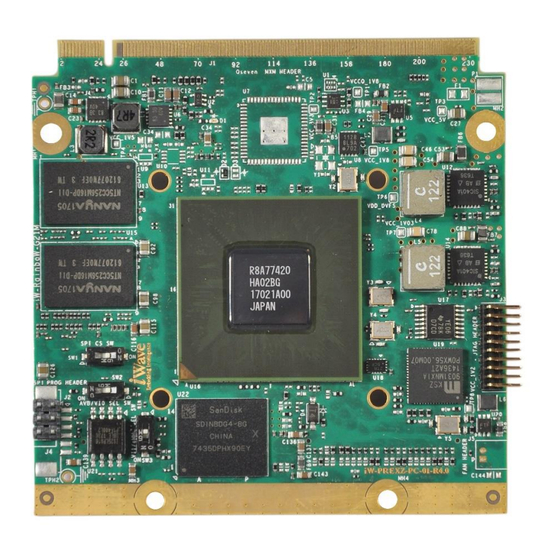

- Page 1 RZ/G1H Qseven SOM Hardware User Guide iW-RainboW-G21M RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 1 of 92...

- Page 2 If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. “iWave Systems Tech. Pvt. Ltd.” REL1.1 iWave Systems Technologies Pvt.

- Page 3 No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

-

Page 4: Table Of Contents

2.6.19 Power Control Signal ........................... 26 2.6.20 Reset Signal ..............................26 Expansion Connector1 Interfaces ........................42 2.7.1 Parallel Camera Interfaces .......................... 43 Expansion Connector2 Interfaces ........................50 2.8.1 10/100Mbps Ethernet ..........................51 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 4 of 92... - Page 5 APPENDIX I ..............................89 RZ/G1H Qseven SOM Configuration Switches ....................89 APPENDIX II ..............................90 RZ/G1H SPI Programmer Board ........................90 APPENDIX III ............................... 91 RZ/G1H Qseven SOM Development Platform ....................91 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 5 of 92...

- Page 6 Table 16: Power Sequence Timing ..........................80 Table 17: Power Consumption ............................81 Table 18: Environmental Specification ........................... 82 Table 19: Orderable Product Part Numbers ........................88 Table 20: SOM Configuration Switches ........................... 89 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 6 of 92...

-

Page 7: Introduction

This document is the Hardware User Guide for the RZ/G1H Qseven System On Module based on the Renesas’s RZ/G1H Application processor. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the RZ/G1H Qseven System On Module from a Hardware Systems perspective. - Page 8 Serial Sound Interface SDRAM Synchronous Dynamic Random Access Memory System On Module Time Division Multiplexing Time Pulse Unit UART Universal Asynchronous Receiver/Transmitter Universal Serial Bus USB OTG USB On The Go REL1.1 iWave Systems Technologies Pvt. Ltd. Page 8 of 92...

-

Page 9: Terminlogy Description

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On-SOM. References • RZ/G1H CPU Hardware User Manuals • Qseven® Specification Version 2.0 • Qseven® Design Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 9 of 92... -

Page 10: Important Note

If CPU pin doesn’t have multiplexing option, then the signal name is mentioned as, “Function name” Example: I2C3_SDA In this signal, functionality which we are using I2C3_SDA Note: The above naming is not applicable for other signals which are not connected to CPU. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 10 of 92... -

Page 11: Architecture And Design

This section provides detailed information about the RZ/G1H Qseven SOM features and Hardware architecture with high level block diagram. Also this section provides detailed information about Qseven edge connector & Expansion connector’s pin assignment and usage. RZ/G1H QevenSOM Block Diagram iW-RainboW-G21M - RZ/G1H Qseven SOM Block Diagram PCIe x 1¹ DDR3 -1GB... -

Page 12: Rz/G1H Qsevensom Features

• LVDS x 2 Ports • HDMI x 1 Port • SSI/I2S (Audio Interface) x 1 Port • Debug UART • Data UART (with CTS & RTS) x 1 Port REL1.1 iWave Systems Technologies Pvt. Ltd. Page 12 of 92... - Page 13 In RZ/G1H CPU, EtherAVB and VIN0 are multiplexed in same pins and so either one interface only can be used at a time. A DIP switch (SW2) is provided on SOM to select either EtherAVB or VIN0. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 13 of 92...

- Page 14 8bit and VIN2 are multiplexed in same pins and so VIN2 cannot be supported when VIN1 is supported in 16bit mode. If VIN1 is supported in 8bit mode, then VIN2 also can be supported in 8bit mode. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 14 of 92...

-

Page 15: Rz/G1H Cpu

Figure 2: RZ/G1H CPU Simplified Block Diagram Note: Please refer the latest RZ/G1H Datasheet & Reference Manual for Electrical characteristics of RZ/G1H CPU which may be revised from time to time. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 15 of 92... -

Page 16: Memory

VIN2 is selected. To program the boot code in to the SPI flash (for the first time or if boot code is corrupted), use iWave’s RZ/G1H SPI Programmer Board through SPI Flash Programming Header (J4) (or) JTAG debugger through JTAG Header (J3). -

Page 17: Emmc Flash

3.3V voltage level. In SOM power off condition, this device will take power from Qseven Edge (VCC_RTC) coin cell power input (Pin 193) and continues to keep the current time. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 17 of 92... -

Page 18: Qseven Pcb Edge Connector

Number of Pins - 230 Connector Part - Not Applicable (On Board PCB Edge connector) Mating Connector - IMSA-18010S-230A-GN1 from IRISO 88882-2D0K from Aces AS0B326-S78N-7F from FOXCONN CN113-230-0001VE from Yamaichi Electronics REL1.1 iWave Systems Technologies Pvt. Ltd. Page 18 of 92... -

Page 19: Gigabit Ethernet

VIN0. If the DIP switch is set to “OFF” position, then EtherAVB is supported. If the DIP switch is set to “ON” position, then VIN0 is supported. This DIP switch position can be read by software though GPIO pin “GP5_21”. Note: For more details on DIP switch (SW2), refer APPENDIX I. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 19 of 92... -

Page 20: Usb 3.0 Host Interface

Note: In RZ/G1H CPU, USB3.0 & SATA0 High speed transceivers are multiplexed in same pins and so either one interface only can be used at a time. By default, USB3.0 is supported. Please contact iWave if SATA support is required. -

Page 21: Sata Interface (Optional)

Note: In RZ/G1H CPU, USB3.0 & SATA0 and PCIe & SATA1 High speed transceivers are multiplexed in same pins and so either one interface only can be used at a time correspondingly. By default, USB3.0 & PCIe is supported. Please contact iWave if SATA support is required. 2.6.5 USB 2.0 OTG Interface The RZ/G1H Qseven SOM supports One USB2.0 OTG interface on Qseven Edge connector. -

Page 22: Sd Interface

Note: In RZ/G1H SOM, RZ/G1H CPU’s DU_LVDS1 output can be connected to either HDMI transmitter or Secondary LVDS port of Qseven Edge. By default, it is connected to Secondary LVDS port of Qseven Edge. Please contact iWave for more details. -

Page 23: Hdmi Interface (Optional)

Note: In RZ/G1H SOM, RZ/G1H CPU’s DU_LVDS1 output can be connected to either HDMI transmitter or Secondary LVDS port of Qseven Edge. By default, it is connected to Secondary LVDS port of Qseven Edge. Please contact iWave for more details. -

Page 24: Data Uart Interface

32bit x 64 stages for transmit FIFOs & 32bit × 256 stages for receive FIFOs and allows MSB first or LSB first selectable for data transmission and reception. For more details, refer Qseven Edge connector pins 199 to 203 on Table 4. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 24 of 92... -

Page 25: I2C Interface

Note: Most of the RZ/G1H CPU pins which are connected to Qseven Edge connector and Expansion connectors can be configured as GPIO with interrupt capable (if not used as other interface). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 25 of 92... -

Page 26: Manufacturing/Debug Uart Interface

For more details, refer Qseven Edge connector pins 204,208 & 209 on Table 4. Note: Optionally JTAG interface can be supported instead of Debug UART interface on Qseven Edge connector in RZ/G1H Qseven SOM. Please contact iWave for more details. 2.6.18 Power Input The RZ/G1H Qseven SOM works with single 5V power input (VCC) from Qseven Edge connector and generates all other required powers internally On-SOM itself. -

Page 27: Table 4: Qseven Pcb Edge Connector Pin Assignment

& 8 pins through resistors and default populated. It is recommended to use any one place only. GBE_ACT# GPHY_ACTIVITY O, 3.3V CMOS/ Gigabit Ethernet activity status _LED1 4.7K PU LED. GBE_CTREF REL1.1 iWave Systems Technologies Pvt. Ltd. Page 27 of 92... - Page 28 SATA0_TXP) through 0.01uF AC Coupling Capacitors and default not populated. SATA1_TX+ SATA0_TX- Default NC. Note: TODN0_SATA & TODN1_SATA optionally connected this (for SATA0_TXN) through 0.01uF AC Coupling Capacitors and default not populated. SATA1_TX- REL1.1 iWave Systems Technologies Pvt. Ltd. Page 28 of 92...

- Page 29 GPIO for implementing SDIO LED indication. SDIO_CMD SD2_CMD(GP3_ SD2_CMD/ IO, 3.3V CMOS SD2 command. 10K PU SDIO_WP SD2_WP(GP3_2 SD2_WP / I, 3.3V CMOS SD2 write Protect. 10K PU REL1.1 iWave Systems Technologies Pvt. Ltd. Page 29 of 92...

- Page 30 Same signal is also connected On-SOM controller. HDA_BCLK/ SSI_SCK34(GP4_ SSI_SCK34/ O, 3.3V CMOS SSI3/4 Audio transmit clock. I2S_CLK SMB_ALERT# HDA_SDI/ SSI_SDATA3(GP SSI_SDATA3/ I, 3.3V CMOS SSI3 Audio receive data. I2S_SDI 4_10) REL1.1 iWave Systems Technologies Pvt. Ltd. Page 30 of 92...

- Page 31 I, 3.3V CMOS Over current sense input for AC30 USB3.0 port. Note: This pin is connected to CPU USB2_OVC pin through resistor and default populated. USB_4_5_OC USB_P5-/ USB_SSTX1- USB_P4-/ USB_SSRX1- REL1.1 iWave Systems Technologies Pvt. Ltd. Page 31 of 92...

- Page 32 AE31 Note: This pin is connected from CPU USB0_DM pin. USB_P0- USB_HUB1OUT IO, DIFF USB Host Port0 data negative. Note: This pin is connected from On-SOM USB Hub USBDM_DN1 pin. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 32 of 92...

- Page 33 LVDS1_CH2_P DU_LVDS1_CH2_P/ O, 1.8V LVDS LVDS secondary channel LVDS_B2+ AJ20 differential pair2 positive. Note: If HDMI transmitter is supported on SOM, then this pin will become NC. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 33 of 92...

- Page 34 Note: If HDMI transmitter is supported on SOM, then this pin will become NC. eDP0_AUX-/ DU_LVDS0_CLK DU_LVDS0_CLK_N/ O, 1.8V LVDS LVDS primary channel differential LVDS_A_CLK- AG18 clock negative. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 34 of 92...

- Page 35 GP2_I2C_CLK I2C3_SCL IIC3_SCL/ O, 3.3V OD/ I2C3 clock. 1K PU /LVDS_DID_C AJ15 Note: Same signal is optionally connected Qseven edge connector through resistor default populated. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 35 of 92...

- Page 36 DP_AUX+ DP_LANE1-/ Default NC. TMDS_LANE Note: HDMI differential data lane 1 negative (HDMI_D1M) signal from HDMI Transmitter optionally connected to this pin. DP_AUX- Power Ground. Power Ground. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 36 of 92...

- Page 37 (HDMI_I2C_CLK) signal from HDMI Transmitter is optionally connected to this pin. DP_HDMI_H Default NC. Note: HDMI Hot plug detect (HDMI_HPD) signal from HDMI Transmitter optionally connected to this pin. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 37 of 92...

- Page 38 Power Ground. Power Ground. PCIE3_TX+ PCIE3_RX+ PCIE3_TX- PCIE3_RX- Power Ground. Power Ground. PCIE2_TX+ PCIE2_RX+ PCIE2_TX- PCIE2_RX- UART0_TX SCIFB2_TXD(GP SSI_SDATA8/ O, 3.3V CMOS SCIFB2 Serial Communication 4_23) Interface Serial Data Transmitter. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 38 of 92...

- Page 39 General purpose input/output 6. GPIO6 AA31 192 LPC_LDRQ#/ Q7_GPIO7_(GP4 SSI_SCK5/ IO, 3.3V CMOS General purpose input/output 7. GPIO7 _14) 193 VCC_RTC VRTC_3V0 I, 3V Power 3V backup coin cell input for RTC. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 39 of 92...

- Page 40 SPI Serial clock (MSIOF0). 5_12) 204 MFG_NC4 JTAG_TRSTB Default NC. Note: Optionally CPU TRST# pin is connected to this pin through 1.8V to 3.3V level translator and default not populated. 205 VCC_5V_SB REL1.1 iWave Systems Technologies Pvt. Ltd. Page 40 of 92...

- Page 41 ¹ Important Note: These signals are also used for RZ/G1H CPU bootstrap setting on SOM and so no external loads or pull-up/pull-down resistors connected to these pins which will change the boot configuration. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 41 of 92...

-

Page 42: Expansion Connector1 Interfaces

The interfaces which are available at 80pin Expansion Connector1 are explained in following sections. Figure 4: Expansion Connector1 Number of Pins - 80 Connector Part Number - DF17(2.0)-80DP-0.5V(57) Mating Connector - DF17(3.0)-80DS-0.5V(57) from Hirose Staking Height - 5mm REL1.1 iWave Systems Technologies Pvt. Ltd. Page 42 of 92... -

Page 43: Parallel Camera Interfaces

8bit and VIN2 are multiplexed in same pins and so VIN2 cannot be supported when VIN1 is supported in 16bit mode. If VIN1 is supported in 8bit mode, then VIN2 also can be supported in 8bit mode. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 43 of 92... -

Page 44: Table 6: Expansion Connector1 Pin Assignment

Video Input Channel0 data bit1 (in 8bit mode) [or] Video Input Channel1 blue data bit1 (in 16bit mode). VI2_G6(GP1_6) A22/ I, 3.3V CMOS Video Input Channel2 green data bit6 (in 8bit mode). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 44 of 92... - Page 45 Video Input Channel3 data bit0 (in 8bit mode) [or] Video Input Channel0 green data bit4 (in 16bit mode). Power Ground. VI3_CLK(GP1_23) EX_WAIT0/ I, 3.3V CMOS Video Input Channel3 pixel clock (in 8bit mode). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 45 of 92...

- Page 46 (in 16bit mode). Power Ground. VI3_DATA7(GP0_7) I, 3.3V CMOS Video Input Channel3 data bit7 (in 8bit mode). VI0_G2(GP0_10) D10/ I, 3.3V CMOS Video Input Channel0 green data bit2 (in 16bit mode). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 46 of 92...

- Page 47 Channel0 green data bit5 (in 16bit mode). VI1_B3/VI1_DATA3(GP3_3) SD0_DAT1/ I, 3.3V CMOS Video Input Channel1 data bit3 (GroupB) (in 8bit mode) [or] Video Input Channel1 blue data bit3 (GroupB) (in 16bit mode). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 47 of 92...

- Page 48 Channel0 blue data bit3 (in 16bit mode). VI0_CLK(GP2_0) VI0_CLK/ I, 3.3V CMOS/ Video Input Channel0 pixel clock. VI0_G1(GP0_9) I, 3.3V CMOS Video Input Channel0 green data bit1 (in 16bit mode). REL1.1 iWave Systems Technologies Pvt. Ltd. Page 48 of 92...

- Page 49 These signals are also used for On-SOM SPI Flash and so either one interface only can be used at time. These signals are also used for On-SOM EtherAVB PHY interface and so either one interface only can be used at time. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 49 of 92...

-

Page 50: Expansion Connector2 Interfaces

80pin Expansion connector2 are explained in the following sections. Figure 5: Expansion Connector2 Number of Pins - 80 Connector Part Number - DF17(2.0)-80DP-0.5V(57) Mating Connector - DF17(3.0)-80DS-0.5V(57) from Hirose Staking Height - 5mm REL1.1 iWave Systems Technologies Pvt. Ltd. Page 50 of 92... -

Page 51: 10/100Mbps Ethernet

For more details, refer Expansion connector2 pins 2,4,8,10,11,12 & 14 on Table 8 Note: In RZ/G1H Qseven SOM, optionally EtherMAC interface can be directly supported on Expansion Connector2 instead of EtherMAC PHY interface. Please contact iWave for more details. 2.8.2 I2S Audio Interface The RZ/G1H Qseven SOM supports one I2S audio interface port on Expansion connector2. -

Page 52: Data Uart Interface

64 mailboxes in two selectable mailbox mode, Normal mailbox mode and FIFO mailbox mode. To connect external CAN module to this bus, it is necessary to add transceiver in between. For more details, refer Expansion connector2 pins 41 & 45 on Table 8. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 52 of 92... -

Page 53: Spi Interface

Note: In RZ/G1H Qseven SOM, three TPU0 signals (TPU0TO0, TPU0TO1 & TPU0TO2 channels) which are connected to Qseven Edge connector is also connected to Expansion connector2. Please refer Expansion connector2 pin 29, 36 & 37 on Table 8 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 53 of 92... -

Page 54: Table 8: Expansion Connector2 Pin Assignment

ETH_REF_CLK(GP2_23) ETH_REF_CLK/ I, 3.3V CMOS Default NC. AL10 Note: ETH_REF_CLK from EtherMAC is optionally connected to this pin through resistor and default not populated. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 54 of 92... - Page 55 I, 3.3V CMOS Serial Communication Interface AB27 (SCIF2) Serial Data Receiver. GPIO_(GP4_17) SSI_SCK6/ IO, 3.3V CMOS/ General Purpose input/output. 100K PU GPIO/MD19(GP0_31) ¹ A15/MD19 IO, 3.3V CMOS/ General purpose input/output. 10K PD REL1.1 iWave Systems Technologies Pvt. Ltd. Page 55 of 92...

- Page 56 O, 3.3V CMOS/ Pulse Width Modulated Output. 100K PU VTHREF0 VTHREF0/ O, 1.8V Analog Thermal Reference Voltage from RZ/G1H CPU. CAN0_TX(GP4_18) SSI_WS6/ O, 3.3V CMOS/ Transmit output for CAN Channel0. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 56 of 92...

- Page 57 Audio Serial data for SSI channel 0 (SSI_SDATA0) is connected to this pin through resistor default populated. Note: Same signal is optionally connected HDMI Transmitter through resistor and default not populated. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 57 of 92...

- Page 58 PRESETOUT# is connected to this pin through resistor default populated. Note: MLBP_SIG_P is optionally connected to this pin through resistor and default not populated. MSIOF3_SCK(GP5_4) SCIFA2_SCK/ O, 3.3V CMOS SPI serial clock (MSIOF3). AB28 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 58 of 92...

- Page 59 ¹ Important Note: These signals are also used for RZ/G1H CPU bootstrap setting on SOM and so no external loads or pull-up/pull-down resistors to be connected to these pins which will change the boot configuration. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 59 of 92...

-

Page 60: Other Features

SOM. This is optional feature and may not be populated by default. Figure 6: JTAG Header Number of Pins - 20 Connector Part - GRPB102MWCN-RC from Sullins Connector Solutions Mating Connector - LPPB102CFFN-RC from Sullins Connector Solutions REL1.1 iWave Systems Technologies Pvt. Ltd. Page 60 of 92... -

Page 61: Table 9: Jtag Header Pin Assignment

Ground. I, 1.8V CMOS/ Only pull down is provided. 10K PD Note: Optionally this pin is connected to CPU ACK pin (AF13) through resistor and default not populated. Power Ground. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 61 of 92... -

Page 62: Spi Programming Header

2.9.2 SPI Programming Header To program the boot code in to the SPI flash (for the first time or if boot code is corrupted), use iWave’s RZ/G1H SPI Programmer Board through 6pin SPI Flash Programming Header (J4) (or) JTAG debugger through JTAG Header (J3). -

Page 63: Power In Connector (Optional)

CONN HEADER VERT 2CKT 2.5MM 0099990986 2Pin TH FUSE FAST 24VDC 3A SF-0603F300-2 0603 CONN HOUSING 2POS 2.5MM 0050375023 Mating connector SHROUD for P1 CONN FEMALE 22-28AWG 0008701039 Mating connector 2.5MM TIN crimp pin REL1.1 iWave Systems Technologies Pvt. Ltd. Page 63 of 92... -

Page 64: Rz/G1H Pin Multiplexing On Qseven Edge And Expansion Connectors

This table has been prepared by referring Renesas’s RZ/G1H Hardware User Manual. Important Note: It is strongly recommended to use the pin function same as selected in the iWave’s Qseven SOM for iWave’s BSP reusability and to have compatible Qseven modules in future for upgradability. - Page 65 AH15 IIC3_SDA I2C3_SDA IIC3_SDA Thermal SSI_SDATA6 MSIOF0_RX DACK2 IRQ2 HRTS0#_B GP1_29 GP1_29 Trip DU_LVDS0_CL DU_LVDS0_CL AG17 DU_LVDS0_CL DU_LVDS0_CL AG18 LVDS0 DU_LVDS0_C DU_LVDS0_C AJ18 H0_P H0_P DU_LVDS0_C DU_LVDS0_C AJ19 H0_N H0_N REL1.1 iWave Systems Technologies Pvt. Ltd. Page 65 of 92...

- Page 66 DU_LVDS1_C AJ22 H0_N H0_N LVDS1 DU_LVDS1_C DU_LVDS1_C AL21 H1_P H1_P DU_LVDS1_C DU_LVDS1_C AL22 H1_N H1_N DU_LVDS1_C DU_LVDS1_C AJ20 H2_P H2_P DU_LVDS1_C DU_LVDS1_C AJ21 H2_N H2_N DU_LVDS1_C DU_LVDS1_C AG22 H3_P H3_P REL1.1 iWave Systems Technologies Pvt. Ltd. Page 66 of 92...

- Page 67 TX2_B GP0_25 GP0_25 B/VI2_B1_B SSI_SDATA5_ VI2_DATA2_ MSIOF2_SYNC VI0_R6 VI0_R6_B GP0_26 GP0_26 B/VI2_B2_B GPIO's SSI_SDATA6 FMIN_D DU_DR5 GP4_19 GP4_19 MSIOF0_TX DREQ2 HSCK1_B HCTS0#_B GP1_28 GP1_28 DU_EXHSYN SSI_SCK5 SCIFB1_SCK C/DU_HSYN GP4_14 GP4_14 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 67 of 92...

- Page 68 GP0_22 GP0_22 MSIOF1_TXD_ TPU0TO0 GP0_20 GP0_20 SCIFA1_TXD_ TPU0TO1 GP0_21 GP0_21 SCIFA2_TXD_ AK11 PWM1 GP5_30 GP5_30 Debug UART SCIFA2_RXD_ AJ11 PWM2 GP5_31 GP5_31 AG16 TRST# TRST# AE14 JTAG AH14 AH12 AF14 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 68 of 92...

-

Page 69: Table 13: Rz/G1H Cpu Iomux For Expansion Connector1 Interfaces

VI1_VSYNC# SSI_WS78_C GP1_25 GP1_25 (8bit) VI1_HSYNC#_ SSI_SCK78_ DREQ0 VI1_HSYNC# VI2_R7 SSI_WS78_B GP1_24 GP1_24 SD1_WP MMC1_D7 VI1_CLK_B IIC2_SDA_D I2C2_SDA_D GP3_15 GP3_15 VI1_DATA7_ VI2_DATA7_ SD0_WP MMC0_D7 IIC1_SDA_B I2C1_SDA_B GP3_7 GP3_7 B/VI1_B7_B B/VI2_B7_B REL1.1 iWave Systems Technologies Pvt. Ltd. Page 69 of 92... - Page 70 GP1_14 GP1_14 MSIOF3_SC VI3_DATA0 VI0_G4 VI0_G4_B GP0_0 GP0_0 VI3 Input SCIFA0_RTS MSIOF0_SC (8bit) EX_WAIT0 IRQ3 VI3_CLK HRX0_B GP1_23 GP1_23 MSIOF1_RXD_ EX_CS5# CAN0_RX VI3_VSYNC# VI1_G2 VI1_G2_B VI2_R4 IIC1_SDA I2C1_SDA GP1_17 GP1_17 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 70 of 92...

- Page 71 ¹ Important Note: These signals are also used for RZ/G1H CPU bootstrap setting on SOM and so no external loads or pull-up/pull-down resistors to be connected to these pins which will change the boot configuration. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 71 of 92...

-

Page 72: Table 14: Rz/G1H Cpu Iomux For Expansion Connector2 Interfaces

SCIFA1_TXD DU_DG1 GP5_1 GP5_1 AB27 SCIFA2_TXD DU_DB1 IIC2_SDA I2C2_SDA GP5_6 GP5_6 SCIF2 AC27 SCIFA2_RXD DU_DB0 IIC2_SCL I2C2_SCL GP5_5 GP5_5 HCTS0# SSI_SCK9 DU_DB4 GP5_10 GP5_10 HSCIF0 HRTS0# SSI_WS9 DU_DB5 GP5_11 GP5_11 REL1.1 iWave Systems Technologies Pvt. Ltd. Page 72 of 92... - Page 73 ¹ Important Note: These signals are also used for RZ/G1H CPU bootstrap setting on SOM and so no external loads or pull-up/pull-down resistors to be connected to these pins which will change the boot configuration. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 73 of 92...

-

Page 74: Rz/G1H Cpu Reference Schematic

RZ/G1H Qseven SOM Hardware User Guide 2.11 RZ/G1H CPU Reference Schematic RZ/G1H CPU and DDR3 reference schematic is provided below. Important Note: This schematic is provided only for reference without any warranty and support. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 74 of 92... - Page 75 RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 75 of 92...

- Page 76 RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 76 of 92...

- Page 77 RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 77 of 92...

- Page 78 RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 78 of 92...

-

Page 79: Technical Specification

² RZ/G1H Qseven SOM doesn’t support VCC_5V_SB standby voltage input from Qseven Edge Connector. RZ/G1H Qseven SOM use this voltage as backup power source to RTC controller when VCC is off. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 79 of 92... -

Page 80: Power Input Sequencing

VCC rise time to PWGIN rise time ≥ 0 ms PWGIN fall time to VCC fall time ≥ 0 ms VCC fall time to VCC_RTC fall time ≥ 0 ms REL1.1 iWave Systems Technologies Pvt. Ltd. Page 80 of 92... -

Page 81: Power Consumption

0.757A/3.785W it up after 300sec RTC power when no VCC supply is provided VCC_RTC ¹ Power consumption measurements have been done in iWave’s RZ/G1H CPU based Qseven Development platform (iW- G21D-Q74H-3D002G-E004G-LCA) with iWave’s Linux3.10.31 BSP (iW-PREXZ-SC-01-R2.0-REL1.0-Linux3.10.31- PATCH015). REL1.1 iWave Systems Technologies Pvt. Ltd. -

Page 82: Environmental Characteristics

Heat spreader has to be used with application specific thermal solutions like heat sinks, Chassis, fans, Heat pipes etc. iWave supports Heat Sink & Heat Spreader Solution for RZ/G1H Qseven SOM. Please refer the below figures for Heat Sink & Heat Spreader dimension details. For ordering information, refer section 4 ORDERING INFORMATION. -

Page 83: Figure 10: Heat Sink Dimensions

RZ/G1H Qseven SOM Hardware User Guide Figure 10: Heat Sink Dimensions REL1.1 iWave Systems Technologies Pvt. Ltd. Page 83 of 92... -

Page 84: Rohs Compliance

3.2.4 Electrostatic Discharge iWave’s RZ/G1H Qseven SOM is sensitive to electro static discharge and so high voltages caused by static electricity could damage some of the devices on board. It is packed with necessary protection while shipping. Do not open or use the SOM except at an electrostatic free workstation. -

Page 85: Mechanical Characteristics

Figure 12: Mechanical dimension of Qseven SOM- Top View Note: The Qseven PCB cooling plate shown above is to be used as a cooling interface between the Qseven module and the application specific cooling solution. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 85 of 92... -

Page 86: Figure 13: Mechanical Dimension Of Rz/G1H Qseven Som- Bottom View

Header (4.7mm) followed by Inductor (3.12mm) and bottom side maximum height component is expansion connector (4.30mm±0.15mm). Please refer the below figure which gives height details of the RZ/G1H Qseven SOM. Figure 14: Mechanical dimension of RZ/G1H Qseven SOM- Side View REL1.1 iWave Systems Technologies Pvt. Ltd. Page 86 of 92... -

Page 87: Guidelines To Insert The Qseven Som Into Carrier Board

(in the second photo), such that the board is fixed firmly into the expansion connectors. Figure 15: Qseven Module Insertion procedure Note: Photo shown above is for only reference and not exactly represents RZ/G1H Qseven SOM. REL1.1 iWave Systems Technologies Pvt. Ltd. Page 87 of 92... -

Page 88: Ordering Information

The below table provides the standard orderable part numbers for different RZ/G1H Qseven SOM variations. Please contact iWave for orderable part number of higher RAM memory size or Flash memory size SOM configurations. Also if the desired part number is not listed in below table or if any custom configuration part number is required, please contact iWave. -

Page 89: Rz/G1H Qseven Som Configuration Switches

4bit mode only is supported and VIN1 is eMMC 8bit Mode is supported and VIN1 is not supported on Expansion Connector1 supported on Expansion Connector1 Figure 16: Configuration Switches REL1.1 iWave Systems Technologies Pvt. Ltd. Page 89 of 92... -

Page 90: Rz/G1H Spi Programmer Board

RZ/G1H SPI Programmer Board iWave Systems supports RZ/G1H SPI Programmer Board to program the boot code in to the RZ/G1H SOM’s SPI flash. This board can be directly interfaced to RZ/G1H SOM through SPI Flash Programming Header (J4) for programming the boot code in to the SPI flash (for the first time or if boot code is corrupted). -

Page 91: Rz/G1H Qseven Som Development Platform

7. APPENDIX III RZ/G1H Qseven SOM Development Platform iWave Systems supports iW-RainboW-G21D – RZ/G1H Qseven SOM Development Platform which is targeted for quick validation of RZ/G1H CPU based Qseven SOM and its features. Being a Nano-ITX form factor with 120mm x 120mm size, the carrier board is highly packed with all necessary interfaces &... - Page 92 RZ/G1H Qseven SOM Hardware User Guide REL1.1 iWave Systems Technologies Pvt. Ltd. Page 92 of 92...

Need help?

Do you have a question about the iW-RainboW-G21M and is the answer not in the manual?

Questions and answers