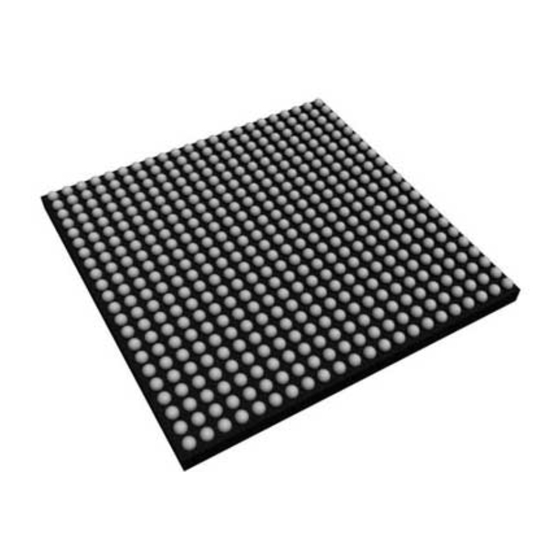

Microsemi SmartFusion2 User Manual

Soc fpga and igloo2 fpga fabric

Hide thumbs

Also See for SmartFusion2:

- User manual (829 pages) ,

- Demo manual (40 pages) ,

- Configuration manual (23 pages)

Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Need help?

Do you have a question about the SmartFusion2 and is the answer not in the manual?

Questions and answers