Table of Contents

Advertisement

Quick Links

Download this manual

See also:

User Manual

Freescale Semiconductor

Technical Data

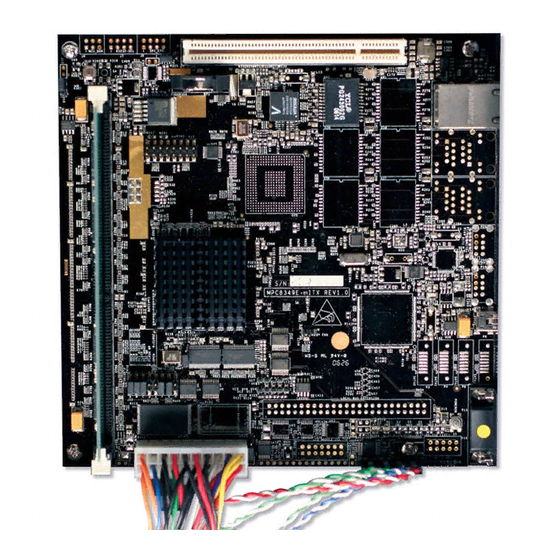

MPC8349E PowerQUICC™ II Pro

Integrated Host Processor Hardware

Specifications

The MPC8349E PowerQUICC™ II Pro is a next generation

PowerQUICC II integrated host processor. The MPC8349E

contains a PowerPC™ processor core built on Power

Architecture™ technology with system logic for

networking, storage, and general-purpose embedded

applications. For functional characteristics of the processor,

refer to the MPC8349E PowerQUICC™ II Pro Integrated

Host Processor Reference Manual.

To locate published errata or updates for this document, refer

to the MPC8349E product summary page on our website

listed on the back cover of this document or, contact your

local Freescale sales office.

The information in this document is accurate for

revision 1.1 silicon and earlier. For information on

revision 3.0 silicon and later versions (for orderable

part numbers ending in A or B), see the

MPC8349EA PowerQUICC™ II Pro Integrated

Host Processor Hardware Specifications.

See

Section 23.1, "Part Numbers Fully Addressed

by This Document,"

determination.

© Freescale Semiconductor, Inc., 2005-2007. All rights reserved.

NOTE

for silicon revision level

Document Number: MPC8349EEC

Rev. 10, 07/2007

Contents

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . 7

3. Power Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 10

4. Clock Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5. RESET Initialization . . . . . . . . . . . . . . . . . . . . . . . . . 13

6. DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7. DUART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

9. USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

10. Local Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

11. JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2

C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

13. PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

14. Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

15. GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

16. IPIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

17. SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

18. Package and Pin Listings . . . . . . . . . . . . . . . . . . . . . 54

19. Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

20. Thermal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

21. System Design Information . . . . . . . . . . . . . . . . . . . 79

22. Document Revision History . . . . . . . . . . . . . . . . . . . 83

23. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 85

Advertisement

Table of Contents

Summary of Contents for Freescale Semiconductor MPC8349E PowerQUICC II Pro

-

Page 1: Table Of Contents

23. Ordering Information ......85 MPC8349EA PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications. Section 23.1, “Part Numbers Fully Addressed by This Document,” for silicon revision level determination. © Freescale Semiconductor, Inc., 2005–2007. All rights reserved. -

Page 2: Overview

— DRAM chip configurations from 64 Mbit to 1 Gbit with x8/x16 data ports — Full error checking and correction (ECC) support — Page mode support (up to 16 simultaneous open pages) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 3 — Selectable hardware-enforced coherency — Address translation units for address mapping between host and peripheral — Dual address cycle for target — Internal configuration registers accessible from PCI MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 4 – USB root hub with one downstream-facing port – Enhanced host controller interface (EHCI) compatible – High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 5 — On-chip digital filtering rejects spikes on the bus — System initialization data optionally loaded from I C-1 EPROM by boot sequencer embedded hardware • DMA controller MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 6 — Software watchdog timer — Eight general-purpose timers • Designed to comply with IEEE Std. 1149.1™, JTAG boundary scan • Integrated PCI bus and SDRAM clock generation MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 7: Electrical Characteristics

Figure on the PCI interface can overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 3. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 8 Not to Exceed 10% of t interface Note: 1. t refers to the clock period associated with the bus clock interface. interface Figure 2. Overshoot/Undershoot Voltage for GV MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 9: Power Sequencing

To minimize the time that I/O pins are actively driven, it is recommended to apply core voltage before I/O voltage and assert PORESET before the power supplies fully ramp up. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 10: Power Characteristics

Maximum power is based on a voltage of V = 1.2 V, worst case process, a junction temperature of T = 105°C, and an artificial smoke test. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 11 = 25 pF GMII or TBI 0.06 RGMII or RTBI 0.04 12 MHz 0.01 Multiply by 2 if using 2 ports. 480 MHz Other I/O 0.01 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 12: Clock Input Timing

5. The CLKIN/PCI_CLK driver’s closed loop jitter bandwidth should be <500 kHz at –20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 13: Reset Initialization

Input setup time for POR configuration signals — PCI_SYNC_IN (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the MPC8349E is in PCI agent mode MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 14 8:1 ratio results in the maximum. 2. The csb_clk is determined by the CLKIN and system PLL ratio. See Section 19, “Clocking.” MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 15: Ddr Sdram

1. This parameter is sampled. GV = 2.5 V ± 0.125 V, f = 1 MHz, T = 25°C, V = GV /2, V (peak-to-peak) = 0.2 V. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 16: Ddr Sdram Interface

ADDR/CMD output hold with respect to MCK — DDKHAX 333 MHz 2.65 266 MHz 200 MHz MCS(n) output setup with respect to MCK — DDKHCS 333 MHz 3.45 266 MHz 200 MHz MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 17 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8349E. Note that t follows the symbol DDKHMP conventions described in note 1. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 18 Table 15. DDR SDRAM Measurement Conditions Symbol Unit Notes ± 0.31 V 0.5 × GV Notes: 1. Data input threshold measurement point. 2. Data output measurement point. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 19 Unit 4 devices (12 pF) 9 devices (27 pF) 36 devices (108 pF) + 40 pF compensation capacitor 36 devices (108 pF) + 80 pF compensation capacitor MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 20: Duart

2. The middle of a start bit is detected as the 8 sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16 sample. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 21: Ethernet: Three-Speed Ethernet, Mii Management

, in this case, represents the LV symbol referenced in Table 1 Table 2. GMII/MII pins not needed for RGMII or RTBI operation are powered by the OV supply. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 22 GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). 2. This symbol represents the external GTX_CLK125 signal and does not follow the original symbol naming convention. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 23 For example, the subscript of t represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 24 For example, the subscript of t represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 25 R (rise) or F (fall). Figure 10 provides the AC test load for TSEC. = 50 Ω Output = 50 Ω Figure 10. TSEC AC Test Load MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 26 (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). 2. This symbol represents the external GTX_CLK125 and does not follow the original symbol naming convention MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 27 2. Setup and hold time of even numbered RCG are measured from the riding edge of PMA_RX_CLK1. Setup and hold times of odd-numbered RCG are measured from the riding edge of PMA_RX_CLK0. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 28 5. Duty cycle reference is LV 6. This symbol represents the external GTX_CLK125 and does not follow the original symbol naming convention. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 29 (At PHY) RXD[8:5][3:0] RXD[8:5] RXD[3:0] RXD[7:4] RXD[7:4][3:0] SKRGT RXD[4] RXD[9] RX_CTL RXDV RXERR SKRGT RX_CLK (At PHY) Figure 14. RGMII and RTBI AC Timing and Multiplexing Diagrams MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 30 Input low current = Max = 0.5 V –600 — Note: 1. The symbol V , in this case, represents the LV symbol referenced in Table 1 Table MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 31 333 MHz, the delay is 58 ns). Figure 15 shows the MII management AC timing diagram. MDCR MDCH MDCF MDIO (Input) MDDVKH MDDXKH MDIO (Output) MDKHDX Figure 15. MII Management Interface Timing Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 32: Usb

5. For active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 33 AC test load and signals for the USB, respectively. = 50 Ω Output = 50 Ω Figure 16. USB AC Test Load USB0_CLK/USB1_CLK/DR_CLK USIXKH USIVKH Input Signals USKHOV USKHOX Output Signals: Figure 17. USB Signals MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 34: Local Bus

Local bus clock to data valid for LAD/LDP — LBKHOV2 Local bus clock to address valid for LAD — LBKHOV3 Output hold from local bus clock (except LAD/LDP and LALE) — LBKHOX1 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 35 LALE output fall to LAD output transition (LATCH hold time) — LBOTOT1 LALE output fall to LAD output transition (LATCH hold time) — LBOTOT2 LALE output fall to LAD output transition (LATCH hold time) — LBOTOT3 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 36 9. DLL bypass mode is not recommended for use at frequencies above 66 MHz. Figure 18 provides the AC test load for the local bus. = 50 Ω Output = 50 Ω Figure 18. Local Bus C Test Load MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 37 Input Signal: LGTA LBKHOV Output Signals: LSDA10/LSDWE/LSDRAS/ LSDCAS/LSDDQM[0:3] LBKHOZ LA[27:31]/LBCTL/LBCKE/LOE LBKHOV Output Signals: LAD[0:31]/LDP[0:3] LBKLOV LBOTOT LALE Figure 20. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 38 Input Signals: LAD[0:31]/LDP[0:3] (DLL Bypass Mode) LBKHOZ LBKHOV UPM Mode Output Signals: LCS[0:3]/LBS[0:3]/LGPL[0:5] Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Bypass Mode) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 39 Input Signals: LAD[0:31]/LDP[0:3] (DLL Bypass Mode) LBKHOZ LBKHOV UPM Mode Output Signals: LCS[0:3]/LBS[0:3]/LGPL[0:5] Figure 23. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Bypass Mode) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 40 UPM Mode Input Signal: LUPWAIT LBIXKH1 LBIVKH1 Input Signals: LAD[0:31]/LDP[0:3] LBKHOZ1 LBKHOV1 UPM Mode Output Signals: LCS[0:3]/LBS[0:3]/LGPL[0:5] Figure 24. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (DLL Enabled) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 41: Jtag

Input setup times: — Boundary-scan data JTDVKH — TMS, TDI JTIVKH Input hold times: — Boundary-scan data JTDXKH — TMS, TDI JTIXKH Valid times: Boundary-scan data JTKLDV JTKLOV MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 42 JTAG clock input timing diagram. JTAG External Clock JTKHKL JTGR JTGF VM = Midpoint Voltage (OV DD /2) Figure 26. JTAG Clock Input Timing Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 43 TDI, TMS Data Valid JTKLOV JTKLOX Output Data Valid JTKLOZ Output Data Valid VM = Midpoint Voltage (OV DD /2) Figure 29. Test Access Port Timing Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 44: I 2 C

Hold time (repeated) START condition (after this period, the first clock — I2SXKL pulse is generated) Data setup time — I2DVKH μs Data hold time: CBUS compatible masters — — I2DXKL C bus devices MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 45 AC timing diagram for the I C bus. I2CF I2DVKH I2KHKL I2CF I2CL I2SXKL I2CR I2SXKL I2CH I2SVKH I2PVKH I2DXKL Figure 31. I C Bus AC Timing Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 46: Pci

3, 4 PCKHOZ Input setup to clock — 3, 5 PCIVKH Input hold from clock — 3, 5 PCIXKH REQ64 to PORESET setup time — clocks PCRVRH MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 47 5. The setup and hold time is with respect to the rising edge of PORESET. Figure 32 provides the AC test load for PCI. = 50 Ω Output = 50 Ω Figure 32. PCI AC Test Load MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 48 Figure 33. PCI Input AC Timing Diagram Figure 34 shows the PCI output AC timing diagram. PCKHOV PCKHOX Output Delay PCKHOZ High-Impedance Output Figure 34. PCI Output AC Timing Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 49: Timers

2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by external synchronous logic. Timer inputs are required to be valid for at least t ns to ensure proper operation. TIWID MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 50: Gpio

2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by external synchronous logic. GPIO inputs must be valid for at least t ns to ensure proper operation. PIWID MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 51: Ipic

2. IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by external synchronous logic. IPIC inputs must be valid for at least t ns to ensure proper operation in edge triggered mode. PICWID MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... -

Page 52: Spi

(first two letters of functional block)(reference)(state)(signal)(state) NIKHOX (NI) for the time SPICLK clock reference (K) goes to the high state (H) until outputs (O) are invalid (X). MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 53 (See Note) NIKHOX Output Signals: SPIMOSI (See Note) Note: The clock edge is selectable on SPI. Figure 37. SPI AC Timing in Master Mode (Internal Clock) Diagram MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 54: Package And Pin Listings

Interconnects Pitch 1.00 mm Module height (typical) 1.46 mm Solder balls 62 Sn/36 Pb/2 Ag (ZU package) 95.5 Sn/0.5 Cu/4Ag (VV package) Ball diameter (typical) 0.64 mm MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 55 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls. 5. Parallelism measurement must exclude any effect of mark on top surface of package. Figure 38. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC8349E TBGA MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 56 AD33, AD34, AE29, AE30, AH32, AH33, AH34, AM33, AJ31, AJ32, AJ33, AJ34, AK32, AK33, AK34, AM34, AL33, AL34, AK31, AH30 PCI2_C/BE[3:0]/PCI1_C/BE[7:4] AC32, AE32, AH31, AL32 PCI2_PAR/PCI1_PAR64 AG34 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 57 Y2, K3, J3, AP2, AN6 MRAS MCAS MCS[0:3] AG2, AG1, AK1, AL4 MCKE[0:1] H3, G1 MCK[0:5] U2, F4, AM3, V3, F2, AN3 MCK[0:5] U3, E3, AN2, V4, E1, AM4 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 58 LGPL0/LSDA10/cfg_reset_source0 AP27 LGPL1/LSDWE/cfg_reset_source1 AL25 LGPL2/LSDRAS/LOE AJ24 LGPL3/LSDCAS/cfg_reset_source2 AN27 LGPL4/LGTA/LUPWAIT/LPBSE AP28 LGPL5/cfg_clkin_div AL26 LCKE AM27 LCLK[0:2] AN28, AK26, AP29 LSYNC_OUT AM12 LSYNC_IN AJ10 General Purpose I/O Timers GPIO1[0]/GTM1_TIN1/GTM2_TIN2 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 59 GPIO1[10]/GTM1_TGATE4/ GTM2_TGATE3 GPIO1[11]/GTM1_TOUT4/ GTM2_TOUT3 USB Port 1 MPH1_D0_ENABLEN/ DR_D0_ENABLEN MPH1_D1_SER_TXD/ DR_D1_SER_TXD MPH1_D2_VMO_SE0/ DR_D2_VMO_SE0 MPH1_D3_SPEED/DR_D3_SPEED MPH1_D4_DP/DR_D4_DP MPH1_D5_DM/DR_D5_DM MPH1_D6_SER_RCV/ DR_D6_SER_RCV MPH1_D7_DRVVBUS/ DR_D7_DRVVBUS MPH1_NXT/DR_SESS_VLD_NXT MPH1_DIR_DPPULLUP/ DR_XCVR_SEL_DPPULLUP MPH1_STP_SUSPEND/ DR_STP_SUSPEND MPH1_PWRFAULT/ DR_RX_ERROR_PWRFAULT MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 60 MPH0_PWRFAULT/DR_RX_VALIDH MPH0_PCTL0/DR_LINE_STATE0 MPH0_PCTL1/DR_LINE_STATE1 MPH0_CLK/DR_RX_VALID Programmable Interrupt Controller MCP_OUT AN33 IRQ0/MCP_IN/GPIO2[12] IRQ[1:5]/GPIO2[13:17] C22, A22, D21, C21, B21 IRQ[6]/GPIO2[18]/CKSTOP_OUT IRQ[7]/GPIO2[19]/CKSTOP_IN Ethernet Management Interface EC_MDC EC_MDIO Gigabit Reference Clock EC_GTX_CLK125 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 61 TSEC2_RX_CLK TSEC2_RX_DV/GPIO1[23] TSEC2_RXD[7:4]/GPIO1[26:29] A13, B13, C13, A12 TSEC2_RXD[3:0]/GPIO1[13:16] D7, A6, E8, B7 TSEC2_RX_ER/GPIO1[25] TSEC2_TXD[7]/GPIO1[31] TSEC2_TXD[6]/ DR_XCVR_TERM_SEL TSEC2_TXD[5]/ DR_UTMI_OPMODE1 TSEC2_TXD[4]/ DR_UTMI_OPMODE0 TSEC2_TXD[3:0]/GPIO1[17:20] B5, A5, F8, B6 TSEC2_TX_ER/GPIO1[24] TSEC2_TX_EN/GPIO1[12] MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 62 SPIMOSI AN32 SPIMISO AP33 SPICLK AK30 SPISEL AL31 Clocks PCI_CLK_OUT[0:7] AN9, AP9, AM10, AN10, AJ11, AP10, AL11, AM11 PCI_SYNC_IN/PCI_CLOCK AK12 PCI_SYNC_OUT AP11 RTC/PIT_CLOCK AM32 CLKIN JTAG TRST MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 63 Power for DDR R6, T6, U5, V1, W5, Y5, AA4, AB3, AC4, DRAM I/O AD5, AF3, AG5, AH2, AH5, AH6, AJ6, voltage AK6, AK8, AK9, AL6 (2.5 V) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 64 6. This pin must always be tied to GND. 7. This pin must always be pulled up to OV 8. This pin must always be left not connected. 9. Thermal sensitive resistor. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 65: Clocking

PCI agent devices in the system, to allow the MPC8349E to function. When the MPC8349E is configured as a PCI agent device, PCI_CLK is the primary input clock and the CLKIN signal should be tied to GND. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 66 Off, csb_clk, csb_clk/2, csb_clk/3 Security core csb_clk/3 Off, csb_clk, csb_clk/2, csb_clk/3 csb_clk/3 Off, csb_clk, csb_clk/2, csb_clk/3 USB DR, USB MPH PCI1, PCI2 and DMA complex csb_clk Off, csb_clk MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 67 0010 × 2 0011 × 3 0100 × 4 0101 × 5 0110 × 6 0111 × 7 1000 × 8 1001 × 9 1010 × 10 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 68 (CLKIN or PCI_CLK) and the internal coherent system bus clock (csb_clk). Table 55 Table 56 show the expected frequency values for the CSB frequency for select csb_clk to CLKIN/PCI_SYNC_IN ratios. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 69 8 : 1 CFG_CLKIN_DIV selects the ratio between CLKIN and PCI_SYNC_OUT. CLKIN is the input clock in host mode; PCI_CLK is the input clock in agent mode. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 70 RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (csb_clk) and the e300 core clock (core_clk). Table 57 shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in Table 57 should be considered as reserved. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 71 Core VCO frequency = core frequency × VCO divider. The VCO divider must be set properly so that the core VCO frequency is in the range of 800–1800 MHz. 19.3 Suggested PLL Configurations Table 58 shows suggested PLL configurations for 33 and 66 MHz input clocks. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 72 The PLL configuration reference number is the hexadecimal representation of RCWL, bits 4–15 associated with the SPMF and COREPLL settings given in the table. The input clock is CLKIN for PCI host mode or PCI_CLK for PCI agent mode. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 73: Thermal

Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance An estimation of the chip junction temperature, T , can be obtained from the equation: × P + (R θ MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 74 ) to determine the junction temperature and a measure of the temperature at the top center of the package case using the following equation: Ψ × P where: = junction temperature (°C) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 75 AAVID 31 × 35 × 23 mm pin fin Natural convection AAVID 31 × 35 × 23 mm pin fin 1 m/s AAVID 31 × 35 × 23 mm pin fin 2 m/s MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 76 Millennium Electronics (MEI) 408-436-8770 Loroco Sites 671 East Brokaw Road San Jose, CA 95112 Internet: www.mei-thermal.com Tyco Electronics 800-522-2800 Chip Coolers™ P.O. Box 3668 Harrisburg, PA 17105-3668 Internet: www.chipcoolers.com MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 77 From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 78 × P + (R θ where: = junction temperature (°C) = case temperature of the package (°C) = junction-to-case thermal resistance (°C/W) θ = power dissipation (W) MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 79: System Design Information

PLL power supply filter circuit. 10 Ω (or L2AV 2.2 µF 2.2 µF Low ESL Surface Mount Capacitors Figure 40. PLL Power Supply Filter Circuit MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 80 /2. R then becomes the resistance of the pull-up devices. R and R are designed to be close to each other in value. Then, Z = (R )/2. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 81 PORESET deasserts. Then the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 82 C pins, the Ethernet Management MDIO pin, and IPIC interrupt pins. For more information on required pull-up resistors and the connections required for the JTAG interface, refer to application note AN2931, PowerQUICC™ Design Checklist. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 83: Document Revision History

Table 58, “Suggested PLL Configurations:” Removed some values from suggested PLL configurations for reference numbers 902, 922, 903, and 923. Table 65, “Part Numbering Nomenclature:” Updated TBD values in note 1. Added Table 66 “SVR Settings.” MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 84 Table 1: Typical values for power dissipation are changed to ‘TBD.’ 4/2005 Table 1: Addition of note 1. Table 51: Addition of Therm0 (K32). 4/2005 Initial release. MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

-

Page 85: Ordering Information

Table 64 shows the SVR settings by device and package type. Table 64. SVR Settings Device Package SVR (Rev. 1.0) MPC8349E TBGA 8050_0010 MPC8349 TBGA 8051_0010 MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor... - Page 86 ATWLYYWW is the traceability code. CCCCC is the country code. MMMMM is the mask number. YWWLAZ is the assembly traceability code. Figure 42. Freescale Part Marking for TBGA Devices MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 87 Ordering Information THIS PAGE INTENTIONALLY LEFT BLANK MPC8349E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 10 Freescale Semiconductor...

- Page 88 Headquarters surgical implant into the body, or other applications intended to support or sustain life, ARCO Tower 15F or for any other application in which the failure of the Freescale Semiconductor product 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 could create a situation where personal injury or death may occur. Should Buyer...

Need help?

Do you have a question about the MPC8349E PowerQUICC II Pro and is the answer not in the manual?

Questions and answers