Table of Contents

Advertisement

Quick Links

Features

■

Pin and function compatible with CY7C1041CV33

■

High speed

❐

t

= 10 ns

AA

■

Low active power

❐

I

= 90 mA at 10 ns (industrial)

CC

■

Low CMOS standby power

❐

I

= 10 mA

SB2

■

2.0V data retention

■

Automatic power down when deselected

■

TTL compatible inputs and outputs

■

Easy memory expansion with CE and OE features

■

Available in Pb-free 48-ball VFBGA, 44-pin (400-mil) molded

SOJ, and 44-pin TSOP II packages

Logic Block Diagram

Note

1. For guidelines on SRAM system design, refer to the "System Design Guidelines" Cypress application note, available at www.cypress.com.

Cypress Semiconductor Corporation

Document #: 38-05473 Rev. *E

INPUT BUFFER

A

0

A

1

A

2

A

3

A

256K × 16

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

•

198 Champion Court

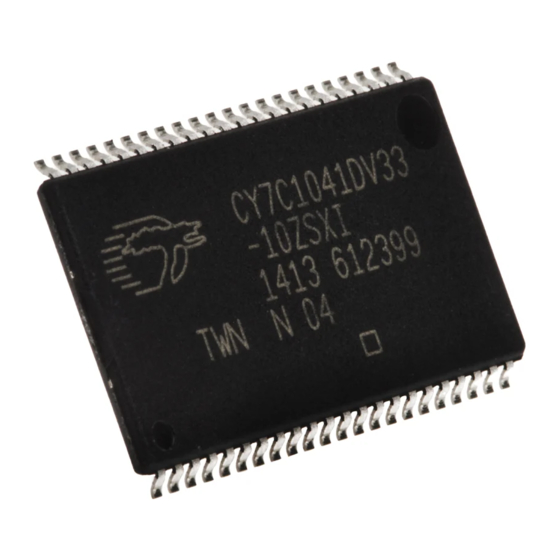

4 Mbit (256K x 16) Static RAM

Functional Description

[1]

The CY7C1041DV33

is a high performance CMOS Static RAM

organized as 256K words by 16 bits. To write to the device, take

Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte

LOW Enable (BLE) is LOW, then data from IO pins (IO

is written into the location specified on the address pins (A

A

). If Byte HIGH Enable (BHE) is LOW, then data from IO pins

17

(IO

to IO

) is written into the location specified on the address

8

15

pins (A

to A

).

0

17

To read from the device, take Chip Enable (CE) and Output

Enable (OE) LOW while forcing the Write Enable (WE) HIGH. If

BLE is LOW, then data from the memory location specified by

the address pins appears on IO

from memory appears on IO

page 9 for a complete description of read and write modes.

The input and output pins (IO

impedance state when the device is deselected (CE HIGH),

outputs are disabled (OE HIGH), BHE and BLE are disabled

(BHE, BLE HIGH), or during a write operation (CE LOW and WE

LOW).

The CY7C1041DV33 is available in a standard 44-pin 400-mil

wide SOJ and 44-pin TSOP II package with center power and

ground (revolutionary) pinout and a 48-ball fine-pitch ball grid

array (FBGA) package.

IO

–IO

0

7

IO

–IO

8

15

BHE

WE

CE

OE

BLE

,

•

San Jose

CA 95134-1709

CY7C1041DV33

to IO

0

to IO

. If BHE is LOW, then data

0

7

to IO

. See the

Truth Table

8

15

to IO

) are placed in a high

0

15

•

408-943-2600

Revised July 17, 2008

)

7

to

0

on

[+] Feedback

[+] Feedback

Advertisement

Table of Contents

Summary of Contents for Cypress Semiconductor CY7C1041DV33

-

Page 1: Functional Description

(BHE, BLE HIGH), or during a write operation (CE LOW and WE LOW). The CY7C1041DV33 is available in a standard 44-pin 400-mil wide SOJ and 44-pin TSOP II package with center power and ground (revolutionary) pinout and a 48-ball fine-pitch ball grid array (FBGA) package. - Page 2 4. Pinout 1 is compliant with CY7C1041CV33 and pinout 2 is JEDEC compliant. The difference between the two is that the higher and lower byte IOs (IO balls) are swapped. Document #: 38-05473 Rev. *E –10 (Industrial) Figure 1. 44-Pin SOJ/TSOP II Figure 3. 48-Ball VFBGA (Pinout 2) CY7C1041DV33 –12 (Automotive) Unit [3, 4] [7:0] Page 2 of 13...

-

Page 3: Maximum Ratings

, f = f Max V CE > V – 0.3V, > V – 0.3V, or V < 0.3V, f = 0 CY7C1041DV33 Ambient Speed Temperature 3.3V ± 0.3V –40°C to +85°C 10 ns 3.3V ± 0.3V –40°C to +125°C 12 ns –10 (Industrial) -

Page 4: Notes

Still Air, soldered on a 3 × 4.5 inch, four layer printed circuit board 3.0V 50 Ω 30 pF* 1.5V Rise Time: 1 V/ns 351Ω AC Test Loads and Waveforms CY7C1041DV33 Unit FBGA TSOP II Unit Package Package Package °C/W 27.89... -

Page 5: Document #: 38-05473 Rev. *E

AC Test Loads and is less than t is less than t HZCE LZCE HZOE LZOE HZBE CY7C1041DV33 –12 (Automotive) Unit Waveforms. Transition is measured when the outputs enter is less than t , and t is less than t for any given... -

Page 6: Notes

[16, 17] Figure 4. Read Cycle No. 1 and t HZWE > 50 μs or stable at V > 50 μs. to V CC(min.) CC(min.) CY7C1041DV33 [14] Ind’l Auto 3.0V DATA VALID Page 6 of 13 Unit [+] Feedback [+] Feedback... -

Page 7: Document #: 38-05473 Rev. *E

19. Data IO is high impedance if OE or BHE and BLE = V 20. If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high impedance state. Document #: 38-05473 Rev. *E LZOE LZBE DATA VALID CY7C1041DV33 [17, 18] HZOE HZCE HZBE HIGH... -

Page 8: Document #: 38-05473 Rev. *E

NOTE 21 HZOE Note 21. During this period the IOs are in the output state and input signals should not be applied. Document #: 38-05473 Rev. *E DATA VALID CY7C1041DV33 [19, 20] Page 8 of 13 [+] Feedback [+] Feedback... -

Page 9: Document #: 38-05473 Rev. *E

Read Upper Bits Only Data In Write All Bits High-Z Write Lower Bits Only Data In Write Upper Bits Only High-Z Selected, Outputs Disabled CY7C1041DV33 LZWE Mode Power Standby (I Active (I Active (I Active (I Active (I Active (I... -

Page 10: Document #: 38-05473 Rev. *E

Ordering Information Speed (ns) Ordering Code CY7C1041DV33-10BVI CY7C1041DV33-10BVXI CY7C1041DV33-10BVJXI CY7C1041DV33-10VXI CY7C1041DV33-10ZSXI CY7C1041DV33-12BVXE CY7C1041DV33-12VXE CY7C1041DV33-12ZSXE Please contact your local Cypress sales representative for availability of these parts Package Diagrams Figure 10. 48-Ball VFBGA (6 x 8 x 1 mm) (51-85150) TOP VIEW A1 CORNER 6.00±0.10... -

Page 11: Document #: 38-05473 Rev. *E

Package Diagrams (continued) Figure 11. 44-Pin (400-mil) Molded SOJ (51-85082) Document #: 38-05473 Rev. *E Figure 12. 44-Pin TSOP II (51-85087) CY7C1041DV33 51-85082-*B 51-85087-*A Page 11 of 13 [+] Feedback [+] Feedback... -

Page 12: Document #: 38-05473 Rev. *E

Document History Page Document Title: CY7C1041DV33 4 Mbit (256K x 16) Static RAM Document Number: 38-05473 Orig. of Submission Rev. ECN No. Change 201560 See ECN 233729 See ECN 351117 See ECN 446328 See ECN 480177 See ECN 2541850 VKN/PYRS Document #: 38-05473 Rev. -

Page 13: Document #: 38-05473 Rev. *E

All product and company names mentioned in this document are the trademarks of their respective holders PSoC Solutions psoc.cypress.com General clocks.cypress.com Low Power/Low Voltage Precision Analog LCD Drive image.cypress.com CAN 2.0b Revised July 17, 2008 CY7C1041DV33 psoc.cypress.com/solutions psoc.cypress.com/low-power psoc.cypress.com/precision-analog psoc.cypress.com/lcd-drive psoc.cypress.com/can psoc.cypress.com/usb Page 13 of 13 [+] Feedback [+] Feedback...

Need help?

Do you have a question about the CY7C1041DV33 and is the answer not in the manual?

Questions and answers