Table of Contents

Advertisement

Quick Links

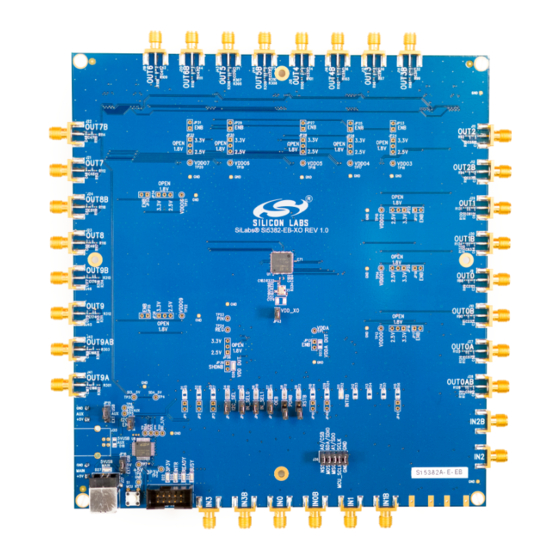

Si5381/82 Evaluation Board User's Guide

The Si5381/82A-E-EB is used for evaluating the Ultra-Low Phase

Noise Quad/Dual PLL. The Si5381/82 employs fourth-generation

DSPLL technology to enable clock generation for LTE/ JESD204B

applications which require the highest level of jitter performance.

The Si5381/82A-E-EB has four independent input clocks and a to-

tal of 12 outputs with 4/2 PLLs. The Si5381/82A-E-EB also has

four independent input clocks and a total of 12 outputs with 2

PLLs. The Si5381/82A-E-EB can be easily controlled and config-

ured using Silicon Labs' Clock Builder Pro™ (CBPro™) software

tool.

The device revision is distinguished by a white 1 inch x 0.187 inch label with the text

"Si5381/82A-E-EB" installed in the lower left hand corner of the board. (For ordering pur-

poses only, the terms "EB" and "EVB" refer to the board and the kit respectively. For the

purpose of this document, the terms are synonymous in context.)

silabs.com | Building a more connected world.

EVB FEATURES

• Powered from USB port or external power

supply

• Onboard 54 MHz XO provides holdover

mode of operation on the Si5381/82

• CBPro GUI programmable VDDO supplies

allow each of the ten primary outputs to

have its own supply voltage selectable

from 3.3, 2.5, or 1.8 V

• CBPro GUI-controlled voltage, current,

and power measurements of VDD and all

VDDO supplies

• Status LEDs for power supplies and

control/status signals of Si5381/82

• SMA connectors for input clocks and

output clocks

Rev. 1.1

Advertisement

Table of Contents

Summary of Contents for Silicon Laboratories Si5381/82

- Page 1 Si5381/82 Evaluation Board User's Guide The Si5381/82A-E-EB is used for evaluating the Ultra-Low Phase EVB FEATURES Noise Quad/Dual PLL. The Si5381/82 employs fourth-generation DSPLL technology to enable clock generation for LTE/ JESD204B • Powered from USB port or external power applications which require the highest level of jitter performance.

-

Page 2: Si5381/82 Functional Block Diagram

See 2. Quick Start and Jumper Defaults 6.1 Installing ClockBuilderPro (CBPro) Desktop Software for more information. Note: All Si5381/82 schematics, BOMs, User’s Guides, and software can be found online at the following link: http://www.silabs.com/ si538x-4x-evb USB +5V... -

Page 3: Quick Start And Jumper Defaults

4. You can use ClockBuilderPro to create, download, and verify a frequency plan on the Si5381/82A-E-EB. 5. Download the Si5381/82 data sheet for more information or go to Clock Development Tools and search for the latest Si5381/82 datasheet. The following table lists the Si5381/82A-E-EB jumper defaults. Table 2.1. Si5381/82A-E-EVB Jumper Defaults* Location... -

Page 4: Status Leds

Main USB +5 V present D27, D22, and D26 are illuminated when USB +5 V, Si5381/82 +3.3 V, and Si5381/82 Output +5 V supply voltages, respectively, are present. D25, D21, and D24 are status LEDs showing on-board MCU activity. D11 and D12 are status indicators from the DUT. -

Page 5: External Reference Input (Xa/Xb)

Si5381/82 Evaluation Board User's Guide External Reference Input (XA/XB) 4. External Reference Input (XA/XB) An external XO is used to produce an ultra-low jitter reference clock for the DSPLL and to provide a stable reference for the free-run and holdover modes. The XO footprint on the Si5381/82A-E-EVB can accommodate both 3.2mm x 5 mm and 2.5 mm x 3.2 mm pack- age sizes. -

Page 6: Clock Input And Output Circuits

Si5381/82 Evaluation Board User's Guide Clock Input and Output Circuits 5. Clock Input and Output Circuits 5.1 Clock Input Circuits (INx/INxB and FB_IN/FB_INB) The Si5381/82A-E-EB has eight SMA connectors (IN0/IN0B–IN2/IN2B and IN3(FB_IN)/IN3B(FB_INB)) for receiving external clock sig- nals. All input clocks are terminated as shown in the figure below. Note input clocks are ac coupled and 50 Ω terminated. This repre- sents four differential input clock pairs. -

Page 7: Using The Si5381/82A-E-Evb And Installing Clockbuilderpro (Cbpro) Desktop Software

Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6. Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.1 Installing ClockBuilderPro (CBPro) Desktop Software To install the CBPro software on any Windows 7 (or above) PC:... - Page 8 In this case, J33 can be used to provide power to the output drivers separately from the main Si5381/82 device supplies. To make this change, move jumper JP15 to connect pins 2-3 “EXT”. Connect J33 to an external 5 V, 0.5 A or higher power source. Make sure that the polarity of the +5 V and GND connections are correct.

- Page 9 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.4 Overview of ClockBuilderPro Applications Note: The following instructions and screen captures may vary slightly depending on your version of ClockBuilder Pro. The ClockBuilderPro installer will install two main applications.

- Page 10 Application 2: Figure 6.5. EVB GUI Use the EVB GUI to do the following: • Download configuration to EVB’s DUT (Si5381/82). • Control the EVB’s regulators. • Monitor voltage, current, power on the EVB. 6.5 Common ClockBuilderPro Work Flow Scenarios There are three common workflow scenarios when using CBPro and the Si5381/82A-E-EB.

- Page 11 Once you open the default plan, a popup will appear. Figure 6.8. CBPro—Write Design Dialog Select “Yes” to write the default plan to the Si5381/82 device mounted on your EVB. This ensures the device on the EVB is configured with the latest parameters from Silicon Labs.

- Page 12 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software Figure 6.9. CBPro—Write Progress Window After CBPro writes the default plan to the EVB, click on “Open EVB GUI” as shown in the figure below. Figure 6.10. CBPro—Open EVB GUI Button The EVB GUI window will appear on the desktop.

- Page 13 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.6.1 Verify Free-Run Mode Operation Assuming no external clocks have yet been connected to the INPUT CLOCK differential SMA connectors, labeled “INx/INxB” and loca- ted around the perimeter of the EVB, the DUT should now be operating in free-run mode and locked to the onboard XO.

- Page 14 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software Your configuration’s design report will appear in a new window, as shown below. Compare the observed output clocks to the frequen- cies and formats noted in your default project’s Design Report.

- Page 15 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.7 Workflow Scenario #2: Modifying the Default Silicon Labs-Created Device Configuration To modify the configuration using the CBPro Wizard, click on the appropriate category. The category may also be selected from a drop- down list by clicking on the “Design Dashboard”...

- Page 16 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software As you edit the settings, you may notice the “Frequency Plan Valid” link in the lower left corner updating. You can click on this link to bring up the design report to confirm that the information is correct.

- Page 17 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.8 Workflow Scenario #3: Testing a User-Created Device Configuration Figure 6.18. CBPro—Open Design Project Link Using the windows file browser popup, locate your CBPro design file (*.slabtimeproj or *.sitproj file).

- Page 18 Si5381/82 Evaluation Board User's Guide Using the Si5381/82A-E-EVB and Installing ClockBuilderPro (CBPro) Desktop Software 6.9 Exporting the Register Map File for Device Programming by a Host Processor You can also export your configuration to a file format suitable for in-system programming by selecting “Export” as shown below: Figure 6.21.

-

Page 19: Writing A New Frequency Plan Or Device Configuration To Non-Volatile Memory (Otp)

7. Writing A New Frequency Plan or Device Configuration to Non-volatile Memory (OTP) The Si5381/82 device loads the Non-Volatile Memory (OTP) on either a powerup or a hard reset, overwriting any previous volatile reg- ister changes. This allows the device to begin functioning as desired on powerup/hard-reset without manual intervention. To restart the device while preserving volatile changes and without loading the OTP, use soft-reset through the registers or EVB-GUI. -

Page 20: Serial Device Communications (Si5381/82 Mcu)

The MCU on-board the Si5381/82A-E-EB communicates with the Si5381/82 device through a 4-wire SPI (Serial Peripheral Interface) link. The MCU is the SPI master and the Si5381/82 device is the SPI slave. The Si5381/82 device can also support a 2-wire I... -

Page 21: Si5381/82-E-Eb Schematic And Bill Of Materials (Bom)

The Si5381/82-E-EB Schematic and Bill of Materials (BOM) can be found online at: http://www.silabs.com/si538x-4x-evb Note: Please be aware the Si5381/82-E-EB schematic is in OrCad Capture hierarchical format and not in a typical “flat” schematic format. silabs.com | Building a more connected world. - Page 22 Trademark Information Silicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, Z-Wave, and others are trademarks or...

Need help?

Do you have a question about the Si5381/82 and is the answer not in the manual?

Questions and answers