Table of Contents

Advertisement

Quick Links

Table of Contents

1

Introduction ......................................................................................................................................................................... 2

2

Features .............................................................................................................................................................................. 2

3

Functional Description ......................................................................................................................................................... 3

3.1. VDD Power Supplies ............................................................................................................................................... 3

3.2. Output Enable .......................................................................................................................................................... 3

4

Power Supply Connections ................................................................................................................................................. 4

5

Setting Output Enable in the EVK ....................................................................................................................................... 5

6

Input Clock Configuration .................................................................................................................................................... 5

7

Configuring EVK for DC Coupled Input LVCMOS Clock ..................................................................................................... 6

7.1. Driving Clock Inputs with LVCMOS Driver (DC coupled) ......................................................................................... 6

8

PCB Schematic ................................................................................................................................................................... 7

8.1. Schematic Sheet1 .................................................................................................................................................... 7

8.2. Schematic Sheet2 .................................................................................................................................................... 8

8.3. Schematic Sheet3 .................................................................................................................................................... 9

SiT92114EB User Manual | Rev 0.5

SiT92114 Evaluation Board (EVB) HW

User Manual

Page 1 of 10

www.sitime.com

Advertisement

Table of Contents

Summary of Contents for SiTime SiT92114

-

Page 1: Table Of Contents

SiT92114 Evaluation Board (EVB) HW User Manual Table of Contents Introduction ..................................2 Features ....................................2 Functional Description ................................. 3 3.1. VDD Power Supplies ............................... 3 3.2. Output Enable ................................3 Power Supply Connections ..............................4 Setting Output Enable in the EVK ............................5 Input Clock Configuration .............................. -

Page 2: Introduction

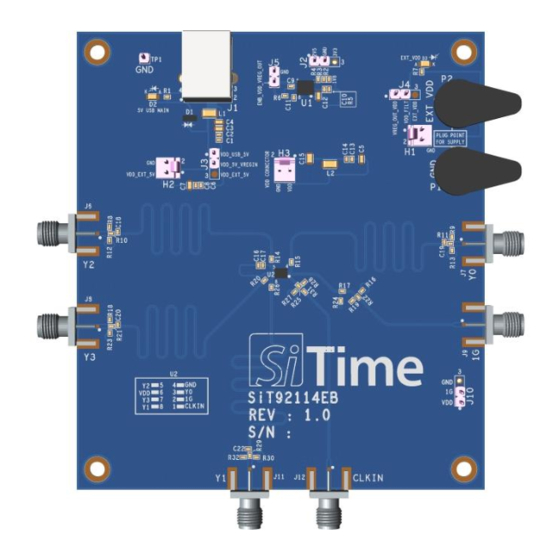

SiT92114 Evaluation Board (EVB) HW User Manual 1 Introduction The SiT92114 Evaluation Board is designed for evaluating the SiT92114, a high-performance LVCMOS ultra low jitter buffer. Figure 1. SiT92114 EVK Board 2 Features High-performance 1:4 LVCMOS clock buffer Very low pin-to-pin skew: <50 ps Very low additive jitter: <50 ps... -

Page 3: Functional Description

3 Functional Description The SiT92114 is a 4-output LVCMOS clock fan out buffer with low additive jitter that can operate up to 200MHz. The output buffer can be Enabled / Disabled via 1G pin. The device is offered in a 8-pin DFN (COL) package. -

Page 4: Power Supply Connections

SiT92114 Evaluation Board (EVB) HW User Manual 4 Power Supply Connections SiT92114 buffer operates on a Single VDD supply. The VDD supply can be 3.3 V ±5%, 2.5 V ±5%, 1.8 V ±10%. The VDD supply can be set as in Table Table 2. -

Page 5: Setting Output Enable In The Evk

SiT92114 Evaluation Board (EVB) HW User Manual 5 Setting Output Enable in the EVK The jumper setting for controlling the output enable are given Table Table 4. Jumper settings to control clock select and output enable Jumper state Logic state... -

Page 6: Configuring Evk For Dc Coupled Input Lvcmos Clock

SiT92114 Evaluation Board (EVB) HW User Manual 7 Configuring EVK for DC Coupled Input LVCMOS Clock 7.1. Driving Clock Inputs with LVCMOS Driver (DC coupled) Single ended clocks should be DC coupled to the CLKIN. This is shown Figure 4. -

Page 7: Pcb Schematic

SiT92114 Evaluation Board (EVB) HW User Manual 8 PCB Schematic 8.1. Schematic Sheet1 Figure 5. Schematic Sheet 1 – DUT Connections SiT92114EB User Manual | Rev 0.5 Page 7 of 10 www.sitime.com... -

Page 8: Schematic Sheet2

SiT92114 Evaluation Board (EVB) HW User Manual 8.2. Schematic Sheet2 Figure 6. Schematic Sheet 2 – USB Connections SiT92114EB User Manual | Rev 0.5 Page 8 of 10 www.sitime.com... -

Page 9: Schematic Sheet3

SiT92114 Evaluation Board (EVB) HW User Manual 8.3. Schematic Sheet3 Figure 7. Schematic Sheet 3 – VDD Supply SiT92114EB User Manual | Rev 0.5 Page 9 of 10 www.sitime.com... - Page 10 © SiTime Corporation February 2024. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Need help?

Do you have a question about the SiT92114 and is the answer not in the manual?

Questions and answers