Table of Contents

Advertisement

Quick Links

Table of Contents

1

Introduction ......................................................................................................................................................................... 2

2

Features .............................................................................................................................................................................. 2

3

Functional Description ......................................................................................................................................................... 3

3.1. VDD and VDDO Power Supplies ............................................................................................................................. 3

3.2. Clock Inputs ............................................................................................................................................................. 3

3.3. Clock States (Input vs Output States) ...................................................................................................................... 4

3.4. Output Enable .......................................................................................................................................................... 4

4

Power Supply Connections ................................................................................................................................................. 4

5

Setting Input Clock Select and Output Enable in the EVK................................................................................................... 5

6

Input Clock Configuration .................................................................................................................................................... 6

7

Configuring for Single ended AC coupled Input Clock ........................................................................................................ 7

7.1. Driving Clock Inputs with LVCMOS Driver (AC coupled) ......................................................................................... 7

8

Configuring EVK for DC Coupled Input LVCMOS Clock ..................................................................................................... 8

8.1. Driving Clock Inputs with LVCMOS Driver (DC coupled) ......................................................................................... 8

8.2. EVK Changes for Driving Clock Inputs with LVCMOS Driver (DC coupled, single ended) ...................................... 8

9

Driving Differential LVDS or LVDS Boost (AC coupled) .................................................................................................... 10

10

Board Configuration for driving DC Coupled LVDS ........................................................................................................... 10

10.1. LVDS (DC coupled) ............................................................................................................................................... 10

11

Board Configuration Required for Driving DC/AC coupled LVPECL ................................................................................. 11

11.1. DC/AC Coupled LVPECL ....................................................................................................................................... 11

12

EVB Snapshot ................................................................................................................................................................... 12

13

PCB Schematic ................................................................................................................................................................. 13

13.1. Schematic Sheet1 .................................................................................................................................................. 13

13.2. Schematic Sheet2 .................................................................................................................................................. 14

13.3. Schematic Sheet3 .................................................................................................................................................. 15

13.4. Schematic Sheet4 .................................................................................................................................................. 16

13.5. Schematic Sheet5 .................................................................................................................................................. 17

13.6. Schematic Sheet6 .................................................................................................................................................. 18

13.7. Schematic Sheet7 .................................................................................................................................................. 19

13.8. Schematic Sheet8 .................................................................................................................................................. 20

SiT92110EB User Manual | Rev 0.5

SiT92110 Evaluation Board (EVB) HW

User Manual

Page 1 of 21

www.sitime.com

Advertisement

Table of Contents

Summary of Contents for SiTime SiT92110

-

Page 1: Table Of Contents

SiT92110 Evaluation Board (EVB) HW User Manual Table of Contents Introduction ..................................2 Features ....................................2 Functional Description ................................. 3 3.1. VDD and VDDO Power Supplies ..........................3 3.2. Clock Inputs ................................3 3.3. Clock States (Input vs Output States) ........................4 3.4. -

Page 2: Introduction

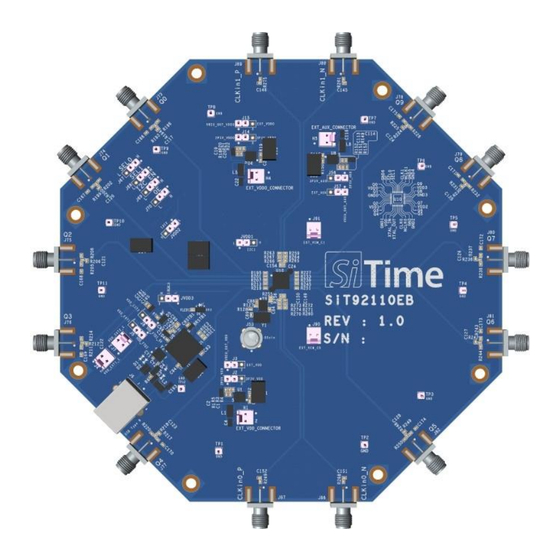

SiT92110 Evaluation Board (EVB) HW User Manual 1 Introduction The SiT92110 Evaluation Board is designed for evaluating the SiT92110, a 10 output LVCMOS low jitter fan out buffer. Figure 1 SiT92110 EVK Board 2 Features Additive jitter performance of 50 fs RMS. -

Page 3: Functional Description

3 Functional Description The SiT92110 is a 10-output LVCMOS clock fan out buffer with low additive jitter that can operate up to 250MHz. It features a 3:1 input multiplexer with an optional crystal oscillator input and ten LVCMOS output. The device is offered in a 32-pin QFN package. -

Page 4: Clock States (Input Vs Output States)

4 Power Supply Connections SiT92110 buffer has two supplies VDD and VDDO. The VDDO supply is dedicated supply for the output LVCMOS drivers. The VDDO supply can be 3.3V+/-5%, 2.5V+/-5%, 1.8V+/-10%, 1.5V+/-10%. The VDD supply is dedicated for the input clock receiver, clock distribution unit and the XO inside SiT92110. -

Page 5: Setting Input Clock Select And Output Enable In The Evk

SiT92110 Evaluation Board (EVB) HW User Manual Table 6 Setting VDDO voltage Jumper setting VDDO (V) J14 shorted between pins 2,3 J14 shorted between pins 1,2 J14 left open Notes: Schematic Sheet2 1. Refer for Jumper J14 connection. 2. VDDO output is set to 3.3V using U4 LDO in the EVK’s default configuration. -

Page 6: Input Clock Configuration

SiT92110 Evaluation Board (EVB) HW User Manual 6 Input Clock Configuration The input clock is ac coupled and terminated with differential 100 Ohms. Thus, the EVK is configured for differential input clock as shown in Schematic Sheet7. Figure 3 Input Clock Configuration SiT92110EB User Manual | Rev 0.5... -

Page 7: Configuring For Single Ended Ac Coupled Input Clock

SiT92110 Evaluation Board (EVB) HW User Manual 7 Configuring for Single ended AC coupled Input Clock Many applications require the buffer to receive single ended input clock. Therefore, some minimal changes need to be done to the EVK to accomplish single ended operation. -

Page 8: Configuring Evk For Dc Coupled Input Lvcmos Clock

Case1: Let us look at the case where a LVCMOS driver (of 50 Ohm impedance) drive a 50 Ohm load which is located at the input of SiT92110. Let the supply of LVCMOS driver be 1.8 V. Then the swing of the clock at the chip input is 0.9 Vpp. We to set the reference voltage at the reference node at 0.45 V. - Page 9 SiT92110 Evaluation Board (EVB) HW User Manual Case2: if load is purely capacitive, then we just need to float the reference node with 0.1uF capacitor attached to it. The reference node is biased internally to VDD/2. Figure 6 Single ended LVCMOS input, DC coupling Capacitive load...

-

Page 10: Driving Differential Lvds Or Lvds Boost (Ac Coupled)

SiT92110 Evaluation Board (EVB) HW User Manual 9 Driving Differential LVDS or LVDS Boost (AC coupled) The input sees a 100 Ohm differential resistance which gives a current path for LVDS or LVDS boost. The 100 Ohm differential signal is followed by AC coupling capacitor of 0.1uF. So, no change in board configuration is required. -

Page 11: Board Configuration Required For Driving Dc/Ac Coupled Lvpecl

SiT92110 Evaluation Board (EVB) HW User Manual 11 Board Configuration Required for Driving DC/AC coupled LVPECL 11.1. DC/AC Coupled LVPECL The LVPECL standard requires a DC path for the input clock driver. The 50 Ohm termination at the receiver is biased with VDDO-2V. -

Page 12: Evb Snapshot

SiT92110 Evaluation Board (EVB) HW User Manual 12 EVB Snapshot Figure 10 EVB Snapshot Block 1 has jumper settings to configure chip VDD as mentioned in Table Block 2 has jumper settings to configure chip VDDO as mentioned in Table 6. -

Page 13: Pcb Schematic

SiT92110 Evaluation Board (EVB) HW User Manual 13 PCB Schematic 13.1. Schematic Sheet1 Figure 11 Schematic Sheet 1 - VDD Input Side Supply SiT92110EB User Manual | Rev 0.5 Page 13 of 21 www.sitime.com... -

Page 14: Schematic Sheet2

SiT92110 Evaluation Board (EVB) HW User Manual 13.2. Schematic Sheet2 Figure 12 Schematic Sheet 2 – VDDO Output Side Supply SiT92110EB User Manual | Rev 0.5 Page 14 of 21 www.sitime.com... -

Page 15: Schematic Sheet3

SiT92110 Evaluation Board (EVB) HW User Manual 13.3. Schematic Sheet3 Figure 13 Schematic Sheet 3 – Auxiliary Supply SiT92110EB User Manual | Rev 0.5 Page 15 of 21 www.sitime.com... -

Page 16: Schematic Sheet4

SiT92110 Evaluation Board (EVB) HW User Manual 13.4. Schematic Sheet4 Figure 14 Schematic Sheet 4 – USB Connection SiT92110EB User Manual | Rev 0.5 Page 16 of 21 www.sitime.com... -

Page 17: Schematic Sheet5

SiT92110 Evaluation Board (EVB) HW User Manual 13.5. Schematic Sheet5 Figure 15 Schematic Sheet 5 – FTDI Connection SiT92110EB User Manual | Rev 0.5 Page 17 of 21 www.sitime.com... -

Page 18: Schematic Sheet6

SiT92110 Evaluation Board (EVB) HW User Manual 13.6. Schematic Sheet6 Figure 16 Schematic Sheet 6 – FTDI to DUT Mapping SiT92110EB User Manual | Rev 0.5 Page 18 of 21 www.sitime.com... -

Page 19: Schematic Sheet7

SiT92110 Evaluation Board (EVB) HW User Manual 13.7. Schematic Sheet7 Figure 17 Schematic Sheet 7 – Input Clock SiT92110EB User Manual | Rev 0.5 Page 19 of 21 www.sitime.com... -

Page 20: Schematic Sheet8

SiT92110 Evaluation Board (EVB) HW User Manual 13.8. Schematic Sheet8 Figure 18 Schematic Sheet 8 – DUT Connection SiT92110EB User Manual | Rev 0.5 Page 20 of 21 www.sitime.com... - Page 21 © SiTime Corporation February 2024. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Need help?

Do you have a question about the SiT92110 and is the answer not in the manual?

Questions and answers