Table of Contents

Advertisement

Quick Links

Document Information

Abstract

The N9H30 hardware development guide is intended for hardware

system designers who require a hardware implementation overview

for N9H30 based system.

The features include a basic 12 MHz external crystal for system

operation, and a crystal of 32.768 kHz for RTC circuitry, USB 2.0

Host reference design, USB 2.0 device reference design, 12-bit

SARADC reference design, I

design, Smart Card Interface, LCD interface and UART (universal

asynchronous receiver/transmitter) connections.

The N9H30 series has rich memory interfaces, SD, eMMC, NAND

Flash, SPI Flash and EBI interface for system booting, data storage

and files accesses.

This design guide can be apply to all N9H30 series packages.

Apply to

N9H30 Series.

The information described in this document is the exclusive intellectual property of

Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller and microprocessor based

system design. Nuvoton assumes no responsibility for errors or omissions.

For additional information or questions, please contact: Nuvoton Technology Corporation.

Jun. 19, 2023

N9H30 Series Hardware Development Guide

Application Note for 32-bit NuMicro

All data and specifications are subject to change without notice.

www.nuvoton.com

Page 1 of 41

®

Family

2

2

C, I

S for audio codec reference

AN0073

Rev 1.01

Advertisement

Table of Contents

Summary of Contents for Nuvoton N9H30 Series

- Page 1 The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. Nuvoton is providing this document only for reference purposes of NuMicro microcontroller and microprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.

-

Page 2: Table Of Contents

AN0073 Table of Contents POWER SUPPLIES....................... 4 1.1 Power Supply Scheme ........................ 4 1.2 RESET ............................6 1.3 Power on setting ........................10 1.4 Power Operating Modes ......................12 CLOCK CIRCUITRY ....................13 2.1 External Crystal Sources ......................13 2.2 PCB Design Guide ........................14 SAR_ADC ........................ - Page 3 AN0073 REFERENCE DESIGN ....................32 Jun. 19, 2023 Page 3 of 41 Rev 1.01...

-

Page 4: Power Supplies

This chapter describes design considerations related to the N9H30 series power supply scheme and power operating modes. Power Supply Scheme The N9H30 series should be supplied by a stabilized power; VDD33, VDD12, MVDD, AVDD, RTCVDD, USB0_VDD, USB1_VDD, USBPLL0, USBPLL1 and PLLVDD Some points need to take care when using these power rails: ... - Page 5 AN0073 The following is power supply scheme of N9H30 series. VDD33 PLL_VDD12 VD33 PLLVD12 10uF 0.1uF 0.1uF 10uF VDD12 USB0_VDD PLLVS PLLVS VD12 USB0_VDD 10uF 0.1uF 0.1uF 10uF MVDD USBPLL0 MVDD USBPLL0VD12 4.7uF 2.2uF 0.1uF 10uF AVDD USB1_VDD USBPLLVS USBPLLVS...

-

Page 6: Reset

AN0073 RESET Hardware Reset Conditions: Power-on Reset (POR) Low level on the nRESET Pin (nRST) Watch-dog time-out reset (WDT) Low voltage reset (LVR) The internal Power on Reset (POR) circuit without any external resistor or capacitor supports a power on ratio within 1V/0.1us~1V/100ms. - Page 7 AN0073 Symbol Parameter Min. Typ. Unit Test Condition AVDD 3.3V power Power Rising 1V/1u AVDD rising from 0V Rate Voltage to 3.3V Active level 1.65 1.82 Power slew rate is 3.3V/20mS. Tpor POR output low duration Table 1.2-2 Power-On Reset at POR33 Figure 1.2-2 Power-On Reset at POR33 Symbol Parameter...

- Page 8 AN0073 Table 1.2-4 Power-On Reset at POR12 The purpose of Watchdog Timer (WDT) is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up system from Idle/Power-down mode. ...

- Page 9 AN0073 The Low Voltage Reset (LVR) and the Low Voltage Detector (LVD) both will generate logic high or logic low output for digital core once the monitored power, VDD, surpasses or falls below their detection level. The block diagram as Figure CHARATERISTICS SYMBOL UNIT...

-

Page 10: Power On Setting

AN0073 Power on setting The power-on setting is used to configure the chip to enter the specified state when the chip is powered up or reset. Since each pin of power on setting has an internal pulled-up resistor when in reset period. If the application needs to set the configuration to “0”, the proper pull-down must be added resisters for corresponding configuration pins. - Page 11 AN0073 Output turn on. Output turn off. Table 1.3-4 System Power-On Setting Guide for Booting Mode NAND Flash Page Size 2K page. 4K page. 8K page. None. Table 1.3-5 System Power-On Setting Guide for NAND Flash Page Size NAND Flash ECC Type BCH 12T.

-

Page 12: Power Operating Modes

AN0073 Power Operating Modes The N9H30 series has four kinds of operating modes: Normal mode: CPU runs normally and all clocks are ON. Idle mode: CPU entering Sleep mode while CPU clock stops and other clocks are ON. -

Page 13: Clock Circuitry

AN0073 2 Clock Circuitry This chapter describes that design considerations for N9H30 series CLK oscillation installation. External Crystal Sources There are two external clock sources for the N9H30 series: Main CLK source with 12 MHz for PLL controller 32.768 kHz CLK source for RTC counter The oscillators of 12 MHZ CLK and RTC_32K are connected with a quartz X’tal and two capacitors... -

Page 14: Pcb Design Guide

Table 2.1-2 32.768 kHz Cin, Cout & Rf Recommend Value PCB Design Guide Applications requiring low power oscillators on the N9H30 series must take PCB layout into consideration. The oscillators on the N9H30 series consume very little current, and it sometimes makes the oscillator circuit sensitive to neighboring circuits. -

Page 15: Sar_Adc

AN0073 3 SAR_ADC This chapter describes design considerations related to the N9H30 ADC. Analog Signals The analog-to-digital converter contains one 12-bit Successive Approximation Register analog- to-digital converter (SAR A/D converter) with eight input channels. The A/D converter supports two operation modes: 4-wire or 5-wire mode. The ADC is especially suitable to act as touch screen controller. - Page 16 AN0073 001 (ADC1) ADC high speed input port. VHS = 1, it supports 1MS/S. VHS = 0, it supports 200KS/S. 010 (ADC2) A low speed input which could support 200KS/S; Keypad signal input pin. 011 (ADC3) VSENSE The input port is intended for 5-wire touch screen detection.

-

Page 17: Input Signal Impedance (Excluding Adc 0)

AN0073 AVDD ADC7 ADC6 8 Channel ADC5 Internal ADC4 SAR ADC ADC3 ADC1 AVDD Keypad ADC2 Resistor divider ADC0 & switch Figure 3.3-1 ADC Functional Block Diagram Input Signal Impedance (Excluding ADC 0) The input current on analog input pins depends on analog input voltage and sampling rate. In the sampling mode, the input current charges the internal sampling capacitor. -

Page 18: High Speed Mode (1 Msps)

AN0073 3.4.1 High Speed Mode (1 MSPS) Csamp = 25.6pF Fclk = 16 MHz Rref: 300 Ron: 20 0.69*(12+1)*Csamp*1.1*(Rsrc+Ron+Rref) < (1/Fclk)*3 → Rsrc < 422 3.4.2 Low Speed Mode (200 KSPS) Csamp = 25.6pF Fclk = 3.2 MHz Rref: 300 Ron: 20... -

Page 19: Key Pad Scan

AN0073 3.4.4 Key Pad Scan This signal is designed for Key Pad Scan from A_2. Figure 3.5.4-1 Key Pads Detection Diagram Note: If a user applies the keypad using this structure and meanwhile, he/she needs the interrupt generator, please make sure Res1≦ 20K and Res2< 5.6*Res1. Moreover, a 0.01uF cap is recommended at A_2 on board. - Page 20 AN0073 A_2 = 1.2375V when K1 switch is pressed. A_2 = 1.4143V when K2 switch is pressed. A_2 = 1.98V when K3 switch is pressed. A_2 = 2.2846V when K4 switch is pressed. A_2 = 2.475V when K5 switch is pressed. A_2 = 2.6053V when K6 switch is pressed.

-

Page 21: Rtc

AN0073 4 RTC The N9H30 series is built-in a Real Time Clock (RTC) which is operated by the independent power supply while the system power is off. The RTC uses a 32.768 kHz external crystal. The following section will describe design considerations related to the N9H30 RTC block. -

Page 22: Usb Bus

AN0073 5 USB Bus The N9H30 is integrated with two USB ports which 1st port (USB0) is supported with USB 1.1 /2.0 device and USB1.1/2.0 Host, and the 2nd one (USB1) is only supported with USB 2.0 Host. USB host function is compliant to Enhanced Host Controller Interface (EHCI) 1.0 specification to connect with USB 2.0 High-Speed (HS) device and compliant to Open Host Controller Interface (OHCI) 1.0 specification to connect with USB 1.1 Full-Speed (FS) and Low-Speed (LS) devices,... -

Page 23: Rext And Usb Power

AN0073 1 = USB port 0 used as a USB host. The value of R1/R2 and C1/C2 depends on the No reserving R/C component if impedance is impedance matching. matching. Figure 5.1-1 Example of USB Device Connection 5.1.2 REXT and USB Power The REXT, an external resistor with precision 12.1 K... - Page 24 AN0073 Use the following general routing and placement guidelines when laying out a new design. These guidelines will help to minimize signal quality and EMI problems. The high speed USB validation efforts focused on a four-layer PCB where the first layer is a signal layer, the second layer is power, the third layer is ground and the fourth is a signal layer.

-

Page 25: Through Hole Consideration For D+ And D

AN0073 split or radiating from the edge of the PCB. Separate signal traces into similar categories and route similar signal traces together (such as routing differential pairs together). Keep high-speed USB signals clear of the core logic set. High current transients are produced during internal state transitions and can be very difficult to filter out. -

Page 26: Signal Trace For D+ And D

USB port. The characteristic impedance should be 50 for full speed USB1.1. For reducing the trace length, the USB terminal should be as close as the USB port of the N9H30 series. Figure 5.2-4 Signal Trace for D+ and D- 5.2.4... -

Page 27: High Speed Usb Trace Length Matching

AN0073 Figure 5.2-5 Multi-Layer PCB USB Bus Trace Space Recommendation Figure 5.2-6 Layer PCB USB Bus Trace Space Recommendation 5.2.5 High Speed USB Trace Length Matching Use the following trace length matching guidelines. High-Speed USB signal pair traces should be trace-length matched. Max trace-length mismatch between High-Speed USB signal pairs (such DM0 and DP0) should be no greater than 150 mils. -

Page 28: Emi/Esd Considerations

AN0073 Figure 5.2-7 4-Layer PCB structures 5.2.8 EMI/ESD Considerations The following guidelines apply to the selection and placement of common mode chokes and ESD protection devices. 5.2.9 EMI - Common Mode Chokes Testing has shown that common mode chokes can provide required noise attenuation. A design may include a common mode choke footprint to provide a stuffing option in the event the choke is needed to pass EMI testing. - Page 29 AN0073 USB0 Device High Speed USB0 Host High Speed Jun. 19, 2023 Page 29 of 41 Rev 1.01...

- Page 30 AN0073 USB1 Host High Speed Figure 5.2-9 USB High Speed Eye-Diagram The eye diagram above shows high speed signal quality, as the common mode impedance increases, this distortion will increase, so you should test the effects of the common mode choke on full speed and high-speed signal quality.

-

Page 31: Esd

AN0073 designer is trying to suppress. 2. Once the designer has a part that gives passing EMI results, the second step is to test the effect this part has on signal quality. Higher impedance common mode chokes generally have a greater damaging effect on signal quality, so be careful about increasing the impedance without doing thorough testing. - Page 32 AN0073 6 Reference Design This chapter shows the NuMaker-HMI-N9H30 board reference design circuit. Figure 5.2-1 N9H30 HMI Demo Board Schematic Block Diagram Figure 5.2-2 GPIO List Jun. 19, 2023 Page 32 of 41 Rev 1.01...

- Page 33 AN0073 Figure 5.2-3 System Power Jun. 19, 2023 Page 33 of 41 Rev 1.01...

- Page 34 AN0073 Figure 5.2-4 N9H30 Figure 5.2-5 Setting, ICE, Reset, Debug, Key Jun. 19, 2023 Page 34 of 41 Rev 1.01...

- Page 35 AN0073 Figure 5.2-6 Memory Jun. 19, 2023 Page 35 of 41 Rev 1.01...

- Page 36 AN0073 Figure 5.2-7 I2S, I2C_0 Jun. 19, 2023 Page 36 of 41 Rev 1.01...

- Page 37 AN0073 Figure 5.2-8 RS_232_2 Jun. 19, 2023 Page 37 of 41 Rev 1.01...

- Page 38 AN0073 Figure 5.2-9 USB Jun. 19, 2023 Page 38 of 41 Rev 1.01...

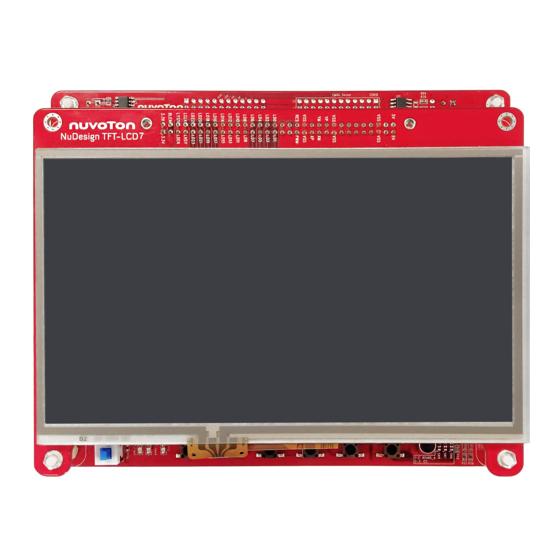

- Page 39 AN0073 Figure 5.2-10 LCD Jun. 19, 2023 Page 39 of 41 Rev 1.01...

- Page 40 AN0073 Revision History Date Revision Description Initial version. 2018.02.12 1.00 Modified format. 2023.06.19 1.01 Updated reference design in chapter 6. Jun. 19, 2023 Page 40 of 41 Rev 1.01...

- Page 41 AN0073 Important Notice Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, “Insecure Usage”.

Need help?

Do you have a question about the N9H30 Series and is the answer not in the manual?

Questions and answers