Table of Contents

Advertisement

Quick Links

Document Information

Abstract

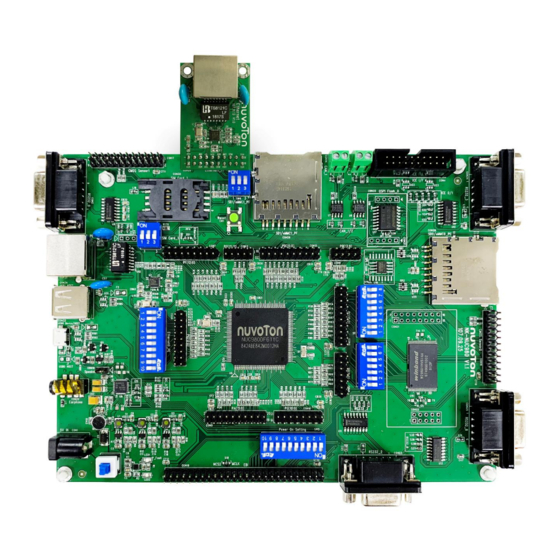

This document introduces how to use the NUC980 series and

describes the minimum hardware resources required to develop a

basic system.

Apply to

NUC980 Series

The information described in this document is the exclusive intellectual property of

Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microprocessor based system

design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

NUC980 Series Hardware Design Guide

Application Note for 32-bit NuMicro

www.nuvoton.com

™

Family

Advertisement

Table of Contents

Summary of Contents for Nuvoton NUC980 Series

- Page 1 The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. Nuvoton is providing this document only for reference purposes of NuMicro microprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.

-

Page 2: Table Of Contents

Table of Contents POWER SUPPLIES ........................ 6 1.1 Power Supply Scheme ........................ 6 1.1.1 NUC980 Power Scheme ........................7 1.2 Power Operating Modes ......................7 1.3 DC Electrical Characteristics ..................... 9 1.4 RTCVDD ............................11 1.4.1 RTC Power Backup & Power Saving .................... 11 RESET ............................ - Page 3 7.2 ADC Selection of Input Signals ....................33 7.3 Selection of Reference Voltage ....................34 7.4 ADC Characteristics ........................35 7.5 Typical Connection and Application Note ................36 USB ............................37 8.1 USB Termination ........................38 8.2 USB REXT and USB Power....................... 40 8.3 PCB Layout Considerations .....................

- Page 4 11.3.4 Recommendations ......................... 64 12 CONTROLLER AREA NETWORK (CAN) INTERFACE .......... 65 12.1 Pin Configuration ........................65 12.2 Reference Connection ....................... 66 12.3 CAN BUS Layout Recommendations ..................67 13 FMI NAND & SD/EMMC INTERFACES ................. 68 13.1 Pin Configuration ........................68 13.2 FMI Reference Connection .......................

- Page 5 USB1.1 FS HOST lite ........................98...

-

Page 6: Power Supplies

1.1 Power Supply Scheme The NUC980 series should be supplied by a stabilized power; VDD33, VDD12, MVDD, AVDD, RTCVDD, USB0_VDD, USB1_VDD, USBPLL0, USBPLL1 and PLLVDD Some points need to take care when using these power rails: ... -

Page 7: Nuc980 Power Scheme

1.1.1 NUC980 Power Scheme VIO_VDD PLLVDD PLLVDD VD33 10uF 0.1uF 0.1uF 10uF VCORE_VDD USB0VDD USB0VDD VD12 0.1uF 10uF 0.1uF 10uF MVDD USB0PLLVDD USBPLL0 MVDD 10uF 0.1uF 0.1uF 10uF AVDD USB1VDD USB1VDD AVDD33 0.1uF 10uF 10uF 0.1uF RTCVDD USB1PLLVDD USBPLL1 RTCVDD PLLVSS AVSS USBPLLVSS... - Page 8 RTC alarm or relative alarm interrupt is active. UART 0/1/2/3/4/5/6/7/8/9 UARTx_nCTS pin toggleed (x is 0, 1, 2, 3, 4, 5, 6, 7, 8 or 9). – – UARTx_RXD pin goes low level (x is 0, 1, 2, 3, 4, 5, 6, 7, 8 or 9). Received data FIFO reached threshold.

-

Page 9: Dc Electrical Characteristics

1.3 DC Electrical Characteristics Table 1-3 DC electrical characteristics Specification Parameter Sym. Test Conditions MIN. TYP. Max. Unit Core Operation voltage 1.14 1.32 DD12 I/O Operation Voltage 2.97 3.63 DD33 Memory I/O Operation Voltage 1.70 1.90 DD (1) for DDR or DDR2 Memory I/O Operation Voltage 2.97 3.63... - Page 10 Specification Parameter Sym. Test Conditions MIN. TYP. Max. Unit System Power Off & RTC V BAT33 VBAT33 Power only...

-

Page 11: Rtcvdd

1.4 RTCVDD NUC980 series is built-in a Real Time Clock (RTC) which is operated by the independent power supply while the system power is off. The RTC uses a 32.768 KHz external crystal. This section will describe that design considerations related to the RTCVDD. -

Page 12: Reset

2 RESET Hardware Reset conditions can be issued by one of the below listed events. For these reset event flags can be read by RSTSTS register. Power-on Reset (POR). Low level on the nRESET Pin (nRST). Watch-dog time-out reset (WDT). ... - Page 13 Figure 2.1-2 Power-On Reset at POR12 Table 2.1-1 POR12 Electrical Characteristics SYMBOL Description Min. Typ. Max. Unit Condition DVDD Power Supply Power rising rate 1V/1us Active level 0.63 0.76 0.86 Power slew rate is 1.2V/20mS@25℃ POR_ENB=0 POR output low duration Power DVDD(rise) at Vrr to POR(rise) at 1/2 DVDD (DVDD slew...

- Page 14 Figure 2.1-3 Power-On Reset at POR33 Table 2.1-2 POR33 Electrical Characteristics SYMBOL Description Min. Typ. Max. Unit Condition DVDD Power Supply Power rising rate 1V/1us Active level 1.65 1.83 Power slew rate is 3.3V/20mS@25℃ POR_ENB=0 POR output low duration Power AVDD(rise) at Vrr to POR(rise) at 1/2 AVDD (AVDD slew...

-

Page 15: Nrst

2.2 nRST Except for typical R & C elements tied to nRST pin is necessary that we also suggest to adding an auxiliary circuit as the following figure to ensure that system robustness. Note. About related components parameters use please refer to the below circuitry shows on. Figure 2.2-1 nRST External CKT Table 2.2-1 nRESET Characteristics Test Conditions... -

Page 16: Wdt

2.3 WDT The purpose of Watchdog Timer (WDT) is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up system from Idle/Power-down mode. ... -

Page 17: Lvr

2.4 LVR The Low Voltage Reset (LVR) and the Low Voltage Detector (LVD) both will generate logic high or logic low output for digital core once the monitored power, VDD, surpasses or falls below their detection level. The block diagram as Figure, Table 2.4-1 Internal LVR/LVD Characteristics Symbol Parameter... -

Page 18: Power Sequence

3 Power sequence 3.1 Power-on Sequence 3.1.1 Condition-1 ≥ T ≥ T If T , the time of delay gap between < 0.5mS is prefer. MVDD CORE Note. The time of delay gap is meaning that timing between T with T core When the time of delay gap <... -

Page 19: Condition-2

3.1.2 Condition-2 ≥ T ≥ T If T , it is acceptable as the below waveform, the time of delay gap CORE MVDD between < 1mS is prefer. Note. The time of delay gap is meaning that timing between T with T core The time of delay gap <... -

Page 20: Power-Down Sequence

3.2 Power-down Sequence The sequence doesn’t care. Note. represents VDD12 powered time for Core power CORE represents MVDD powered time for MVDD power MVDD represents VDD33 powered time for I/O power... -

Page 21: Power On Setting

4 Power on setting The power-on setting is used to configure the chip to enter the specified state when the chip is powered up or reset. Since each pin of power on setting has an internal pulled-up resistor when in reset period. If the application needs to set the configuration to “0”, the proper pull-down must be added resisters for corresponding configuration pins as the figure shown. - Page 22 Table 4-2 System Power-On Setting, SYS_PWRON[2] for SPI Booting Speed Selection Table 4-3 System Power-On Setting, SYS_PWRON[3] for WDT RESET Enable/Disable Table 4-4 System Power-On Setting, SYS_PWRON[5:4] for Debugging...

- Page 23 Table 4-5 System Power-On Setting, SYS_PWRON[9:6] for NAND Type Selection Table 4-6 System Power-On Setting for MISC. type selection...

- Page 24 Table 4-7 System Power-On Setting for USB port0 Host/Device Selection Note. USB0_ID pin has an internal pull-up with 50K Ω around.

-

Page 25: Clock

This section describes that design considerations with CLK oscillation installation. 5.1 External Crystal Sources There are two external clock sources for the NUC980 series: HXT, external 12 MHz high speed crystal input for PLL precise timing operation. LXT, external 32.768 kHz low speed crystal input for RTC function and low speed clock source. -

Page 26: Hxt, High Speed Xtal 12Mhz

5.2 HXT, High Speed XTAL 12MHz C1 and C2 should use high-quality ceramic capacitors, usually C1 with C2 have same value by symmetry. Here, C1/C2 using 15 pF is recommended for resonating with low ESR (≦50 Ω) 12MHz crystal and the crystal’s CL is 12pF around. Typically, PCB layout and NUC980 package capacitances should be calculation, the capacitance can estimate be 2pF around if PCB was 4-layers with FR4 material. -

Page 27: Lxt, Low Speed Xtal 32.768 Khz

5.3 LXT, Low Speed XTAL 32.768 KHz About RTC 32.768KHz oscillation circuit that C1 and C2 are recommended to use high- quality ceramic capacitors. Usually C1 with C2 have same value by symmetry. Using 15 pF is recommended for resonating with 32.768KHz crystal. For getting that accuracy 32.768KHz, typical engineer can operate the timer counter machine to calibrate C1/C2 value or alternative use software method that adjust NUC980 RTC frequency compensation register for approach. -

Page 28: External Bus Interface (Ebi)

6 External Bus Interface (EBI) The EBI supports 8-/16-bit data width have three chip selects that can connect three external devices with different timing setting requirements. EBI supports dedicated external chip select pin with polarity control for each bank, also supports accessible space up to 1 Mbytes for each bank, actually external addressable space is dependent on package pin out. -

Page 29: Ebi Pin Configuration

6.2 EBI Pin Configuration Table 6-2 EBI pin-list EBI_ADDR0 PG.0 MFP1 EBI address bus bit 0. EBI_ADDR1 PG.1 MFP1 EBI address bus bit 1. PG.2 MFP1 EBI_ADDR2 EBI address bus bit 2. PB.2 MFP1 EBI_ADDR3 PG.3 MFP1 EBI address bus bit 3. EBI_ADDR4 PG.6 MFP1... - Page 30 PC.2 MFP1 EBI_DATA2 EBI data bus bit 2. PD.13 MFP8 PC.3 MFP1 EBI_DATA3 EBI data bus bit 3. PD.14 MFP8 PC.4 MFP1 EBI_DATA4 EBI data bus bit 4. PD.15 MFP8 PC.5 MFP1 EBI_DATA5 EBI data bus bit 5. PF.0 MFP8 PC.6 MFP1 EBI_DATA6...

-

Page 31: Ebi Connectivity

EBI_nWE PA.7 MFP1 EBI write enable output pin. 6.3 EBI Connectivity Follow the pin configuration table to connect the EBI bus to connector (as the below example circuitry) for external devices connectivity, such as SRAM, LCD…etc. Figure 6.3.Example Circuitry for EBI devices connection... -

Page 32: Sar_Adc

7 SAR_ADC NUC980 series contains one 12-bit Successive Approximation Register analog-to-digital converter (SAR A/D converter) with 9 input channels. The ADC output coding is offset in binary, 1LSB=VREF/4096, the transfer characteristic is shown in Figure. ADC_OUT ADC_OUT 1111 1111 1111... -

Page 33: Adc Selection Of Input Signals

Table 7.1-1 SAR_ADC interfaces pin-list Group Pin Name GPIO ADC_CH0 PB.0 MFP8 ADC_CH1 PB.1 MFP8 ADC_CH2 PB.2 MFP8 ADC_CH3 PB.3 MFP8 ADC_CH4 PB.4 MFP8 ADC_CH5 PB.5 MFP8 ADC_CH6 PB.6 MFP8 ADC_CH7 PB.7 MFP8 AVREF ADC_VREF 7.2 ADC Selection of Input Signals IN_SEL[3:0] Select Analog... -

Page 34: Selection Of Reference Voltage

200KS/S 1000 VREF ADC low speed input, only support 200KS/S 7.3 Selection of Reference Voltage REF_SEL[1:0] ADC Analog Reference Pair Selection Signals AVSS33 to 2.5V buffer output, or VREF input AVSS33 to AVDD33 01 or 10 Reserved Note. Reference voltage is flexible, and could be selected according to the application. For example, CH0 inputs a sine wave for rail to rail, REF_SEL should be set to 00 or 11. -

Page 35: Adc Characteristics

7.4 ADC Characteristics Symbol Parameter Min. Typ. Max. Unit Test Conditions Resolution is external AVREF Differential Nonlinearity Error ±1 is external AVREF Integral Nonlinearity Error -1.2 is external AVREF Offset Error +3.7 is external AVREF Gain Error (Transfer Gain) -6.6 is external AVREF Absolute Error Monotonic... -

Page 36: Typical Connection And Application Note

7.5 Typical Connection and Application Note As the figure shown that ADC detection supports external channel-0 to channel-7, For avoiding NUC980 be damage and big leakage occurred when ADC_AVDD didn’t powered yet, that voltage detection source VIN input to ADC channel directly is illegal and inhibition. -

Page 37: Usb

8 USB NUC980 integrated 6 USB 1.1 Full Speed Host Lite ports and two USB ports which the USB0 supports USB 2.0 High Speed Dual Role (Host/Device), the USB1 is dedicated support USB 2.0 High Speed Host Controller. About USB Host Lite ports are compliant with USB Revision 2.0 Specification, compatible with OHCI (Open Host Controller Interface) Revision 1.0. -

Page 38: Usb Termination

PE.7 MFP6 PA.13 MFP4 PB.11 MFP4 USBHL5_DM USB host lite port-5 differential signal D-. PF.8 MFP6 PE.8 MFP6 USBHL5 PA.14 MFP4 PB.12 MFP4 USBHL5_DP USB host lite port-5 differential signal D+. PF.9 MFP6 PE.9 MFP6 The following guidelines will provide PCB design considerations for system designer reference. - Page 39 Figure 8.1 Example for USB termination connection...

-

Page 40: Usb Rext And Usb Power

8.2 USB REXT and USB Power The USB REXT signal needs an external resistor with precision 12.1K ohm for preventing any noise interference to the reference bias, the REXT which should be placed close to the pins of NUC980 USB_REXT and USB_VSS as figure shown. Of course PCB design also needs to take care of USB power and ground as the figure shown the USBVDD33, USBVDD12 and USBVSS, they are isolated with ferrite bead and 0 ohm resistor for reducing possible power noise from system. -

Page 41: Pcb Layout Considerations

8.3 PCB Layout Considerations Traces the DP/DM to the connector, the signal swing during high-speed operation on the DP/DM line is relatively a small waveform about 400mV. So, if there is any differential noise picked up will affect transceiver signal on the pair traces. When the DP/DM traces are not shield, the traces behave like an antenna to pick up noise by the surrounding components. - Page 42 common mode) b. Avoid routing of USB signals within 25 mils of any anti-etch to avoid coupling to the next split or radiating from the edge of the PCB. 10. Separate signal traces into similar categories and route similar signal traces together (such as routing differential pairs together).

-

Page 43: Through Hole Consideration For D+ And D

8.3.2 Through Hole Consideration for D+ and D- For the two-layer or multi-layer of PCB, when the signals of D+ and D- need to be through another layer, in which the resistively of through hole should be concerned. To lower the resistively issue for the sensitivity case, the two-via or multi-via should be adapted, as shown in the following figure. -

Page 44: Usb High Speed Trace Spacing

8.3.4 USB High Speed Trace Spacing The following figure provides an illustration of the recommended trace spacing for multi- layer and 2-layer PCB. Maintain parallelism between USB differential signals with the trace spacing needed to achieve 90ohms differential impedance. Deviations will normally occur due to package breakout and routing to connector pins. -

Page 45: High Speed Usb Trace Length

8.3.5 High Speed USB Trace Length Main board’s USB signal pairs total trace length should be less than or equal 18 inches. 8.3.6 PCB Stacking for USB The following is an example of PCB layout stack-up for USB 4-Layer Stack-Up, ... -

Page 46: Usb Emi/Esd Considerations

8.3.7 USB EMI/ESD Considerations The following guidelines apply to the selection and placement of common mode chokes and ESD protection devices. 8.3.8 EMI - Common Mode Chokes Testing has shown that common mode chokes can provide required noise attenuation. A design may include a common mode choke footprint to provide a stuffing option in the event the choke is needed to pass EMI testing. - Page 47 Figure 8.3.8-2 USB Full Speed Figure 8.3.8-3 USB port0 High Speed Device...

- Page 48 Figure 8.3.8-4 USB port0 High Speed HOST Figure 8.3.8-5 USB port1 High Speed HOST...

-

Page 49: Usb Esd Solution

The eye diagram above shows USB signal quality, as the common mode impedance increases, this distortion will increase, so you should test the effects of the common mode choke on full speed and high-speed signal quality. Finding a common mode choke that meets the designer’s needs is a two-step process. 1. -

Page 50: Ethernet

9 Ethernet NUC980 provides 2 Ethernet MAC Controller (EMAC) for Network application. Supports both half and full duplex for 10 Mbps or 100 Mbps operation the EMAC supports RMII (Reduced MII) interface to connect with external Ethernet PHY. Table 9-1 RMII 0/1 interfaces pin-list RMII0_CRSDV PE.1 MFP1... -

Page 51: Rmii Phy Layout Guideline (Refer To Ic+ Ip101G Design Guide)

9.1 RMII PHY layout guideline (refer to IC+ IP101G design guide) Figure 9.1-1 RMII interface connection Block A and B may be better placed as close to magnetic as possible. Let the trace between Ethernet PHY and magnetic as short as possible, and keep the Tx+/-(So as Rx+/-) signal traces to be symmetry. - Page 52 magnetic device with magnetic field should be separated (Isolation) and mounted at 90° to each other. Figure 9.1-2 placement notices for RJ45 to Transformer and RMII...

-

Page 53: Power And Ground

9.2 Power and Ground A). It is better that do not try to partition GND at all. Never use right angle for all partition on power plane or GND plane, so as each signal trace should be. B).No power and GND planes can be underneath the isolated area for the RJ-45 connector and magnetic. -

Page 54: For W & W' Need Better Isolation, Ex: Shielding With Gnd

Figure 9.3.2 PCB trace line width notices for RMII to Transformer Note. D: Line width is as wide as possible in the range of (6mil ~ 12 mil), ex: 8mil. L: Width between differential pair should be small, ex: 4mil. W: Isolation width between TX+/- and RX+/- is as wide as possible, ex: 30mil. -

Page 55: Keep The Distance Between Tx+/- & Rx+/- Differential Pairs For Good Isolation

B) The length of each signal trace shouldn’t exceed 1/20 of the highest harmonic wavelength. For example, for the 25MHz clock trace shouldn’t exceed 30cm and for the 50MHz signal trace shouldn’t exceed 12cm (Tx+/-, Rx+/-). C) De-couple cap should be placed as close to IC as possible, and the traces should be short. Every Ethernet PHY analog/digital power needs de-couple cap and keeps the analog power close to analog GND pin, digital power close to digital GND pin. - Page 56 Ferrite Beads should be as close to IC pins and let it on the rating of 100Ω@100MHz. The ferrite bead between DVDD and AVDD of Ethernet PHY pins should be placed as close to Ethernet PHY as possible, and at the same side as Ethernet PHY, not opposite side.

-

Page 57: Better Analog Performance

9.4 Better Analog Performance A) When using regulator such as 5V to be 3.3V, the rated current of the regulator should be at least 300mA. B) Both Analog GND pins and Digital GND pins must maintain a good GND return path (One GND plane is recommended. -

Page 58: Capture Sensor Interface

10 Capture Sensor Interface The Image Capture Interface is designed to capture image data from a sensor. After capturing or fetching image data, it will process the image data, and then FIFO output them into frame buffer. NUC980 have two sets of CMOS capture sensor interfaces with supporting CCIR601 and CCIR656 type sensor and resolution up to 3M pixels. -

Page 59: Reference Connection

Table 10.1-1 video capture-2 interface pin-list VCAP1_CLKO PE.12 MFP7 Video image interface-1 sensor clock pin. VCAP1_DATA0 PE.2 MFP7 Video image interface-1 data pin. VCAP1_DATA1 PE.3 MFP7 Video image interface-1 data pin. VCAP1_DATA2 PE.4 MFP7 Video image interface-1 data pin. VCAP1_DATA3 PE.5 MFP7 Video image interface-1 data pin. -

Page 60: Pcb Design Considerations

Figure 10.2-2 reference connection with NT99142 CMOS sensor 10.3 PCB Design Considerations Routing sequences: PCLK MCLK Data HREF VSYNC Others Connect GND/AGND and route ground plane as large as possible. Minimum gap between PCLK and MCLK trace is double of trace width (W*2). - Page 61 Route ground trace adjacent to PCLK/MCLK traces to reduce crosstalk between other traces, or route power or low frequency signal adjacent to PCLK/MCLK traces. Priority: GND->Power->Low frequency signals Note: low frequency signal: I2C/PWDN/ RESETN/VSYNC etc. In 2-layer design, avoid route any signal trace parallel to PCLK/MCLK nearby. ...

-

Page 62: Quad Serial Peripheral Interface (Qspi)

11 Quad Serial Peripheral Interface (QSPI) The Quad Serial Peripheral Interface (QSPI) applies to synchronous serial data communication and allows full duplex transfer. Devices communicate in Master/Slave mode with the 4-wire bi-direction interface. The chip contains one QSPI controller performing a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. -

Page 63: Pcb Layout Considerations For Qspi Flash

11.3 PCB Layout Considerations for QSPI Flash QSPI0 supports (up to 100MHz) high speed SPI flash memory device for booting. For PCB design, standard high speed layout practices should be followed. This session provides the recommendations for PCB layout. 11.3.1 Power Supply Decoupling The SPI Flash has one power supply pin (VCC) and one ground pin (GND). -

Page 64: Data Signal Routing

11.3.3 Data Signal Routing QSPI Flash has a 4-bit data bus, IO0 - IO3. In order to keep the correct timing for the data transfer, in the PCB routing, the data traces should match the time delay with the clock trace from the host controller to the Flash. -

Page 65: Controller Area Network (Can) Interface

12 Controller Area Network (CAN) Interface The Controller Area Network (CAN) is a serial communications protocol that efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high speed networks to low cost multiple wiring. The maximum signaling rate is 1 Mbps. -

Page 66: Reference Connection

Group Pin Name GPIO Type Description PC.0 MFP3 PD.13 MFP4 PE.5 MFP2 PA.0 MFP7 CAN3_RXD PE.6 MFP2 CAN3 bus receiver input. PE.10 MFP2 CAN3 PA.1 MFP7 CAN3_TXD PE.7 MFP2 CAN3 bus transmitter output. PE.12 MFP2 12.2 Reference Connection Figure 12.2-1 CAN BUS Connectivity... -

Page 67: Can Bus Layout Recommendations

Figure 12.2-2 reference circuit for CAN BUS transceiver connection 12.3 CAN BUS Layout Recommendations The following points should be considered to achieve best performance: • It is recommended to place the CAN transceiver as close as possible to the ECU connector in order to minimize track length of bus lines. -

Page 68: Fmi Nand & Sd/Emmc Interfaces

13 FMI NAND & SD/eMMC Interfaces NUC980 Flash Memory Interface (FMI) controller has DMA unit and FMI unit. The DMA unit provides a DMA (Direct Memory Access) function for FMI to exchange data between system memory (ex. SDRAM) and shared buffer (128 bytes), and the FMI unit control the interface of SD0/eMMC0 or NAND flash. - Page 69 Table 13.1-2 SD/eMMC interfaces pin-list SD0 clock output pin SD0_CLK PC.6 MFP6 eMMC0_CLK eMMC0 clock output pin SD0 command/response pin SD0_CMD PC.5 MFP6 eMMC0_CMD eMMC0 command/response pin SD0 data line bit 0. SD0_DATA0 PC.7 MFP6 eMMC0_DATA0 eMMC0 data line bit 0. SD0 data line bit 1.

-

Page 70: Fmi Reference Connection

13.2 FMI Reference Connection Figure 13.2-1 reference circuit for NAND Flash connectivity Figure 13.2-2 reference circuit for SD0/eMMC0 connectivity with PC port... -

Page 71: General Pcb Signal Routing Guidelines

Figure 13.2-3 reference circuit for SD1/eMMC1 connectivity with PC port 13.3 General PCB Signal Routing Guidelines The following general guidelines must be considered before and throughout the PCB layout design effort: Use the VSS plane as a primary reference or return path for all signals. Power should only be considered as secondary reference option where a solid continuous ground reference is also present. -

Page 72: 14 I²C, Spi & I²S Interfaces

14 I²C, SPI & I²S Interfaces The I² C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. NUC980 provides 4 sets of I² C devices with Master/Slave mode, it supports Standard mode (100kbps), Fast mode (400kbps) and Fast mode plus (1Mbps), it can support SMBus and PMBus and with PDMA operation. - Page 73 Table 14.1-2 SPI0/1 interfaces pin-list PC.6 MFP5 SPI0_CLK SPI0 serial clock pin. PD.9 MFP1 PC.8 MFP5 SPI0_MISO SPI0 MISO (Master In, Slave Out) pin. PD.11 MFP1 PC.4 MFP6 PC.7 MFP5 SPI0_MOSI SPI0 MOSI (Master Out, Slave In) pin. PC.14 MFP5 SPI0 PD.10 MFP1...

-

Page 74: Reference Connection

Table 14.1-3 I²S interface pin-list PA.3 MFP2 I2S_BCLK PG.10 MFP8 I2S bit clock output pin. PB.4 MFP3 PA.4 MFP2 I2S_DI I2S data input pin. PB.7 MFP3 PA.5 MFP2 I2S_DO I2S data output pin. PB.5 MFP3 PA.2 MFP2 I2S_LRCK PA.15 MFP8 I2S left right channel clock output pin. - Page 75 SPIx_CLK SPI_CLK SPI_DO SPIx_MISO NUC980 Slave SPI Master SPI_DI SPIx_MOSI SPIx_SS0 / SPIx_SS1 SPI_SS Note: x = 0, 1 SPI_CLK SPIx_CLK SPI_DI SPIx_MISO NUC980 Master SPI Slave SPI_DO SPIx_MOSI SPI_SS SPIx_SS0 Note: x = 0, 1 Figure 14.2-2 SPI0/1 Application Block Diagram I2S_BCLK I2S_LRCK Audio...

- Page 76 I2S_BCLK I2S_LRCK Audio I2S_DO Controller Codec (Slave) (Master) I2S_DI I2S_MCLK I2S_BCLK I2S_LRCK Audio Controller Codec I2S_DO (PCM Mode) I2S_DI Figure 14.2-3 I²S Application Block Diagram Figure 14.2-4 I²C & I²S connectivity with external audio codec...

-

Page 77: Pcb Layout Considerations

14.3 PCB Layout Considerations 14.3.1 I²C The I² C bus is a world standard over thousands different ICs manufactured. Additionally, the I² C bus is used in various control architectures such as System Management Bus (SMBus), Power Management Bus (PMBus). Serial, 8-bit, bi-directional data transfers can be made at up to 100 Kbit/s in Standard-mode, up to 400Kbit/s in Fast-mode, or up to 1Mbit/s in Fast- mode Plus, also up to 3.4 Mbit/s in High-speed mode. -

Page 78: Uart & Smart Card Interface (Iso/Iec 7816-3)

15 UART & Smart Card Interface (ISO/IEC 7816-3) The NUC980 provides 10 channels of Universal Asynchronous Receiver/Transmitters (UART). The UART controller performs Normal Speed UART and supports flow control function. The UART controller performs a serial-to-parallel conversion on data received from the peripheral and a parallel-to-serial conversion on data transmitted from the CPU. - Page 79 PB.12 MFP1 UART3_CTS PD.5 MFP2 UART3 clear to Send input pin. PF.4 MFP5 PB.11 MFP1 UART3_RTS PD.4 MFP2 UART3 request to Send output pin. PF.5 MFP5 PC.4 MFP5 UART3 PB.10 MFP1 UART3_RXD UART3 data receiver input pin. PD.3 MFP2 PF.6 MFP5 PC.3 MFP5...

- Page 80 PA.3 MFP1 UART6_RTS UART6 request to Send output pin. PD.9 MFP2 PA.4 MFP1 UART6_RXD PD.11 MFP2 UART6 data receiver input pin. PE.8 MFP5 PA.5 MFP1 UART6_TXD PD.10 MFP2 UART6 data transmitter output pin. PE.9 MFP5 PB.7 MFP5 UART7_CTS UART7 clear to Send input pin. PF.0 MFP5 PB.5...

- Page 81 PE.7 MFP5 PE.12 MFP3 Table 15.1-1 SMART Card0/1 interfaces pin-list PA.2 MFP3 SC0_CD Smart Card 0 card detect pin. PC.15 MFP4 PA.5 MFP3 SC0_CLK Smart Card 0 clock pin. PC.12 MFP4 PA.4 MFP3 SC0_DAT Smart Card 0 data pin. PC.13 MFP4 PA.3 MFP3...

-

Page 82: Reference Connection

15.2 Reference Connection Figure 15.2-1 UART with Control Flow Block Diagram Figure 15.2-2 IrDA Control Block Diagram... - Page 83 Figure 15.2-3 RS485 mode Block Diagram Figure 15.2-4 RS232 connectivity with UART2...

- Page 84 Figure 15.2-5 SMART Card connectivity with SC1...

-

Page 85: Reference Schematic

USB0_REXT VDD33 USB0_REXT VDD33 VD33 VD33 USB1_REXT VD33_ADC USB1_REXT VD33_ADC VSS_ADC VDD18 VSS_ADC VDD18 VD18 nuvoTon Technology Corp. VD18 VDD12 VDD12 VD12 Title VD12 NUC980 Reference Circuit Power Filter Size Document Number System Block Thursday, July 26, 2018 Date: Sheet... -

Page 86: Gpio Pin Assignment List

RMII_0 x1 PC15 NAND_D7 ADC_0 x1 UART_2/6/8 x3 UART_0 debug port x1 PWM_01 x1 LED x8 ICE_0 x1 nuvoTon Technology Corp. USB_0 Device x1 Title NUC980 Reference Circuit USB_1 HOST x1 USB_0/1/2/3/4/5 HOST Lite x6 Size Document Number GPIO List... -

Page 87: System Power Supply

1 . 8 V D R A M P o w e r 102p ZT7103T VBUS 200K TSOT-25 VBUS VD33_RTC VD33_RTC VDD33 100K VDD33 nuvoTon Technology Corp. VDD18 VDD18 Title NUC980 Reference Circuit VDD12 VDD12 Size Document Number Power Date: Thursday, July 26, 2018... -

Page 88: Nuc980 Main Chip

PD14 PC11/E_D11/CP0_D3/ND_D3/SC0_R PD14/RT4/TM3_T/IC3_C/CA1_R/UL0_M/PW2/E_D3 PC12 PD13 PC12/E_D12/CP0_D4/ND_D4/SC0_C/SD0_CD/TX8 PD13/RX4/TM2_C/CA2_T/PW1/E_D2 PC13 PD12 PC13/E_D13/CP0_D5/ND_D5/SC0_D/RX8 PD12/TX4/TM2_T/CA2_R/PW0/E_D1 PC14 PD11 PC14/E_D14/CP0_D6/ND_D6/SC0_P/SP0_D0/RT8 PD11/SP0_DI/RX6/TM5_E PC15 PD10 nuvoTon Technology Corp. PC15/E_D15/CP0_D7/ND_D7/SC0_CD/CT8 PD10/SP0_DO/TX6/TM4_E VD33 VDD33_IO PD9/SP0_C/RT6/TM3_E PD2/QSP0_S0/TX3/TM4_C PD8/SP0_S0/CT6/TM2_E Title PD3/QSP0_C/RX3/TM4_T PD7/QSP0_D3/RX2/CA0_T/TM1_E NUC980 Reference Circuit PD4/QSP0_D0/RT3/TM5_C PD6/QSP0_D2/TX2/CA0_R/TM0_E VSS_IO PD5/QSP0_D1/CT3/TM5_T Size Document Number... -

Page 89: Power Cap Filter

10uF 10uF USB0_REXT USB0_REXT USB1_REXT USB1_REXT VDD12 VDD12 VD12 VD12 VDD18 VDD18 VD18 VD18 VDD33 VDD33 VD33 VD33 nuvoTon Technology Corp. VD33_ADC VD33_ADC VSS_ADC VSS_ADC Title NUC980 Reference Circuit Size Document Number Power Filter Thursday, July 26, 2018 Date: Sheet... -

Page 90: Reset, Power-On Setting, Xtal & Debugging

PG[15:11] PG[15:11] 2N3904 32K_IN 32K_IN 32K_OUT HEADER 8 32K_OUT 100K 12M_IN 12M_IN 12M_OUT 12M_OUT nRESET nRESET nuvoTon Technology Corp. VDD33 VDD33 VDD12 Title VDD12 NUC980 Reference Circuit Size Document Number Setting, ICE, Reset, Debug Date: Thursday, July 26, 2018 Sheet... -

Page 91: Nand Flash

N_CLE N_D3 PC11 I/O3 VDD33 N_ALE N_D4 PC12 VDD33 I/O4 N_WE N_D5 PC13 I/O5 N_WP N_D6 PC14 NAND Flash I/O6 N_D7 PC15 I/O7 nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number Memory Date: Thursday, July 26, 2018 Sheet... -

Page 92: Ethernet Rmii Phy + Rj45

E_MDI_TN LED- E_PHY_AD3 E_RX+ E_CRS LED+ LED- E_RX- 5.1K E_MDI_RP E_CRSDV Shield 5.1K Shield E_MDI_RN TS8121C nuvoTon Technology Corp. CB23 CB24 0.01uF/2KV 0.01uF 0.1uF 0.1uF 0.01uF Title NUC980 Reference Circuit Size Document Number 0.01uF/2KV Ethernet Thursday, July 26, 2018 Date:... -

Page 93: I²C Interface

R e a l T i m e C l o c k I C VD33_RTC 4.7K 4.7K I2C0_SCL I2C0_SDA TIMER VDD33 E E P R O M I C VDD33 4.7K 4.7K I2C2_SCL I2C2_SDA EEPROM nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number Date: Thursday, July 26, 2018 Sheet... -

Page 94: Led Indication

D o w n l i n k c o m m u n i c a t i o n VDD33 VDD33 VDD33 VDD33 VDD33 VDD33 LED1 LED2 LED3 LED4 LED5 LED6 PA[7:6] PA[7:6] PD[7:2] PD[7:2] VDD33 VDD33 nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number Date: Thursday, July 26, 2018 Sheet... -

Page 95: Uart Interface

R S 2 3 2 VDD33 PA10 UART2_TXD UART2_RXD UART2_RTS RS232 檢 測 R S 2 3 2 VDD33 UART6_TXD UART6_RXD UART6_RTS RS232 nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number RS_232 Thursday, July 26, 2018 Date: Sheet... -

Page 96: Spi Interface

P o w e r M e a s u r e m e n t I C VDD33 SPI1_DO MOSI SPI1_DI MISO SPI1_SS0 SPI1_CLK GPIO1 GPIO1 GPIO2 GPIO2 MEASURE nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number Date: Thursday, July 26, 2018 Sheet... -

Page 97: Usb Hs Host & Device

USB0_VBUSVKD VBUS CON3 USB miniAB RECEP. FUSE(6V/1A) U S B 1 H O S T CON4 VBUS USB1_DM USB1_DP Shield Shield USB TYPE-A RECAP. nuvoTon Technology Corp. Title NUC980 Reference Circuit Size Document Number Date: Thursday, July 26, 2018 Sheet... - Page 98 H O S T L i t e _ 5 USBHL3_DM USBHL4_DM USBHL5_DM USBHL3_DP USBHL4_DP USBHL5_DP VSS VSS PD[15:14] PD[15:14] nuvoTon Technology Corp. PF[9:0] PF[9:0] Title NUC980 Reference Circuit Size Document Number HOST Lite Date: Thursday, July 26, 2018 Sheet...

- Page 99 AN180901 Revision History Date Revision Description 2018.12.12 1.00 Initially issued. Dec. 06, 2018 Page 99 of 100 Rev 1.0...

- Page 100 All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claims to Nuvoton as a result of customer’s Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Need help?

Do you have a question about the NUC980 Series and is the answer not in the manual?

Questions and answers