Table of Contents

Advertisement

Quick Links

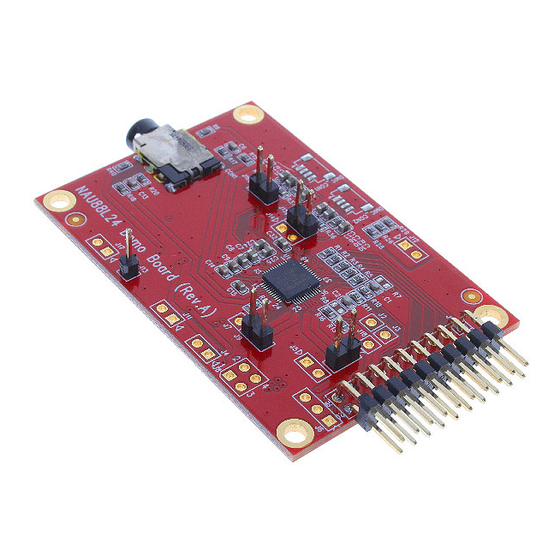

Ultra-Low Power Audio CODEC with Stereo Class D Drivers and Ground-

Referenced Headphone Amplifier with Advanced Headset Detection

GENERAL DESCRIPTION

The NAU88L24 is an ultra-low power high performance audio codec designed for smartphone, tablet PC, and other

portable devices that supports both analog and digital audio functions. It includes one I2S/PCM interface, one digital

mixer, two high quality DACs, two high quality ADCs, two mono differential or one stereo differential analog microphone

inputs, four analog single-ended microphone inputs, four digital PDM microphone inputs, one single ended stereo

auxilary or one differential mono inputs, one differential HS mic input, one stereo 2.9W class D loudspeaker amplifier

driver for 4 Ω loading and 5V supply, and one stereo class G headphone amplifier with automatic headset detection.

The advanced on-chip signal processing engine that includes dynamic range compressors (DRC), 5-band parametric

equalizer (PEQ), and programmable high pass and notch filter block, can maximize audio quality and eliminate any

undesirable frequency components.

The NAU88L24 also has powerful headset detection that supports jack insertion / ejection, microphone detection,

distinct key / short key / long key / key release detection features as well as an integrated frequency locked loop (FLL)

to support various clocks.

FEATURES

DAC: 103dB SNR (A-weighted) @ 0dB gain, 1.8V

and -77dB THD @ 20mW and RL= 32Ω, DAC

playback to headphone output mode

ADC: 100dB SNR (A-weighted) @ 0dB MIC gain,

1.8V, Fs = 48KHz and -85dB THD, 1.8V, MIC gain

6dB, OSR 128x

1 Digital I2S/PCM I/O port

Dynamic Range Compressor (DRC)

5 Band Parametric Equalizer

1 Headset Microphone, 4 Analog or 4 Digital PDM

MIC input supports

Stereo .97W Class D Loudspeaker @ 4.2V, 8Ω,

1% THD+N (1.38W @ 5.0V, 8Ω, 1% THD+N)

Class G Headphone Amplifier (27mW @ 32Ω, 1%

THD+N)

Stereo Auxiliary Input

Sampling rate from 8K to 96 KHz

Headset Detection

Apr 11, 2022

Jack Insertion and Ejection Detection

MIC Detection and Distinct Keys Detection

Package:

QFN-48 (6X6mm, 0.4mm Pitch) package

56 Balls WLCSP package with 0.4mm Pitch

package

Applications

Tablets / Ultra-Portable Laptops

Smartphones

Audio Docking Systems

Portable Game Players

Cameras

Page 1 of 96

NAU88L24

Rev 2.1

Advertisement

Table of Contents

Summary of Contents for Nuvoton NAU88L24

- Page 1 Referenced Headphone Amplifier with Advanced Headset Detection GENERAL DESCRIPTION The NAU88L24 is an ultra-low power high performance audio codec designed for smartphone, tablet PC, and other portable devices that supports both analog and digital audio functions. It includes one I2S/PCM interface, one digital...

-

Page 2: Block Diagram

Block Diagram Selector/ Selector/ Mixer Mixer Ʃ MIC1+/DMCLK1 Ʃ AUX_L/MONO+ HPCOM Ʃ MIC1-/DMDATA1 ADC Effect Ʃ Volume MIC2+/AUX_R/DMCLK2 Ʃ SPKOUTL+ Ʃ SPKOUTL- MONO-/HSMIC+ DAC Effect MIC2-/DMDATA2 Digital Audio Ʃ Ʃ SPKOUTR+ SPKOUTR- HSMIC- Interface Volume MICBIAS MICBIAS CPOUTP VDDCP DMCLK1/2 DMIC VSSCP Charge... -

Page 3: Table Of Contents

Table of Contents BLOCK DIAGRAM ............................2 PIN DIAGRAM-QFN48 ..........................6 PIN DIAGRAM-WLCSP ..........................7 Ordering Information ..............................7 PIN DESCRIPTION-QFN48 .......................... 8 PIN DESCRIPTION-56 BALLS WLCSP ..................... 10 ELECTRICAL CHARACTERISTICS ......................12 GENERAL DESCRIPTION ........................ 15 Inputs ................................. 15 Outputs .............................. - Page 4 Device Protection ..........................44 9.1.3 Class D without filter ........................... 44 9.1.4 Class D Filters ............................ 45 9.1.5 NAU88L24 EMI performance ......................46 Class G Headphone Driver and Charge Pump ..................46 HEADSET DETECTION ........................47 10.1 Jack Detection ............................47 10.2 Microphone Detection ..........................

- Page 5 11.3 Enable analog ADC ........................... 53 11.4 Enable/Disable FLL ............................ 53 11.5 Enable/Disable DAC ..........................54 11.6 Enable/Disable Class D Driver ........................54 11.7 Enable/Disable Headphone ........................54 11.8 Enable DAC to Headphone Low Power MP3 Playback Mode ..............55 11.9 Enable DAC to Class D Low Power MP3 Playback Mode .................

-

Page 6: Pin Diagram-Qfn48

Pin Diagram-QFN48 AUX_L/MONO+ MIC1+/DMCLK1 SCLK MIC1-/DMDATA1 SDIO VSSA GPIO1 VDDA MICBIAS VDDSPK Top View VDDMIC SPKOUTR+ MICDET VSSSPK VREF SPKOUTR- VSSA VDDSPK VDDA SPKOUTL- CPOUTP VSSSPK Note: NAU88L24IG (6mm X 6mm QFN 48 pin) have same pin diagram and pin descriptions Apr 11, 2022 Page 6 of 96 Rev 2.1... -

Page 7: Pin Diagram-Wlcsp

Pin Diagram-WLCSP Top View GP4/ MIC2-/ MIC2+/ DACIN HSMIC- VDDB VSSD DMDATA2 DMCLK2 GP2/ AUXL/ SCLK MCLK VDDC HSMIC+ JKDET MONO+ AUX_R/ MIC1+/ SDIO BCLK IFSEL VSSA MONO- DMCLK1 MIC1-/ GP1/ VDDA DMDATA1 BIAS 3.66mm TEST VREF SPKR+ SPKR- VSSA VDDA CPCA SPKL-... -

Page 8: Pin Description-Qfn48

Pin Description-QFN48 Pin # Name Type Functionality AUX_L/MONO + Analog Input PGA Mono+ or Left channel Auxiliary Analog Input MIC1+/DMCLK1 Analog Input / Digital PGA MIC1+ Analog Input or Digital Microphone 1 Output Clock Output MIC1-/DMDATA1 Analog Input / Digital PGA MIC1- Analog Input or Digital Microphone 1 Input Data Input... - Page 9 VDDC Supply Digital core supply JKDET Analog Input Jack detect input HSMIC- Analog Input Headset Microphone negative Analog input MIC2+/AUX_R /DMCLK2 Analog Input / Digital PGA MIC2+ or AUXR Analog Input or Digital Output Microphone 2 Clock Output MIC2-/DMDATA2 Analog Input / Digital PGA MIC2- Analog Input or Digital Microphone 2 Input Data Input...

-

Page 10: Pin Description-56 Balls Wlcsp

Pin Description-56 Balls WLCSP Pin # Name Type Functionality GPIO4/SDO Digital I/O General Purpose IO / 3 Wire Data Output DACIN Digital Input Serial Audio data input for I2S or PCM data VDDB Supply Digital IO Supply VSSD Ground Digital IO ground HSMIC- Analog Input Headset Microphone negative Analog input... - Page 11 CPCA Analog I/O Charge Pump switching capacitor node A CPOUTP Analog I/O Charge Pump positive voltage VCCP1 Supply Charge Pump Supply VSSSPK Ground Class-D amplifier supply ground SPKOUTL+ Analog Output Class-D amplifier Left Channel positive Output VDDSPK Supply Class-D amplifier supply HPCOM Analog Input Headphone ground reference...

-

Page 12: Electrical Characteristics

Electrical Characteristics Conditions: Shutdown ModeV A = V B = V C = 1.8V; V SPK = V MIC= 4.2V. (Loudspeaker) = 8 Ω+68uH, R (Headphone) = 32 Ω, f = 1kHz, MCLK=12.288MHz, unless otherwise specified. Limits apply for T = 25°C Units Symbol... - Page 13 Units Symbol Parameter Conditions Typical Limit (Limit) ADC Total Harmonic Distortion + MIC Input, MIC_GAIN = -3dB, VIN = THD+N Noise 1Vrms, f = 1kHz, Fs = 48kHz Reference = VOUT(0dBFS), A- Weighted, MIC Input, MIC Gain = 0dB,fs = 8kHz, Mono Differential Input Reference = VOUT(0dBFS), A- Signal to Noise Ratio Weighted, MIC Input, MIC Gain =...

- Page 14 Recommended Operating Conditions Condition Symbol Typical Units Digital Supply Range 1.98 Digital Supply Range for FLL 1.61 1.98 operation and for Fs > 48KHz Digital I/O Supply Range Analog Supply Range Headphone Supply Range Loudspeaker Supply Range Microphone Bias Supply Voltage Temperature Range °C >...

-

Page 15: General Description

I2S and PCM devices. Power Supply This NAU88L24 has been designed to operate reliably using a wide range of power supply conditions and power-on/power-off sequences. However, because of existence of ESD protection diodes between the supplies, that will have impact on the application of the supplies. -

Page 16: Power On And Off Reset

2.1 Power on and off reset The NAU88L24 includes a power on and off reset circuit on chip that resets the internal logic to its default state when the VDDA and VDDC supplies power up. This reset function will be automatically and internally generated when the power supplies are too low for reliable operation of the internal logic circuitry. -

Page 17: Vref

DMDATA2 Figure 1: Microphone Input Block Diagram with Registers 3.1.1 V The NAU88L24 includes a mid-supply, reference circuit that produces voltage close to VDDA/2 that is decoupled to V through the V pin by means of an external bypass capacitor. Because V... -

Page 18: Mic Bias

4.7uF can be used. 3.2 Digital MIC Inputs In addition to analog inputs, the NAU88L24 is setup to handle up to four digital MIC inputs using the DMCLK1/2 and DMDATA1/2 pins that are multiplexed with the MIC1/2+ and MIC1/2- pins, respectively. -

Page 19: Line Inputs

Application Notes: • The clock phase for the selection of the digital MIC is configurable using ENA_CTRL.DMIC_LCH_EDGE_ADC_CH01 REG0X01[14] ENA_CTRL.DMIC_LCH_EDGE_ADC_CH23 REG0X01[15]. • The DMCLK rate can be selected using CLK_DIVIDER.CLK_DMIC_SRC REG0X03[12:10]. • Both digital MIC inputs can be used simultaneously. However, both digital MIC and analog MIC inputs cannot. -

Page 20: Adc Dynamic Range Compressor (Drc)

4.1 ADC Dynamic Range Compressor (DRC) The NAU88L24 includes DRCs for the four channels in the ADC. However, to control the DRC, the four channels have been paired and denoted as CH01 or CH23 in the register map for channel 0/1 and channel 2/3, respectively. - Page 21 Input (dB) Knee 4 Knee 3 Knee 2 Knee 1 CMP2 Figure 4: DRC Static Characteristics Each of the sections labeled NG, EXP, CMP2, CMP1, and LMT are controlled by setting the slope and knee point values in the registers. The table below provides the corresponding registers and their locations. Static Curve Slope Knee Point...

-

Page 22: Adc Digital Volume Control

Application Notes: • The Y axis distance adjusting along curve cannot exceed 36dB. • Smooth Knee filter function can be enabled by using DRC_KNEE_IP12_ADC_CH01.DRC_SMTH_ENA_ADC_CH01 REG0X38[7] DRC_KNEE_IP12_ADC_CH23.DRC_SMTH_ENA_ADC_CH23 REG0X3C[7] for channel 0/1 and 2/3, respectively. • The gain values can also be individually read in decimal by using DRC_GAINL_ADC0 REG0X40, DRC_GAINL_ADC1... -

Page 23: Programmable Notch Filter

ADC_FILTER_CTRL.SMPL_RATE REG0X23[7:5] HPFCUT_ADC _CH## 8 kHz 12 kHz 16 kHz 24 kHz 32 kHz 48kHz Table 6: High Pass Filter Cut-off Frequencies in Hz 4.4 Programmable Notch Filter In addition to the HPF filter described in section 4.3, channel 0 and 1 have an optional notch filter available in the ADC digital block. -

Page 24: Adc Path Digital Mixer

4.5 ADC Path Digital Mixer The NAU88L24 implements a channel based digital mixer for ADC output that can select between input channels and I2S channels to mix for the four ADC channel outputs. The figure below shows a block diagram of how the mixer works along with the related registers. -

Page 25: Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L24 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and µ-law. The A-law algorithm is primarily used in European communication systems and the µ-law algorithm is primarily used by North America, Japan, and... -

Page 26: Dac Dynamic Range Control (Drc)

DAC Digital Path (X2 channels) Digital ƩΔ Digital Filter Filter Digital Volume High Pass Notch 5 Band Volume High Pass Notch 5 Band Audio Mixer Mixer Control Filter Filter Equalizer Control Filter Filter Equalizer Interface Class D Class D Amplifier Amplifier Figure 6: DAC Digital Path The DAC digital block uses 24-bit signal processing to generate analog audio with a 16-bit digital sample... -

Page 27: Dac Digital Volume Control

CMP2 DRC_SLOPE_DAC.DRC_CMP2_SLP_DAC DRC_KNEE_IP12_DAC.DRC_KNEE2_IP_DAC REG0X47[8:6] REG0X45[4:0] DRC_SLOPE_DAC.DRC_EXP_SLP_DAC DRC_KNEE_IP34_DAC.DRC_KNEE3_IP_DAC REG0X47[10:9] REG0X46[13:8] DRC_SLOPE_DAC.DRC_NG_SLP_DAC DRC_KNEE_IP34_DAC.DRC_KNEE4_IP_DAC REG0X47[13:12] REG0X46[5:0] Table 14: DAC DRC Static Curve Control Registers Application Notes: • Smooth Knee function can be enabled by using DRC_KNEE_IP12_DAC.DRC_SMTH_ENA_DAC REG0X45[7]. • The gain values can be individually read by using DRC_GAIN_DAC_CH0.DRC_GAIN_DAC_CH0 REG0X49[15:0] DRC_GAIN_DAC_CH1.DRC_GAIN_DAC_CH1 REG0X4A[15:0]... -

Page 28: 5-Band Equalizer

5.5 DAC Path Digital Mixer with Side tone The NAU88L24 implements a channel based digital mixer for DAC output that can select between ADC input channels, I2S channels and the opposing DAC output channel to mix into the output of the two DAC channels. -

Page 29: Companding

Reg0X32[11:10] ADCTODAC_CH0_SEL ADC CH 0 Reg0X32[15] Reg0X34[15:8] MIXLR_SEL_CH0 ADCTODAC_ATTU_CH0 ADC CH 1 ADC CH 2 I2S CH 0 ADC CH 3 Ʃ DAC CH 0 Left Channel Reg0X32[9] DAC_CH0_SEL Reg32[8:0] DGAIN_CH0_DAC I2S CH 0 I2S CH 1 Reg0X33[11:10] ADCTODAC_CH1_SEL ADC CH 0 Reg0X34[7:0] ADCTODAC_ATTU_CH1 Reg0X33[15]... -

Page 30: Μ-Law

DAC output channels. Clocking and Sample Rates The internal clocks for the NAU88L24 are derived from a common internal clock source, CLK_DIVIDER.SYSCLK_SRC REG0X03[15]. This master system clock can set directly by the MCLK_PIN input or it can be generated from a Frequency Locked Loop (FLL) using the MCLK_PIN, BCLK or FS as a reference. - Page 31 frequencies, the FLL provides additional flexibility for a wide range of MCLK inputs or as a free running clock in the absence of an external reference. The figures below is a block diagram illustrating how the various register settings can be used to adjust/select the MCLK, BCLK, FS, and ADC_CLK clock frequency.

-

Page 32: Frequency Locked Loop (Fll)

BCLK_DIV ÷ MCLK BCLK ÷ LRC_DIV Register: PORT0_I2S_PCM_CTRL2 Figure 9: BCLK and FS Frequency Selection Bits BCLK_DIV Divide by 1 Divide by 2 Divide by 4 Divide by 8 Divide by 16 Divide by 32 Table 22: PORT0_I2S_PCM_CTRL_2.BCLK_DIV REG0X1D[2:0] Register Settings Bits LRC_DIV Divide by 256... - Page 33 FLL_CLK_REF_SRC FLL_CLK_REF_DIV MCLKI 00/01 FREF ÷ BCLK Frequency Detector IDAC Register: FLL4 Register: FLL3 FLL_INTEGER FLL_RATIO Register: FLL3 Register: FLL1 Order ƩΔ ÷2 -1, 0, 1, 2 FLL_FRAC Register: FLL2 MCLK_SRC MCLK SYSCLK_SRC Register: CLK_DIVIDER Figure 10: FLL Block diagram The integrated FLL can be used to generate a SYSMCLK from a wide variety of reference sources such as, MCLK, BCLK, and FS or as a free running clock in the absence of an external reference.

-

Page 34: Control Interfaces

Randomize the number of Filter Output Bits to average out output noise. If ‘00’, there is no dither. Control Interfaces The NAU88L24 includes a serial control bus that provides access to all of the device control registers and may be configured as a 2-wire interface that conforms to industry standard implementations of the I2C serial bus. -

Page 35: 2-Wire-Serial Control Mode (I C Style Interface)

The 2-wire bus is a bidirectional serial bus protocol. This protocol defines any device that sends data onto the bus as a transmitter (or master), and the receiving device as the receiver (or slave). The NAU88L24 can function only as a slave device when in the 2-wire interface configuration. -

Page 36: 2-Wire Read Operation

START condition and Device address but with R/W = 1. After the NAU88L24 recognizes its Device Address the second time, it will transmit an ACK followed by a two byte value containing the 16 bits of data in the NAU88L24 control registers requested by the master. During this phase, the master generates an ACK with each byte of data transferred. -

Page 37: Software Reset

SDIOH 7.6 Software Reset The NAU88L24 and all of its control registers can be reset to default initial conditions by writing any value to REG0X00 twice using any of the control interface modes. Writing to any other valid register address terminates the reset condition, but all registers will now be set to their power-on default values. -

Page 38: Right-Justified Audio Data

PORT0_I2S_PCM_CTR PORT0_I2S_PCM_CTR PORT0_I2S_PCM_CTR PCM Mode L_1.AIFMT L_2.PCM_TS L_1.LRP REG0X1C[6] REG0X1C[1:0] REG0X1D[10] Right Justified Left Justified PCM A PCM B PCM Time Don’t care Slot Table 24: Digital Audio Interface Modes 8.1 Right-Justified Audio Data In right-justified mode, the LSB is clocked on the last BCLK rising edge before FS transitions. When FS is HIGH, channel 0 data is transmitted and when FS is LOW, channel 1 data is transmitted. -

Page 39: Pcm A Audio Data

The PCM time slot mode is used to delay the time at which the DAC and/or ADC data are clocked. This can be useful when multiple NAU88L24 chips or other devices are sharing the same audio bus. This will allow each chip’s audio to be delayed around each other without interference. -

Page 40: Tdm I2S Audio Data

This mode can be used to swap channel 0 and channel 1 audio or cause both channels to use the same data. • When using the NAU88L24 with other driver chips, the SDO pin can be set to pull up or pull down by enabling PORT0_I2S_PCM_CTRL_2.ADCDAT_PE REG0X1D[6] and selecting up or down with PORT0_I2S_PCM_CTRL_2.ADCDAT_PS... -

Page 41: Tdm Pcm B Audio Data

The PCM offset mode is used to delay the time at which the ADC data is clocked. This increases the flexibility of the NAU88L24 to be used in a wide range of system designs. One key application of this feature is to enable multiple NAU88L24 or other devices to share the audio data bus, thus enabling more than four channels of audio. - Page 42 CHANNEL 3 CHANNEL2 CHANNEL 0 CHANNEL 1 BCLK SDI/SDO Figure 27: TDM PCM Offset Audio Format Application Notes: • When using PORT0_LEFT_TIME_SLOT.TSLOT_L REG0X1E[9:0] for time slot shift in TDM mode, the four channels will shift together for the same chip. The shift number should be N* Word Lenghth +1, and available channels should be >...

-

Page 43: Outputs

9 Outputs The NAU88L24 provides two types of integrated output drivers. The stereo pair of high power, high quality Class D speaker drivers, which can support 3W each in stereo mode and a pair of Class G ground-reference headphone outputs. -

Page 44: Device Protection

9.1.3 Class D without filter The NAU88L24 is designed for use without any filter circuits on the Class D output line so they can be connected directly to a speaker. This type of filter-less design is suitable for portable applications where the speaker is very close to the amplifier. -

Page 45: Class D Filters

Figure 29: Speaker Outputs Connected to Speaker without Filter Circuit 9.1.4 Class D Filters In some applications, the short trace lengths are not possible because of speaker size limitations or other design considerations. In these applications, the long traces will cause EMI issues. To reduce the EMI issues, typical filters like ferrite bead and LC can be used. -

Page 46: Nau88L24 Emi Performance

9.2 Class G Headphone Driver and Charge Pump The NAU88L24 uses Class G speaker drivers powered by a charge pump for the headphones. For typical operation with large and small signals the charge pump provides ±1.8V and ±0.9V, respectively. These output drivers are driven by dedicated left and right DACs and can provide 30mW of power to a 32 Ω... -

Page 47: Headset Detection

ENHSL[1] Figure 33: DAC to Headphone out path diagram 10 Headset Detection The NAU88L24 includes an extensive set of detection features to support various types of headsets for global compatibility. 1. Headset jack insertion detection: 2. This feature detects when a headset is inserted into the external headset jack. Headset jack ejection detection: •... -

Page 48: Microphone Detection

• It is recommended that the host checks for the IRQ to be consistently valid within 10ms in order to avoid false detection due to glitches. Once the host validates the jack detect, the host needs to initiate the power up sequence and headset support sequences. - Page 49 Figure 35: Key Detection Each of these output signals from the eight comparators go through three de-bounce filters not shown in the block diagram. After each of press key signals are received through the de-bounce filters, the associated interrupts are triggered and can be read from INTERRUPT_SETTING REG0X11.

- Page 50 MAX ADCOUT[7:0] Key Release Level 7 Threshold Voltage Key 7 Level 6 Threshold Voltage Key 6 Level 5 Threshold Voltage Key 5 Level 4 Threshold Voltage Key 4 Level 3 Threshold Voltage Key 3 Level 2 Threshold Voltage Key 2 Level 1 Threshold Voltage Key 1...

-

Page 51: Sar Adc

be set to 15, less than 50% of difference 150 and 116. SARADC_VDET_THR1=133=8’b10000101, HY_COEFF[3:0]=15=4’b1111 7) The third threshold voltage could be 181, the middle of 150 and 212 from 1) and 2). Hysteresis value can be set to 15, less than 50% of difference 116 and 212. SARADC_VDET_THR2=150=8’b10010110 HY_COEFF[3:0]=15=4’b1111 Combining 5), 6), and 7), a single HY_COEFF[3:0]=15=4’b1111... -

Page 52: Jack Interrupt Sequence

Table 29: SAR ADC MICBIAS Gain Tracking Settings 10.4 Jack Interrupt Sequence The NAU88L24 includes an interrupt sequence feature that can detect various types of interrupts and trigger associated sequences. This system works by continually waiting for an interrupt to occur. Once an interrupt occurs, the x10 register is read to determine the type of interrupt while the x11 register is reset to prepare for further interrupts. -

Page 53: Basic Register Sequences

Interrupt Figure 40: Key Release Flowchart 11 Basic Register Sequences The following register sequences are general guides to help setup the NAU88L24. 11.1 To enable V and General Bias 1. Reset all registers by writing anything to register 0x00 twice 2. -

Page 54: Enable/Disable Dac

1. Set FLL_DCO_RSV.DCO_EN REG0X09[15] 2. Set FLL1.SYSCLK_SRC REG0X03[15] To Enable Free Running Mode 1. Set FLL_DCO_RSV.DCO_EN REG0X09[15] 2. Set FLL1.SYSCLK_SRC REG0X03[15] 3. Set FLL_DCO_RSV.DCO_EN REG0X09[15] 4. Set FLL1.SYSCLK_SRC REG0X03[15] To Enable Free Running Mode with Reference Clock 1. Set FLL_DCO_RSV.DCO_EN REG0X09[15] 2. -

Page 55: Enable Dac To Headphone Low Power Mp3 Playback Mode

4. Set ATT_PORT0.ATT0HSL REG0X7B[4:0] ATT_PORT0.ATT0HSR REG0X7B[12:8] = -30dB (Adjust RDAC and LDAC HS attenuation to -30dB) 5. Set ENABLE_LO.ENHSL REG0X6B[1:0] ENABLE_LO.ENHSR REG0X6B[3:2] = 01( enable DAC right to right headphone output, DAC left input to left headphone output.) 6. Set BOOST.NAMP_THRSHLD REG0X76[1:0] BOOST.PAMP_THRSHLD REG0X76[3:2] = 11... - Page 56 2. Set enable global analog bias by BOOST.BIASEN REG0X76[12] =1 and VMID pre-charge disabled by BIAS_ADJ.PVDMDFST REG0X76[13] 3. Set MIC bias output =VDDA by MIC_BIAS.MICBIASLVL1[2:0] REG0 74[2:0] =0, then turn on mic bias MIC_BIAS.POWERUP REG74[8]=1 4. Set jack ejection de-bounce time =10ms by JACK_DET_CTRL.EJECT_DT[1:0] REG0XD[3:2] 5.

-

Page 57: Control And Status Registers

12 Control and Status Registers Function Function ENA_CTRL DRC_KNEE_IP34_ADC_CH23 CLK_GATING_ENA DRC_SLOPE_ADC_CH23 CLK_DIVIDER DRC_ATKDCY_ADC_CH23 FLL1 DRC_GAINL_ADC0 FLL2 DRC_GAINL_ADC1 FLL3 DRC_GAINL_ADC2 FLL4 DRC_GAINL_ADC3 FLL5 DRC_KNEE_IP12_DAC FLL6 DRC_KNEE_IP34_DAC FLL_DCO_RSV DRC_SLOPE_DAC JACK_DET_CTRL DRC_ATKDCY_DAC INTERRUPT_SETTING_1 DRC_GAIN_DAC_CH0 IRQ_STATUS DRC_GAIN_DAC_CH1 CLEAR_INT_REG MODE INTERRUPT_SETTING MODE1 SAR_ADC MODE2 VDET_COEFFICIENT CLASSG VDET_THRESHOLD_1 OPT_EFUSE... - Page 58 Function Name Description HARDWA HARDWARE_ Hardware Reset RE_RST RESET (Write any value once to reset all the registers.) DMIC_LCH_E DMIC Signal Phase For CH23 DGE_ADC_C 0 = (DEFAULT - Left on falling & Right on rising) 1 = (Left on rising & Right on falling) DMIC_LCH_E DMIC Signal Phase For CH01 DGE_ADC_C...

- Page 59 Function Name Description ADC Clock Polarity CLK_ADC_PL 0 = Non-inverted (DEFAULT) 1 = Inverted I2S Clock Gating Enable Control (For master mode) CLK_I2S_EN 0 = Disable (DEFAULT) 1 = Enable Gain Control Clock Gating Enable Control CLK_GAIN_E 0 = Disable (DEFAULT) 1 = Enable OTP Clock Gating Enable Control (When MCLK present, HP trimmed part needs to turn...

- Page 60 Function Name Description FLL Latch Drive Strength Multiplier (When FLL running at high frequency with long decimal number, DSP needs to operate at high speed. By adjusting ICTRL_LATCH, FLL DSP can optimize between performance and power consumption (111 ICTRL_LATC has highest power consumption for FLL DSP.) On the other hand, (DCO frequency)/(FLL input reference frequency)=integer, default setting can be used to reduce power.

- Page 61 Function Name Description FLL 10-bit Integer DCO Divider For FLL Filter Clock (The value is in orders of 2. When 0x8[13]=1, it selects DCO clock as FLL filter clock. The filter clock rate FLL_N2 needs to be less than 1Mhz. With setting proper value, filter clock can be divided down from DCO clock.

- Page 62 Function Name Description Jack Insertion/ Detection Logic Polarity JKDET_PL 0 = Falling edge (DEFAULT) 1 = Rising edge Jack Detection Logic Control JKDET_LOGI 0 = OR gate (DEFAULT) 1 = AND gate DEFAULT 0x0000 RESERVED RESERVED Jack Ejection Mask Flag Enable Control JK_EJECT_IN (Ejection IRQ in Sleep4JACK Mode) TP_MASK...

- Page 63 Function Name Description Write Operation (Write bits[15:0] clear corresponding REG10 [15:0] Write 1s to bits that you want to reset to 0, except) Bit0 or Bit1 = clear Jack insertion interrupt Bit2 or Bit3 = clear Jack ejection interrupt Read Operation (REG11[7:0] - RD_SAR level, key detection status for CLR_REG10_I each key)

- Page 64 Function Name Description Jack Insertion/Detection Interrupt Disable Control JACK_DET_I 0 = Enable interrupt; interrupt status read from register NT_DIS or IRQ pad (DEFAULT) 1 = Disable interrupt and IRQ pad DEFAULT 0x1000 SAR Inverted Output Enable Control SAR_OUT_IN 0 = Disable (DEFAULT) 1 = Enable SAR Enable Control SAR_ENA...

- Page 65 Function Name Description Hysteresis Coefficient (∆ = HY_COEFF Coefficient ranges from 0-15 matching the binary value. SAR ADC Level is from Low to High Voltage: HY_COEFF Level 0 is the lowest voltage. Each Level Threshold Voltage would add hysteresis. Threshold_ON = SARADC_VDET_THRx -∆ Threshold_OFF =SARADC_VDET_THRx+∆...

- Page 66 Function Name Description 8-bit Word For Companding Mode Of Operation Enable Control CMB8 0 = Normal operation (DEFAULT - No companding) 1 = 8-bit operation for companding mode uLaw Offset Select UA_OFF 0 = 1’s complement (DEFAULT) 1 = 2’s complement Bit Clock Phase Inversion Option For BCLK 0 = Non-inverted (DEFAULT) 1 = Inverted...

- Page 67 Function Name Description Master/Slave Mode Enable Control BCLKDIV 0 = Slave mode (DEFAULT) 1 = Master mode DEFAULT 0x0010 RESERVED Left Channel PCM Time Slot Start Value (When PCM_TS=1, both TSLOT_L and TSLOT_R need to set different values: N*WordLength+1 PORT0_L PCM TDM Offset Mode Slot start value when in EFT_TIME TSLOT_L...

- Page 68 Function Name Description ADC Data Source Under TDM/I2S Mode 00 = From slot 0 (DEFAULT) ADC_TXEN 01 = From slot 1 10 = From slot 2 11 = From slot 3 DEFAULT 0x0000 ADC CH23 HPF Enable Control HPFEN_ADC_ 0 = Disable (DEFAULT) CH23 1 = Enable ADC CH23 HPF Application Mode...

- Page 69 Function Name Description First Order Dynamic Element Matching Dithering Select (Set probability of first order DEM dithering.) (Step size is 1/16.) 0000 = No dithering (DEFAULT) 0001 = 1/16 0010 = 2/16 0011 = 3/16 0100 = 4/16 0101 = 5/16 DEM_DITHER 0110 = 6/16 0111 = 7/16...

- Page 70 Function Name Description Notch Filter 2 Update Bit 0 = (DEFAULT) Register write causes new value to be pending an update bit event on REG27(NOTCH FILTER1) NFU2 Register write operation will load new REG28(NOTCH FILTER2) value and any pending value in NOTCH_F REG27(NOTCH FILTER1) to be effective ILTER_2...

- Page 71 Function Name Description EQ2 Digital Gain Control (Step size is 1dB.) 0x00 = +12dB 0x01 = +11dB ▼ EQ2G 0x0C = 0dB (DEFAULT) ▼ 0x17 = -11dB 0x18 = -12dB DEFAULT 0x2C2C EQ5 Bandwidth Control EQ5BW 0 = Narrow bandwidth (DEFAULT) 1 = Wide bandwidth EQ5 -3dB Cut-off Frequency Select 00 = 5.3KHz...

- Page 72 Function Name Description ADC CH0 Digital Gain Control (Step size is 0.5dB.) 0x000 = -128dB 0x001 = -127.5dB DGAIN_ADC_ ▼ 0x100 = 0dB (DEFAULT) ▼ 0x163 = +49.5dB 0x164 = +50dB DEFAULT 0x0100 DAC To ADC CH1 Attenuation Control (Step size is 3dB.) 0x00 = Mute 0x02 = -128dB DACTOADC_...

- Page 73 Function Name Description DAC To ADC CH3 Attenuation Control (Step size is 3dB.) 0x00 = Mute 0x02 = -128dB DACTOADC_ 0x03 = -36dB ATTU_CH3 0x04 = -33dB ▼ 0x0E = -3dB 0x0F = 0dB DAC To ADC CH3 Source Select DACTOADC_ 0 = CH0 (DEFAULT) CH3_SEL...

- Page 74 Function Name Description DAC CH0 Digital Gain Control (Step size is 0.5dB.) 0x000 = -128dB 0x001 = -127.5dB DGAIN_CH0_ ▼ 0x100 = 0dB (DEFAULT) ▼ 0x163 = +49.5dB 0x164 = +50dB DEFAULT 0x0100 DAC CH1 Data Mixing Control MIXLR_SEL_ 0 = No mix, pass ADC CH3 signal (DEFAULT) 1 = Mix I2S right channel ADC To DAC CH1 Source Select 00 = ADC CH0 (DEFAULT)

- Page 75 Function Name Description DRC ADC CH01 Knee Point 1 Select (Step size is 1dB.) 0x00 = 0dB 0x01 = -1dB DRC_KNEE1_ ▼ IP_ADC_CH01 0x06 = -6dB (DEFAULT) ▼ 0x1E = -30dB 0x1F = -31dB DEFAULT 0x1486 DRC ADC CH01 Knee Point 4 Select (Step size is 1dB.) 0x00 = -35dB 0x01 = -36dB...

- Page 76 Function Name Description DRC ADC CH01 Peak Detection Release Time (Ts = 1/SMPL_RATE) 0000 = 63*Ts 0001 = 127*Ts DRC_PK_CO 0010 = 255*Ts 0011 = 511*Ts EF2_ADC_CH 0100 = 1023*Ts 0101 = 2047*Ts (DEFAULT) 0110 = 4095*Ts 0111 = 8191*Ts 1001= 16383*Ts DRC ADC CH01 Attack Time (Ts = 1/SMPL_RATE)

- Page 77 Function Name Description DRC ADC CH23 Knee Point 3 Select (Step size is 1dB.) 0x00 = -18dB 0x01 = -19dB DRC_KNEE3_ ▼ IP_ADC_CH23 0x12 = -36dB (DEFAULT) ▼ 0x1E = -80dB 0x1F = -81dB DEFAULT 0x0F12 DRC ADC CH23 Noise Gate Slope DRC_NG_SLP 00 = 1:1 01 = 2:1...

- Page 78 Function Name Description DRC ADC CH23 Decay Time (Ts = 1/SMPL_RATE) 0000 = 63*Ts 0001 = 127*Ts 0010 = 255*Ts 0011 = 511*Ts DRC_DCY_A 0100 = 1023*Ts 0101 = 2047*Ts DC_CH23 0110 =4095*Ts 0111 = 8191*Ts (DEFAULT) 1000 = 16383*Ts 1001 = 32757*Ts 1010 = 65535*Ts DEFAULT...

- Page 79 Function Name Description DRC DAC Noise Gate Slope DRC_NG_SLP 00 = 1:1 01 = 2:1 _DAC 10 = 4:1 (DEFAULT) 11 = 8:1 DRC DAC Expansion Slope DRC_EXP_SL 00 = 1:1 01 = 2:1 P_DAC 10 = 4:1 (DEFAULT) 11 = 8:1 DRC DAC Compressor Slope (Lower Region) 000 = 0 001 = 1:2...

- Page 80 Function Name Description RESERVED RESERVED MODE1 DEFAULT Read Only RESERVED RESERVED MODE2 DEFAULT Read Only Class-G Function Clock Divider Select 00 = Clock 2MHz (DEFAULT) CLASSG_CLK 01 = 1/3 MCLK _SRC 10 = MCLK 11 = Disable CLK (disable charge pump) Class-G Timer Select (Define time for supplies go to +-0.9 after a Class G signal goes lower than threshold voltage.)

- Page 81 Function Name Description MISC_CT RESERVED RESERVED Time-out Function Disable Control TIMEOUT_DIS 0 = Disable (DEFAULT) ABLE I2C_TIME 1 = Enable TIMEOUT_TM Time-out Function Coefficient DEFAULT 0xEFFF TEST_MO TEST_MODE RESERVED DEFAULT 0x0000 I2C_DEVICE_I I2C Device ID I2C_DEVI CE_ID REG_SI_REV I2C Silicon Revision ID DEFAULT Read Only 0x1AF1 RAM Test Status Bit...

- Page 82 Function Name Description Headphone Output Driver Current Trim Select 1 DRV_IBCTRH 0 = Low drive current (DEFAULT) 1 = High drive current Headphone Output Driver Current Trim Select 2 DRV_ICUTHS 0 = Low drive current (DEFAULT) 1 = High drive current TRIM_SE Offset Trim Disable Control TTINGS...

- Page 83 Function Name Description DAC Test Mode 0 = Disable (DEFAULT) TESTDAC 1 = Enable Bit0 = Force headphone left DAC to GND Bit1 = Force headphone right DAC to GND RESERVED RESERVED Headphone Right Output Path Enable Control 0 = Disable (DEFAULT) 1 = Enable ENHSR Bit0 = Enable DAC right channel to right headphone...

- Page 84 Function Name Description Left Channel Class-D Driver Gain For DAC Right Input (Step size is 1dB.) 00000 = Mute (DEFAULT) CLASSDGAIN 00001 = 0dB 00002 = 1dB ▼ 11000 = 23dB 11001 = 24dB DEFAULT 0x0000 RESERVED RESERVED Right Channel Class-D Driver Gain For DAC Left Input (Step size is 1dB.) 00000 = Mute (DEFAULT)

- Page 85 Function Name Description DAC Enable Control 0 = Disable (DEFAULT) DAC_EN 1 = Enable Bit0 = Left DAC Bit1 = Right DAC DAC Clock Enable Control 0 = Disable (DEFAULT) CLK_DAC_EN 1 = Enable Bit0 = Left DAC Bit1 = Right DAC DAC Smoothing Filter On HS Output Enable Control FC_CTR...

- Page 86 Function Name Description PGA In Class-A Mode Of Operation Enable Instead Of Class-AB Enable Control STG2_SEL 0 = Disable (DEFAULT) 1 = Enable VMID Pre-charge Disable Control PDVMDFST 0 = Disable (DEFAULT) 1 = Enable Global Analog Bias Enable Control BIASEN 0 = Disable (DEFAULT) 1 = Enable...

- Page 87 Function Name Description Right Channel PGA Input Mode Select 0 = Disable (DEFAULT) 1 = Enable Bit0 = MONO-/HSMIC+/HSMIC- (QFN) FEPGA_MOD AUX_R/HSMIC+/HSMIC- (WLCSP) Bit1 = MIC2+/DMCLK2/MIC2-/DMDATA2/AUXR(QFN) MIC2+/DMCLK2/MIC2-/DMDATA2 (WLCSP) Bit2 = RESERVED Bit3 = Shorts each inputs and terminates with 12kOhm differentially Left Channel PGA Input Mode Select 0 = Disable (DEFAULT)

- Page 88 Function Name Description RESERVED RESERVED Right Channel Front End PGA Attenuation Control QFN (MONO-/HSMIC+)&(HSMIC-) WLCSP (AUXR/HSMIC+)&(HSMIC-) (Step size is 1.5dB.) FEPGA_ATTN 00000 = 0dB (DEFAULT) 00001 = -1.5dB ▼ 11110 = -45dB 11111 = -46.5dB FEPGA_A TTENUAT RESERVED RESERVED Left Channel Front End PGA Attenuation Control QFN (AUXL/MONO+)&(MONO-/HSMIC+) WLCSP (AUXL/MONO+)&(MONO-) (Step size is 1.5dB.)

- Page 89 Function Name Description Main Driver Power Enable Control 0 = Disable (DEFAULT) PUP_MAIN_D 1 = Enable Bit0 = Left HP driver Bit1 = Right HP driver DEFAULT 0x0000 RESERVED RESERVED Speaker Pull Down Resistor Enable Control (Only work with PUP_MAIN_DRV=00) 0 = Disable (DEFAULT) PULL_SPKR_ 1 = Enable...

-

Page 90: Typical Application Diagram

13 Typical Application Diagram +1.8V +1.8V +1.8V +1.8V VDDMIC DMIC1L DMIC1R DMIC2R DMIC2L VDDA VDDC VDDB 200 Ohm Line In AUX_L/MONO + SCLK MIC1+/DMCLK1 SDIO MIC1-/DMDATA1 GPIO1/CSB VSSA +1.8V VDDA VDDSPK MICBIAS QFN 48-pin SPKOUTR+ VDDMIC +3.3V MICDET VSSSPK SPKOUTR- VREF VDDSPK VSSA... -

Page 91: Package Information

14 Package Information 14.1 QFN 48L 7X7MM^2 QFN 48L 7X7 MM^2, Thickness: 0.9 MM (Saw type) COPLANARITY SYMBOL TOTAL THICKNESS 0.85 0.90 STAND OFF 0.00 0.04 0.05 MOLD THICKNESS 0.65 0.67 L/F THICKNESS 0.203 REF LEAD WIDTH 0.20 0.25 0.30 BODY SIZE 7.0 BSC 7.0 BSC... -

Page 92: Qfn48L 6X6Mm^2

14.2 QFN48L 6x6MM^2 QFN 48L 6X6 MM^2, Thickness: 0.9 mm (Max) Pitch 0.4mm Apr 11, 2022 Page 92 of 96 Rev 2.1... -

Page 93: Wlcsp 56 Balls

14.3 WLCSP 56 Balls 56 Balls WLCSP with Pitch 0.4mm Bottom View MIC2-/ MIC2+/ GP4/ HSMIC- VDDB VSSD DACIN DMDATA2 DMCLK2 GP2/ AUXL/ HSMIC+ VDDC MCLK SCLK JKDET MONO+ MIC1+/ AUX_R/ VSSA IFSEL BCLK SDIO MONO- DMCLK1 MIC1-/ VDDA BIAS DMDATA1 3.66mm VREF... -

Page 94: Ordering Information

NAU88L24IG 6 X 6 mm QFN-48 Green NAU88L24VG 3.22 X 3.66 mm 56 Balls WLCSP Green NAU88L24 _ _ Package Material: Pb-free Package Package Type: 48-Pin QFN Package 48-Pin QFN Package WLCSP Package Apr 11, 2022 Page 94 of 96... -

Page 95: Revision History

Revision History VERSION DATE DESCRIPTION Mar 23, 2016 Initial Release P.17, P.57, p.68 Reg0x1A default setting is 0040 with description P.81, Register 69 VDDB changed to VDDA Mar 23, 2016 P.10, 12 Notes described supplies domain for pins P.14, adding HPL&HPR maximum loading capacitance P.86, Reg80 JAMFORCE1,2, JAMNODCLOW P.36, Table 23 LR_DIV correction from 3 bits to 2 bits P.35 Fig.8 changed... -

Page 96: Important Notice

All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claims to Nuvoton as a result of customer’s Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Need help?

Do you have a question about the NAU88L24 and is the answer not in the manual?

Questions and answers