Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Acromag AcroPack AP522

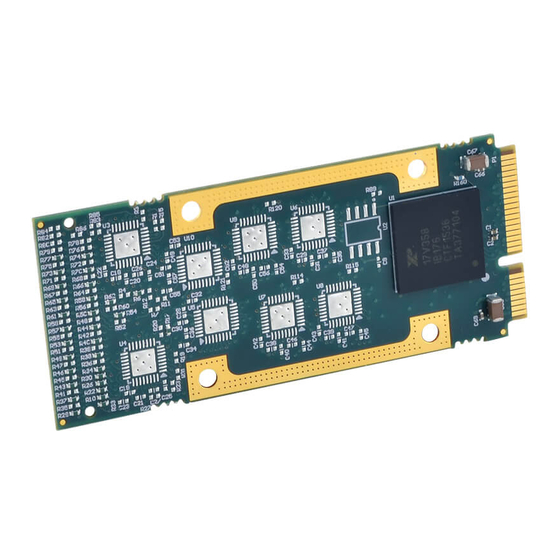

- Page 1 AP522 AcroPack Serial Communication Module USER’S MANUAL ACROMAG INCORPORATED 30765 South Wixom Road Wixom, MI 48393-2417 U.S.A. Tel: (248) 295-0310 Email: solutions@acromag.com Copyright 2019, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice. 8501139B...

-

Page 2: Table Of Contents

2.4 Field I/O Connector ....................10 Table 2.1 Field I/O Connector Pin Assignments ................11 2.5 RS-422/485 Termination ..................... 14 2.6 Noise and Grounding Considerations ................14 2.7 Logic Interface Connector ................... 14 Acromag, Inc. Tel: 248-295-0310 - 1 - - 1 - http://www.acromag.com www.acromag.com... - Page 3 3.4.3 Baud Rate Generator Divisors (DLM, DLL and DLD) ..............29 3.4.3.1 DLM[7:0], DLL[7:0] and DLD[3:0] ................... 30 Table 3.9 Typical Data Rates with Internal 125MHz Clock at 16X Sampling ....... 31 Acromag, Inc. Tel: 248-295-0310 - 2 - - 2 - http://www.acromag.com...

- Page 4 3.4.20 XCHAR Register – Read Only ....................47 Table 3.23 XCHAR Register ......................47 4.0 SERVICE AND REPAIR ....................49 4.1 Service and Repair Assistance ..................49 4.2 Preliminary Service Procedure ..................49 Acromag, Inc. Tel: 248-295-0310 - 3 - - 3 - http://www.acromag.com www.acromag.com...

- Page 5 Table 5.4 MTBF (AP522-LF) ......................51 5.5 PCIe Bus Specifications ....................52 APPENDIX A .......................... 53 AP-CC-01 Heatsink Kit Installation ..................53 CERTIFICATE OF VOLATILITY ..................56 REVISION HISTORY ......................57 Acromag, Inc. Tel: 248-295-0310 - 4 - - 4 - http://www.acromag.com www.acromag.com...

-

Page 6: General Information

The information contained in this manual is subject to change without notice, and Acromag, Inc. (Acromag) does not guarantee its accuracy. Acromag makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. -

Page 7: Acropack Information - All Models

Programmable Baud Rate – Each individual channel has its own programmable baud rate generator with fractional divisor. While the UART supports data rates up to 31.25Mbps, the serial transceivers only support data rates up to 20Mbps. Acromag, Inc. Tel: 248-295-0310 - 6 - - 6 - http://www.acromag.com... -

Page 8: Key Features Pcie Interface

Compatibility – PCI Express Base Specification v2.1 compliant PCI Express Endpoint. 1.4 Signal Interface Products This AcroPack module will mate directly to all Acromag AP carriers. Once connected, the module is accessed via a front panel connector. The cables and termination panels are also available. For optimum performance with the AP522 communication modules, use of the shortest possible length of shielded I/O cable is recommended. -

Page 9: References

AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of “C” functions which link with existing user code to make possible simple control of all Acromag AcroPack modules. 1.6 References The following resources regarding AcroPack modules are available for download on Acromag’s website or by contacting your sales representative. -

Page 10: Preparation For Use

It is important that the user employ satisfactory overall system design. It is understood and agreed by the Buyer and Acromag that this is the Buyer's responsibility. -

Page 11: Installation Considerations

Refer to the specifications section for loading and power requirements. Be sure that the system power supplies are able to accommodate the power IMPORTANT: Adequate air requirements of the system boards, plus the installed Acromag board, circulation must be provided to within the voltage tolerances specified. - Page 12 Field I/O 13 TXD-_C Field I/O 14 TXD+_C RSVD/ISOL RSVD/ISOL Field I/O 15 RXD-_C Field I/O 16 RXD+_C RSVD/ISOL RSVD/ISOL Field I/O 17 TXD-_D Field I/O 18 TXD+_D Acromag, Inc. Tel: 248-295-0310 - 11 - - 11 - http://www.acromag.com www.acromag.com...

- Page 13 Field I/O 30 RXD+_F RSVD/ISOL RSVD/ISOL Field I/O 31 Field I/O 32 RSVD/ISOL RSVD/ISOL Field I/O 33 TXD-_G Field I/O 34 TXD+_G RSVD/ISOL RSVD/ISOL Field I/O 35 RXD-_G Acromag, Inc. Tel: 248-295-0310 - 12 - - 12 - http://www.acromag.com www.acromag.com...

- Page 14 Field I/O 46 RSVD/ISOL RSVD/ISOL No Connect Field I/O 47 No Connect Field I/O 48 RSVD/ISOL RSVD/ISOL Field I/O 49 No Connect No Connect Field I/O 50 RSVD/ISOL RSVD/ISOL Acromag, Inc. Tel: 248-295-0310 - 13 - - 13 - http://www.acromag.com www.acromag.com...

-

Page 15: Rs-422/485 Termination

N.C. (LED_WLAN#) +3.3V N.C. (LED_WWAN#) +3.3V N.C. (USB_D+) N.C. (USB_D-) PETp0 PETn0 SMB_DATA SMB_CLK N.C. (+1.5V) PERp0 PERn0 +3.3V PERST# TDI (UIM_C4) N.C. (W_DISABLE#) TDO (UIM_C8) N.C. (UIM_VPP) Acromag, Inc. Tel: 248-295-0310 - 14 - - 14 - http://www.acromag.com www.acromag.com... - Page 16 AP522 module. Note 6: TDI is tied to TDO on the AP522 module as it does not use JTAG. Acromag, Inc. Tel: 248-295-0310 - 15 - - 15 - http://www.acromag.com...

-

Page 17: Programming Information

Address Registers and the Interrupt Register which must be read to determine the base address assigned to the board and the interrupt request that goes active on a board interrupt request. Acromag, Inc. Tel: 248-295-0310 - 16 - - 16 - http://www.acromag.com... -

Page 18: Uart And Device Configuration Registers

The Device Configuration Registers are accessible from all UART channels, however not all bits can be controlled by all channels. The control of the 8XMODE, 4XMODE, RESET, and SLEEP bits are only available for that particular channel. Acromag, Inc. Tel: 248-295-0310 - 17 - - 17 - http://www.acromag.com... - Page 19 0x1000-0x13FF Repeat above registers for UART 4 0x1400-0x17FF Repeat above registers for UART 5 0x1800-0x1BFF Repeat above registers for UART 6 0x1C00-0x1FFF Repeat above registers for UART 7 Acromag, Inc. Tel: 248-295-0310 - 18 - - 18 - http://www.acromag.com www.acromag.com...

- Page 20 Read/Write MPIO[15:8] 0x00 level control 0x097 MPIO3T[15:8] Not Used. 0x00 0X098 MPIOINV[15:8] Not Used. 0x00 0x099 MPIOSEL[15:8] Not Used. 0xFF 0x09A MPIOOD[15:8] Not Used. 0x00 0x09B Reserved 0x00 Acromag, Inc. Tel: 248-295-0310 - 19 - - 19 - http://www.acromag.com www.acromag.com...

-

Page 21: The Global Interrupt Registers - Int0, Int1, Int2 And Int3

All bits start up zero. A special interrupt condition is generated by the XR17V358 upon awakening from sleep after all eight channels were put to sleep mode earlier. This wake-up interrupt is cleared by a read to the INT0 register. Acromag, Inc. Tel: 248-295-0310 - 20 - - 20 - http://www.acromag.com... -

Page 22: Interrupt Clearing

Channel 0 interrupt. It is controlled through 4 configuration registers [TIMERCNTL, TIMER, TIMELSB, TIMERMSB]. The TIMERCNTL register provides the Timer commands such as start/stop. 3.2.2.1 TIMERMSB[31:24] and TIMERLSB[23:16] Acromag, Inc. Tel: 248-295-0310 - 21 - - 21 - http://www.acromag.com www.acromag.com... -

Page 23: Timercntl[7:0] Register

The following paragraphs describe the operation of the 16-bit Timer/Counter. The following conventions will be used in this discussion: • ’N’ is the 16-bit value programmed in the TIMER MSB, LSB registers Acromag, Inc. Tel: 248-295-0310 - 22 - - 22 - http://www.acromag.com... -

Page 24: 8Xmode[7:0] (Default 0X00)

0x00 at all other times. Stopping the Timer does not clear the interrupt and neither does subsequent restarting. 3.2.3 8XMODE[7:0] (default 0x00) Each bit selects 8X or 16X sampling rate for that UART channel. The Acromag, Inc. Tel: 248-295-0310 - 23 - - 23 - http://www.acromag.com... -

Page 25: 4Xmode[15:8] (Default 0X00)

A receive data start bit transition will not wake up the UART if the Multidrop mode is disabled (DLD[6] = 0) and the receiver is disabled (MSR[2] = 1, MSR[0] = 0). Acromag, Inc. Tel: 248-295-0310 - 24 - - 24 - http://www.acromag.com... -

Page 26: Dvid[15:8]

3.2.10 MPIO Registers The MPIO pins of the Exar device are reserved for device identification. As inputs, MPIO[15:0] on the AP522 module will read 0x0001 through the MPIOLVL registers. Acromag, Inc. Tel: 248-295-0310 - 25 - - 25 - http://www.acromag.com... -

Page 27: Transmit And Receive Data

0x0100 (channel 0), 0x0500 (channel 1), 0x0900 (channel 2), 0x0D00 (channel 3), 0x1100 (channel 4), 0x1500 (channel 5), 0x1900 (channel 6), 0x1D00 (channel 7). This operation is 4 times faster than reading the data in 256 Acromag, Inc. Tel: 248-295-0310 - 26 - - 26 - http://www.acromag.com... -

Page 28: Fifo Data Loading/Unloading Through The Uart Channel Registers, Thr And Rhr, In 8-Bit Format

0 0 0 0 DLL - Divisor LSB Read/Write LCR[7]=1 0 0 0 1 IER - Interrupt Enable Register Read/Write LCR[7]=0 0 0 0 1 DLM - Divisor MSB Read/Write LCR[7]=1 Acromag, Inc. Tel: 248-295-0310 - 27 - - 27 - http://www.acromag.com www.acromag.com... -

Page 29: Receiver

The transmitter section comprises of a 256 byte FIFO, a byte-wide Transmit Holding Register (THR) and an 8-bit Transmit Shift Register (TSR). THR receives a data byte from the host (non-FIFO mode) or a data byte from the Acromag, Inc. Tel: 248-295-0310 - 28 - - 28 - http://www.acromag.com... -

Page 30: Transmit Holding Register (Thr)

3.4.3 Baud Rate Generator Divisors (DLM, DLL and DLD) Each UART has its own Baud Rate Generator (BRG) with a prescaler for the transmitter and receiver. The prescaler is controlled by a software bit in the Acromag, Inc. Tel: 248-295-0310 - 29 - - 29 - http://www.acromag.com... -

Page 31: Dlm[7:0], Dll[7:0] And Dld[3:0]

DLD = ROUND ( (Calculated Divisor - TRUNC (Calculated Divisor) )*16) In the formulas above, please note that: TRUNC (N) = Integer Part of N. For example, TRUNC (5.6) = 5. ROUND (N) = N rounded towards the closest Acromag, Inc. Tel: 248-295-0310 - 30 - - 30 - http://www.acromag.com... -

Page 32: Dld[7:4]

When the receive FIFO (FCR bit [0] = logic 1) and receive interrupts (IER bit [0] = logic 1) are enabled, the RHR interrupts (see ISR bits [4:3]) status will reflect the following: Acromag, Inc. Tel: 248-295-0310 - 31 - - 31 - http://www.acromag.com... -

Page 33: Ier Versus Receive/Transmit Fifo Polled Mode Operation

Note that the receive FIFO must also be enabled via bit-0 of the FCR in FIFO mode. TX Ready Interrupt Enable: 0 = Disable transmit ready interrupt (default). Acromag, Inc. Tel: 248-295-0310 - 32 - - 32 - http://www.acromag.com... - Page 34 When software flow control in enabled, and one or two sequential receive data characters match the preprogrammed Xoff 1-2 values an interrupt will be issued. RTS# Output Interrupt Enable: Not supported. Acromag, Inc. Tel: 248-295-0310 - 33 - - 33 - http://www.acromag.com www.acromag.com...

-

Page 35: Interrupt Status Register (Isr) - Read Only

Special character interrupt is cleared by a read to ISR. • Wake-up indicator is cleared by a read to the INT0 register. Table 3.12 Interrupt Source and PRIORITY ISR BITS Source of the Interrupt Priority Level Acromag, Inc. Tel: 248-295-0310 - 34 - - 34 - http://www.acromag.com www.acromag.com... -

Page 36: Fifo Control Register (Fcr) - Write Only

1 = Reset the receive FIFO pointers and FIFO level counter logic (the receive shift register is not cleared or altered). This bit will return to logic 0 after resetting the FIFO. Tx FIFO Reset: Acromag, Inc. Tel: 248-295-0310 - 35 - - 35 - http://www.acromag.com... - Page 37 Table 3.14 Transmit and Receive Trigger FCTR Compatibility FIFO Trigger Table and Level Table [7:6] [7:6] [5:4] Trigger Trigger Selection Level Level 16C550, 16C2550, 16C2552, 16C554, 16C580, 16L580 Acromag, Inc. Tel: 248-295-0310 - 36 - - 36 - http://www.acromag.com www.acromag.com...

-

Page 38: Line Control Register (Lcr) - Read/Write

0 0 = 5 Data Bits 0 1 = 6 Data Bits Length 1 0 = 7 Data Bits 1 1 = 8 Data Bits Select Stop Bit 0 = 1 Stop Bit Acromag, Inc. Tel: 248-295-0310 - 37 - - 37 - http://www.acromag.com www.acromag.com... - Page 39 Note that bit 7 must be set high to access the divisor latch registers DLL & DLM of the baud rate generator or access the Enhanced Feature Register (EFR). Bit 7 must be low to access the Receiver Holding Register (RHR), the Acromag, Inc. Tel: 248-295-0310 - 38 - - 38 - http://www.acromag.com...

-

Page 40: Modem Control Register (Mcr) - Read/Write

Programmable Baud Rate Generator without further modification. 1 = Divide by four. 125MHz divided by 4, or 31.25MHz, is fed to the Programmable Baud Acromag, Inc. Tel: 248-295-0310 - 39 - - 39 - http://www.acromag.com... -

Page 41: Line Status Register (Lsr) - Read Only

Error following last data bit or parity bit detected as a zero/space bit). This bit is reset low when the CPU reads the contents of the LSR. In FIFO Acromag, Inc. Tel: 248-295-0310 - 40 - - 40 - http://www.acromag.com... -

Page 42: Modem Status Register (Msr) - Read Only

3.4.10 Modem Status Register (MSR) – Read Only The Modem Status Register (MSR) provides the host CPU with an indication on the status of the modem input line from a modem or other peripheral device. Acromag, Inc. Tel: 248-295-0310 - 41 - - 41 - http://www.acromag.com... -

Page 43: Modem Status Register (Msr) - Write Only

The bits are enabled by EFR bit-4. Table 3.19 Auto RS485 Half- MSR[7:4] DELAY IN BIT TIMES Duplex Direction Control Delay from Transmit to Receive 0000 0001 0010 0011 0100 Acromag, Inc. Tel: 248-295-0310 - 42 - - 42 - http://www.acromag.com www.acromag.com... -

Page 44: Msr[3:0]

1 = Xon/xoff software flow control characters will be transmitted even though the transmitter is disabled. Receiver 0 = Enable Receiver (default). Disable 1 = Disable Receiver Acromag, Inc. Tel: 248-295-0310 - 43 - - 43 - http://www.acromag.com www.acromag.com... - Page 45 FIFO will be sent out. Please note that setting this bit to a logic 1 stops any character from going out. Also, this bit must be a logic 0 for the Send Char Immediate function (see MCR[3]). Acromag, Inc. Tel: 248-295-0310 - 44 - - 44 - http://www.acromag.com...

-

Page 46: Scratch Pad (Scr) - Read/Write

Feature Register Software 00XX = No Transmit Flow Control Flow 10XX = Transmit Xon1/Xoff1 Control 01XX = Transmit Xon2/Xoff2 11XX = Transmit Xon1 and Xon2, Xoff1 and Xoff2 Acromag, Inc. Tel: 248-295-0310 - 45 - - 45 - http://www.acromag.com www.acromag.com... - Page 47 (EFR bits 0-3 must be set to a logic “0”). Not supported. Hardware Flow Control Not Supported. Hardware Flow Control Acromag, Inc. Tel: 248-295-0310 - 46 - - 46 - http://www.acromag.com www.acromag.com...

-

Page 48: Transmit Fifo Level Counter - Read Only

If the last received control character was a Xon Detect character, Xon characters (Xon1, Xon2) or an Xon- Indicator Any character, this bit will be set to a logic 1. This Acromag, Inc. Tel: 248-295-0310 - 47 - - 47 - http://www.acromag.com www.acromag.com... - Page 49 If the last transmitted control character was a Xon character or characters (Xon1, Xon2), this bit will Indicator be set to a logic 1. This bit will clear after the read. Reserved. Reserved. Acromag, Inc. Tel: 248-295-0310 - 48 - - 48 - http://www.acromag.com www.acromag.com...

-

Page 50: Service And Repair

SMT repair and service tools are used. For these and other reasons, it is strongly recommended that a non-functioning board be returned to Acromag for repair. Acromag has automated diagnostic and test equipment that thoroughly checks the performance of suspect boards. -

Page 51: Specifications

Note 1: An air cooled application with an AcroPack module will require a minimum airflow of 200LFM. Note 2: A conduction cooled application with an AcroPack module will require purchase of the Heatsink AP-CC-01. Acromag, Inc. Tel: 248-295-0310 - 50 - - 50 - http://www.acromag.com... -

Page 52: Other Environmental Requirements

FN2. Per MIL-HDBK-217, Ground Benign, Controlled, G Temperature MTBF (Hours) MTBF (Years) Failure Rate (FIT Table 5.4 MTBF (AP522-LF) 25°C 7,878,110 899.3 126.9 40°C 5,290,138 603.9 189.0 FIT is Failures in 10 hours. Acromag, Inc. Tel: 248-295-0310 - 51 - - 51 - http://www.acromag.com www.acromag.com... -

Page 53: Pcie Bus Specifications

5.5 PCIe Bus Specifications Compatibility Conforms to PCI Express Base Specification, Revision 2.0 Line Speed Gen1 (2.5Gbps) Lane Operation 1-Lane 16K Memory Space Required One Base Address Register Acromag, Inc. Tel: 248-295-0310 - 52 - - 52 - http://www.acromag.com www.acromag.com... -

Page 54: Ap-Cc-01 Heatsink Kit Installation

AP-CC-01 Heatsink Kit Installation Hardware Bottom view Top view AP-CC-01 Heat Sink Kit This example will show how to install the AP-CC-01 Heatsink kit with an APCe7020 carrier. Acromag, Inc. Tel: 248-295-0310 - 53 - - 53 - http://www.acromag.com www.acromag.com... - Page 55 USER’S MANUAL AP522 ACROPACK 1. Install two standoffs and secure with two screws. 2. Install the AcroPack module. 3. Install the Heatsink and secure with 4 screws. Acromag, Inc. Tel: 248-295-0310 - 54 - - 54 - http://www.acromag.com www.acromag.com...

- Page 56 USER’S MANUAL AP522 ACROPACK 4. AP-CC-01 Installation is complete. Note: Make sure the thermal pad is making contact with the UART IC. Acromag, Inc. Tel: 248-295-0310 - 55 - - 55 - http://www.acromag.com www.acromag.com...

-

Page 57: Certificate Of Volatility

Does this product contain Non-Volatile memory (i.e. Memory of whose contents is retained when power is removed) ■ No □ Yes Acromag Representative Name: Title: Email: Office Phone: Office Fax: Russ Nieves Director of solutions@acromag.com 248-295-0310 248-624-9234 Sales and Marketing Acromag, Inc. Tel: 248-295-0310 - 56 - - 56 - http://www.acromag.com www.acromag.com... -

Page 58: Revision History

28 JAN 2019 LMP/ARP Initial Release. 11 JUL 2019 ENZ/ARP Updated UART register descriptions and Baud Rate selection details. Added Appendix A. Updated “Where to Get Help” section. Acromag, Inc. Tel: 248-295-0310 - 57 - - 57 - http://www.acromag.com www.acromag.com...

Need help?

Do you have a question about the AcroPack AP522 and is the answer not in the manual?

Questions and answers