Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Acromag APZU AcroPack Series

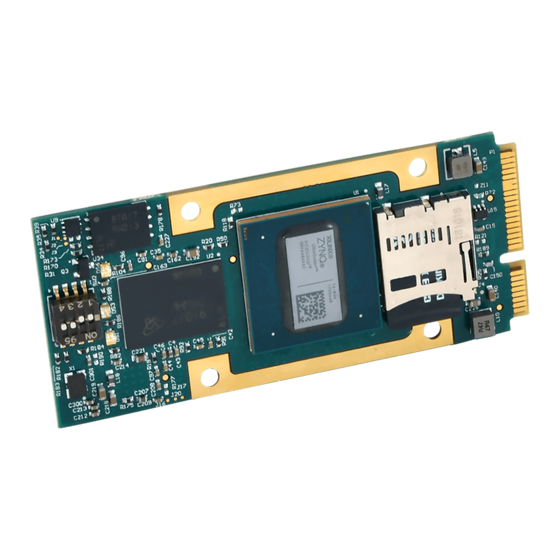

- Page 1 Zynq Ultrascale+ Based Module USER’S MANUAL ACROMAG INCORPORATED 30765 South Wixom Road Wixom, MI 48393-2417 U.S.A. Tel: (248) 295-0310 Fax: (248) 624-9234 Copyright 2020, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice. 8501150A...

-

Page 2: Table Of Contents

2.4 Field I/O Connector ...................... 12 Table 2.2 Field I/O Connector Pin Assignments .................. 12 2.5 Logic Interface Connector ..................... 14 Table 2.3 Logic Interface Connections ....................14 3.0 PROGRAMMING INFORMATION ................16 Acromag, Inc. Tel: 248-295-0310 - 1 - www.acromag.com... - Page 3 4.2 Digital Interface Logic ....................26 5.0 OVERVIEW OF XILINX VIVADO AND VITIS TOOLS .......... 31 5.0.1 APZU Testing Hardware Requirements ................... 31 5.0.2 Vitis Integrated Design Environment and Vivado Design Suite ..........31 Acromag, Inc. Tel: 248-295-0310 - 2 - www.acromag.com...

- Page 4 8.3.3 Isolation ..........................70 8.3.4 Vibration and Shock Standards ....................70 8.3.5 EMC Directives ........................70 8.4 Reliability Prediction ...................... 70 Table 8.4.1 MTBF of APZU-303 ......................70 8.5 Field I/O ........................71 Acromag, Inc. Tel: 248-295-0310 - 3 - www.acromag.com...

-

Page 5: General Information

The information contained in this manual is subject to change without notice, and Acromag, Inc. (Acromag) does not guarantee its accuracy. Acromag makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. -

Page 6: Acropack Information - All Models

C to 75 1.3.2 Key Features Zynq UltraScale Plus device XCZU3CG o Dual-core ARM Cortex-A53 Processing Unit 1.5GHz CPU Single/double precision Floating Point Unit o Dual-core ARM Cortex-R5 Real-Time processor system Acromag, Inc. Tel: 248-295-0310 - 5 - www.acromag.com... -

Page 7: Key Features Pcie Interface

PCIe Bus – The AP module includes a PCI Express Generation 1 interface operating at a bus speed of 2.5 Gbps with one lane in each direction. Compatibility – PCI Express Base Specification v2.1 compliant PCI Express Endpoint. Acromag, Inc. Tel: 248-295-0310 - 6 - www.acromag.com... - Page 8 (512 x 32) XCZU3CG Ethernet MAC USB-UART AcroPack 50 Pin Boot Mode Power Chip 3.3V TTL Digital Bank 26 3 RS485 Ports Programmable Logic (PL) Bank 65 Figure 1 Block Diagram Model APZU-303 Acromag, Inc. Tel: 248-295-0310 - 7 - www.acromag.com...

-

Page 9: Signal Interface Products

Bank 65 Figure 2 Block Diagram Model APZU-301/304 1.4 Signal Interface Products This AcroPack Module will mate directly to all Acromag AP carriers. Once connected, the module is accessed via a 68 pin front panel connector. Breakout Panel The cables and termination panels are also available. The APZU Cable... -

Page 10: Windows

AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of “C” functions which link with existing user code to make possible simple control of all Acromag AcroPack modules. 1.6 References The following resources regarding AcroPack modules are available for download on Acromag’s website or by contacting your sales representative. -

Page 11: Preparation For Use

It is important that the user employ satisfactory overall system design. It is understood and agreed by the Buyer and Acromag that this is the Buyer's responsibility. -

Page 12: Installation Considerations

Refer to the specifications section for loading and power requirements. Be sure that the system power supplies are able to accommodate the power IMPORTANT: Adequate air requirements of the system boards, plus the installed Acromag board, circulation must be provided to within the voltage tolerances specified. -

Page 13: Field I/O Connector

60 Volt isolation. The signals listed in Table 2.2 are available on the APZU Cable Breakout panel Acromag part number 5028-626. For the APZU-303 these signals include: 20 TTL, three RS485 signal pairs, UART to USB port, USB 2.0, Ethernet via RJ-45, push button reset, and power-on push button. - Page 14 PS_POR_PB SW2 Reset POWER_EN_PB POWER_EN_PB SW1 Power Notes (2.1): 1. J4 – Carrier Field I/O 68-pin Champ Manufacturer Name: TE Connectivity Part: 5796055-1 2. J5 – USB Shielded I/O Receptacle Molex 67329-8001 Acromag, Inc. Tel: 248-295-0310 - 13 - www.acromag.com...

-

Page 15: Logic Interface Connector

N.C. (LED_WPAN#) N.C. (LED_WLAN#) +3.3V N.C. (LED_WWAN#) +3.3V N.C. (USB_D+) N.C. (USB_D-) PETp0 PETn0 SMB_DATA SMB_CLK +1.5V PERp0 PERn0 +3.3V PERST# TDI (UIM_C4) N.C. (W_DISABLE#) TDO (UIM_C8) UIM_VPP RECLK+ UIM_RESET REFCLK- UIM_CLK UIM_DATA Acromag, Inc. Tel: 248-295-0310 - 14 - www.acromag.com... - Page 16 Note 5: The SM bus signals SMB_CLK and SMB_DATA will be used to clock a carrier location serial stream from the carrier. These signals are under the control of the AcroPack module. Acromag, Inc. Tel: 248-295-0310 - 15 - www.acromag.com...

-

Page 17: Programming Information

Data Ports. The most important Configuration Registers are the Base Address Registers and the Interrupt Register which must be read to determine the base address assigned to the board and the interrupt request that goes active on a board interrupt request. Acromag, Inc. Tel: 248-295-0310 - 16 - www.acromag.com... - Page 18 Register accesses as 32, 16, and 8-bit data in memory space are permitted. In addition, the ingress translation register maps BAR2 PCIe bus space 64K byte space into the Zynq DDR memory space starting at 0x100_0000. Acromag, Inc. Tel: 248-295-0310 - 17 - www.acromag.com...

- Page 19 RS485 Direction Control Register 0x0000 0034→ 31:0 NOT USED 0x0000 01FF 0x0000 0200 31:0 Firmware Revision Register 0x0000 0204→ 31:0 NOT USED 0x0000 1FFF Note 1: RS485 is only available on the APZU-303 model. Acromag, Inc. Tel: 248-295-0310 - 18 - www.acromag.com...

-

Page 20: Global Interrupt Register (Read/Write) - (Bar1 + 0X0000 0000)

Module Site Location Bits. These bits identify the location on the carrier of the AP module. Carrier Site A 2 to 0 Carrier Site B Carrier Site C Carrier Site D Acromag, Inc. Tel: 248-295-0310 - 19 - www.acromag.com... -

Page 21: Digital Input/Output Registers (Read/Write) - (Bar1 + 0X0000 0008)

27 of this register. APZU-303 The data direction (input or output) of the 20 TTL digital channels is selected via bits-0 through 19 of this register. Acromag, Inc. Tel: 248-295-0310 - 20 - www.acromag.com... -

Page 22: Interrupt Enable Register (Read/Write) - (Bar1 + 0X0000 0010)

Interrupt Polarity Register. Channel read or write operations use 8-bit, 16-bit, or 32-bit data transfers. Note that interrupts will not occur unless they are enabled. Acromag, Inc. Tel: 248-295-0310 - 21 - www.acromag.com... -

Page 23: Interrupt Polarity Registers (Read/Write) - (Bar1 + 0X0000 0018)

The RS485 Data register is used to monitor/read or set/write channels 0 through 2. Channels 0 to 2 are accessed at the carrier base address + 0000_002C via data bits 0 to 2. Acromag, Inc. Tel: 248-295-0310 - 22 - www.acromag.com... -

Page 24: Rs485 Direction Control Register (Read/Write) - (Bar1 + 0X0000 0030)

ADC can be converted to temperature using the following equation. The 10-bits digitized and output from the ADC can be converted to temperature by using the following equation. �������������� × 509.3140064 ����������������������(°��) = − 280.2308787 1024 Acromag, Inc. Tel: 248-295-0310 - 23 - www.acromag.com... -

Page 25: Block Ram

Further, all event inputs are reset, set to positive events, and disabled following reset. A false input signal is ensured for inputs left floating (i.e. reads as 0). The Interrupt Enable bit is cleared with a software reset. Acromag, Inc. Tel: 248-295-0310 - 24 - www.acromag.com... -

Page 26: Quad-Spi Flash

2-Kbit EEPROM A 2-Kbit EEPROM is accessible over the I2C bus to store the unique 48-bit ethernet MAC address. ST Microelectronics The EEPROM is accessible through I2C slave device identifier address 0xA0. M24C02-RMC6TG Acromag, Inc. Tel: 248-295-0310 - 25 - www.acromag.com... -

Page 27: Theory Of Operation

With LVDS input an optional internal differential termination in the XDC file set DIFF_TERM_ADV = TERM_100 or DIFF_TERM = TRUE. Acromag, Inc. Tel: 248-295-0310 - 26 - www.acromag.com... - Page 28 (Reduced pin count GMII for direct connection) to Copper. The magnetics and RJ-45 connector needed to complete the ethernet interface are resident on the APZU Cable Breakout panel (Acromag part number 5028-626). The ethernet PHY pins RGMII are routed from Zynq PS MIO pins MIO64 to MIO77.

- Page 29 24.0 MHz oscillator. IMPORTANT: Only connect the USB cable after The USB connector is resident on the APZU Cable Breakout panel (Acromag the APZU has powered up. part number 5028-626). USB 5 volts will interfere The USB pins are routed from Zynq PS MIO pins MIO52 to MIO63.

- Page 30 FPGA is configured. The LED is located on the top side of the module near switch SW2. Clocks The APZU+ provides the following system clocks to the Zynq chip. PS_CLK: PS reference clock 33.333MHz Acromag, Inc. Tel: 248-295-0310 - 29 - www.acromag.com...

- Page 31 The APZU+ Reset is managed by the Texas Instrument Power Chip. At power-up the Zynq chip is held in reset until all power rails have ramped up and are stable. A push button on the APZU Cable Breakout panel Acromag part number 5028-626 allows manual resetting of the Zynq chip.

-

Page 32: Overview Of Xilinx Vivado And Vitis Tools

The installation and selection window is shown below for the Windows Self Extracting Web Installer. The AcroPack Zynq module is supported by Vitis WebPack which is free from Xilinx. Acromag, Inc. Tel: 248-295-0310 - 31 - www.acromag.com... -

Page 33: Vivado And The Programmable Logic

UltraScale+ Processing System, peripherals, and the interconnection of these components, along with their respective detailed configuration. Acromag provides an FPGA generated firmware example design that provides host access to the hardware digital I/O on the AP module. The example design is intended to be a starting point from which customers will develop their customized applications. - Page 34 This top level file ties together the design_1_wrapper.vhd and the M01_AXI.vhd file. The design_1_wrapper.vhd is generated by the IP Integrator Block Design. The M01_AXI.vhd was created by Acromag to allow custom VHDL control of the digital I/O. Acromag, Inc. Tel: 248-295-0310 - 33 - www.acromag.com...

- Page 35 USER’S MANUAL SERIES APZU+ ACROPACK The current project contains the Acromag example design. To access the ARM processing system, we open the block design of the Vivado project using IP Integrator. Select => Open Block Design The top level block diagram of the example design is shown in the Figure below.

- Page 36 USER’S MANUAL SERIES APZU+ ACROPACK The Block Memory Generator is configured as a True Dual Port RAM. The AXI_ACLK is configured as a 100MHz clock and associated with the M01_AXI interface. Acromag, Inc. Tel: 248-295-0310 - 35 - www.acromag.com...

- Page 37 USER’S MANUAL SERIES APZU+ ACROPACK The M01_AXI port is configured as 32-bit data, 32-bit address, AXI lite interface. Acromag, Inc. Tel: 248-295-0310 - 36 - www.acromag.com...

- Page 38 USER’S MANUAL SERIES APZU+ ACROPACK The AXI reset signal was also made available to the top level design. The AXI_RESETn signal is defined as shown below. Acromag, Inc. Tel: 248-295-0310 - 37 - www.acromag.com...

- Page 39 AXI interconnect slave interfaces configured above. Double click UART 1 canvas to access the UART 1 options. Notice the blocks checked below correspond with those enabled for operation in their corresponding configuration dialog. Acromag, Inc. Tel: 248-295-0310 - 38 - www.acromag.com...

- Page 40 USER’S MANUAL SERIES APZU+ ACROPACK In the Zynq block design window, select Advanced Configuration. Expand the UART Baud Rate Selection section and notice that the UART1 Baud rate is set to 115200. Acromag, Inc. Tel: 248-295-0310 - 39 - www.acromag.com...

- Page 41 Under PL to PS the IRQ0[0-7] is set to 1 as seen below. The Zynq GIC (generic interrupt controller) receives PL to PS interrupt on pl_ps_irq0. The Cortex-A53 MPCore uses an external generic interrupt controller GIC-400 to support interrupts. Acromag, Inc. Tel: 248-295-0310 - 40 - www.acromag.com...

- Page 42 The offset address and size corresponding to the M01_AXI, BRAM, and system management wizard are shown below. These addresses correspond to those given in the user’s manual. Acromag, Inc. Tel: 248-295-0310 - 41 - www.acromag.com...

- Page 43 Select Reset to confirm resetting of the output products Right click Your Design_1.bd again, then select Generate Output Products Make sure Synthesis Options is set to Global then click Generate to confirm. Click OK when generation is complete. Acromag, Inc. Tel: 248-295-0310 - 42 - www.acromag.com...

- Page 44 APZU_top.vhd file. This is how the IP block logic is connect the top level of the design. If necessary, edit the APZU_top.vhd for use with your updated design_1_wrapper.vhd. Select Run Synthesis, Implementation, and Generate Bitstream Select OK Acromag, Inc. Tel: 248-295-0310 - 43 - www.acromag.com...

- Page 45 Vivado can now be closed. Project development will continue with Vitis in section 5.2.1. When you create the platform in Vitis IDE using APZU_top.xsa, the ZIP file automatically unzips and files are created in the project platform folder. Acromag, Inc. Tel: 248-295-0310 - 44 - www.acromag.com...

-

Page 46: Apzu Programmable Logic Block Design Constraints

The process requires having Zynq MPSoC block in Vivado Block Design in order to include the PS in the project, and using the SDK to create a First Stage Boot Loader (FSBL) for the PS, an optional PS application, and finally Acromag, Inc. Tel: 248-295-0310 - 45 - www.acromag.com... -

Page 47: Vitis Integrated Design Environment (Ide)

Note that by default, the psu_init.tcl will be sourced prior to running your application. That is how the ARM gets initialized for proper operation. The First Stage Boot Loader (FSBL) handles this. Acromag, Inc. Tel: 248-295-0310 - 46 - www.acromag.com... -

Page 48: Creating A Hardware Platform Using Vitis Ide

When creating a new FSBL (First Stage Boot Loader) proceed as directed below. In the Vitis IDE, go to File => New => Platform Project. Enter the Hardware Platform name APZU_wrapper and click Next Acromag, Inc. Tel: 248-295-0310 - 47 - www.acromag.com... - Page 49 USER’S MANUAL SERIES APZU+ ACROPACK Browse to the APZU_top.xsa file in the myVitis folder => select open. Select Finish Acromag, Inc. Tel: 248-295-0310 - 48 - www.acromag.com...

- Page 50 USER’S MANUAL SERIES APZU+ ACROPACK The Vitis IDE generates the platform. The files that are generated are displayed in the explorer window as shown in the following figure. Acromag, Inc. Tel: 248-295-0310 - 49 - www.acromag.com...

- Page 51 Select Board Support Package under the standalone on psu_cortexa53_0 BSP. b. Click Modify BSP Settings. c. On the Overview page, select the xilffs, xilpm, xilsecure, Iwip211 (TCP/IP stack configuration) libraries. d. Select OK Acromag, Inc. Tel: 248-295-0310 - 50 - www.acromag.com...

- Page 52 USER’S MANUAL SERIES APZU+ ACROPACK Now build the hardware by right-clicking on APZU_wrapper > Build project. The hardware platform is ready. You can create applications using this platform and test on APZU-30x hardware. Acromag, Inc. Tel: 248-295-0310 - 51 - www.acromag.com...

- Page 53 Select psu_corexa53_0 as seen below. Select File => New => Application Project. Select => Next Select APZU_wrapper [custom] as Platform. Select Next. Enter the Application Project Name of APZU_Example With Create New hi-lighted Select=> Next Acromag, Inc. Tel: 248-295-0310 - 52 - www.acromag.com...

- Page 54 USER’S MANUAL SERIES APZU+ ACROPACK With standalone on psu_cortexa53_0 hi-lighted Select => Next Acromag, Inc. Tel: 248-295-0310 - 53 - www.acromag.com...

- Page 55 SD boot. Select => Create Image Using Windows Explorer, navigate to the application directory, then into APZU_Example, then into the newly created bootimage directory (./APZU_Example /_ide/bootimage). Notice that two files have been Acromag, Inc. Tel: 248-295-0310 - 54 - www.acromag.com...

- Page 56 Drivers from www.silabs.com. On the host system set the device manager properties. My Computer -> Properties -> Device Manager. Right-select on USB to UART Bridge -> select Properties. Under the Port Setting tab -> Select Acromag, Inc. Tel: 248-295-0310 - 55 - www.acromag.com...

- Page 57 Finally, make sure to select the correct Flash Type. For the APZU, it is QSPI-X4-SINGL. Select Program button Should proceed to Performing Program Operation. It will initialize, Erase, and then program the flash. Acromag, Inc. Tel: 248-295-0310 - 56 - www.acromag.com...

- Page 58 USER’S MANUAL SERIES APZU+ ACROPACK Test boot from flash. Set Dip switch with only switch 2 OFF all others ON position. Acromag, Inc. Tel: 248-295-0310 - 57 - www.acromag.com...

-

Page 59: Apzu Processing System Bare Metal Software

Since the host system is unaware of the AXI domain address on the Endpoint, an ingress translation is setup to map incoming BAR-hit transactions to AXI transactions. Before setting up the ingress translation Acromag, Inc. Tel: 248-295-0310 - 58 - www.acromag.com... - Page 60 6. Conclude by writing 0xA3 to the DMA0_CHAN_SCRATCH2 register. The host will poll the DMA0_CHAN_SCRATCH2 register for 0xA3 to identify ingress setup has completed. The various translation registers are listed in the Zynq UltraScale+ MPSoC Register Reference (UG1087) Acromag, Inc. Tel: 248-295-0310 - 59 - www.acromag.com...

- Page 61 SERIES APZU+ ACROPACK The print statements from the bare metal application running on the APZU are seen on a putty terminal. The host example design application prompts are shown in image to right. Acromag, Inc. Tel: 248-295-0310 - 60 - www.acromag.com...

-

Page 62: Ethernet Bare Metal Software

Enter Telnet 192.168.1.10 7 at the CMD prompt of the host computer The telnet session will start Each character entered will be echoed back as seen below. Note the escape character is Ctrl ] or ^] q will close the connection Acromag, Inc. Tel: 248-295-0310 - 61 - www.acromag.com... -

Page 63: Iic Bare Metal Software

The page size is set to 16. The IIC function to the PMIC power chip is called IicPsRepeatedStartExample. The PMIC is first found. The function then reads a page size of five. Acromag, Inc. Tel: 248-295-0310 - 62 - www.acromag.com... -

Page 64: Usb Bare Metal Software

The USB port on the breakout board should be connected to a USB port on a host PC. In Device Manager on the host PC the APZU+ USB port will be identified as a USB Mass Storage Device under the Universal Serial Bus Controllers (as seen below). Acromag, Inc. Tel: 248-295-0310 - 63 - www.acromag.com... - Page 65 USER’S MANUAL SERIES APZU+ ACROPACK If USB Mass Storage Device is double selected, it will show the following. Acromag, Inc. Tel: 248-295-0310 - 64 - www.acromag.com...

- Page 66 The host PC will ask to format the drive. Enter a Volume label and start the format operation. As a test a text file can be moved to the newly formatted drive. Select Format disk and enter Volume label name. Acromag, Inc. Tel: 248-295-0310 - 65 - www.acromag.com...

- Page 67 APZU. Disconnect USB port when not in use. DMA0 Breakout of the USB test is accomplished by writing 0x123 to the scratch3 register (address BAR0 + 0x5C) over the PCIe bus. Acromag, Inc. Tel: 248-295-0310 - 66 - www.acromag.com...

-

Page 68: Led Bare Metal Software

The LEDs are tied to GPIO pins 46 and 47. The code used to test the LEDs is given below. ConfigPtr = XGpioPs_LookupConfig(GPIO_DEVICE_ID); XGpioPs_CfgInitialize(&Gpio, ConfigPtr,ConfigPtr->BaseAddr); XGpioPs_SetDirectionPin(&Gpio, 47, 1); XGpioPs_SetOutputEnablePin(&Gpio, 47, 1); XGpioPs_WritePin(&Gpio, 47, 0x0); printf("LED 47 ON...\n"); XGpioPs_SetDirectionPin(&Gpio, 46, 1); XGpioPs_SetOutputEnablePin(&Gpio, 46, 1); XGpioPs_WritePin(&Gpio, 46, 0x0); printf("LED 46 ON...\n"); Acromag, Inc. Tel: 248-295-0310 - 67 - www.acromag.com... -

Page 69: Service And Repair

SMT repair and service tools are used. For these and other reasons, it is strongly recommended that a non-functioning board be returned to Acromag for repair. Acromag has automated diagnostic and test equipment that thoroughly checks the performance of suspect boards. -

Page 70: Specifications

165 mA Typical, 200 mA maximum -12 VDC +/- 5% Not Used Note 1: Typical current draw for all models with Acromag Example design 8.3 Environmental Considerations Summarized below are the operating temperature range, airflow and other environmental requirements and applicable standards for the AcroPack module. -

Page 71: Relative Humidity

FN2. Per MIL-HDBK-217, Ground Benign, Controlled, G Table 8.4.1 MTBF of APZU-303 Temperature MTBF (Hours) MTBF (Years) Failure Rate (FIT 25°C 1,459,102 685.4 40°C 923,762 105.5 1,082.5 FIT is Failures in 10 hours. Acromag, Inc. Tel: 248-295-0310 - 70 - www.acromag.com... -

Page 72: Field I/O

40 Mbyte/s Write Rate Note 1: PCIe x1 Gen 1 = 2.5GT/s (with 10-bit encoding we have a 20% loss in possible throughput due to encoding) giving 2.0 G bits/sec or 250M Bytes/sec. Acromag, Inc. Tel: 248-295-0310 - 71 - www.acromag.com... - Page 73 Simple write operations are just as fast as DMA read operations. Write data is presented to the AcroPack in one transaction. Measured 4-byte back to back write accesses taking place every 100ns. Acromag, Inc. Tel: 248-295-0310 - 72 - www.acromag.com...

- Page 74 Boot File for ZYNQ Physically Remove MicroSD ■ Yes card and erase using □ No Computer Acromag Representative Name: Title: Email: Office Phone: Office Fax: Russ Nieves Sales and solutions@acromag.com 248-295-0310 248-624-9234 Marketing Acromag, Inc. Tel: 248-295-0310 - 73 - www.acromag.com...

- Page 75 The revision history for this document is summarized in the table below. Release Date Version EGR/DOC Description of Revision (mm/dd/yyyy) 7/23/2020 Preliminary LMP/LMP Preliminary Document Publication 11/3/2020 LMP/LMP Release with product introduction Acromag, Inc. Tel: 248-295-0310 - 74 - www.acromag.com...

Need help?

Do you have a question about the APZU AcroPack Series and is the answer not in the manual?

Questions and answers