Table of Contents

Advertisement

Quick Links

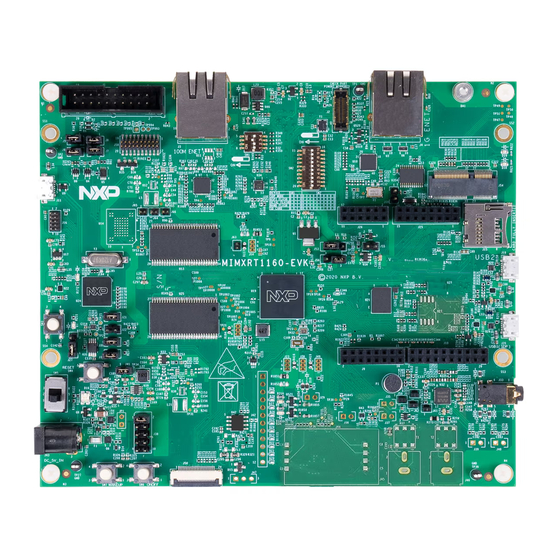

MIMXRT1170HDUG

Hardware Development Guide for the MIMXRT1160/1170 Processor

Rev. 2 - 09/2021

1 Introduction

This document's purpose is to help hardware engineers design and test

their MIMXRT1170 processor-based designs. It provides information about

board layout recommendations and design checklists to ensure first-pass

success and avoid board bring-up problems. This guide is released along with

the relevant device-specific hardware documentation such as data sheets,

reference manuals, and application notes available on

RT1160 shares the same design with RT1170, so engineers can

also use this document for RT1160.

2 Background

The i.MX RT1170 is a new processor family featuring NXP's advanced implementation of the high performance Arm

Core and power efficient Arm Cortex-M4 core. It provides high CPU performance and real-time response.

The i.MX RT1170 has 2 MB of on-chip RAM in total, including a 512 KB RAM which can be flexibly configured as Tightly-Coupled

Memory (TCM) or general purpose On-Chip RAM (OCRAM). The i.MX RT1170 integrates advanced power management module

with DC-DC and LDOs that reduce complexity of external power supply and simplify power sequencing.

It provides various memory interfaces, including SDRAM, Raw NAND FLASH, NOR FLASH, SD/eMMC, Quad SPI, Hyper

RAM/Flash. It also provides a wide range of other interfaces for connecting external peripherals, such as WLAN, BluetoothR, GPS,

displays, and camera sensors. Like other i.MX processors, i.MX RT1170 also has rich audio and video features, including MIPI

CSI/DSI, LCD display, graphics accelerator, camera interface, S/PDIF, and I

The i.MX RT1170 applications processor can be used in areas such as industrial HMI, IoT, high-end audio appliance, low-end

instrument cluster, Point-of-Sale(PoS), motor control, and home appliances.

3 Power supply

For power supply voltage specifications, refer to the Operating Ranges table in the device data sheets. See

for power supply decoupling recommendations.

The

Figure 1

in this section is applicable to RT1170 silicon and these tables do not include the on-chip LDO output

specification, which can be found in the device data sheet.

nxp.com.

NOTE

NOTE

Contents

1

Introduction......................................1

2

Background..................................... 1

3

Power supply...................................1

4

Clocks..............................................7

5

Debugging and programming..........8

6

Boot, reset, and miscellaneous..... 10

7

Layout recommendations.............. 18

8

Related resources......................... 22

9

Revision history............................. 22

2

S audio interface.

User Guide

®

®

Cortex

-M7

Table 1

and

Table 2

Advertisement

Table of Contents

Summary of Contents for NXP Semiconductors MIMXRT1170HDUG

-

Page 1: Table Of Contents

MIMXRT1170HDUG Hardware Development Guide for the MIMXRT1160/1170 Processor Rev. 2 — 09/2021 User Guide Contents 1 Introduction Introduction........1 Background........1 This document’s purpose is to help hardware engineers design and test Power supply........1 their MIMXRT1170 processor-based designs. It provides information about Clocks..........7... - Page 2 NXP Semiconductors Power supply Table 1. Processor supply capacitors when on-chip DCDC regulators are used 0.1 μF 0.22 μF 1 μF 2.2 μF 4.7 μF 22 μF Power rail Notes DCDC_IN Place 0402 under balls M5, N5, place 0603 as close as possible to the processor.

- Page 3 NXP Semiconductors Power supply Table 1. Processor supply capacitors when on-chip DCDC regulators are used (continued) 0.1 μF 0.22 μF 1 μF 2.2 μF 4.7 μF 22 μF Power rail Notes NVCC_EMC2_X Place 2.2 μF under balls H6, J6 NVCC_GPIO Place 2.2 μF under ball M12...

- Page 4 NXP Semiconductors Power supply Table 2. Processor supply capacitors when external PMIC or regulators utilized (on-chip DCDC regulators not used) (continued) 0.1 μF 0.22 μF 1 μF 2.2 μF 4.7 μF 22 μF Power rail Notes NVCC_SD1 Place under ball D14...

- Page 5 NXP Semiconductors Power supply Table 3. Power supply and SNVS domain signals (continued) Item Recommendation Description • PMIC_STBY_REQ—configurable output • Be careful to use SNVS signals to drive external load as the SNVS GPIO drive is quite low, refer to the i.MX •...

- Page 6 NXP Semiconductors Power supply Figure 1. Power control diagram 3.1 On-chip DC/DC module The internal DC/DC of RT1170 has two outputs, one output (VDD_DIG) typical 0.7 V~1.15 V, another output (VDD_ANA) typical 1.8 V and its switching frequency is about 1.5 MHz.

-

Page 7: Clocks

NXP Semiconductors Clocks Figure 2. DC/DC function diagram NOTE The processor's on-chip DC-DC regulator is suitable for consumer and industrial applications up to 105 degrees C. For automotive applications, contact your NXP representative. 4 Clocks Table 4 for the clock configuration. The 32.768-kHz and 24-MHz oscillators are used for the EVK design. For RT1170, it is necessary to use 32.768-kHz and 24-MHz crystals for the hardware design. -

Page 8: Debugging And Programming

NXP Semiconductors Debugging and programming Table 4. Clocks’ configurations (continued) Signal name Recommended connections Description of this forcing clock must not exceed the VDD_SNVS_DIG level and the frequency shall be <100 kHz under the typical conditions. An on-chip loose-tolerance ring... - Page 9 NXP Semiconductors Debugging and programming NOTE By default, the RT1170 silicon can use both SWD and JTAG modes using the Arm stitching sequence. For the RT1170EVK board, it defaults to use the SWD debug without any board modification. If you want to use the JTAG debug, solder out R187, R208, R195, and R78, because some JTAG signals are multiplexed with other functions.

-

Page 10: Boot, Reset, And Miscellaneous

NXP Semiconductors Boot, reset, and miscellaneous Table 8. Serial downloader I/Os table Signals Recommendation Description The serial downloader provides a means to download a The ROM polls for the UART1 and USB1 1.UART1 program image to the chip over the USB and UART serial activity circularly until the ROM gets 0x5A, 2. - Page 11 NXP Semiconductors Boot, reset, and miscellaneous Figure 3. Boot mode setting Table 10. Reset and miscellaneous recommendations Item Recommendation Description 1. POR_B The POR_B input (if used) must be See the “System Boot” chapter in your immediately asserted at power-up and...

- Page 12 NXP Semiconductors Boot, reset, and miscellaneous Table 10. Reset and miscellaneous recommendations (continued) Item Recommendation Description DCDC_PSWITCH PIN is below 0.5 V before power up. For portable applications, the ON/OFF A brief connection to GND in 2. ON/OFF input may be connected to the the OFF mode causes the internal ON/OFF SPST push-button.

- Page 13 NXP Semiconductors Boot, reset, and miscellaneous Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note LPSPI4_SDI GPIO_DISP_B2_13 ALT9 SEMC NAND SEMC_DATA00 GPIO_EMC_B1_00 ALT0 Parallel NAND flash connected to the SEMC is a primary SEMC_DATA01 GPIO_EMC_B1_01 ALT0 boot option.

- Page 14 NXP Semiconductors Boot, reset, and miscellaneous Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note USDHC2_CD_B GPIO_AD_26 ALT11 USDHC2_WP GPIO_AD_27 ALT11 USDHC2_VSELECT GPIO_AD_28 ALT11 USDHC2_DATA3 GPIO_SD_B2_00 ALT0 USDHC2_DATA2 GPIO_SD_B2_01 ALT0 USDHC2_DATA1 GPIO_SD_B2_02 ALT0 USDHC2_DATA0 GPIO_SD_B2_03...

- Page 15 NXP Semiconductors Boot, reset, and miscellaneous Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note FLEXSPI1_A_DATA GPIO_SD_B2_10 ALT1 FLEXSPI1_A_DATA GPIO_SD_B2_11 ALT1 FLEXSPI1_A_DQS GPIO_EMC_B2_18 ALT6 Second option FlexSPI2 (QSPI / FLEXSPI2_B_DATA GPIO_EMC_B1_41 ALT4 Octal serial NOR flash memory...

- Page 16 NXP Semiconductors Boot, reset, and miscellaneous Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note FLEXSPI2_A_DATA GPIO_EMC_B2_18 ALT4 FLEXSPI2_A_DATA GPIO_EMC_B2_19 ALT4 FLEXSPI2_A_DATA GPIO_EMC_B2_20 ALT4 GPIO_MUX2_IO08 GPIO_EMC_B1_40 ALT5 Second option GPIO_MUX4_IO03 GPIO_SD_B1_00 ALT5 FlexSPI Reset SEMC_ADDR09...

- Page 17 NXP Semiconductors Boot, reset, and miscellaneous Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note FLEXSPI_A_DATA3 GPIO_SD_B1_11 ALT1 FLEXSPI_A_SS0_B GPIO_AD_B1_15 ALT0 QSPI memory attached to FlexSPIN OR- FlexSPI is a primary boot option. QSPI-2nd Option...

-

Page 18: Layout Recommendations

NXP Semiconductors Layout recommendations Table 11. ROM Bootloader Peripheral PinMux (continued) Peripheral Instance Port (IO function) Mode Note FLEXSPI_A_DATA3 GPIO_SD_B1_11 ALT1 FlexSPI RESET GPIO1_IO29 GPIO_AD_B1_13 ALT5 NOTE ROM does not support boot from FLEXSPI_B port directly. ROM always seeks a valid Flash Configuration Block from the FLEXSPI_A port and then re-configures the FLEXSPI controller using the valid parameters in the block read-out. - Page 19 NXP Semiconductors Layout recommendations Figure 5. IMXRT1170EVK stackup implementation 7.2 Placement of bulk and decoupling capacitors Place the small decoupling capacitors and the larger bulk capacitors on the bottom side of the CPU. The 0402 decoupling capacitors and the 0603 bulk capacitors must be placed as close as possible to the power balls. Placing the decoupling capacitors close to the power balls is critical to minimize inductance and ensure the high-speed transient current demand of the processor.

- Page 20 NXP Semiconductors Layout recommendations For Octal Flash where a DQS signal is provided by the memory, need to use the option of FlexSPIn_MCR0[RXCLKSRC] = 0x3 which can achieve 166 MHz DDR R/W, in such case FlexSPI_DQS pin should be connected to the flash directly.

- Page 21 NXP Semiconductors Layout recommendations • Clock and other high-speed traces must be as short as possible, it’s necessary to have a GND plane under these traces. • RXC and TXC are high-speed (125MHz) signals; Keep a 20mil space between clock and data signals.

-

Page 22: Related Resources

NXP Semiconductors Related resources Table 12. Recommended connections for unused analog interfaces (continued) Recommendations if Unused Module Ball Name not required). Leakage is typically 45 μA but could be a few hundred μA at high temperature. VDD_MIPI_1P8 For lowest leakage, 10 kΩ resistor to ground. For possible easier layout but higher leakage, tie directly to power (inductors and capacitors are not required). - Page 23 NXP Semiconductors Revision history Table 13. Revision history Revision number Date Substantive changes 09/2021 • Updated the document title from "Hardware Development Guide for the MIMXRT1170 Processors" to "Hardware Development Guide for the MIMXRT1160/1170 Processors" • Added a note to provide support on RT1160 in the...

- Page 24 Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Need help?

Do you have a question about the MIMXRT1170HDUG and is the answer not in the manual?

Questions and answers