Table of Contents

Advertisement

Quick Links

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution

of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business

relationships with customers from,Europe,America and south Asia,supplying obsolete and hard-to-find components

to meet their specific needs.

With the principle of "Quality Parts,Customers Priority,Honest Operation,and Considerate Service",our business

mainly focus on the distribution of electronic components. Line cards we deal with include

Microchip,ALPS,ROHM,Xilinx,Pulse,ON,Everlight and Freescale. Main products comprise

IC,Modules,Potentiometer,IC Socket,Relay,Connector.Our parts cover such applications as commercial,industrial,

and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service

and solution. Let us make a better world for our industry!

Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Advertisement

Table of Contents

Summary of Contents for Cypress FM33256B

- Page 1 Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from,Europe,America and south Asia,supplying obsolete and hard-to-find components to meet their specific needs.

- Page 2 256-Kbit (32 K × 8) Serial (SPI) F-RAM Features Functional Overview 256-Kbit ferroelectric random access memory (F-RAM) The FM33256B device integrates F-RAM memory with the most ■ commonly needed functions for processor-based systems. Logically organized as 32 K × 8 ❐...

- Page 3 FM33256B Logic Block Diagram Document Number: 001-86213 Rev. *C Page 2 of 39...

-

Page 4: Table Of Contents

WRDI - Reset Write Enable Latch ......25 PSoC® Solutions ............39 Status Register and Write Protection ......26 Cypress Developer Community ......... 39 RDSR - Read Status Register ........26 Technical Support ............. 39 Document Number: 001-86213 Rev. *C... -

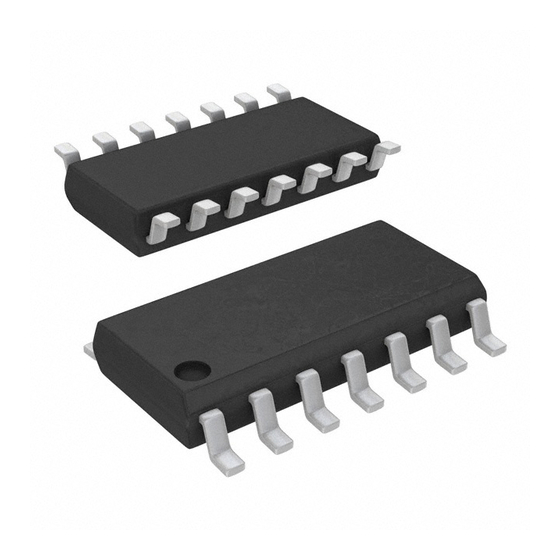

Page 5: Pinout

FM33256B Pinout Figure 1. 14-pin SOIC pinout Pin Definitions Pin Name I/O Type Description Input Chip Select. This active LOW input activates the device. When HIGH, the device enters low-power standby mode, ignores SCK and SI inputs, and the SO output is tristated. When LOW, the device internally activates the SCK signal. -

Page 6: Overview

VTP Setting VTP1 VTP0 Memory Architecture 2.6 V The FM33256B is available with 256-Kbit of memory. The device 2.75 V uses two-byte addressing for the memory portion of the chip. 2.9 V This makes the device software compatible with its standalone 3.0 V... -

Page 7: Manual Reset

25 ms resolution and 0 ms to 775 ms range. Manual Reset Figure 4. Window Timer The RST is a bi-directional signal allowing the FM33256B to filter and de-bounce a manual reset switch. The RST input detects an external low condition and responds by driving the RST signal... -

Page 8: Event Counter

The typical solution uses a pull-up resistor on the CNT pin and will continuously draw battery current. The FM33256B chip allows the user to invoke a polled mode, which occasionally samples the pin in order to FM33256B minimize battery drain. -

Page 9: Alarm

FM33256B Alarm flag and ACS pin will remain in this state until the AF bit is cleared by writing it to a '0'. Clearing the AEN bit will prevent further The alarm function compares user-programmed values to the matches from setting AF but will not automatically clear the AF... -

Page 10: Backup Power

FM33256B is set, then the core will be updated prior to loading the user 8th clock of the write to register 00h (W = ‘0’), the RTC starts registers. The user registers are frozen and will not be updated counting with a timebase that has been reset to zero again until the R bit is cleared to a '0'. -

Page 11: Trickle Charger

When the CAL bit in register 00h is set to a '1', the clock enters loading capacitors are required nor suggested. calibration mode. The FM33256B employs a digital method for If a 32.768 kHz crystal is not used, an external oscillator may be calibrating the crystal oscillator frequency. - Page 12 FM33256B Table 4. Digital Calibration Adjustments Positive Calibration for slow clocks: Calibration will achieve ± 2.17 PPM after calibration Measured Frequency Range Error Range (PPM) Program Calibration Register to: 512.0000 511.9989 2.17 000000 511.9989 511.9967 2.18 6.51 100001 511.9967 511.9944 6.52...

- Page 13 FM33256B Table 4. Digital Calibration Adjustments (continued) Negative Calibration for fast clocks: Calibration will achieve ± 2.17 PPM after calibration Measured Frequency Range Error Range (PPM) Program Calibration Register to: 512.0000 512.0011 2.17 000000 512.0011 512.0033 2.18 6.51 000001 512.0033 512.0056...

-

Page 14: Register Map

FM33256B Register Map The RTC and processor companion functions are accessed via 30 special function registers, which are mapped to unique opcodes. The interface protocol is described on page 23. The registers contain timekeeping data, alarm settings, control bits, and information flags. - Page 15 FM33256B Table 6. Default Register Values Address Hex Value Address Hex Value Address Hex Value 0x81 0x00 0x00 0x81 0x00 0x00 0x80 0x00 0x00 0x80 0x00 0x00 0x80 0x00 0x00 0x40 0x01 0x80 0x00 0x00 0x00 0x00 0x00 0x00 0x00...

- Page 16 FM33256B Table 7. Register Description Address Description Alarm – Month 10 Month Month.3 Month.2 Month.1 Month.0 Contains the alarm value for the month and the mask bit to select or deselect the Month value. Match. Setting this bit to ‘0’ causes the Month value to be used in the alarm match logic. Setting this bit to ‘1’...

- Page 17 FM33256B Table 7. Register Description (continued) Address Description F(1:0) Square Wave Frequency Select: These bits select the frequency on the ACS pin when the CAL and AL/SW bits are both ‘0’. Nonvolatile. Setting F(1:0) 1 Hz 00 (default) 512 Hz...

- Page 18 FM33256B Table 7. Register Description (continued) Address Description Serial Number Byte 2 SN.23 SN.22 SN.21 SN.20 SN.19 SN.18 SN.17 SN.16 Serial Number Byte 1 SN.15 SN.14 SN.13 SN.12 SN.11 SN.10 SN.9 SN.8 Serial Number Byte 0 SN.7 SN.6 SN.5 SN.4 SN.3...

- Page 19 FM33256B Table 7. Register Description (continued) Address Description Watchdog Control WDET4 WDET3 WDET2 WDET1 WDET0 Watchdog Enable: When WDE = ‘1’, a watchdog timer fault will cause the RST signal to go active. When WDE = ‘0’ the timer runs but has no effect on the RST pin. Nonvolatile, read/write.

- Page 20 FM33256B Table 7. Register Description (continued) Address Description Watchdog Control WDST4 WDST3 WDST2 WDST1 WDST0 WDST(4:0) Watchdog StartTime. Sets the starting time for the watchdog window timer with 25 ms (max.) resolution. The window timer allow independent leading and trailing edges (start and end of window) to be set. New watchdog timer settings are loaded when the timer is restarted by writing the 1010b pattern to WR(3:0).

- Page 21 FM33256B Table 7. Register Description (continued) Address Description Power-On Reset: When the RST signal is activated by V < V , the POR bit will be set to ‘1’. A manual reset will not set this flag. Note that one or both of the watchdog flags and the POR flag could be set if both reset sources have occurred since the flags were cleared by the user.

- Page 22 FM33256B Table 7. Register Description (continued) Address Description Timekeeping – Minutes 10 min.2 10 min.1 10 min.0 Min.3 Min.2 Min.1 Min.0 Contains the BCD value of minutes. Lower nibble contains the lower digit and operates from 0 to 9; upper nibble contains the upper minutes digit and operates from 0 to 5.

- Page 23 FM33256B Table 7. Register Description (continued) Address Description Read Time. Setting the R bit to '1' copies a static image of the timekeeping core and places it into the user registers. The user can then read them without concerns over changing values causing system errors. The R bit going from ‘0’...

-

Page 24: Serial Peripheral Interface - Spi Bus

After CS is activated, the first byte transferred from the bus master is the opcode. Following the opcode, any addresses and The FM33256B has two separate pins for SI and SO, which can data are then transferred. The CS must go inactive after an... -

Page 25: Spi Modes

FM33256B Status Register The FM33256B has an 8-bit Status Register. The bits in the Status Register are used to configure the device. These bits are described in Table 10 on page Figure 13. System Configuration with SPI Port MOSI MISO... -

Page 26: Power Up To First Access

Command Structure Figure 17. WREN Bus Configuration There are eight commands, called opcodes, that can be issued by the bus master to the FM33256B. They are listed in Table These opcodes control the functions performed by the memory and processor companion.

Need help?

Do you have a question about the FM33256B and is the answer not in the manual?

Questions and answers