Table of Contents

Summary of Contents for ADLINK Technology COM Express Express-CFR

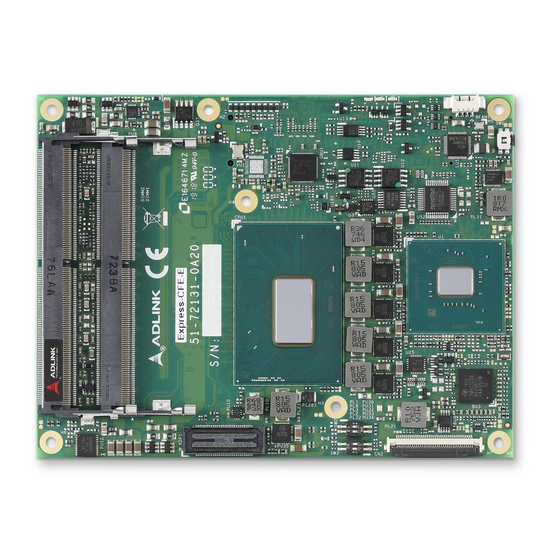

- Page 1 Express-CFR User’s Manual COM Express Basic Size Type 6 Module with Hexa-core Mobile 9th Gen Intel® Core™ and Intel® Xeon® Processors Manual Rev.: Revision Date: September 30, 2019 Part Number: 50-1J099-1000 Leading EDGE COMPUTING...

- Page 2 Preface Copyright Copyright © 2019 ADLINK Technology, Inc. This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

-

Page 3: Table Of Contents

Express-CFR Table of Contents Preface ..........................ii List of Figures ........................v List of Tables........................vi Introduction........................1 Specifications ......................3 2.1. Core System ........................3 2.2. Expansion Busses......................4 2.3. Video ..........................4 2.4. Audio ..........................4 2.5. LAN ..........................4 2.6. Multi I/O and Storage ......................5 2.7. -

Page 4: Preface

6.1. System Memory Map ....................47 6.2. I/O Map ......................... 47 6.3. Interrupt Request (IRQ) Lines ..................48 6.4. PCI Configuration Space Map..................50 6.5. PCI Interrupt Routing Map ....................51 6.6. SMBus Address Table ....................51 BIOS Setup.......................53 7.1. Menu Structure......................53 7.2. Main ..........................54 7.3. -

Page 5: List Of Figures

Express-CFR List of Figures Figure 1: Express-CFR Functional Block Diagram ..................7 Figure 2: Express-CFR Mechanical Drawing ...................8 Figure 3: Express-CFR Connector, Switch and LED Locations............33 Figure 4: Express-CFR and the DB40 Debug Module ................34 Figure 5: Express-CFR Switch Locations....................39 Figure 6: COM Express Mounting Methods .................. - Page 6 List of Tables Table 1: Express-CFR AB/CD Pin Definitions..................9 Table 2: 40-pin Debug Connector Pin Definition ................... 35 Table 3: Express-CFR LED Descriptions ....................36 Table 4: Fan Connector Pin Definition ....................37 Table 5: PCI Express Configuration Switch Settings ................39 Table 6: BIOS Select and Mode Configuration Switch Settings............

-

Page 7: Introduction

Express-CFR 1. Introduction The Express-CFR is the first COM Express® COM.0 R3.0 Basic Size Type 6 module supporting the Hexa-core (6 cores) 64-bit 9 Generation Intel® Core™ i7 and Xeon® processors and quad-core (4 cores) Intel® Core™ i5/i3 processors (codename “Coffeelake-H”) with Mobile Intel® QM370, HM370, CM246 Chipset. The Hexa-core processors support up to 12 threads (Intel®... - Page 8 This page intentionally left blank. Introduction...

-

Page 9: Specifications

Express-CFR 2. Specifications 2.1. Core System Hexa-core 9th Generation Intel® Core™ and and Xeon® processor (formerly “Coffee Lake Refresh) • Xeon® E-2276ME, 2.8(4.5)GHz, 12MB, 45W (35W cTDP, 6C/GT2) • Xeon® E-2276ML, 2.0(4.2)GHz, 12MB, 25W (6C/GT2) • Xeon® E-2254ME, 2.6(3.8)GHz, 8MB, 45W (35W cTDP, 4C/GT2) •... -

Page 10: Expansion Busses

2.2. Expansion Busses PCI Express x16 Gen3 (can be configured to 1x16, 2 x8 or 1 x8 plus 2 x4) PCI Express 6 PCI Express x1 Gen3 (AB): Lanes 0/1/2/3/4/5 2 PCI Express x1 Gen3 (CD): Lane 6/7 Notes: PCIe lanes 0/1/2/3 can also be configured to x2, x4 PCIe lanes 4/5/6/7 can also be configured to x2, x4. -

Page 11: Multi I/O And Storage

Express-CFR 2.6. Multi I/O and Storage Intel® QM370/HM370/CM246 Chipset Integrated 4x USB 3.0 (USB 0,1,2,3), 4x USB 2.0 (USB 4,5,6,7) All USB supported by xHCI controllers 4x SATA 6Gb/s (SATA 0,1,2,3) SATA 4 GPO and 4 GPI (GPI with interrupt) GPIO/SD SD/GPIO muxed design, switched by BIOS setting SD functions as storage device only... -

Page 12: Debug

2.10. Debug 40-pin flat cable connector to be used with DB-40 debug module Supports: BIOS POST code LED, BMC access, SPI BIOS flashing, power testpoints, debug LEDs 60-pin XDP header for ICE debug of CPU/chipset 2.11. Power Specifications AT and ATX mode (AT mode startup controlled by SEMA Board Controller) Power Modes ATX: 12V±5% / 5Vsb ±5% or AT = 12V±5% Standard Voltage Input... -

Page 13: Functional Diagram

Express-CFR 2.17. Functional Diagram SODIMM 3 2133/2400 MHz 4-32 GB DDR4 SODIMM 1 2133/2400 MHz 4-32 GB DDR4 Mobile SODIMM 2 Gen Intel® Core™ DDI 2 2133/2400 MHz Intel® Xeon® E 4-32 GB DDR4 DP/HDMI/DVI Pentium®/Celeron® G DDI 3 Processor DP/HDMI/DVI eDP x4 PCIe x16 (Gen3) -

Page 14: Mechanical Drawing

2.18. Mechanical Drawing All are dimensions shown in millimeters. Tolerances should be ± 0.25mm (±0.010”), unless otherwise noted. The tolerances of the module connector locating peg holes (dimensions [16.50, 6.00] and [16.50, 18.00]) should be ±0.10mm (±0.004”). Figure 2: Express-CFR Mechanical Drawing Specifications... -

Page 15: Pinouts And Signal Descriptions

Express-CFR 3. Pinouts and Signal Descriptions 3.1. AB/CD Pin Definitions The Express-CFR is a Type 6 module supporting USB 3.0 upgrade signals and DDI channels on the CD connector. All pins in the COM Express specification are described, including those not supported on the Express-CFR. Those not supported on the Express-CFR module are crossed out. - Page 16 Row A Row B Row C Row D Name Name Name Name USB6- USB7- DDI3_CTRLCLK_AUX+ DDI1_PAIR3+ USB6+ USB7+ DDI1_PAIR3- DDI3_CTRLDATA_AUX- USB_6_7_OC# USB_4_5_OC# DDI3_DDC_AUX_SEL RSVD USB4- USB5- DDI3_PAIR0+ DDI2_PAIR0+ USB4+ USB5+ DDI3_PAIR0- DDI2_PAIR0- GND (fixed) GND (fixed) GND (fixed) GND (fixed) USB2- USB3- DDI3_PAIR1+...

- Page 17 Express-CFR Row A Row B Row C Row D Name Name Name Name GND (FIXED) GND (FIXED) GND (FIXED) GND (FIXED) LVDS_A_CK+ LVDS_B_CK+ PEG_RX9+ PEG_TX9+ LVDS_A_CK- LVDS_B_CK- PEG_RX9- PEG_TX9- LVDS_I2C_CK LVDS_BKLT_CTRL RSVD RSVD LVDS_I2C_DAT VCC_5V_SBY GPI3 VCC_5V_SBY PEG_RX10+ PEG_TX10+ RSVD VCC_5V_SBY PEG_RX10- PEG_TX10-...

-

Page 18: Signal Description Terminology

3.2. Signal Description Terminology The following terms are used in the COM Express AB/CD Signal Descriptions below. Input to the Module Output from the Module Bi-directional input/output signal Open drain output I 3.3V Input 3.3V tolerant I 5V Input 5V tolerant O 3.3V Output 3.3V signal level O 5V... -

Page 19: Ab Signal Descriptions

Express-CFR 3.3. AB Signal Descriptions 3.3.1. Audio Signals Signal Pin # Description PU/PD Comment HDA_RST# Reset output to CODEC, active low. O 3.3VSB HDA_SYNC Sample-synchronization signal to the O 3.3V CODEC(s). HDA_BITCLK Serial data clock generated by the I/O 3.3V external CODEC(s). - Page 20 3.3.3. LVDS Signal Pin # Description PU/PD Comment LVDS_A0+ LVDS Channel A differential pairs O LVDS LVDS is default LVDS_A0- support LVDS_A1+ LVDS_A1- LVDS_A2+ LVDS_A2- LVDS_A3+ LVDS_A3- LVDS_A_CK+ LVDS Channel A differential clock O LVDS LVDS_A_CK- LVDS_B0+ LVDS Channel B differential pairs O LVDS LVDS_B0- LVDS_B1+...

- Page 21 Express-CFR 3.3.4. Note: eDP is supported by build option, in place of LVDS. Signal Pin # Description PU/PD Comment eDP_TX3+ eDP differential pairs O PCIE AC coupled off eDP_TX3- module eDP_TX2+ eDP_TX2- eDP_TX1+ eDP_TX1- eDP_TX0+ eDP_TX0- eDP_VDD_EN eDP power enable O 3.3V eDP_BKLT_EN eDP backlight enable...

- Page 22 3.3.6. SATA Signal Pin # Description PU/PD Comment SATA0_TX+ Serial ATA channel 0, Transmit Output differential O SATA AC coupled on SATA0_TX- pair. Module SATA0_RX+ Serial ATA channel 0, Receive Input differential I SATA AC coupled on SATA0_RX- pair. Module SATA1_TX+ Serial ATA channel 1, Transmit Output differential O SATA...

- Page 23 Express-CFR 3.3.7. PCI Express Signal Pin # Description PU/PD Comment PCIE_TX0+ PCI Express channel 0, Transmit AC coupled on Module PCIE_TX0- Output differential pair. PCIE PCIE_RX0+ PCI Express channel 0, Receive I PCIE AC coupled off Module PCIE_RX0- Input differential pair. PCIE_TX1+ PCI Express channel 1, Transmit AC coupled on Module...

- Page 24 3.3.8. LPC Bus Signal Pin # Description PU/PD Comment LPC_AD[0:3] B4-B7 LPC multiplexed address, command and I/O 3.3V data bus LPC_FRAME# B3 LPC frame indicates the start of an LPC O 3.3V cycle LPC_DRQ0# LPC serial DMA request I 3.3V NC pins LPC_DRQ1# LPC_SERIRQ...

- Page 25 Express-CFR 3.3.9. Signal Pin # Description PU/PD Comment USB0+ USB differential data pairs for Port 0 USB 1.1/ 2.0 compliant USB0- 3.3VSB USB1+ USB differential data pairs for Port 1 USB 1.1/ 2.0 compliant USB1- 3.3VSB USB2+ USB differential data pairs for Port 1 USB 1.1/ 2.0 compliant USB2- 3.3VSB...

- Page 26 3.3.10. USB Root Segmentation USB on COMe Module HSIO Function on PCH Comment USB 0 USB 3.1 #1 All USB are from XHCI controllers. USB 1 USB 3.1 #4 USB 2 USB 3.1 #3 USB 3 USB 3.1 #2 3.3.11. SPI (BIOS only) Signal Pin #...

- Page 27 Express-CFR 3.3.12. Miscellaneous Signal Pin # Description PU/PD Comment SPKR Output for audio enunciator, the “speaker” in O 3.3V PC-AT systems Output indicating that a watchdog time-out O 3.3V event has occurred. THRM# Input from off-module temp sensor indicating an I 3.3VSB over-temp situation.

- Page 28 3.3.15. General Purpose I/O (GPIO) Signal Pin # Description PU/PD Comment After hardware GPO[0] General purpose output pins. O 3.3V PD 10K 3.3V RESET output low GPO[1] General purpose output pins. O 3.3V PD 10K 3.3V After hardware RESET output low GPO[2] General purpose output pins.

- Page 29 Express-CFR 3.3.17. Power and System Management Signal Pin # Description PU/PD Comment PWRBTN# Power button to bring system out of S5 (soft off), active on PU 10K falling edge. 3.3VSB 3.3VSB SYS_RESET# B49 Reset button input. Active low request for module to reset and PU 10K reboot.

- Page 30 3.3.18. Power and Ground Signal Pin # Description Comment VCC_12V A104-A109 Primary power input: +12V nominal (wide range 5 ~ 8.5-20 V 20V). B104-B109 All available VCC_12V pins on the connector(s) shall be used. VCC_5V_S B84-B87 Standby power input: +5.0V nominal. See section 7 5Vsb ±5% “Electrical Specifications“...

-

Page 31: Cd Signal Descriptions

Express-CFR 3.4. CD Signal Descriptions 3.4.1. USB 3.0 Extension Signal Pin # Description PU/PD Comment USB_SSRX0- Additional Receive signal differential pairs for the I PCIE AC coupled off USB_SSRX0+ SuperSpeed USB data path on USB0 module USB_SSTX0- Additional Transmit signal differential pairs for O PCIE AC coupled on USB_SSTX0+... - Page 32 3.4.3. DDI Channels DDI 1 Signal Description PU/PD Comment DDI1_PAIR0+ Digital Display Interface1 O PCIE Pair 4 to Pair 6 differential pairs DDI1_PAIR0- Not supported DDI1_PAIR1+ DDI1_PAIR1- DDI1_PAIR2+ DDI1_PAIR2- DDI1_PAIR3+ DDI1_PAIR3- DDI1_PAIR4+ DDI1_PAIR4- DDI1_PAIR5+ DDI1_PAIR5- DDI1_PAIR6+ DDI1_PAIR6- DDI1_HPD Digital Display Interface Hot-Plug I 3.3V Detect 100K...

- Page 33 Express-CFR DDI 2 Signal Description PU/PD Comment DDI2_PAIR0+ Digital Display Interface2 O PCIE DDI2_PAIR0- differential pairs DDI2_PAIR1+ DDI2_PAIR1- DDI2_PAIR2+ DDI2_PAIR2- DDI2_PAIR3+ DDI2_PAIR3- DDI2_HPD I 3.3V 100K DDI2_CTRLCLK_AUX+ If DDI2_DDC_AUX_SEL is floating I/O PCIE AC couple on Module 100K DP2_AUX+ If DDI2_DDC_AUX_SEL pulled I/O OD HDMI2_CTRLCLK high...

- Page 34 DDI 3 Signal Description PU/PD Comment DDI3_PAIR0+ Digital Display Interface3 differential O PCIE DDI3_PAIR0- pairs DDI3_PAIR1+ DDI3_PAIR1- DDI3_PAIR2+ DDI3_PAIR2- DDI3_PAIR3+ DDI3_PAIR3- DDI3_HPD I 3.3V PD 100K DDI3_CTRLCLK_AUX+ If DDI3_DDC_AUX_SEL is floating I/O PCIE PD 100K AC couple on Module DP2_AUX+ If DDI3_DDC_AUX_SEL pulled high I/O OD HDMI2_CTRLCLK...

- Page 35 Express-CFR 3.4.4. DDI to DP/HDMI Mapping Pin Name HDMI / DVI DDI1_PAIR0+ DP1_LANE0+ TMDS1_DATA2+ DDI1_PAIR0- DP1_LANE0- TMDS1_DATA2- DDI1_PAIR1+ DP1_LANE1+ TMDS1_DATA1+ DDI1_PAIR1- DP1_LANE1- TMDS1_DATA1- DDI1_PAIR2+ DP1_LANE2+ TMDS1_DATA0+ DDI1_PAIR2- DP1_LANE2- TMDS1_DATA0- DDI1_PAIR3+ DP1_LANE3+ TMDS1_CLK+ DDI1_PAIR3- DP1_LANE3- TMDS1_CLK- DDI1_PAIR4+ DDI1_PAIR4- DDI1_PAIR5+ DDI1_PAIR5- DDI1_PAIR6+ DDI1_PAIR6- DDI1_HPD DP1_HPD...

- Page 36 3.4.5. PCI Express Graphics x16 (PEG) Signal Description PU/PD Comment PEG_RX0+ PCI Express Graphics transmit differential pairs. I PCIE AC couple off PEG_RX0- module PEG_RX1+ PEG_RX1- PEG_RX2+ PEG_RX2- PEG_RX3+ PEG_RX3- PEG_RX4+ PEG_RX4- PEG_RX5+ PEG_RX5- PEG_RX6+ PEG_RX6- PEG_RX7+ PEG_RX7- PEG_RX8+ PEG_RX8- PEG_RX9+ PEG_RX9- PEG_RX10+...

- Page 37 Express-CFR 3.4.6. Module Type Definition Signal Pin # Description Comment TYPE0# The TYPE pins indicate to the Carrier Board the Pin-out Type that is Type 6 TYPE1# implemented on the module. The pins are tied on the module to either TYPE2# ground (GND) or are no-connects (NC).

- Page 38 This page intentionally left blank. Pinouts and Signal Descriptions...

-

Page 39: Connector Pinouts On Module

Express-CFR 4. Connector Pinouts on Module This chapter describes connectors and pinouts, LEDs and switches that are used on the module but are not included in the PICMG standard specification 4.1. Connector, Switch and LED Locations 40-pin Multi- Purpose BIOS Defaults Reset Switch... -

Page 40: Figure 4: Express-Cfr And The Db40 Debug Module

Express-CFR and the DB40 Debug Module For illustration purposes only Figure 4: Express-CFR and the DB40 Debug Module Connector Pinouts on Module... -

Page 41: 40-Pin Debug Connector

Express-CFR 4.2. 40-pin Debug Connector FPC Connector Type: FCI 59GF Flex 10042867 Pin Orientation 40-pin Debug Connector Pin Definition on the COM Express Module Interface Signal Remark Interface Signal Remark SPI Program VCC_SPI_IN SPI Power Input from flash tool TXD6 interface to module. -

Page 42: Status Leds

4.3. Status LEDs To facilitate easier maintenance, status LED’s are mounted on the board. LED1 LED2 LED3 LED Descriptions Name Color Connection Function LED1 Blue BMC output Power Sequence Status Code (BMC) Power Changes, RESET (see 5.1.4 Exception Codes below) LED2 Green Power Source 3Vcc... -

Page 43: Fan Connector

Express-CFR 4.4. Fan Connector Connector Type: JVE 24W1125A-04M00 Pin Orientation 1 2 3 4 Pin Assignment Name Description FAN_PWMOUT FAN_TACHIN Ground Table 4: Fan Connector Pin Definition Connector Pinouts on Module... -

Page 44: Bios Setup Defaults Reset Button

4.5. BIOS Setup Defaults Reset Button To perform a hardware reset of BIOS default settings, perform the following steps: 1. Shut down the system. 2. Press the BIOS Setup Defaults RESET Button continuously and boot up the system. You can release the button when the BIOS prompt screen appears 3. -

Page 45: Switch Settings

Express-CFR 4.6. Switch Settings Switch Locations BIOS Select and Mode Configuration Switch PCI Express Configuration Switch Figure 5: Express-CFR Switch Locations 4.6.1. PCI Express Configuration Switch. PCI Express Configuration Switch (also referred to as the PEG config. switch) allows you to configure the PCI Express x16 lanes from the CPU as 1 PCIe x16, 2 PCIe x8, or 1 PCIe x8 + 2 PCIe x4. -

Page 46: Table 6: Bios Select And Mode Configuration Switch Settings

4.6.2. BIOS Select and Mode Configuration Switch The module has two BIOS chips and BIOS operation can be configured to "PICMG" and dual-BIOS "Failsafe" modes using BIOS Select and Mode Configuration Switch, Pin 2. Setting the module to PICMG mode will configure the BIOS chips on the module as SPI0 and SPI1. In PICMG mode, a BIOS chip cannot be placed in the SPI0 slot on the carrier. -

Page 47: Pcie X16-To-Two-X8 Adapter Card

Express-CFR 4.7. PCIe x16-to-two-x8 Adapter Card The Express-CFR can be used with the PCIe x16-to-two-x8 Adapter Card on the Express-BASE6 Reference Carrier to support bifurbication of the CPU's PEG interface (PCIe x16). The card reroutes the PCIe x16 to two x8 and allows testing of two independent PCIe add-on cards with x8/x4/x2/x1 width. - Page 48 This page intentionally left blank. Connector Pinouts on Module...

-

Page 49: Smart Embedded Management Agent (Sema)

Express-CFR 5. Smart Embedded Management Agent (SEMA) The onboard microcontroller (BMC) implements power sequencing and Smart Embedded Management Agent (SEMA) functionality. The microcontroller communicates via the System Management Bus with the CPU/chipset. The following functions are implemented: ‧ Total operating hours counter. Counts the number of hours the module has been run in minutes. ‧... -

Page 50: Board Specific Sema Functions

5.1. Board Specific SEMA Functions 5.1.1. Voltages The BMC of the Express-CFR implements a voltage monitor and samples several onboard voltages. The voltages can be read by calling the SEMA function “Get Voltages”. The function returns a 16-bit value divided into high-byte (MSB) and low-byte (LSB). -

Page 51: Table 8: Sema Bmc Status

Express-CFR 5.1.3. BMC Status This register shows the status of BMC controlled signals on the Express-CFR. Status Bit Signal WDT_OUT LVDS_VDDEN LVDS_BKLTEN BIOS_MODE POSTWDT_DISn SEL_BIOS BIOS_DIS0n BIOS_DIS1n Table 8: SEMA BMC Status 5.1.4. Exception Codes In case of an error, the BMC drives a blinking code on the blue Status LED (LED1). The same error code is also reported by the BMC Flags register. -

Page 52: Table 9: Sema Exception Codes

Exception Code Error Message NO_V5_DUAL NO_PWRSRC_GD NO_P_5V_3V3_S0_PG Table 9: SEMA Exception Codes 5.1.5. BMC Flags The BMC Flags register returns the last detected Exception Code since power-up and shows the BIOS in use and the power mode. Description [ 0 ~ 4 ] Exception Code [ 6 ] 0 = AT mode... -

Page 53: System Resources

Express-CFR 6. System Resources 6.1. System Memory Map Address Range (hex) Description FF000000-FFFFFFFF Motherboard resources FEE00000-FEEFFFFF Motherboard resources FED45000-FED93FFF Motherboard resources FED40000-FED44FFF Trusted Platform Module 2.0 FED10000-FED3FFFF Motherboard resources FED00000-FED003FF High precision event timer FC800000-FE7FFFFF PCI Express Root Complex E0000000-EFFFFFFF Motherboard resources 90000000-DFFFFFFF PCI Express Root Complex... -

Page 54: Interrupt Request (Irq) Lines

Hex Range Device RTC Controller RTC Controller RTC Controller RTC Controller RTC Controller 76h – 77h RTC Controller Motherboard resources Motherboard resources A0h – A1h Interrupt Controller B2h – B3h Motherboard resources B4h – B5h Interrupt Controller B8h – B9h Interrupt Controller BCh –... - Page 55 Express-CFR IRQ# Typical Intterupt Resource Connected to Pin Available PS/2 Mouse IRQ12 via SERIRQ / PIRQ Note (1) Note (1) Intel Serial IO GPIO Host Controller PIRQ Note (1) PIRQ Note (1) Note (1): These IRQs can be used for PCI devices when onboard device is disabled. APIC Mode IRQ# Typical Intterupt Resource...

-

Page 56: Pci Configuration Space Map

6.4. PCI Configuration Space Map Bus Number Device Number Function Number Routing Description Intel host Bridge Internal Intel I.G.D. Internal Gaussian Mixture Model Internal Thermal Subsystem Internal xHCI Controller Internal Intel RAM Internal Intel Corporation System Device Internal I2C Interface 0 Internal I2C Interface 1 Internal... -

Page 57: Pci Interrupt Routing Map

Express-CFR 6.5. PCI Interrupt Routing Map P.E.G. Root IGFX LPC Bridge HD Audio SMBus Line Port Controller Controller Int0 INTA:16 INTA:16 INTA:16 INTA:16 INTA:16 INTA:16 Int1 INTB:17 INTB:17 Int2 INTC:18 INTC:18 Int3 INTD:19 INTD:19 SATA Thermal XHCI Line Controller Controller Controller Controller Int0... - Page 58 This page intentionally left blank. System Resources...

-

Page 59: Bios Setup

Express-CFR 7. BIOS Setup 7.1. Menu Structure This section presents the six primary menus of the BIOS Setup Utility. Use the following table as a quick reference for the contents of the BIOS Setup Utility. The subsections in this section describe the Submenus and setting options for each menu item. -

Page 60: Main

7.2. Main The Main Menu provides read-only information about your system and also allows you to set the System Date and Time. Refer to the tables below the screen shot of this menu for details of the Submenus and settings. 7.2.1. - Page 61 Express-CFR Board Information Info only Description Runtime Statistics Info only Total Runtime Read only The returned value specifies the total time in minutes the system is running in S0 state. Current Runtime Read only The returned value specifies the time in seconds the system is running in S0 state.

-

Page 62: Advanced

7.3. Advanced This menu contains the settings for most of the user interfaces in the system 7.3.1. CPU Configuration Feature Options Description Type Info only Display CPU information. Info only Display CPU information. Microcode Revision Info only Display CPU Microcode Revision. Speed Info only Display CPU frequency. - Page 63 Express-CFR Feature Options Description the Package RAPL algorithm. Platform PL1 Time Window Platform Power Limit 1 Time Window value in seconds. The value may vary from 0 to 128. 0 = default values. Indicates the time window over which Platform TDP value should be maintained. C states Enable/Disable CPU Power Management.

- Page 64 Feature Options Description LVDS Backlight Mode Select LVDS Backlight control function. BMC Mode GTT Mode LVDS Backlight Brightness A change takes effect immediately. Brightness Setting Set GOP Brightness value Integrated Display Configuration Info only eDP/LVDS Enable/Disable eDP/LVDS Disable Enable DDI port 1 No Device Set DDI port 1 function to DisplayPort or HDMI.

- Page 65 Express-CFR 7.3.3. Power Management Feature Options Description Power Management Info only Enable ACPI Auto Configuration Enables or Disables BIOS ACPI Auto Configuration. Disabled Enabled Enable Hibernation Disabled Enables or Disables System ability to Hibernate (OS/S4 Sleep State). This option may not be effective Enabled with some operating systems.

- Page 66 Feature Options Description V5SBY Read only Display actual voltage of the V5VSB. Read only Display actual voltage of the V12. 7.3.4. USB Configuration Feature Options Description USB Configuration Info only USB Module Version Info only USB Controllers: Info only USB Devices: Info only XHCI Compliance Mode Option to enable Compliance Mode.

- Page 67 Express-CFR 7.3.6.1. System Management > SEMA Features Feature Options Description SEMA Features: Info only Displays the SEMA features. 7.3.6.2. System Management > Flags Feature Options Description Flags Info only BMC Flags Read only BIOS Select Read only ATX/AT-Mode Read only Exception Code Read only 7.3.7.

- Page 68 7.3.7.1. Temperatures and Fan Speed > Smart Fan Feature Options Description Smart Fan Info only CPU Smart FanTemperature CPU Smart FanTemperature Source. CPU Sensor Source Board Sensor CPU Fan Mode CPU Fan Mode AUTO (Smart Fan) Fan Off Fan On Trigger Point 1 Info only Trigger Temperature...

- Page 69 Express-CFR Feature Options Description Serial Port 2 Configuration Submenu NCT5104D Super IO Configuration Info only Serial Port 1 Configuration Submenu Serial Port 2 Configuration Submenu NCT5104DSEC Super IO Info only Configuration 7.3.9.1. W83627DHGSEC Super IO Configuration > Serial Port 1 Configuration Feature Options Description...

- Page 70 Feature Options Description IRQ=3,4,5,6,7,10,11,12 IO=268h; IRQ=3,4,5,6,7,10,11,12 7.3.9.3. NCT5104D Super IO Configuration > Serial Port 1 Configuration Feature Options Description Serial Port 1 Configuration Info only Serial Port Enable or Disable Serial Port (COM). Enabled Disabled Device Settings IO=3f8h; IRQ=4 Fixed configuration of serial port. Change Settings Select an optimal setting for Super IO device.

- Page 71 Express-CFR Feature Options Description Disabled Console Redirection Settings Submenu COM2 Info only Console Redirection Console Redirection Enable or Disable. Enabled Disabled Console Redirection Settings Submenu COM3 Info only Console Redirection Enabled Console Redirection Enable or Disable. Disabled Console Redirection Settings Submenu COM4 Info only...

- Page 72 Feature Options Description ANSI/VT100 terminals. Enable Recorder Mode With this mode enabled only text will be sent. This is Disabled to capture Terminal data. Enable Resolution 100x31 Enables or disables extended terminal resolution Disabled Enable Putty KeyPad Select FunctionKey and KeyPad on Putty. VT100 LINUX XTERMR6...

- Page 73 Express-CFR Feature Options Description Miscellaneous Info only Network Controls the execution of UEFI Network OpROM Do not launch UEFI 7.3.11.1. Miscellaneous > Trusted Computing Feature Options Description Security Device Support Enables or Disables BIOS support for security device. Disabled O.S. will not show Security Device. TCG EFI protocol Enabled and INT1A interface will not be available.

- Page 74 7.3.13. Network Stack Configuration Feature Options Description Network Stack Enable/Disable UEFI network stack. Disabled Enabled IPv4 PXE Support Enable/Disable IPv4 PXE boot support. If disabled, Disabled IPv4 PXE boot support will not be available. Enabled IPv4 HTTP Support Enable/Disable IPv4 HTTP boot support. If disabled, Disabled IPv4 HTTP boot support will not be available.

-

Page 75: Chipset

Express-CFR 7.4. Chipset Feature Options Description System Agent (SA) Configuration Submenu PCH-IO Configuration Submenu 7.4.1. Chipset > System Agent (SA) Configuration Feature Options Description System Agent (SA) Configuration Info only SA PCIe Code Version Read only VT-d Read only Memory Configuration Submenu Graphics Configuration Submenu... - Page 76 7.4.1.1. Chipset > System Agent (SA) Configuration > Memory Configuration Feature Options Description Memory Configuration Info only Maximum Memory Frequency Maximum Memory Frequency Selections in MHz. Auto 1067 Valid values should match the refclk, i.e. divide by 133 1200 or 100 1333 1400 1600...

- Page 77 Express-CFR 7.4.1.2. Chipset > System Agent (SA) Configuration > Graphics Configuration Feature Options Description Graphics Configuration Info only Skip Scaning of External Gfx If Enable, it will not scan for External Gfx Card on Disabled Card PEG and PCH PCIE Ports Enabled Select which of IGFX/PEG/PCI Graphics device Primary Display...

- Page 78 7.4.1.3. Chipset > System Agent (SA) Configuration > PEG Port Configuration Feature Options Description PEG Port Configuration Info only PEG 0:1:0 Read only Enable Root Port Disabled Enable or Disable the Root Port Enabled Auto Max Link Speed Configure PEG 0:1:0 Max Speed Auto Gen1 Gen2...

- Page 79 Express-CFR Feature Options Description PEG0 Slot Power Limit Value Sets the upper limit on power supplied by slot. Power limit (in Watts) is calculated by multiplying this value by the Slot Power Limit Scale. Values 0-255 PEG0 Slot Power Limit Scale Select the scale used for the Slot Power Limit Value.

- Page 80 Feature Options Description PEG11 RxCTLE Overide When Enabled, overrides PEG1 RxCTLE adaptive Disabled Enabled behavior When Enabled, overrides PEG2 RxCTLE adaptive PEG12 RxCTLE Overide Disabled Enabled behavior DMI RxCTLE Overide When Enabled, overrides DMI RxCTLE adaptive Disabled Enabled behavior 7.4.2. Chipset >...

- Page 81 Express-CFR 7.4.2.1. Chipset > PCH-IO Configuration > PCI Express Configuration Feature Options Description PCI Express Configuration Info only PCI Express Clock Gating Disabled PCI Express Clock Gating Enable/Disable for each root port. Enabled The control of Active State Power Management of the DMI Link ASPM Control Disabled DMI Link.

- Page 82 Feature Options Description L1.1 L1.1 & L1.2 Gen3 Eq Phase3 Method PCIe Gen3 Equalization Phase 3 Method Hardware Static Coeff. UPTP Upstream Port Transmitter Preset DPTP Downstream Port Transmitter Preset Enable/Disable Access Control Services Extended Disabled Capability Enable Disabled Enable/Disable Precision Time Measurement Enable Disabled Enable/Disable Downstream Port Containment...

- Page 83 Express-CFR Feature Options Description Extra Bus Reserved Extra Bus Reserved (0-7) for bridges behind this Root Bridge. Reseved Memory Reserved Memory for this Root Bridge (1-20) MB. Reserved I/O Reserved I/O (4K/8K/12K/16K/20K) Range for this Root Bridge. PCH PCIe LTR Configuration Info only Disabled PCH PCIE Latency Reporting Enable/Disable.

- Page 84 Feature Options Description Alternate Server Software Feature Mask Submenu Configuration Aggressive LPM Support Disabled Enable PCH to aggressively enter link power state. Enabled SATA Controller Speed Default Indicates the maximum speed the SATA controller can support. Gen1 Gen2 Gen3 Serial ATA Port X Info only Software Preserve Info only...

- Page 85 Express-CFR 7.4.2.5. Chipset > PCH-IO Configuration > Serial IO Configuration Feature Options Description I2C0 Controller Disabled Enables or Disables Serial IO Controller. If given device is Function 0 PSF disabling is skipped. Enabled PSF default will remain and device PCI CFG Space will still be visible.

-

Page 86: Security

7.5. Security Feature Options Description Password Description Info only Administrator Password Enter password User Password Enter password Secure Boot menu Submenu 7.5.1. Secure Boot menu Feature Options Description Secure Boot Info only Secure Boot feature is Active if Secure Boot is Secure Boot Control Disabled Enabled,platform Key(PK) is enrolled and the System... - Page 87 Express-CFR Feature Options Description Key Exchange Keys Details Enroll Factory Defaults or load the keys from a file with: Export 1. Public Key Certificate in: Update a) EFI_SIGNATURE_LIST Append b) EFI_CERT_X509 (DER encoded) Delete c) EFI_CERT_RSA2048 (bin) d) EFI_CERT_SHA256 (bin) 2.

- Page 88 7.5.2. HDD Security Configuration Feature Options Description HDD Password Description Info only Set User Password Enter HDD User Set HDD User Password. password *** It is advised to power cycle the system after setting the HDD password ***. Discard or Save changes option in setup does not have any impact on HDD when password is set or removed.If the ‘Set HDD User Password’...

-

Page 89: Boot

Express-CFR 7.6. Boot 7.6.1. Boot Configuration Feature Options Description Boot Configuration Info only Number of seconds to wait for setup activation key. Setup Prompt Timeout 65535(0xFFFF) means indefinite waiting. Bootup NumLock State Select the keyboard NumLock state Quiet Boot Disabled Enables or disables Quiet Boot option Enabled Fast Boot... -

Page 90: Save & Exit

7.7. Save & Exit 7.7.1. Reset Options Feature Options Description Save Changes and Reset Save Changes and Reset Save Changes and Exit Exit system setup after saving the changes. Discard Changes and Exit Exit system setup without saving any changes. Save Changes and Reset Reset the system after saving the changes. -

Page 91: Bios Checkpoints, Beep Codes

Express-CFR 8. BIOS Checkpoints, Beep Codes This section of this document lists checkpoints and beep codes generated by AMI Aptio BIOS. The checkpoints defined in this document are inherent to the AMIBIOS generic core, and do not include any chipset or board specific checkpoint definitions. -

Page 92: Status Code Ranges

8.1. Status Code Ranges Status Code Description Range 0x01 – 0x0B SEC execution 0x0C – 0x0F SEC errors 0x10 – 0x2F PEI execution up to and including memory detection 0x30 – 0x4F PEI execution after memory detection 0x50 – 0x5F PEI errors 0x60 –... - Page 93 Express-CFR SEC Error Codes 0x0C – 0x0D Reserved for future AMI SEC error codes 0x0E Microcode not found 0x0F Microcode not loaded 8.2.2. SEC Beep Codes None 8.2.3. PEI Phase Status Code Description Progress Codes 0x10 PEI Core is started 0x11 Pre-memory CPU initialization is started 0x12...

- Page 94 Status Code Description 0x35 CPU post-memory initialization. Boot Strap Processor (BSP) selection 0x36 CPU post-memory initialization. System Management Mode (SMM) initialization 0x37 Post-Memory North Bridge initialization is started 0x38 Post-Memory North Bridge initialization (North Bridge module specific) 0x39 Post-Memory North Bridge initialization (North Bridge module specific) 0x3A Post-Memory North Bridge initialization (North Bridge module specific) 0x3B...

- Page 95 Express-CFR Status Code Description S3 Resume Error Codes 0xE8 S3 Resume Failed 0xE9 S3 Resume PPI not Found 0xEA S3 Resume Boot Script Error 0xEB S3 OS Wake Error 0xEC-0xEF Reserved for future AMI error codes Recovery Progress Codes 0xF0 Recovery condition triggered by firmware (Auto recovery) 0xF1 Recovery condition triggered by user (Forced recovery)

- Page 96 8.2.5. DXE Status Codes Status Code Description 0x60 DXE Core is started 0x61 NVRAM initialization 0x62 Installation of the South Bridge Runtime Services 0x63 CPU DXE initialization is started 0x64 CPU DXE initialization (CPU module specific) 0x65 CPU DXE initialization (CPU module specific) 0x66 CPU DXE initialization (CPU module specific) 0x67...

- Page 97 Express-CFR Status Code Description 0x95 PCI Bus Request Resources 0x96 PCI Bus Assign Resources 0x97 Console Output devices connect 0x98 Console input devices connect 0x99 Super IO Initialization 0x9A USB initialization is started 0x9B USB Reset 0x9C USB Detect 0x9D USB Enable 0x9E –...

- Page 98 Status Code Description 0xB8 – 0xBF Reserved for future AMI codes 0xC0 – 0xCF OEM BDS initialization codes DXE Error Codes 0xD0 CPU initialization error 0xD1 North Bridge initialization error 0xD2 South Bridge initialization error 0xD3 Some of the Architectural Protocols are not available 0xD4 PCI resource allocation error.

-

Page 99: Oem-Reserved Checkpoint Ranges

Express-CFR Status Code Description 0x10 System is waking up from the S1 sleep state 0x20 System is waking up from the S2 sleep state 0x30 System is waking up from the S3 sleep state 0x40 System is waking up from the S4 sleep state 0xAC System has transitioned into ACPI mode. - Page 100 This page intentionally left blank. BIOS Checkpoints, Beep Codes...

-

Page 101: Mechanical Information

Express-CFR 9. Mechanical Information 9.1. Board-to-Board Connectors To allow for different stacking heights, the receptacles for COM Express carrier boards are available in two heights: 5 mm and 8 mm. When 5 mm receptacles are chosen, the carrier board should be free of components. Tyco 3-1827253-6 Foxconn QT002206-2131-3H •... -

Page 102: Thermal Solution

9.2. Thermal Solution This section presents general thermal solution information for COM Express modules for your reference. Photos and details may vary depending on the specific module. 9.2.1. Heat Spreaders The function of the heat spreader is to ensure an identical mechanical profile for all COM Express modules. By using a heat spreader, the thermal solution that is built on top of the module is compatible with all COM Express modules. - Page 103 Express-CFR Step 3: Assemble the heatsink onto the COM Express module. Use the three M2.5, L=6mm screws provided to fasten the heatsink to the module. Note: The Express-CFR uses three screws to attach the heatsink to the COM Express module. Step 4: Place the COM Express module and heatsink assembly onto the connectors on the carrier board as shown.

- Page 104 Step 6: If you are installing a heatsink with a fan, plug the fan connector into the carrier board as shown. Mechanical Information...

-

Page 105: Mounting Methods

Express-CFR 9.3. Mounting Methods There are several standard ways to mount the COM Express module with a thermal solution onto a carrier board. In addition to the choice of 5 mm or 8mm board-to-board connectors, there is the choice of Top and Bottom mounting. -

Page 106: Standoff Types

9.4. Standoff Types The standoffs available for Top and Bottom mounting methods are shown below. Note that threaded standoffs are DIP type and through-hole standoffs are SMT type. Other types not listed are available upon request. 5mm through-hole standoff (SMT type) 5mm threaded standoff (DIP type) P/N: 33-72000-0050 P/N: 33-72016-0050... -

Page 107: Safety Instructions

Express-CFR Safety Instructions Read and follow all instructions marked on the product and in the documentation before you operate your system. Retain all safety and operating instructions for future use. • Please read these safety instructions carefully. • Please keep this User‘s Manual for later reference. •... -

Page 108: Getting Service

5215 Hellyer Avenue, #110, San Jose, CA 95138, USA Tel: +1-408-360-0200 Toll Free: +1-800-966-5200 (USA only) Fax: +1-408-360-0222 Email: info@adlinktech.com ADLINK Technology (China) Co., Ltd. Address: 300 Fang Chun Rd., Zhangjiang Hi-Tech Park, Pudong New Area Shanghai, 201203 China Tel: +86-21-5132-8988 Fax: +86-21-5132-3588 Email: market@adlinktech.com...

Need help?

Do you have a question about the COM Express Express-CFR and is the answer not in the manual?

Questions and answers