Table of Contents

Advertisement

Quick Links

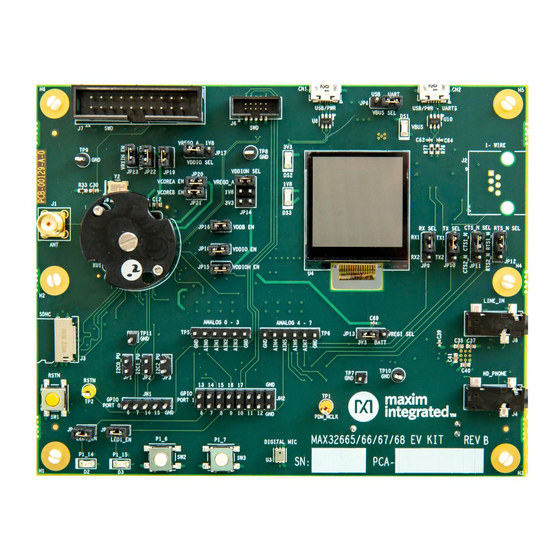

MAX32665–MAX32668 USER GUIDE

UG6971; Rev 0; 6/19

Abstract:

This user guide provides application developers information on how to use the memory and peripherals of the

MAX32665–MAX32668 microcontroller. Detailed information for all registers and fields in the device are covered.

Guidance is given for managing all the peripherals, clocks, power and startup for the device family.

Advertisement

Table of Contents

Summary of Contents for Maxim Integrated MAX32665

- Page 1 This user guide provides application developers information on how to use the memory and peripherals of the MAX32665–MAX32668 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing all the peripherals, clocks, power and startup for the device family.

-

Page 2: Table Of Contents

MAX32665-MAX32668 User Guide MAX32665—MAX32669 User Guide Table of Contents Overview ----------------------------------------------------------------------------------------------------------------- 24 Block Diagram ---------------------------------------------------------------------------------------------------------------- 25 Resource Protection Unit (RPU) ------------------------------------------------------------------------------------ 26 Instances ----------------------------------------------------------------------------------------------------------------------- 26 Usage --------------------------------------------------------------------------------------------------------------------------- 28 2.2.1 Reset State -------------------------------------------------------------------------------------------------------------------------------- 28 2.2.2 MPU Implementation ------------------------------------------------------------------------------------------------------------------ 28 2.2.3 MPU Protection Fault ------------------------------------------------------------------------------------------------------------------ 28 2.2.4... - Page 3 MAX32665-MAX32668 User Guide 3.4.1 Core AHB Interfaces --------------------------------------------------------------------------------------------------------------------- 40 3.4.2 AHB Masters ------------------------------------------------------------------------------------------------------------------------------ 41 Peripheral Register Map --------------------------------------------------------------------------------------------------- 41 3.5.1 APB Peripheral Base Address Map -------------------------------------------------------------------------------------------------- 41 3.5.2 AHB Peripheral Base Address Map ------------------------------------------------------------------------------------------------- 42 Error Correction Coding (ECC) Module --------------------------------------------------------------------------------- 43 3.6.1...

- Page 4 MAX32665-MAX32668 User Guide RAM Memory Management ---------------------------------------------------------------------------------------------- 67 4.8.1 RAM Zeroization ------------------------------------------------------------------------------------------------------------------------- 67 4.8.2 RAM Low Power Modes --------------------------------------------------------------------------------------------------------------- 67 Miscellaneous Control Registers ----------------------------------------------------------------------------------------- 68 4.10 Miscellaneous Control Registers Details ------------------------------------------------------------------------------- 68 4.11 Single Inductor Multiple Output (SIMO) Power Supply ------------------------------------------------------------ 71 4.11.1...

- Page 5 MAX32665-MAX32668 User Guide 7.2.1 Clock Configuration ------------------------------------------------------------------------------------------------------------------- 135 7.2.2 Lock Protection ------------------------------------------------------------------------------------------------------------------------- 135 7.2.3 Flash Write Width --------------------------------------------------------------------------------------------------------------------- 135 7.2.4 Flash Write ------------------------------------------------------------------------------------------------------------------------------ 136 7.2.5 Page Erase ------------------------------------------------------------------------------------------------------------------------------- 136 7.2.6 Mass Erase ------------------------------------------------------------------------------------------------------------------------------ 137 Flash Error Correction Coding ------------------------------------------------------------------------------------------ 137...

- Page 6 MAX32665-MAX32668 User Guide 9.2.3 Data Movement From the DMA to Destination ------------------------------------------------------------------------------- 226 Usage ------------------------------------------------------------------------------------------------------------------------- 227 Count-To-Zero (CTZ) Condition ---------------------------------------------------------------------------------------- 227 Chaining Buffers ----------------------------------------------------------------------------------------------------------- 228 DMA Interrupts ------------------------------------------------------------------------------------------------------------ 230 Channel Timeout Detect ------------------------------------------------------------------------------------------------- 230 Memory-to-Memory DMA ---------------------------------------------------------------------------------------------- 231 DMAC Registers ------------------------------------------------------------------------------------------------------------ 231 9.10...

- Page 7 MAX32665-MAX32668 User Guide 12.1 Instances --------------------------------------------------------------------------------------------------------------------- 260 12.2 UART Frame ----------------------------------------------------------------------------------------------------------------- 260 12.3 UART Interrupts ------------------------------------------------------------------------------------------------------------ 261 12.4 UART Baud Rate Clock Source ------------------------------------------------------------------------------------------ 261 12.5 UART Baud Rate Calculation -------------------------------------------------------------------------------------------- 261 12.6 UART Configuration and Operation ----------------------------------------------------------------------------------- 263 12.7 Wakeup Time --------------------------------------------------------------------------------------------------------------- 263 12.8...

- Page 8 MAX32665-MAX32668 User Guide 13.6 Register Details ------------------------------------------------------------------------------------------------------------ 293 Quad Serial Peripheral Interface (SPI) ------------------------------------------------------------------------- 306 14.1 Instances --------------------------------------------------------------------------------------------------------------------- 307 14.2 SPI Formats ----------------------------------------------------------------------------------------------------------------- 308 14.2.1 Four-Wire SPI --------------------------------------------------------------------------------------------------------------------------- 308 14.2.2 Three-Wire SPI -------------------------------------------------------------------------------------------------------------------------- 309 14.3 Pin Configuration ---------------------------------------------------------------------------------------------------------- 310 14.3.1 QSPIn Alternate Function Mapping ----------------------------------------------------------------------------------------------- 310 14.3.2...

- Page 9 MAX32665-MAX32668 User Guide 16.3 Timer Pin Functionality--------------------------------------------------------------------------------------------------- 330 16.4 One-Shot Mode (000b) --------------------------------------------------------------------------------------------------- 330 16.4.1 One-Shot Mode Timer Period ------------------------------------------------------------------------------------------------------ 331 16.4.2 One-Shot Mode Configuration ----------------------------------------------------------------------------------------------------- 331 16.5 Continuous Mode (001b) ------------------------------------------------------------------------------------------------ 331 16.5.1 Continuous Mode Timer Period ---------------------------------------------------------------------------------------------------- 332 16.5.2...

- Page 10 MAX32665-MAX32668 User Guide 17.7 Pulse Train Interrupts ---------------------------------------------------------------------------------------------------- 352 17.8 Registers --------------------------------------------------------------------------------------------------------------------- 352 17.9 Register Details ------------------------------------------------------------------------------------------------------------ 354 17.9.1 Pulse Train Engine Safe Enable Register ----------------------------------------------------------------------------------------- 363 17.9.2 Pulse Train Engine Safe Disable Register ---------------------------------------------------------------------------------------- 364 Real-Time Clock (RTC) --------------------------------------------------------------------------------------------- 369 18.1...

- Page 11 MAX32665-MAX32668 User Guide 20.1 Instances --------------------------------------------------------------------------------------------------------------------- 387 20.2 Pins and Configuration --------------------------------------------------------------------------------------------------- 388 20.2.1 Pin Configuration ---------------------------------------------------------------------------------------------------------------------- 388 20.2.2 1-Wire I/O (OWM_IO) ---------------------------------------------------------------------------------------------------------------- 388 20.2.3 Pullup Enable (OWM_PE) ----------------------------------------------------------------------------------------------------------- 388 20.2.4 Clock Configuration ------------------------------------------------------------------------------------------------------------------- 388 20.3 1-Wire Protocol ------------------------------------------------------------------------------------------------------------ 389 20.3.1...

- Page 12 MAX32665-MAX32668 User Guide 21.10 Isochronous Endpoints --------------------------------------------------------------------------------------------------- 407 21.10.1 Isochronous IN Endpoints ------------------------------------------------------------------------------------------------------- 407 21.10.2 Isochronous OUT Endpoints ---------------------------------------------------------------------------------------------------- 408 21.11 USBHS Device Registers -------------------------------------------------------------------------------------------------- 409 21.12 USBHS Device Register Details ----------------------------------------------------------------------------------------- 410 21.12.2 Endpoint Register Access Control --------------------------------------------------------------------------------------------- 416 21.12.3...

- Page 13 Figure 16-5: Counter Mode Diagram ............................340 Figure 16-6: Gated Mode Diagram ............................342 Figure 18-1. MAX32665―MAX32668 RTC Block Diagram (12-bit Sub-Second Counter) ............369 Figure 18-2. RTC Busy/Ready Signal Timing ..........................371 Figure 18-3. RTC Interrupt/Wakeup Diagram Wakeup Function ..................... 373 Figure 18-4.

- Page 14 Figure 20-3: 1-Wire Write Time Slot ............................391 Figure 20-4: 1-Wire Read Time Slot ............................391 Figure 20-5: 1-Wire ROM ID Fields ............................392 Figure 22-1: MAX32665—MAX32668 Bluetooth Stack Overview ................... 427 Figure 23-1. Cryptographic Accelerator Block Diagram ......................430 Figure 23-2. DMA Block Diagram ............................. 431 Figure 23-3.

- Page 15 Table 2-2. MAX32665—MAX32668 Master Permission Bits ..................... 26 Table 2-3: MAX32665—MAX32668 AHB Slaves ........................27 Table 2-4. MAX32665—MAX32668 AHB Master/Slave Interconnect Matrix ................27 Table 2-5: RPU APB Register Offsets, Names, Access, and Descriptions ................... 29 Table 2-6: RPU AHB Slave Register Addresses, Names, Access, and Descriptions ..............30 Table 2-7: RPU APB Slave Permission Registers .........................

- Page 16 Table 5-1: MAX32665—MAX32668 Interrupt Vector Table ....................115 Table 6-1: MAX32665—MAX32668 GPIO Pin Count ....................... 119 Table 6-2: MAX32665—MAX32668 GPIO and Alternate Function Matrix, 140 WLP .............. 120 Table 6-3: MAX32665—MAX32668 GPIO Pin Configuration ....................121 Table 6-4: MAX32665—MAX32668 Input Mode Configuration ....................121 Table 6-5: MAX32665—MAX32668 Output Mode Configuration ...................

- Page 17 Table 6-41: GPIOn Pulldown/Pullup Strength Select Register ....................133 Table 6-42: GPIOn Supply Voltage Select Register ........................133 Table 7-1: MAX32665—MAX32668 Internal Flash Memory Organization ................134 Table 7-2: Valid Addresses Flash Writes ..........................135 Table 7-3: Flash Controller Registers ............................137 Table 7-4: Flash Controller Address Pointer Register ......................

- Page 18 Table 8-41: SRCC Cache Control Register ..........................179 Table 8-42: SRCC Invalidate Register ............................180 Table 8-43: MAX32665—MAX32668 SDHC Alternate Function Mapping to SDHC Specification Pin Names ......182 Table 8-44: Registers Used to Generate SD Commands ......................184 Table 8-45: SDHC Register Offsets, Names and Descriptions ....................185 Table 8-46: SDHC SDMA System Address / Argument Register....................

- Page 19 Table 8-95: SDHC Host Controller Version Register ......................... 221 Table 9-1: MAX32665—MAX32668 DMAC and Channel Instances ..................223 Table 9-2: MAX32665—MAX32668 DMAC Source and Destination by Peripheral ..............224 Table 9-3: Data Movement from Source to DMA FIFO ......................226 Table 9-4: Data Movement from the DMA FIFO to Destination ....................

- Page 20 Table 10-10: CRC Value Register .............................. 245 Table 10-11: CRC Pseudo-Random Number Generator Register ..................... 245 Table 11-1: MAX32665—MAX32668 ADC Peripheral Pins ...................... 246 Table 11-2: ADC Clock Frequency and ADC Conversion Time (�������������� = 96������, ���������� = 48������)......249 Table 11-3: Input and Reference Scale Support by ADC Input Channel ..................

- Page 21 Table 17-10: Pulse Train n Loop Configuration Register ......................367 Table 17-11: Pulse Train n Automatic Restart Configuration Register ..................367 Table 18-1. MAX32665―MAX32668 RTC Counter and Alarm Registers ................. 370 Table 18-2. RTC Register Access .............................. 370 Table 18-3. MAX32665―MAX32668 RTC Square Wave Output Configuration ..............374 Table 18-4.

- Page 22 MAX32665-MAX32668 User Guide Table 18-7. RTC Time-of-Day Alarm Register ........................... 377 Table 18-8. RTC Sub-Second Alarm Register ..........................377 Table 18-9. RTC Control Register ............................. 377 Table 18-10. RTC 32KHz Oscillator Digital Trim Register ......................379 Table 18-11. RTC 32KHz Oscillator Control Register ........................ 379 Table 19-1: Watchdog Timer Interrupt Period fSYS_CLK = 96MHz and fPCLK = 48MHz ............

- Page 23 MAX32665-MAX32668 User Guide Table 23-2. Symmetric Block Ciphers ............................433 Table 23-3. Hash Functions ..............................436 Table 23-4. Cryptographic Memory Segments ........................440 Table 23-5. MAA Memory Segments and Locations ........................ 441 Table 23-6. MAA Memory Blinding Example (Memory Instance 0, MAWS > 1024) ..............441 Table 23-7.

-

Page 24: Overview

MAX32665-MAX32668 User Guide Overview The MAX32665–MAX32668 are Arm® Cortex®-M4 with FPU-based microcontrollers with 1MB flash and up to 560KB SRAM that can be configured as 448KB SRAM with error correction coding (ECC). They are ideal for wearable medical fitness applications. Optionally available is a second Arm Cortex-M4 with FPU for audio signal processing in a wireless headset/earbud application (MAX32665/MAX32666 only). -

Page 25: Block Diagram

MAX32665-MAX32668 User Guide Block Diagram Figure 1-1: MAX32665—MAX32668 Block Diagram MAX32665/MAX32666/MAX32667/MAX32668 SD3.0/S DIO3.0/ 96MHz Arm® Cortex®-M4 eMMC4.51 HOST WITH FPU CPU0 60MHz 96MHz HFXOUT NVIC 3 × I C MASTER HFXIN 32 .768kHz Arm® Cortex®-M4 WITH FPU CPU1 7.3728MHz 3 × 4-WIRE UART... -

Page 26: Resource Protection Unit (Rpu)

Because of the structure of the APB bus, there is only one access control bit. This means that the read and write access permissions for a particular master must always be the same. Access permissions for read and write can be configured separately for AHB slaves. Table 2-2. MAX32665—MAX32668 Master Permission Bits Bit Position in SLAVEAPB Register Bit Position in... -

Page 27: Table 2-3: Max32665-Max32668 Ahb Slaves

System RAM, Memory Instance 6 The AHB bus prohibits some AHB master and slave interactions as shown in Table 2-4. The AHB slave ignores the state of prohibited combinations. Table 2-4. MAX32665—MAX32668 AHB Master/Slave Interconnect Matrix AHB Slave AHB Master DMAC0 DMAC1 SYS0... -

Page 28: Usage

MAX32665-MAX32668 User Guide SPIM USBHS Data Cache SDIO/SDHC Target QSPI/SPI Usage 2.2.1 Reset State During a power-on-reset event, RPU registers are reset to their reset value. If RPU protection is desired, the registers must be reprogrammed during the boot sequence. -

Page 29: Registers

MAX32665-MAX32668 User Guide Registers Table 3-1: APB Peripheral Base Address Map for the RPU Peripheral Base Address. Table 2-5: RPU APB Register Offsets, Names, Access, and Descriptions Offset Register Access Description [0x0000] GCR RPU Register [0x0004] SIR RPU Register [0x0008]... -

Page 30: Table 2-6: Rpu Ahb Slave Register Addresses, Names, Access, And Descriptions

MAX32665-MAX32668 User Guide Offset Register Access Description [0x0270] SPIXFC SPIXFC RPU Register [0x0280] DMA0 DMA0 RPU Register [0x0290] FLC0 FLC0 RPU Register [0x0294] FLC1 FLC1 RPU Register [0x02A0] ICC0 ICC0 RPU Register [0x02A4] ICC1 ICC1 RPU Register [0x02F0] ICX RPU Register... -

Page 31: Register Details

MAX32665-MAX32668 User Guide APB Address Register Access Description [0x0F00] SYS_RAM (MI0) SYS_RAM (MI0) RPU Register [0x0F10] SYS_RAM (MI1) SYS_RAM (MI1) RPU Register [0x0F20] SYS_RAM (MI2) SYS_RAM (MI2) RPU Register [0x0F30] SYS_RAM (MI3) SYS_RAM (MI3) RPU Register [0x0F40] SYS_RAM (MI4) SYS_RAM (MI4) RPU Register... - Page 32 MAX32665-MAX32668 User Guide Register Name Register Mnemonic Reference Timer 4 RPU Register TMR4 Table 2-5 Timer 5 RPU Register TMR5 Table 2-5 HTimer 0 RPU Register HTMR0 Table 2-5 HTMR1 Table 2-5 HTimer 1 RPU Register I2C Bus 0 (Bus 0) RPU Register...

-

Page 33: Table 2-8: Rpu Ahb Slave Permission Register

MAX32665-MAX32668 User Guide Register Name Register Mnemonic Reference I2C 0 (Bus 1) RPU Register I2C0_BUS1 Table 2-5 I2C 1 (Bus 1) RPU Register I2C1_BUS1 Table 2-5 I2C 2 (Bus 1) RPU Register I2C2_BUS1 Table 2-5 PTG_BUS1 Table 2-5 Pulse Train Engine (Bus 1) RPU Register... -

Page 34: Memory, Register Mapping, And Access

MAX32665-MAX32668 User Guide Memory, Register Mapping, and Access Memory, Register Mapping, and Access Overview The Arm Cortex-M4 architecture defines a standard memory space for unified code and data access. This memory space is addressed in units of single bytes but is most typically accessed in 32-bit (4 byte) units. It may also be accessed, depending on the implementation, in 8-bit (1 byte) or 16-bit (2 byte) widths. -

Page 35: Figure 3-1: Code Memory Mapping

MAX32665-MAX32668 User Guide Figure 3-1: Code Memory Mapping Legend Arm Cort ex-M4 Defined Buses Memory Spaces Memory Spaces (Cached) External Memory Device (Optional) 0xFFFF_FFFF Int ernal Memory I nstances Undefined/Reserved Reserved 0xA000_0000 0x9FFF_FFFF 0x9FFF_FFFF I-Code A ccess to Co de Sp ace... -

Page 36: Figure 3-2: Data Memory Mapping

MAX32665-MAX32668 User Guide Figure 3-2: Data Memory Mapping Le gend 0x40 13_C000 Pulse Tra in s - BUS 1 0x4012_0000 Reserved ARM Cort ex-M4 AHB Bus Mast ers AHB Bus Masters 0x40 11_D000 I2C (0, 1, 2) – BUS 1... -

Page 37: Standard Memory Regions

The code space memory on the MAX32665—MAX32668 also contains the mapping for the flash information block, from 0x1080 0000 to 0x1080 7FFF. However, this mapping is generally only present during Maxim Integrated production test; it is disabled once the information block has been loaded with valid data and the info block lockout option has been set. This memory is accessible for data reads only and cannot be used for code execution. -

Page 38: Peripheral Space

AHB bus error. The SRAM area on the MAX32665—MAX32668 can be used to contain executable code. Code stored in the SRAM is accessed directly for execution (using the system bus) and is not cached. The SRAM is also where the Arm Cortex-M4 stack must be located, as it is the only general-purpose SRAM memory on the device. -

Page 39: External Device Space

The external device space area of memory is intended for use in mapping off-chip device control functions onto the AHB bus. This memory space is defined from byte address range 0xA000 0000 to 0xDFFF FFFF (1GB maximum). The MAX32665— MAX32668 does not implement this memory area. -

Page 40: External Memory Cache Controller (Emcc)

TPU Memory The MAX32665—MAX32668 contains a specialized 128-bit memory that is designed to preserve critical data (such as a 128- bit AES key) even when the device is in the lowest power-saving state. As long as the RTC power supply is still available, the contents of this memory will be retained, even if the AES block and the main SRAM are shut down completely. -

Page 41: Ahb Masters

MAX32665-MAX32668 User Guide 3.4.2 AHB Masters 3.4.2.1 USB Endpoint Buffer Manager The USB AHB bus master is used to manage endpoint buffers in the SRAM. It has access to the SRAM (read/write, for storage and retrieval of endpoint buffer data), as well as the internal and/or external flash data contents (which can be used to contain static data for transmission by the USB). -

Page 42: Ahb Peripheral Base Address Map

MAX32665-MAX32668 User Guide Peripheral Register Name Register Prefix APB Base Address APB End Address Timer 1 TMR1_ 0x4001 1000 0x4001 1FFF Timer 2 TMR2_ 0x4001 2000 0x4001 2FFF Timer 3 TMR3_ 0x4001 3000 0x4001 3FFF Timer 4 TMR4_ 0x4001 4000... -

Page 43: Error Correction Coding (Ecc) Module

MAX32665-MAX32668 User Guide Table 3-2: AHB Peripheral Base Address Map AHB Peripheral Register Name Register Prefix AHB Base Address AHB End Address USB Hi-Speed Host USBHS_ 0x400B 1000 0x400B 1FFF SDIO/SDHC Controller (AHB) SDHC_ 0x400B 6000 0x400B 6FFF SPIXF Master Controller FIFO... -

Page 44: Table 3-3: Error Correction Coding (Ecc) Enable Register

MAX32665-MAX32668 User Guide Table 3-3: Error Correction Coding (ECC) Enable Register Error Correction Coding Enable GCR_ECC_EN [0x6C00] Bits Field Access Reset Description 31:13 Reserved for Future Use Do not modify this field. fl1eccen Flash1 ECC Enable 0: Disable 1: Enable... - Page 45 MAX32665-MAX32668 User Guide Error Correction Coding Error GCR_ECC_ER [0x0064] Bits Field Access Reset Description fl1eccerr R/W1C ECC Flash1 Error Indicates an ECC error in the Flash1 bank. Write to 1 to clear. 0: No Error 1: Error fl0eccerr R/W1C ECC Flash0 Error Indicates an ECC error in the Flash0 bank.

-

Page 46: Table 3-5: Correctable Error Detected Register

MAX32665-MAX32668 User Guide Table 3-5: Correctable Error Detected Register Correctable Error Detected GCR_ECC_CED [0x0068] Bits Field Access Reset Description 31:13 Reserved for Future Use Do not modify this field. fl1eccnded R/W1C ECC Flash1 Correctable Error Detected Indicates a single bit correctable error in the Flash1 bank. Write to 1 to clear. -

Page 47: Table 3-6: Error Correction Coding (Ecc) Interrupt Enable Register

MAX32665-MAX32668 User Guide Correctable Error Detected GCR_ECC_CED [0x0068] Bits Field Access Reset Description sysram1ecc_ced R/W1C ECC Sysram1 Correctable Error Detected Indicates a single bit correctable error in the Sysram 1 block. Write to 1 to clear. 0: No single bit error detected... -

Page 48: Table 3-7: Error Correction Coding (Ecc) Address Register

MAX32665-MAX32668 User Guide Error Correction Coding Interrupt Enable GCR_ECC_IRQEN [0x006C] Bits Field Access Reset Description sysram4irqen ECC Sysram4 Interrupt Enable When set, indicates that the interrupt is enabled for occurrence upon a detected error in the Sysram4 block if GCR_ECC_EN.sysram4en is set. - Page 49 MAX32665-MAX32668 User Guide Error Correction Coding Address GCR_ECC_ERRAD [0x0070] Bits Field Access Reset Description dataramerr ECC Error Address/DATA RAM Error Address Data depends on which block has reported the error. If sysram, fl0, or fl1, then this bit(s) represents bit 15 of the AMBA address of read which produced the error.

-

Page 50: System, Power, Clocks, Reset

MAX32665-MAX32668 User Guide System, Power, Clocks, Reset There are several clocks used by different peripherals and subsystems. These clocks are highly configurable by firmware, allowing developers to select the combination of application performance and power savings required for the target systems. -

Page 51: Figure 4-1: Clock Block Diagram

MAX32665-MAX32668 User Guide Figure 4-1: Clock Block Diagram Maxim Integrated Page 51 of 457... -

Page 52: Oscillator Inplementation

MAX32665-MAX32668 User Guide 4.1.1 Oscillator Inplementation Before using any oscillator, the desired oscillator must first be enabled by setting the oscillator’s enable bit in the GCR_CLK_CTRL register. Once an oscillator’s enable bit is set, the oscillator’s ready bit must read 1 prior to attempting to use the oscillator as a system oscillator source. -

Page 53: 8Mhz Internal Oscillator

MAX32665— MAX32668 HFXIN The crysta l lo ad, C , as specified in the MAX32665-MAX 32668 datasheet Electrical HFXIN STRAYIN Characteristics Ta ble is req uired to b e 12 pF. Th ere fore, th e tota l ca pacitance se en... -

Page 54: Operating Modes

MAX32665-MAX32668 User Guide Operating Modes The MAX32665—MAX32668 provides four operating modes: • ACTIVE • SLEEP • DEEPSLEEP • BACKUP ACTIVE is the highest performance operating mode. Any low power state can wake up to ACTIVE by a wakeup event shown Table 4-1. -

Page 55: Figure 4-3: Sleep Mode Clock Control

MAX32665-MAX32668 User Guide Figure 4-3: SLEEP Mode Clock Control Maxim Integrated Page 55 of 457... -

Page 56: Deepsleep Low Power Mode

MAX32665-MAX32668 User Guide 4.2.3 DEEPSLEEP Low Power Mode All internal clocks, except the 8kHz, are gated off. SYS_OSC is gated off, so the two main bus clocks PCLK and HCLK are inactive. The CPU state is retained. The 32kHz oscillator can be enabled via firmware. -

Page 57: Figure 4-4: Deepsleep Clock Control

MAX32665-MAX32668 User Guide Figure 4-4: DEEPSLEEP Clock Control Maxim Integrated Page 57 of 457... -

Page 58: Backup Low Power Mode

MAX32665-MAX32668 User Guide 4.2.4 BACKUP Low Power Mode This is the lowest power operating mode. All oscillators are disabled except for the 8kHz and the 32kHz oscillator. The 32kHz oscillator is firmware controlled. SYS_OSC is gated off, so PCLK and HCLK are inactive. The CPU state is not maintained. -

Page 59: Figure 4-5: Backup Mode Clock Control

MAX32665-MAX32668 User Guide Figure 4-5: BACKUP Mode Clock Control Maxim Integrated Page 59 of 457... -

Page 60: Device Resets

MAX32665-MAX32668 User Guide Device Resets Four device resets are available – Peripheral Reset, Soft Reset, System Reset, and Power-On Reset. On completion of any of the four reset cycles, all peripherals are reset. On completion of any reset cycle HCLK and PCLK are operational, the CPU core receives clocks and power, and the device is in ACTIVE mode. -

Page 61: Peripheral Reset

MAX32665-MAX32668 User Guide Table 4-2: Reset and Low Power Mode Effects Peripheral Soft System ACTIVE SLEEP DEEPSLEEP BACKUP Reset Reset Reset Mode Mode Mode Mode Reset Reset 8kHz Osc 32kHz Osc 7.3728 MHz Osc 60MHz Osc 32MHz Osc 96MHz Osc... -

Page 62: System Reset

MAX32665-MAX32668 User Guide To start a Soft Reset, set GCR_RST0.soft_rst = 1. The reset will be completed immediately upon setting GCR_RST0.soft_rst = 1. 4.3.3 System Reset This is the same as Soft Reset except it also resets all GCR, resetting the clocks to their default state. The CPU state is reset as well as the watchdog timers. -

Page 63: Instruction Cache Controller

MAX32665-MAX32668 User Guide Figure 4-6: MAX32665—MAX32668 Cache Controllers Control ® ® ® ® Corte x Cortex CPU0 CPU1 SYSTEM BUS INSTRUCTION CACHE INSTRUCTION CACHE SPIXF CACHE SPIXR CACHE INTERNA L INTERNA L CONTROLLER 0 (ICC0) CONTROLLER 1 (ICC1) CONTROLLER (SFCC) -

Page 64: Flushing The Icc0/Icc1/Sfcc Cache

MAX32665-MAX32668 User Guide Perform the following steps to enable SFCC. 1. Set PWRSEQ_LPMEMSD.icachexipsd to 0 to ensure the cache power is on. 2. Set SFCC_CACHE_CTRL.enable to 1. 3. Read SFCC_CACHE_CTRL.ready until it returns 1. 4.5.2 Flushing the ICC0/ICC1/SFCC Cache The System Configuration Register (GCR_SCON) includes a field for flushing these caches simultaneously. Setting GCR_SCON.ccache_flush to 1 performs a flush of all three caches. -

Page 65: Table 4-6: Iccn Memory Size Register

MAX32665-MAX32668 User Guide Table 4-6: ICCn Memory Size Register ICCn Memory Size ICCn_MEM_SIZE [0x0004] Bits Field Access Reset Description 31:16 memsz Addressable Memory Size Indicates the size of addressable memory by this cache controller instance in 128KB units. 15:0 cchsz Cache Size Returns the size of the cache RAM memory in 1KB units. -

Page 66: External Ram Spixr Cache Controller (Srcc)

MAX32665-MAX32668 User Guide SFCC Cache ID SFCC_CACHE_ID [0x0000] Bits Field Access Reset Description relnum Cache Release Number Returns the release number for this Cache instance. Table 4-10: SFCC Memory Size Register SFCC Memory Size SFCC_MEM_SIZE [0x0004] Bits Field Access Reset... -

Page 67: Ram Memory Management

MAX32665-MAX32668 User Guide RAM Memory Management This device has many features for managing the on-chip RAM. The on-chip RAM includes data RAM, instruction and data caches, and peripheral FIFOs. 4.8.1 RAM Zeroization The GCR Memory Zeroize Register, GCR_MEM_ZERO, allows clearing memory for firmware or security reasons. Zeroization writes all zeros to the specified memory. -

Page 68: Miscellaneous Control Registers

MAX32665-MAX32668 User Guide 4.8.2.1 RAM LIGHTSLEEP RAM can be placed in a low power mode, referred to as LIGHTSLEEP, using the Memory Clock Control Register, GCR_MEM_CLK. LIGHTSLEEP gates off the clock to the RAM and makes the RAM unavailable for read/write operations, while memory contents are retained, reducing power consumption. -

Page 69: Table 4-16: Sqwout And Pdown Output Enable Register

MAX32665-MAX32668 User Guide Error Correction Coding Enable MCR_ECCEN [0x0000] Bits Field Access Reset Description Reserved Do not modify this field. sysram5eccen Sysram5 ECC Enable 0: Disable 1: Enable sysram4eccen Sysram4 ECC Enable 0: Disable 1: Enable sysram3eccen Sysram3 ECC Enable... -

Page 70: Table 4-18: Control Register

MAX32665-MAX32668 User Guide Comparator Enable MCR_AINCOMP [0x000C] Bits Field Access Reset Description aincomp3pd Comparator 3 Disable 0:Comparator is powered and enabled 1:Comparator is powered down and disabled aincomp2pd Comparator 2 Disable 0:Comparator is powered and enabled 1:Comparator is powered down and disabled... -

Page 71: Single Inductor Multiple Output (Simo) Power Supply

MAX32665-MAX32668 User Guide Control MCR_CTRL [0x0010] Bits Field Access Reset Description vddcsw Switch COREB VCOREB can be operated at a lower voltage to minimize leakage in any of the low power modes SLEEP, DEEPSLEEP, and BACKUP. Allows the CPU cores to operate from VCOREA during these low power modes. -

Page 72: Single Inductor Multiple Output (Simo) Registers

MAX32665-MAX32668 User Guide Domain Reset REGI Bluetooth transmitter POR TXOUT Bluetooth receiver POR RXOUT USB peripheral reset Power On GPIO pad held in reset until the voltage DDIO rises above threshold. Power On GPIO pad held in reset until the voltage DDIOH rises above threshold. -

Page 73: Single Inductor Multiple Output (Simo) Registers Details

MAX32665-MAX32668 User Guide Offset Register Name [0x004C] ZERO_CROSS_CAL_C Reserved Reserved. Do not modify this field. [0x0050] ZERO_CROSS_CAL_D Reserved Reserved. Do not modify this field. 4.13 Single Inductor Multiple Output (SIMO) Registers Details Table 4-21: Buck Voltage Regulator A Control Register... -

Page 74: Table 4-23: Buck Voltage Regulator C Control Register

MAX32665-MAX32668 User Guide Table 4-23: Buck Voltage Regulator C Control Register Buck Voltage Regulator A Control VREGO_C [0x000C] Bits Field Access Reset Description 31:8 Reserved Do not modify this field. rangec Regulator Output Range The voltage regulator output range setting. -

Page 75: Table 4-26: High Side Fet Peak Current Vrego_C Vrego_D Register

MAX32665-MAX32668 User Guide High Side FET Peak Current VREGO_A VREGO_B IPKA [0x0014] Bits Field Access Reset Description ipksetb 0x8h Reserved Reserved. Do not modify this field. ipkseta 0x8h Reserved Reserved. Do not modify this field. Table 4-26: High Side FET Peak Current VREGO_C VREGO_D Register... -

Page 76: Table 4-30: Buck Cycle Count Vrego_C Register

MAX32665-MAX32668 User Guide Table 4-30: Buck Cycle Count VREGO_C Register Buck Cycle Count VREGO_C ILOAD_C [0x0028] Bits Field Access Reset Description 31:8 Reserved Do not modify this field. iloadc Reserved Reserved. Do not modify this field. Table 4-31: Buck Cycle Count VREGO_D Register... -

Page 77: Table 4-35: Buck Cycle Count Alert Vrego_D Register

MAX32665-MAX32668 User Guide Table 4-35: Buck Cycle Count Alert VREGO_D Register Buck Cycle Count Alert VREGO_D BUCK_ALERT_THR_D [0x003C] Bits Field Access Reset Description 31:8 Reserved Do not modify this field. buckthrd Reserved Reserved. Do not modify this field. Table 4-36: Buck Regulator Output Ready Register... -

Page 78: Power Sequencer And Always-On Domain Registers

MAX32665-MAX32668 User Guide Table 4-38: Zero Cross Calibration VREGO_B Register Zero Cross Calibration VREGO_B ZERO_CROSS_CAL_B [0x0048] Bits Field Access Reset Description 31:5 Reserved Do not modify this field. zxcalb Reserved Reserved. Do not modify this field. Table 4-39: Zero Cross Calibration VREGO_C Register... -

Page 79: Power Sequencer And Always-On Domain Register Details

MAX32665-MAX32668 User Guide 4.15 Power Sequencer and Always-On Domain Register Details Table 4-42: Low Power Control Register Low Power Control PWRSEQ_LPCN [0x0000] Bits Field Access Reset Description Reserved Do not modify this field. pdowndslen PDOWN DEEPSLEEP Output Enable 0: Disabled... -

Page 80: Table 4-43: Gpio0 Low Power Wakeup Status Flags

MAX32665-MAX32668 User Guide Table 4-43: GPIO0 Low Power Wakeup Status Flags GPIO0 Low Power Wakeup Status Flags PWRSEQ_LPWKST0 [0x0004] Bits Field Access Reset Description 31:0 wakest0 R/W1C GPIO0 Pin Wakeup Status Flag Whenever a GPIO0 pin, in any power mode, transitions from low-to-high or high-to-low, the corresponding bit in this register is set. -

Page 81: Table 4-47: Peripheral Low Power Wakeup Status Flags

MAX32665-MAX32668 User Guide 17:0 Wakeen1 GPIO1 Pin Wakeup Interrupt Enable Write 1 to any bit to enable the corresponding pin on the 32-bit GPIO port to generate an interrupt to wakeup the device from any low power mode to ACTIVE mode. -

Page 82: Table 4-48: Peripheral Low Power Wakeup Enable Register

MAX32665-MAX32668 User Guide Peripheral Low Power Wakeup Status Flags PWRSEQ_LPPWST [0x0030] Bits Field Access Reset Description aincomp1wkst R/W1C Analog Input Comparator 1 Wakeup Status Flag This bit is set when the comparator inputs detect an event. Write 1 to clear. -

Page 83: Table 4-49: Ram Shutdown Control Register

MAX32665-MAX32668 User Guide Peripheral Low Power Wakeup Enable PWRSEQ_LPPWEN [0x0034] Bits Field Access Reset Description usbvbuswken USB VBUS State Change Wakeup Enable Write 1 to enable an interrupt and wakeup the device from any low power mode when PWRSEQ_LPPWST.usbvbuswkst = 1. -

Page 84: Table 4-50: Low Power Vdd Power Down Register

MAX32665-MAX32668 User Guide RAM Shutdown Control PWRSEQ_LPMEMSD [0x0040] Bits Field Access Reset Description Reserved Do not modify this field. sram5sd Sysram5 and Sysram11 Shut Down 0: Power enabled. 1: Power shut down. Affected memory is destroyed. Table 4-13 RAM Block Size and Base Address for base address and size information. -

Page 85: Global Control Registers (Gcr)

MAX32665-MAX32668 User Guide Low Power VDD Power Down PWRSEQ_LPVDDPD [0x0044] Bits Field Access Reset Description vdd4pd Reserved Reserved. Do not modify this field. vdd3pd Reserved Reserved. Do not modify this field. vdd2pd Reserved Reserved. Do not modify this field. Reserved Reserved. -

Page 86: Global Control Register Details (Gcr)

MAX32665-MAX32668 User Guide Offset Register Description [0x0040] GCR_SYS_STAT System Status Flags [0x0044] GCR_RST1 Reset Register 1 [0x0048] GCR_PCLK_DIS1 Peripheral Clocks Disable 1 [0x004C] GCR_EVENT_EN Event Enable Register [0x0050] GCR_REV Revision Register [0x0054] GCR_SYS_STAT_IE System Status Interrupt Enable [0x0064] GCR_ECC_ER Error Correction Coding Error Register... -

Page 87: Table 4-55: Reset Register 0

MAX32665-MAX32668 User Guide System Control GCR_SCON [0x0000] Bits Field Access Reset Description dcache_dis SPIXR Cache Controller (SRCC) Disable This disables the SRCC used for SPIXR code and data cache. Setting this field disables the cache and bypasses the cache line buffer. - Page 88 MAX32665-MAX32668 User Guide Reset 0 GCR_RST0 [0x0004] Bits Field Access Reset Description periph_rst Peripheral Reset Write 1 to reset. 0: Not in reset 1: Reset in progress. Note: Watchdog Timers, GPIO Ports, the AoD, RAM Retention and the General Control Registers (GCR) are unaffected.

- Page 89 MAX32665-MAX32668 User Guide Reset 0 GCR_RST0 [0x0004] Bits Field Access Reset Description spi2 SPI2 Reset Write 1 to reset. 0: Not in reset 1: Reset in progress. spi1 SPI1 Reset Write 1 to reset. 0: Not in reset 1: Reset in progress.

-

Page 90: Table 4-56: System Clock Control Register

MAX32665-MAX32668 User Guide Reset 0 GCR_RST0 [0x0004] Bits Field Access Reset Description gpio1 GPIO1 Reset Write 1 to reset. 0: Not in reset 1: Reset in progress. gpio1 GPIO1 Reset Write 1 to reset. 0: Not in reset 1: Reset in progress. - Page 91 MAX32665-MAX32668 User Guide System Clock Control GCR_CLK_CTRL [0x0008] Bits Field Access Reset Description hirc7m_vs 7.3728MHz Internal Oscillator Voltage Source Select In DEEPSLEEP the 7.3728MHz oscillator voltage is sourced by pin V . When exiting DEEPSLEEP the voltage is automatically switched back to this bit setting.

-

Page 92: Table 4-57: Power Management Register

MAX32665-MAX32668 User Guide System Clock Control GCR_CLK_CTRL [0x0008] Bits Field Access Reset Description 0b001000 Reserved Do not modify this field. Table 4-57: Power Management Register Power Management GCR_PMR 0x000C Bits Field Access Reset Description 31:21 Reserved Do not modify this field. -

Page 93: Table 4-58: Peripheral Clock Divisor Register

MAX32665-MAX32668 User Guide Power Management GCR_PMR 0x000C Bits Field Access Reset Description gpiowken GPIO Wakeup Enable Activity on any GPIO pin configured for wakeup causes an exit from SLEEP, DEEPSLEEP, and BACKUP modes. 0: Disabled. 1: Enabled. Reserved Do not modify this field. -

Page 94: Table 4-59: Peripheral Clock Disable Register 0

MAX32665-MAX32668 User Guide Table 4-59: Peripheral Clock Disable Register 0 Peripheral Clocks Disable 0 GCR_PCLK_DIS0 [0x0024] Bits Field Access Reset Description spixipm SPIXF Master Clock Disable Disabling a clock disables functionality while also saving power. Reads and writes to peripheral registers are disabled. Peripheral register states are retained. - Page 95 MAX32665-MAX32668 User Guide Peripheral Clocks Disable 0 GCR_PCLK_DIS0 [0x0024] Bits Field Access Reset Description timer2 TMR2 Clock Disable Disabling a clock disables functionality while also saving power. Reads and writes to peripheral registers are disabled. Peripheral register states are retained.

-

Page 96: Table 4-60: Memory Clock Control Register

MAX32665-MAX32668 User Guide Peripheral Clocks Disable 0 GCR_PCLK_DIS0 [0x0024] Bits Field Access Reset Description spi0 SPI0 Clock Disable Disabling a clock disables functionality while also saving power. Reads and writes to peripheral registers are disabled. Peripheral register states are retained. - Page 97 MAX32665-MAX32668 User Guide Memory Clock Control GCR_MEM_CLK [0x0028] Bits Field Access Reset Description usbls USB FIFO LIGHTSLEEP Enable Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained. 0: ACTIVE mode. 1: LIGHTSLEEP mode enabled. cryptols Crypto RAM LIGHTSLEEP Enable Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained.

-

Page 98: Table 4-61: Memory Zeroization Control Register

MAX32665-MAX32668 User Guide Memory Clock Control GCR_MEM_CLK [0x0028] Bits Field Access Reset Description sysram3ls Sysram3 LIGHTSLEEP Enable Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained. Table 4-13 RAM for base address and size information. 0: ACTIVE mode. - Page 99 MAX32665-MAX32668 User Guide Memory Zeroization Control GCR_MEM_ZERO [0x002C] Bits Field Access Reset Description usbfifoz USB FIFO Zeroization Write 1 to initiate the operation 0: Operation complete. 1: Operation in progress. cryptoz Crypto MAA Memory Zeroization Write 1 to initiate the operation.

-

Page 100: Table 4-62: System Status Flag Register

MAX32665-MAX32668 User Guide Memory Zeroization Control GCR_MEM_ZERO [0x002C] Bits Field Access Reset Description sram1z R/W1 Sysram1 Zeroization Write 1 to initiate the operation. 0: Operation complete. 1: Operation in progress. sram0z R/W1 Sysram0 Zeroization Write 1 to initiate the operation. - Page 101 MAX32665-MAX32668 User Guide Reset 1 GCR_RST1 [0x0044] Bits Field Access Reset Description htimer1 HTimer 1 Reset Write 1 to initiate the operation. 0: Operation complete. 1: Operation in progress. htimer0 HTimer 0 Reset Write 1 to initiate the operation. 0: Operation complete.

-

Page 102: Table 4-64: Peripheral Clock Disable Register 1

MAX32665-MAX32668 User Guide Reset 1 GCR_RST1 [0x0044] Bits Field Access Reset Description owire One-Wire Reset Write 1 to initiate the operation. 0: Operation complete. 1: Operation in progress. sdhc SDHC Reset Write 1 to initiate the operation. 0: Operation complete. - Page 103 MAX32665-MAX32668 User Guide Peripheral Clock Disable 1 GCR_PCLK_DIS1 [0x0048] Bits Field Access Reset Description wdt0 Watchdog Timer 0 Disable Disabling the clock disables functionality while also saving power. Associated register states are retained but read and write access is blocked.

- Page 104 MAX32665-MAX32668 User Guide Peripheral Clock Disable 1 GCR_PCLK_DIS1 [0x0048] Bits Field Access Reset Description One-Wire Clock Disable Disabling the clock disables functionality while also saving power. Associated register states are retained but read and write access is blocked. 0: Enabled.

-

Page 105: Table 4-65: Event Enable Register

MAX32665-MAX32668 User Guide Peripheral Clock Disable 1 GCR_PCLK_DIS1 [0x0048] Bits Field Access Reset Description btle Bluetooth Digital Baseband Clock Disable Disabling the clock disables functionality while also saving power. Associated register states are retained but read and write access is blocked. -

Page 106: Table 4-66: Revision Register

MAX32665-MAX32668 User Guide Table 4-66: Revision Register Revision GCR_REV [0x0050] Bits Field Access Reset Description 31:16 Reserved 15:0 revision Device Revision Returns the chip revision ID as a packed BCD. For example, 0xA1 would indicate the device is revision A1. -

Page 107: Table 4-69: Error Correction Not Double Error Detected Register

MAX32665-MAX32668 User Guide Error Correction Coding Error GCR_ECC_ER [0x0064] Bits Field Access Reset Description ic1eccerr R/W1C Instruction Cache 1 ECC Error Write to 1 to clear the flag. 0: No error 1: Error ic0eccerr R/W1C Instruction Cache 0 ECC Error Write to 1 to clear the flag. - Page 108 MAX32665-MAX32668 User Guide Error Correction Coding Not Double Error Detected GCR_ECC_NDED [0x0068] Bits Field Access Reset Description fl0eccnded R/W1C Flash0 Not Double ECC Error Detected When cleared, indicates that there is a single correctable error in the Flash0 bank. Write to 1 to clear the flag.

-

Page 109: Table 4-70: Error Correction Coding Interrupt Enable Register

MAX32665-MAX32668 User Guide Error Correction Coding Not Double Error Detected GCR_ECC_NDED [0x0068] Bits Field Access Reset Description sysram1eccnded R/W1C System RAM1 Not Double ECC Error Detected When cleared, indicates that there is a single correctable error in the RAM1 block. Write to 1 to clear the flag. -

Page 110: Table 4-71: Error Correction Coding Address Register

MAX32665-MAX32668 User Guide Table 4-71: Error Correction Coding Address Register Error Correction Coding Address GCR_ECC_ERRAD [0x0070] Bits Field Access Reset Description tagramerr ECC Error Address/TAG RAM Error Data depends on which block has reported the error. If sysram, fl0, or fl1, then this bit(s) represents the bit(s) of the AMBA address of read which produced the error. - Page 111 MAX32665-MAX32668 User Guide Bluetooth LDO Control GCR_BTLE_LDOCR [0x0074] Bits Field Access Reset Description ldotxendly LDOTX Enable Delay Not used. ldotxdisch LDOTX Discharge This bit is used to discharge the LDOTX output using a strong pulldown. For use when switching between Bypass Mode and Regulation Mode.

-

Page 112: Table 4-73: Bluetooth Ldo Delay Count Register

MAX32665-MAX32668 User Guide Table 4-73: Bluetooth LDO Delay Count Register Bluetooth LDO Delay Count GCR_BTLE_LDODCR [0x0078] Bits Field Access Reset Description 31:29 Reserved 28:20 ldotxdlycnt 0x01B Bluetooth LDOTX Delay Count Not used. 19:17 Reserved 16:8 ldorxdlycnt 0x01B Bluetooth LDORX Delay Count Not used. -

Page 113: Function Control Registers

MAX32665-MAX32668 User Guide Arm Peripheral Bus Asynchronous Bridge Select GCR_APB_ASYNC [0x0084] Bits Field Access Reset Description apbasyncI2C0 I2C0 Peripheral Bus Select The access for this peripheral can be performed via one of two different peripheral bus configurations. The system PCLK can be used as any of the other system peripherals that are connected to the APB PCLK domain or a 7.3728MHz... -

Page 114: Aes Key Registers

MAX32665-MAX32668 User Guide Function Control 0 GCR_FCR [0x0000] Bits Field Access Reset Description qspi0_fnc_sel QSPI0 Function Select 0: High speed 96MHz oscillator 1: External clock input Note: See the GPIO chapter for the external clock input pin usb_clk_sel USB Reference Clock Source Select This selects the clock source for the USB Hi-Speed Interface. -

Page 115: Interrupts And Exceptions

Interrupt Vector Table Table 5-1 lists the interrupt and exception table for the MAX32665—MAX32668. There are 95 interrupt entries for the MAX32665—MAX32668, including reserved for future use interrupt place holders. Including the 15 system exceptions for the Arm Cortex-M4 with FPU, the total number of entries is 110. - Page 116 MAX32665-MAX32668 User Guide Exception Offset Name Description (Interrupt) Number [0x0054] TMR0_IRQHandler Timer 0 Interrupt [0x0058] TMR1_IRQHandler Timer 1 Interrupt [0x005C] TMR2_IRQHandler Timer 2 Interrupt [0x0060] TMR3_IRQHandler Timer 3 Interrupt [0x0064] TMR4_IRQHandler Timer 4 Interrupt [0x0068] TMR5_IRQHandler Timer 5 Interrupt [0x006C]...

- Page 117 MAX32665-MAX32668 User Guide Exception Offset Name Description (Interrupt) Number [0x00D0] I2C1_IRQHandler I2C Port 1 Interrupt [0x00D4] Reserved [0x00D8] SPIXC_IRQHandler SPI XIP Interrupt [0x00DC] BTLE_TX_DONE_IRQHandler Bluetooth Transmitter Done Interrupt [0x00E0] BTLE_RX_RCVD_IRQHandler Bluetooth Receive Data Interrupt [0x00E4] BTLE_RX_ENG_DET_IRQHandler Bluetooth Receive Energy Detected...

- Page 118 MAX32665-MAX32668 User Guide Exception Offset Name Description (Interrupt) Number [0x0148] SDHC_IRQHandler SDHC Interrupt [0x014C] OWM_IRQHandler 1-Wire Master Interrupt [0x0150] DMA4_IRQHandler DMA4 Interrupt [0x0154] DMA5_IRQHandler DMA5 Interrupt [0x0158] DMA6_IRQHandler DMA6 Interrupt [0x015C] DMA7_IRQHandler DMA7 Interrupt [0x0160] DMA8_IRQHandler DMA8 Interrupt [0x0164] DMA9_IRQHandler...

-

Page 119: General-Purpose I/O And Alternate Function Pins (Gpio)

Table 6-1 shows the number of GPIO available on each IC package. Some packages and part numbers do not implement all bits of a 32-bit GPIO port. Register fields corresponding to unimplemented GPIO contain indeterminate values and should not be modified. Table 6-1: MAX32665—MAX32668 GPIO Pin Count PACKAGE GPIO... -

Page 120: Table 6-2: Max32665-Max32668 Gpio And Alternate Function Matrix, 140 Wlp

MAX32665-MAX32668 User Guide Table 6-2 shows the alternate functions mapped to each GPIO pin. Table 6-2: MAX32665—MAX32668 GPIO and Alternate Function Matrix, 140 WLP GPIO Port[pin] GPIO ALTERNATE ALTERNATE ALTERNATE ALTERNATE FUNCTION 1 FUNCTION 2 FUNCTION 3 FUNCTION 4 GPIO0[0] P0.0... -

Page 121: Table 6-3: Max32665-Max32668 Gpio Pin Configuration

Each device pin can be individually configured as a GPIO or an alternate function as shown in Table 6-3. The correct alternate function setting must be selected for each pin of a given multi-pin peripheral for proper operation. Table 6-3: MAX32665—MAX32668 GPIO Pin Configuration MODE GPIOn_EN0 GPIOn_EN1... -

Page 122: Table 6-5: Max32665-Max32668 Output Mode Configuration

Output Drive Strength 3, V Supply DDIOH Each GPIO port is assigned a dedicated interrupt vector as shown in the following table. Table 6-6: MAX32665—MAX32668 GPIO Port Interrupt Vector Mapping GPIO Interrupt Status Device Specific Interrupt GPIO Interrupt Source GPIO Interrupt Vector... -

Page 123: Usage

MAX32665-MAX32668 User Guide Usage 6.2.1 Reset State During a power-on-reset event, each GPIO is reset to the default input mode with the weak pullup resistor enabled as follows: • The GPIO Configuration Enable bits shown in Table 6-3 are set to I/O (transition to AF1) mode. -

Page 124: Gpio Interrupt Handling

A single wakeup interrupt vector, GPIOWAKE_IRQHandler, is assigned for all pins of all GPIO ports. When the GPIO wakeup event occurs, the application software must interrogate each GPIOn_INT_STAT register to determine which external port pin caused the wake-up event. Table 6-7: MAX32665―MAX32668 GPIO Wakeup Interrupt Vector GPIO Wake Interrupt GPIO Wake Interrupt Device Specific Interrupt GPIO Wakeup... -

Page 125: Registers

MAX32665-MAX32668 User Guide To enable low power mode wakeup (SLEEP, DEEPSLEEP and BACKUP) using an external GPIO interrupt, complete the following steps: 1. Clear pending interrupt flags by writing to GPIOn_INT_CLR[pin]. 2. Activate the GPIO wakeup function by writing 1 to GPIOn_WAKE_EN[pin]. -

Page 126: Register Details

31:0 GPIO Configuration Enable, Bit 0 This bit, in conjunction with bits in Table 6-3: MAX32665—MAX32668 GPIO Pin Configuration, configures the corresponding device pin for digital I/O or an alternate function modes. This field can be modified directly by writing to this register or... -

Page 127: Table 6-13: Gpio Port N Output Enable Atomic Set Register

MAX32665-MAX32668 User Guide Table 6-13: GPIO Port n Output Enable Atomic Set Register GPIO Port n Output Enable Atomic Set GPIOn_OUT_EN_SET [0x0010] Bits Field Access Reset Description 31:0 GPIO Output Enable Atomic Set Writing 1 to one or more bits sets the corresponding bits in GPIOn_OUT_EN. -

Page 128: Table 6-18: Gpio Port N Input Register

MAX32665-MAX32668 User Guide Table 6-18: GPIO Port n Input Register GPIO Port n Input GPIOn_IN [0x0024] Bits Field Access Reset Description 31:0 GPIO Input Returns the state of the input pin only if the corresponding bit in the GPIOn_IN_EN register is set. The state is not affected by the pin’s configuration as an output or alternate function. -

Page 129: Table 6-22: Gpio Port N Interrupt Enable Register

MAX32665-MAX32668 User Guide Table 6-22: GPIO Port n Interrupt Enable Register GPIO Port n Interrupt Enable GPIOn_INT_EN [0x0034] Bits Field Access Reset Description 31:0 GPIO Interrupt Enable Enable or disable the interrupt for the corresponding GPIO pin. 0: GPIO interrupt disabled. -

Page 130: Table 6-27: Gpio Port N Wakeup Enable Register

MAX32665-MAX32668 User Guide Table 6-27: GPIO Port n Wakeup Enable Register GPIO Port Wakeup Enable GPIOn_WAKE_EN [0x004C] Bits Field Access Reset Description 31:0 GPIO Wakeup Enable Enable the I/O as a wakeup from low power modes (SLEEP, DEEPSLEEP, BACKUP). 0: GPIO is not enabled as a wakeup source from low power modes. -

Page 131: Table 6-32: Gpio Port N Pullup Pulldown Selection 1 Register

Description 31:0 GPIO Configuration Enable, Bit 1 This bit, in conjunction with bits in Table 6-3: MAX32665—MAX32668 GPIO Pin Configuration, configures the corresponding device pin as a GPIO or an alternate function mode. Some GPIO are not implemented all devices. The bits associated with unimplemented GPIO should not be changed from their default value. -

Page 132: Table 6-36: Gpio Port N Configuration Enable Bit 2 Register

Description 31:0 GPIO Configuration Enable, Bit 2 This bit, in conjunction with bits in Table 6-3: MAX32665—MAX32668 GPIO Pin Configuration, configures the corresponding device pin as a GPIO or an alternate function mode. Some GPIO are not implemented all devices. The bits associated with unimplemented GPIO should not be changed from their default value. -

Page 133: Table 6-41: Gpion Pulldown/Pullup Strength Select Register

MAX32665-MAX32668 User Guide Table 6-41: GPIOn Pulldown/Pullup Strength Select Register GPIO Port Pulldown/Pullup Strength Select GPIOn_PS [0x00B8] Bits Field Access Reset Description 31:0 GPIO Pulldown/Pullup Strength Select Selects the strength of the pullup or pulldown resistor for a pin configured for input mode. -

Page 134: Flash Controller (Flc)

7-1, below, shows the start address and end address for each flash instance. The internal flash memory is mapped with a start address of 0x1000 0000 and an end address of 0x100F FFFF for a total of 1MB. Table 7-1: MAX32665—MAX32668 Internal Flash Memory Organization Instance... -

Page 135: Clock Configuration

MAX32665-MAX32668 User Guide 7.2.1 Clock Configuration The Flash Controller requires a 1MHz peripheral clock for operation. The input clock to the Flash Controller block is the system clock, f . Use the Flash Controller clock divisor to generate f = 1MHz, as shown in Equation 7-1 below. -

Page 136: Flash Write

MAX32665-MAX32668 User Guide 7.2.4 Flash Write Writes to a flash location are only successful if the targeted location is already in its erased state. Perform the following steps to write to a flash memory instance: 1. If desired, enable flash controller interrupts by setting the FLCn_INTR.access_error_ie and FLCn_INTR.done_ie bits. -

Page 137: Mass Erase

MAX32665-MAX32668 User Guide 7.2.6 Mass Erase CAUTION: Care must be taken to not erase the flash from which application code is currently executing. Mass erase clears the internal flash memory on an instance basis. Perform the following steps to mass erase a single flash memory instance: 1. -

Page 138: Flash Controller Register Details

MAX32665-MAX32668 User Guide Flash Controller Register Details Table 7-4: Flash Controller Address Pointer Register Flash Address Register FLCn_ADDR [0x0000] Bits Name Access Reset Description 31:0 addr Flash Address Description This field contains the target address for a write operation. A valid internal flash memory address is required for all write operations. -

Page 139: Table 7-7: Flash Controller Interrupt Register

MAX32665-MAX32668 User Guide Flash Controller Control Register FLCn_CTRL [0x0008] Bits Name Access Reset Description Reserved for Future Use Do not modify this field. page_erase R/W1O Page Erase Write a 1 to this field to initiate a page erase at the address in FLCn_ADDR.addr. -

Page 140: Table 7-8: Flash Controller Ecc Data Register

MAX32665-MAX32668 User Guide Flash Controller Interrupt Register FLCn_INTR [0x0024] Bits Name Access Reset Description access_fail R/W0C Flash Access Fail Interrupt Flag This bit is set when an attempt is made to write or erase the flash while the flash is busy or locked. Only hardware can set this bit to 1. Writing a 1 to this bit has no effect. -

Page 141: Table 7-12: Flash Controller Data Register 3

MAX32665-MAX32668 User Guide Table 7-12: Flash Controller Data Register 3 Flash Controller Data Register 3 FLCn_DATA3 [0x003C] Bits Name Access Reset Description 31:0 data3 Flash Data 3 Flash data for bits 127:96. Maxim Integrated Page 141 of 457... -

Page 142: External Memory

MAX32665-MAX32668 User Guide External Memory Overview External memory can be accessed via multiple interfaces. There are three external memory interfaces, two of which are backed by 16KB of cache: • SPI Execute-in-Place FLASH (SPIXF) 16KB dedicated cache • SPI Execute-in-Place RAM (SPIXR) ... -

Page 143: Spixf Master Controller

MAX32665-MAX32668 User Guide Figure 8-1. Simplified SPIXF Block Diagram ® ® ® ® Cortex Corte x CPU0 CPU1 SYSTEM BUS SPIXF CACHE CONTROLLER (SFCC) AHB2APB 16KB SYNC ÷ 2 INSTRUCTION CACHE BUS 0 ÷ 2 PCLK SYS_CLK APB 0 MEMORY DECRYPTION... -

Page 144: Figure 8-2. Simplified Block Diagram

MAX32665-MAX32668 User Guide data in the Transmit FIFO. At the end of every SPI transfer, data is moved from the shift register into the Receive FIFO. Status flags and interrupts are available to monitor the data levels in these FIFOs. -

Page 145: Table 8-1: Spi Header Format

MAX32665-MAX32668 User Guide The format of the header is shown in Table 8-1. If the transaction generates receive data, this data is pushed into the SPI. The Receive FIFO is SPIXFC_FIFO_RX. A complete access sequence to a SPI device is made up of one or more transactions. In some cases, the slave select signal remains asserted across several transactions. - Page 146 MAX32665-MAX32668 User Guide 8.2.1.1.3 Sample SPIXF Master Controller Example Here is an example how to set up the Master Controller: 1. Configure the SPIXF Master Controller mode, number of bytes per page (see SPIXFC_CFG.pgsz and Note below), SCK high and low values, and Slave Select (SS) active timing and inactive timing.

-

Page 147: Table 8-2: Clock Polarity And Phase Combinations

MAX32665-MAX32668 User Guide Multiple headers and payloads are written to the Transmit FIFO for consecutive execution. As an example, complete the following steps to set up the external SPI flash bus width using the SPIXF Master Controller: 1. Configure the SPIXF Master Controller so it can communicate with the default configuration of the external SPI flash chosen using the appropriate register and header settings. - Page 148 MAX32665-MAX32668 User Guide 8.2.1.1.6 Slave Select Transaction Delay Configuration The transaction delay and slave select timing with respect to the active or inactive slave select edge are determined by a combination of the following register fields: • SPIXFC_CFG.ssact • SPIXFC_CFG.ssiact •...

-

Page 149: Figure 8-3. Spixfc Transaction Delay

MAX32665-MAX32668 User Guide Figure 8-3. SPIXFC Transaction Delay SPIXFC MODE 0 SPIXFC_CFG.ssact SPIXFC_CFG.hiclk SPIXFC_CFG.ssact SPIXFC_CFG.loclk SPIXFC_CFG.loclk SPIXFC_CFG.inact An extra pulse is provided at the end of this transaction to SPIXFC MODE 3, SPIXFC_SP_CTRL.sckinh3 = 0 comp ly with some SPI f la sh timing d iag ra ms, an d allow f or higher speeds during SPI READ t ransactions. -

Page 150: Table 8-3: Encrypted Data Write Order To Spix Flash Memory

MAX32665-MAX32668 User Guide 8.2.1.1.7 Slave Select The SPIXF Master Controller operates with one slave device. A dedicated select pin for slave #0 is provided and controlled by hardware. Both execute-in-place and data storage are supported on slave #0. 8.2.1.1.8 Interrupts Interrupt logic is provided to allow efficient servicing of the SPIXF Master Controller by firmware. -

Page 151: Table 8-4. Spixf Master Controller Register Offsets, Names, Access And Description

MAX32665-MAX32668 User Guide 8.2.1.2 SPIXF Master Controller Registers Table 3-1: APB Peripheral Base Address Map for the SPIXF Peripheral Base Offset Address. Table 8-4. SPIXF Master Controller Register Offsets, Names, Access and Description Offset Register Access Description [0x0000] SPIXFC_CFG SPIXF Controller Configuration Register... -

Page 152: Table 8-6. Spixf Controller Slave Select Polarity Register

MAX32665-MAX32668 User Guide SPIXF Controller Configuration Register SPIXFC_CFG [0x0000] Bits Name Access Reset Description 15:12 loclk SCK Low Clocks Number of system clocks that SCK is held low when SCK pulses are generated 0: 16 system clocks 1: 1 system clock... -

Page 153: Table 8-7. Spixf Controller General Control Register

MAX32665-MAX32668 User Guide Table 8-7. SPIXF Controller General Control Register SPIXF Controller General Control Register SPIXFC_GEN_CTRL [0x0008] Bits Name Access Reset Description 31:26 Reserved for Future Use Do not modify this field. sckfbinv SCK Inversion 0: Use SCK as feedback clock... -

Page 154: Table 8-8. Spixf Controller Fifo Control And Status Register

MAX32665-MAX32668 User Guide SPIXF Controller General Control Register SPIXFC_GEN_CTRL [0x0008] Bits Name Access Reset Description sckdr SCK Drive and State This bit reflects the state of the SCK. When in Bit-Bang mode (SPIXFC_GEN_CTRL.bbmode = 1), this bit is written to control the output state of the SCK. -

Page 155: Table 8-9. Spixf Controller Special Control Register

MAX32665-MAX32668 User Guide SPIXF Controller FIFO Control and Status Register SPIXFC_FIFO_CTRL [0x000C] Bits Name Access Reset Description 20:16 rfifolvl Receive FIFO Almost Full Level The Almost Full flag is asserted when the number of used FIFO entries (bytes) exceed this value. FIFO depth is 32 bytes. -

Page 156: Table 8-10. Spixf Controller Interrupt Status Register

MAX32665-MAX32668 User Guide SPIXF Controller Special Control Register SPIXFC_SP_CTRL [0x0010] Bits Name Access Reset Description Reserved for Future Use Do not modify this field sampl SDIO Sample Mode Enable Setting this bit to a 1 enables the ability to drive SDIO outputs prior to the assertion of Slave Select. -

Page 157: Table 8-11. Spixf Controller Interrupt Enable Register

MAX32665-MAX32668 User Guide SPIXF Controller Interrupt Status Register SPIXFC_INT_FL [0x0014] Bits Name Access Reset Description tstall R/W1C Transmit Stalled Interrupt Flag. This flag is set by hardware when the Transmit FIFO is empty, and the selected slave select is asserted. -

Page 158: Spixf Master

MAX32665-MAX32668 User Guide 8.2.1.4 SPIXF Master Controller FIFO Registers Table 3-2: AHB Peripheral Base Address Map for the SPIXF Master Controller FIFO Peripheral Base Address. Table 8-12. SPIXF Master Controller FIFO Register Offsets, Names, Access and Description Offset Register Access... -

Page 159: Figure 8-4. Supported Spi Configuration

MAX32665-MAX32668 User Guide 8.2.2.1 SPIXF Pin Configuration The SPIXF Master and SPIXF Master Controller use a highly-configurable, flexible, and efficient interface supporting single, dual, or quad I/O. Dedicated pins are provided to support high-speed communication. The following pin configurations are supported and shown in Figure 8-4: •... -

Page 160: Figure 8-5. Spixfm Delay Configuration

MAX32665-MAX32668 User Guide causes the slave select to de-assert. The SPIXF block requires reconfiguration prior to subsequent access to external SPI flash space either for execution or data reads. Figure 8-5. SPIXFM Delay Configuration SPIXFM MODE 0 SPIXFM_CFG.ssact SPIXFM_CFG.hiclk SPIXFM_CFG.ssact Several clocks (min 3) SPIXFM_CFG.loclk... - Page 161 MAX32665-MAX32668 User Guide 8.2.2.4 Sample SPIXFM Master Configuration - Execute Code Complete the following steps to execute the SPIXFM Master Configuration sample: 1. Turn on ICache XIP Clock (GCR_PCLK_DIS1.icachexipf = 1). The cache can be put into different power states. See GCR_MEM_CLK for options.

-

Page 162: Table 8-15. Spixfm Master Register Offsets, Names, Access And Description

MAX32665-MAX32668 User Guide SPIXFM slave select is low, the user must not be executing from SPIXFM space, and the SPIXF block should be reset by setting GCR_RST1.spixip = 1. 8.2.2.7 External SPI Flash Decryption If data in the SPI flash is encrypted when written, it might be transparently decrypted on read back using either code execution or data reads. -

Page 163: Table 8-17. Spixfm Fetch Control Register

MAX32665-MAX32668 User Guide SPIXFM Configuration Register SPIXFM_CFG [0x0000] Bits Name Access Reset Description 17:16 ssact Slave Select Active Timing Controls delay from assertion of slave select to start of the SCK pulse and delay from the end of SCK pulses to de-assertion of slave select. See 8.2.1.1.6, above, for details on slave select transaction delay configuration. -

Page 164: Table 8-18. Spixfm Mode Control Register

MAX32665-MAX32668 User Guide SPIXFM Fetch Control Register SPIXFM_FETCH_CTRL [0x0004] Bits Name Access Reset Description 15:14 Reserved for Future Use Do not modify this field. 13:12 data_width Data Width Number of data I/O used to receive data. 0b00: Single SDIO 0b01: Dual SDIO... -

Page 165: Table 8-19. Spixfm Mode Data Register

MAX32665-MAX32668 User Guide SPIXFM Mode Control Register SPIXFM_MODE_CTRL [0x0008] Bits Name Access Reset Description mdclk Mode Clocks Number of SPI clocks needed during the mode/dummy phase of fetch. Table 8-19. SPIXFM Mode Data Register SPIXFM Mode Data Register SPIXFM_MODE_DATA [0x000C]... -

Page 166: Table 8-22. Spixfm Memory Security Control Register

MAX32665-MAX32668 User Guide SPIXFM I/O Control Register SPIXFM_IO_CTRL [0x001C] Bits Name Access Reset Description ss_ds Slave Select Drive Strength This bit controls the drive strength on the dedicated slave select pin. 0: Low Drive Strength. 1: Hi Drive Strength. sck_ds SCK Drive Strength This bit controls the drive strength on the SCK pin. -

Page 167: Spi Execute-In-Place Ram (Spixr)

MAX32665-MAX32668 User Guide SPI Execute-in-Place RAM (SPIXR) The SPI Execute-in-Place RAM Master Controller (SPIXR) is an instantiation of the Quad SPI Interface with the following features: • Four SPI modes (mode 0, 1, 2, and 3) • Master mode only support •... -

Page 168: Spixr Master Controller Registers

MAX32665-MAX32668 User Guide Figure 8-6. Simplified SPIXR Block Diagram ® ® ® ® Cortex Cortex CPU0 CPU1 AHB SYSTEM B US SPIXR CACHE CONTROLLER (SRCC) 16KB EXTERNAL SPI RAM MEMORY CACHE LINE BUFFER GCR_SCON dcache_dis SPIXR CACHE BYPAS S SPIXR... -

Page 169: Spixr Register Details

MAX32665-MAX32668 User Guide Offset Register Access Description [0x0030] SPIXR_STAT SPIXR Active Status Register [0x0034] SPIXR_XMEM_CTRL SPIXR XMEM Control Register 8.3.2 SPIXR Register Details Table 8-25. SPIXR FIFO Data Register SPIXR FIFO Data Register SPIXR_DATA [0x0000] Bits Name Access Reset Description... -

Page 170: Table 8-27. Spixr Transmit Packet Size Register

MAX32665-MAX32668 User Guide SPIXR Master Signals Control Register SPIXR_CTRL1 [0x0004] Bits Name Access Reset Description ss_io Master Slave Select Signal Direction This field must be set to 0 for SPIXR operation. 0: Slave Select is an output Note: The SPIXR only operates as a SPI master in single master mode. Writing 1 to this field is invalid. -

Page 171: Table 8-29. Spixr Slave Select Timing Register

MAX32665-MAX32668 User Guide SPIXR Static Configuration Register SPIXR_CTRL3 [0x000C] Bits Name Access Reset Description Reserved for Future Use Do not modify this field. 13:12 data_width SPIXR Data Width Sets the number of data lines (SDIO pins) for communication. 0: 1-data pin (Single Mode) -

Page 172: Table 8-30. Spixr Master Baud Rate Generator

MAX32665-MAX32668 User Guide SPIXR Slave Select Timing Register SPIXR_SS_TIME [0x0010] Bits Name Access Reset Description 15:8 ssact2 Slave Select Active After Last SCK Number of system clock cycles that SS is active from the last SCK edge to when SS is inactive. -

Page 173: Table 8-31. Spixr Dma Control Register

MAX32665-MAX32668 User Guide SPIXR Master Baud Rate Generator Register SPIXR_BRG_CTRL [0x0014] Bits Name Access Reset Description SCK Low Clock Cycles Control Setting this field to 0 disables the low duty cycle control for SCK. Setting this field to any non-zero value sets the high cycle time to: SCK_LOW = lo ×... -

Page 174: Table 8-32. Spixr Interrupt Status Flag Register

MAX32665-MAX32668 User Guide SPIXR DMA Control Register SPIXR_DMA [0x001C] Bits Name Access Reset Description tx_fifo_clear Clear the TX FIFO Set this field to 1 to clear the TX FIFO and all TX FIFO related flags in the SPIXR_INT_FL register. When the TX FIFO is cleared, the SPIXR_INT_FL.tx_fifo_empty flag is set by hardware. -

Page 175: Table 8-33. Spixr Interrupt Enable Register

MAX32665-MAX32668 User Guide SPIXR Interrupt Status Flag Register SPIXR_INT_FL [0x0020] Bits Name Access Reset Description fault R/W1C Multi-Master Fault Flag Set if the SPI is in Master Mode, Multi-Master Mode is enabled, and a Slave Select input is asserted. A collision also sets this flag. -

Page 176: Table 8-34. Spixr Wakeup Flag Register

MAX32665-MAX32668 User Guide SPIXR Interrupt Enable Register SPIXR_INT_EN [0x0024] Bits Name Access Reset Description fault Multi-Master Fault Interrupt Enable 1: Interrupt enabled 0: Interrupt disabled Reserved for Future Use 1: Interrupt enabled 0: Interrupt disabled Slave Select Deasserted Interrupt Enable... -

Page 177: Table 8-35. Spixr Wakeup Enable Register

MAX32665-MAX32668 User Guide Table 8-35. SPIXR Wakeup Enable Register SPIXR Wakeup Enable Register SPIXR_WAKE_EN [0x002C] Bits Name Access Reset Description 31:4 Reserved for Future Use Do not modify this field. rx_full Wake on RX FIFO Full Enable Set to 1 to wake up the device when this RX FIFO is full. -

Page 178: Spixr Cache Controller (Srcc)

SPI-XiP RAM device. The SRCC includes tag RAM, cache RAM and a line fill buffer as shown in Figure 4-6: MAX32665—MAX32668 Cache Controllers Control. Write allocate and critical word first are options controlled by the application. Each cache line is 256-bits wide with the lower 5-bits of the address used as the cache line index. -

Page 179: Srcc Registers

MAX32665-MAX32668 User Guide 8.4.4 SRCC Registers Table 3-1: APB Peripheral Base Address Map for the SRCC Peripheral Base Address. Table 8-38: External Memory Cache Controller Register Addresses and Descriptions Offset Register Name Access Description [0x0000] SRCC_CACHE_ID Cache ID Register [0x0004]... -

Page 180: Table 8-42: Srcc Invalidate Register

MAX32665-MAX32668 User Guide SRCC Cache Control Register SRCC_CACHE_CTRL [0x0100] Bits Name Access Reset Description 15:3 Reserved for Future Use Do not modify this field. cwfst_dis Critical Word First (CWF) Disable Setting this field to 1 disables Critical Word First operation. When CWF is disabled, the cache fills the cache line before sending the data to the Arm Cortex core. -

Page 181: Secure Digital Host Controller

Details of the SD communication and protocol are not part of the scope of this document. The MAX32665—MAX32668 SDHC only supports a single SD card. SD memory card and SDIO card specifications are available at https://www.sdcard.org. -

Page 182: Instances

8.5.1 Instances The SDHC pin mapping for the SD Host Controller Standard Specification Version 3.0 are shown in Table 8-43, below. Table 8-43: MAX32665—MAX32668 SDHC Alternate Function Mapping to SDHC Specification Pin Names SDHC Alternate Function Specification Alternate Function Number... -

Page 183: Sdhc Peripheral Clock Selection

MAX32665-MAX32668 User Guide SDHC Alternate Function Specification Alternate Function Number Pin Name Pin Name Direction Signal Description SDHC_DAT3 P1.0 DAT[3] SD data bus bit 3. For configuration of the GPIO for SDHC peripheral usage see the General-Purpose I/O and Alternate Function Pins chapter. -

Page 184: Sd Command Generation

MAX32665-MAX32668 User Guide Figure 8-9: SD Bus Protocol - Multi-Block Read Operation Figure 8-10: SD Bus Protocol - Multi Block Write Operation 8.5.4 SD Command Generation Table 8-44 shows the registers required for three transaction types: SDMA generated transactions, ADMA generated transactions, and CPU transactions (includes data transfers and Non-DAT transfers). -

Page 185: Sdhc Registers

MAX32665-MAX32668 User Guide Register SDMA Command ADMA Command CPU Data Transfer Non-DAT (No Data) Transfer Argument 2 No (Protected) SDHC_SDMA Command SDHC_CMD 8.5.5 SDHC Registers Table 3-1: APB Peripheral Base Address Map for the SDHC Peripheral Base Address Table 8-45: SDHC Register Offsets, Names and Descriptions... -

Page 186: Sdhc Register Details

MAX32665-MAX32668 User Guide Offset Register Name Description [0x0050] SDHC_FORCE_CMD Force Event Register for Auto CMD Error Status [0x0052] SDHC_FORCE_EVENT_INT_STAT Force Event Register for Error Interrupt Status [0x0054] SDHC_ADMA_ER ADMA Error Status register [0x0058] SDHC_ADMA_ADDR_0 ADMA System Address register 0 [0x005C]... -

Page 187: Table 8-47: Sdhc Sdma Block Size Register

MAX32665-MAX32668 User Guide Table 8-47: SDHC SDMA Block Size Register SDMA Block Size Register SDHC_BLK_SIZE [0x0004] Bits Name Access Reset Description 31:15 Reserved for Future Use Do not modify this field. 14:12 host_buf Host SDMA Buffer Size This field specifies the size of the contiguous buffer in the system memory for SDMA transfers. -

Page 188: Table 8-48: Sdhc Sdma Block Count Register

MAX32665-MAX32668 User Guide Table 8-48: SDHC SDMA Block Count Register SDMA Block Count Register SDHC_BLK_CNT [0x0006] Bits Name Access Reset Description 31:16 Reserved for Future Use Do not modify this field. 15:0 trans 0x0200 Current Transfer Block Count Set to the total number of blocks to transfer prior to a block transfer operation. Set the Block Count Enable (SDHC_TRANS.blk_cnt_en) bit to 1 for a block transfer. - Page 189 MAX32665-MAX32668 User Guide SDMA Transfer Mode Register SDHC_TRANS [0x000C] Bits Name Access Reset Description read_write Data Transfer Direction Select Sets the direction for DAT line data transfers. Set to 1 to transfer data from the SD card to the SDHC (Read). For all other commands, set this bit to 0 (Write).

-

Page 190: Table 8-51: Summary Of How Register Settings Determine Type Of Data Transfer

MAX32665-MAX32668 User Guide Table 8-51: Summary of how register settings determine type of data transfer Multi/Single Block Select Block Count Enable Block Count Function SDHC_TRANS.multi SDHC_TRANS.blk_cnt_en SDHC_BLK_CNT.trans N.A. N.A. Single transfer N.A. Infinite transfer ≠0 Multiple transfer Stop Multiple transfer... -

Page 191: Table 8-53: Relationship Between Parameters And The Name Of Response Type

Table 8-62 shows the mapping from the Response Registers to the SD Host Controller Standard Specification REP[127:0] notation for the MAX32665—MAX32668. Table 8-63 shows the SD types of response mapped to the MAX32665—MAX32668 Response registers. Maxim Integrated Page 191 of 457... -

Page 192: Table 8-57: Sdhc Response 3 Register

MAX32665-MAX32668 User Guide Table 8-57: SDHC Response 3 Register Response 3 Register SDHC_RESP_3 [0x0016] Bits Name Access Reset Description 15:0 cmd_resp Response Register 3 Response 7 to Response 0 registers are referenced as a contiguous, single register in the SD Host Controller Spec V3.0. -

Page 193: Table 8-61: Sdhc Response 7 Register

MAX32665-MAX32668 User Guide Table 8-61: SDHC Response 7 Register Response 7 Register SDHC_RESP_7 [0x001E] Bits Name Access Reset Description 15:0 cmd_resp Response Register 7 Response 7 to Response 0 registers are referenced as a contiguous, single register in the SD Host Controller Spec V3.0. - Page 194 MAX32665-MAX32668 User Guide Present State Register SDHC_PRESENT [0x0024] Bits Name Access Reset Description 23:20 dat_signal_level SDHC_DAT[3:0] Line Signal Level Indicates the DAT line level for error recovery and debugging. Use to detect the busy signal level as indicated on SDHC_DAT[0].

- Page 195 MAX32665-MAX32668 User Guide Present State Register SDHC_PRESENT [0x0024] Bits Name Access Reset Description read_transfer Read Transfer Active Indicates completion of a read transfer. This bit is set to 1 for either of the following conditions: 1) After the end bit of a Read command.

-

Page 196: Table 8-66: Sdhc Host Control 1 Register

1. 1: Card Inserted 0: No card inserted ext_data_transfer_width Extended Data Transfer Width Extended data transfer width is not supported on the MAX32665—MAX32668. Always reads 0. 0: Bus width is selected by SHDC_HOST_CN_1.data_transfer_width field dma_select DMA Select Sets the DMA mode. -

Page 197: Table 8-67: Sdhc Power Control Register