Nuvoton NuMicro Series Technical Reference Manual

8-bit microcontroller

Hide thumbs

Also See for NuMicro Series:

- User manual (53 pages) ,

- Quick start manual (15 pages) ,

- User manual (41 pages)

Table of Contents

Advertisement

ML51

1T 8051

8-bit Microcontroller

®

NuMicro

Family

ML51 Series

Technical Reference Manual

The information described in this document is the exclusive intellectual property of

Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

®

Nuvoton is providing this document only for reference purposes of NuMicro

microcontroller based

system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

Dec. 05, 2018

Page 1 of 401

Rev 1.00

Advertisement

Table of Contents

Summary of Contents for Nuvoton NuMicro Series

- Page 1 ML51 Series Technical Reference Manual The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. ® Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design.

-

Page 2: Table Of Contents

ML51 TABLE OF CONTENTS 1 GENERAL DESCRIPTION................12 2 FEATURES ....................14 3 PART INFORMATION ................... 17 3.1 ML51 Series Selection Guide ..................17 3.2 ML51 Series Selection Code ..................18 4 PIN CONFIGURATION .................. 19 4.1 Pin Configuration ......................19 4.1.1 ML51 Series Pin Diagram ..................... - Page 3 ML51 9.6.7 Pull-Down Resister Control ..................168 10 TIMER/COUNTER 0 AND 1 ................. 170 10.1 Mode 0 (13-Bit Timer) ..................174 10.2 Mode 1 (16-Bit Timer) ..................175 10.3 Mode 2 (8-Bit Auto-Reload Timer) ..............175 10.4 Mode 3 (Two Separate 8-Bit Timers) ..............176 11 TIMER 2 AND INPUT CAPTURE ..............

- Page 4 ML51 17 SERIAL PERIPHERAL INTERFACE (SPI) ..........231 17.1 Functional Description ..................231 17.2 SPI Protocol Registers ..................234 17.3 Operating Modes ....................240 17.3.1 Master Mode ......................... 240 17.3.2 Slave Mode........................240 17.4 Clock Formats and Data Transfer ..............240 17.5 Slave Select Pin Configuration ................

- Page 5 ML51 21.1 Functional Description ..................293 21.1.1 ADC Operation ......................293 21.1.2 ADC Conversion Triggered by External Source ............295 21.1.3 ADC Conversion Result Comparator................. 295 21.1.4 ADC Continues Conversion ..................296 21.2 Control Registers of ADC ................... 297 22 VOLTAGE REFERENCE ................304 23 ANALOG COMPARATOR CONTROLLER (ACMP) ........

- Page 6 ML51 28.2 Low Power Run Mode ..................354 28.3 Low Power Idle Mode ..................354 28.4 Power-Down Mode ....................354 29 CLOCK SYSTEM ..................355 29.1 System Clock Sources ..................355 29.1.1 Internal Oscillators ......................355 29.1.2 External Crystal/Resonator or Clock Input ............... 356 29.2 System Clock Switching ..................

- Page 7 ML51 37 PACKAGE DIMENSIONS ................390 37.1 LQFP 48 (7x7x1.4 mm) ..................390 37.2 QFN 33 (4x4x0.8 mm) ..................391 37.3 LQFP 32 (7x7x1.4 mm) ..................392 37.4 TSSOP 28 (4.4x9.7x1.0 mm) ................393 37.5 SOP 28 (300 mil) ....................394 37.6 TSSOP 20 (3.0X3.0 mm) ..................

- Page 8 ML51 LIST OF FIGURES Figure 4.1-1 Pin Assignment of QFN-33 Package ................ 19 Figure 4.1-2 Pin Assignment of LQFP-32 Package ..............20 Figure 4.1-3 Pin Assignment of TSSOP-28 Package ..............20 Figure 4.1-4 Pin Assignment of SOP-28 Package ................ 21 Figure 4.1-5 Pin Assignment of TSSOP-20 Package ..............

- Page 9 ML51 Figure 13.2-1 Self Wake-Up Timer Block Diagram ..............196 Figure 15.1-1 Serial Port Mode 0 Timing Diagram ..............199 Figure 15.2-1 Serial Port Mode 1 Timing Diagram ..............200 Figure 15.3-1 Serial Port Mode 2 and 3 Timing Diagram ............201 Figure 16.1-1 SC Controller Block Diagram .................

- Page 10 ML51 Figure 20.1-4 PWM Center-aligned Type Waveform ..............283 Figure 20.1-5 PWM Complementary Mode with Dead-time Insertion ........285 Figure 20.1-6 Fault Brake Function Block Diagram ..............288 Figure 20.2-1 PWM Interrupt Type....................292 Figure 21.1-1 12-bit ADC Block Diagram ..................293 Figure 21.1-2 External Triggering ADC Circuit ................

- Page 11 ML51 List of Tables Table 7.1-1 Special Function Register (SFR) Memory Map ............45 Table 7.1-2 SFR Definitions And Reset Values ................47 Table 7.2-1 Instructions That Affect Flag Settings ..............154 Table 7.2-1 Configuration for Different I/O Modes ............... 156 Table 11.4-1 Watchdog Timer-out Interval Under Different Pre-scalars........

-

Page 12: General Description

ML51 GENERAL DESCRIPTION The ML51 is a Flash embedded 1T 8051-based microcontroller. The instruction set of the ML51 is fully compatible with the standard 80C51 with performance enhanced. The ML51 runs up to 24 MHz at a wide voltage range from 1.8V to 5.5V, and contains up to 64/32/16 Kbytes Flash called APROM for programming code. - Page 13 ML51 Through the high performance of 1T 8051 core, low power performance of ML51 and rich well- designed peripherals, the ML51 benefits for low-power, battery powered devices, general purpose, home appliances, or motor control system. Dec. 05, 2018 Page 13 of 401 Rev 1.00...

-

Page 14: Features

ML51 FEATURES CPU: – Fully static design 8-bit high performance 1T 8051-based CMOS microcontroller. – Instruction set fully compatible with MCS-51. – 4-priority-level interrupts capability. – Dual Data Pointers (DPTRs). Operating: – Wide supply voltage from 1.8 V to 5.5 V. –... - Page 15 ML51 – Peripheral-to-memory and memory-to-peripheral mode: transfer data width byte alignment. Clock sources: – 24 MHz high-speed internal oscillator (HIRC) trimmed to ±1% (accuracy at 25 ℃, 3.3 V), ±5% in all conditions. – 38.4 kHz low-speed internal oscillator (LIRC) calibrating to ±1% by software from high-speed internal oscillator (HIRC) or external crystal (HXT).

- Page 16 – EFT > ± 4.4 KV – Latch-up pass 150 mA Development Tools: – Nuvoton Nu-Link with KEIL and IAR development environment. – Nuvoton In-Circuit-Programmer (Nu-Link). – Nuvoton In-System-Programming (ISP) via UART. Dec. 05, 2018 Page 16 of 401 Rev 1.00...

-

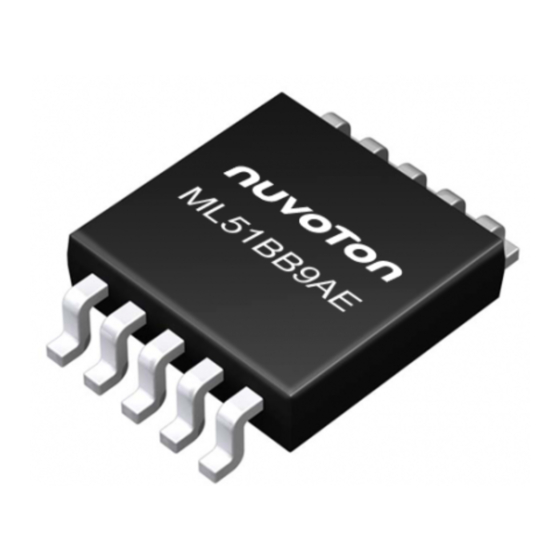

Page 17: Part Information

ML51 PART INFORMATION 3.1 ML51 Series Selection Guide Connectivity Part Number ML51BB9AE 2-ch MSOP10 ML51DB9AE 3-ch TSSOP14 ML51FB9AE 6-ch TSSOP20 ML51OB9AE 6-ch SOP20 ML51XB9AE 6-ch QFN20 ML51EB9AE 8-ch TSSOP28 ML51UB9AE 8-ch SOP28 ML51PB9AE 8-ch LQFP32 ML51TB9AE 8-ch QFN33 ML51EC0AE 8-ch TSSOP28 ML51UC0AE 8-ch... -

Page 18: 3.2 Ml51 Series Selection Code

ML51 3.2 ML51 Series Selection Code Dec. 05, 2018 Page 18 of 401 Rev 1.00... -

Page 19: Pin Configuration

Users can find pin configuaration informations in chapter 3 or by using NuTool - PinConfigure. The ® NuTool - PinConfigure contains all Nuvoton NuMicro Family chip series with all part number, and helps users configure GPIO multi-function correctly and handily. 4.1.1 ML51 Series Pin Diagram 4.1.1.1... -

Page 20: Figure 4.1-2 Pin Assignment Of Lqfp-32 Package

ML51 4.1.1.2 LQFP32 Package Corresponding Part Number: ML51PD1AE / ML51PC0AE / ML51PB9AE nRESET P4.6 P5.6 P0.0 LQFP32 P3.3 ML51PD1AE P0.1 ML51PC0AE P3.2 P0.2 ML51PB9AE P3.1 P0.3 P3.0 P5.2 P5.3 Figure 4.1-2 Pin Assignment of LQFP-32 Package 4.1.1.3 TSSOP28 Package Corresponding Part Number: ML51EC0AE / ML51EB9AE P4.0 P1.4 P4.1... -

Page 21: Figure 4.1-4 Pin Assignment Of Sop-28 Package

ML51 Corresponding Part Number: ML51UC0AE / ML51UB9AE P4.0 P1.4 P4.1 P1.5 P5.1 P1.6 P5.0 P1.7 nRESET P0.0 P4.6 P0.1 P0.2 P3.2 P0.3 P3.1 P5.2 P3.0 P5.3 P2.0 P2.5 P2.1 P2.4 P2.2 P2.3 Figure 4.1-4 Pin Assignment of SOP-28 Package 4.1.1.5 TSSOP20 Package Corresponding Part Number: ML51FB9AE P5.1... -

Page 22: Figure 4.1-6 Pin Assignment Of Tssop-20 Package

ML51 4.1.1.6 SOP20 Package Corresponding Part Number: ML51OB9AE P5.1 P4.6 P5.0 nRESET P3.2 P0.0 P3.1 P0.1 P3.0 P0.2 P0.3 P2.5 P5.2 P2.4 P5.3 P2.3 P2.2 Figure 4.1-6 Pin Assignment of TSSOP-20 Package 4.1.1.7 QFN20 Package Corresponding Part Number: ML51XB9AE 15 14 13 12 11 nRESET P0.0 P4.6... -

Page 23: Figure 4.1-8 Pin Assignment Of Tssop-14 Package

ML51 4.1.1.8 TSSOP14 Package Corresponding Part Number: ML51DB9AE P5.1 P4.6 P5.0 nRESET TSSOP14 P3.1 P0.2 ML51DB9AE P3.0 P0.3 P2.5 P5.2 P2.4 P5.3 Figure 4.1-8 Pin Assignment of TSSOP-14 Package 4.1.1.9 MSOP10 Package Corresponding Part Number: ML51BB9AE P5.0 P5.1 nRESET MSOP10 P0.0 P4.6 ML51BB9AE... -

Page 24: Ml51 Series Multi Function Pin Diagram

ML51 4.1.2 ML51 Series Multi Function Pin Diagram 4.1.2.1 QFN33 Package Corresponding Part Number: ML51TC0AE / ML51TB9AE nRESET Top transparent view INT0 / CLKO / TM0 / PWM0_CH0 / PWM1_BRAKE / P4.6 P5.6 / PWM0_BRAKE / PWM0_CH1 / CLKO QFN33 P0.0 / SPI0_MOSI / SPI1_MOSI / UART0_RXD / PWM0_CH5 PWM0_BRAKE / TM2_EXT0 / PWM1_CH0 / SPI1_SS / P3.3 P0.1 / SPI0_MISO / SPI1_MISO / UART0_TXD / PWM0_CH4... -

Page 25: Figure 4.1-11 Multi Function Pin Assignment Of Lqfp-32 Package

ML51 4.1.2.2 LQFP32 Package Corresponding Part Number: ML51PD1AE / ML51PC0AE / ML51PB9AE nRESET INT0 / CLKO / TM0 / PWM0_CH0 / PWM1_BRAKE / P4.6 P5.6 / PWM0_BRAKE / PWM0_CH1 / CLKO P0.0 / SPI0_MOSI / SPI1_MOSI / UART0_RXD / PWM0_CH5 LQFP32 PWM0_BRAKE / TM2_EXT0 / PWM1_CH0 / SPI1_SS / P3.3 ML51PD1AE... -

Page 26: Figure 4.1-12 Multi Function Pin Assignment Of Tssop-28 Package

ML51 4.1.2.3 TSSOP28 Package Corresponding Part Number:ML51EC0AE / ML51EB9AE P4.0 / UART2_RXD / I2C0_SDA / PWM1_CH5 / ACMP1_O I2C1_SCL / P1.4 P4.1 / UART2_TXD / I2C0_SCL / PWM1_CH4 / ACMP0_O I2C1_SDA / P1.5 P5.1 / UART1_RXD / I2C1_SDA / UART0_RXD / ICE_CLK UART0_TXD / P1.6 UART0_RXD / P1.7 P5.0 / UART1_TXD / I2C1_SCL / UART0_TXD / ICE_DAT... -

Page 27: Figure 4.1-15 Multi Function Pin Assignment Of Sop-20 Package

ML51 4.1.2.6 SOP20 Package Corresponding Part Number: ML51OB9AE P5.1 / UART1_RXD / I2C1_SDA / UART0_RXD / ICE_CLK INT0 / CLKO / TM0 / PWM0_CH0 / PWM1_BRAKE / P4.6 P5.0 / UART1_TXD / I2C1_SCL / UART0_TXD / ICE_DAT nRESET CLKO / TM2_EXT1 / PWM1_CH1 / UART3_RXD / SPI1_CLK / ACMP1_N1 / ADC_CH7 / P3.2 P0.0 / SPI0_MOSI / SPI1_MOSI / UART0_RXD / PWM0_CH5 TM2_EXT2 / PWM1_CH2 / UART0_TXD / UART3_TXD / SPI1_MISO / ACMP1_P3 / ACMP0_P3 / ADC_CH6 / P3.1 P0.1 / SPI0_MISO / SPI1_MISO / UART0_TXD / PWM0_CH4... -

Page 28: Figure 4.1-17 Multi Function Pin Assignment Of Package

ML51 Corresponding Part Number: ML51DB9AE P5.1 / UART1_RXD / I2C1_SDA / UART0_RXD / ICE_CLK INT0 / CLKO / TM0 / PWM0_CH0 / PWM1_BRAKE / P4.6 P5.0 / UART1_TXD / I2C1_SCL / UART0_TXD / ICE_DAT nRESET TM2_EXT2 / PWM1_CH2 / UART0_TXD / UART3_TXD / SPI1_MISO / ACMP1_P3 / ACMP0_P3 / ADC_CH6 / P3.1 P0.2 / SPI0_CLK / SPI1_CLK / UART1_RXD / I2C1_SDA / PWM0_CH3 TM2_EXT0 / PWM1_CH3 / UART0_RXD / SPI1_MOSI / P3.0 P0.3 / SPI0_SS / SPI1_SS / UART1_TXD / I2C1_SCL / PWM0_CH2 / CLKO / PWM1_BRAKE... -

Page 29: 4.2 Pin Description

ML51 4.2 Pin Description The default multi-function pin (MFPx = 0x00) is the GPIO pin. After setting MFPx as non-zero value, the GPIO pin will ANDed with a select function. A simple multi-function demo code for UART0 is given below: SFRS = 0x02;... - Page 30 ML51 [2] [3] [4] Pin Name Description PWM0_CH2 MFP11 GPIO PWM0 channel 2 output. PWM0_BRAKE MFP13 GPIO PWM0 Brake input pin. 11 15 4 P2.2 MFP0 General purpose digital I/O pin. ADC_CH3 MFP1 GPIO ADC channel 3 analog input. ACMP1_N0 MFP1 GPIO Analog comparator 1 negative input 0 pin.

- Page 31 ML51 [2] [3] [4] Pin Name Description MFP13 GPIO Input Capture channel 1 9 P1.1 MFP0 General purpose digital I/O pin. UART3_RXD MFP6 GPIO UART3 data receiver input pin. SC1_DAT MFP6 GPIO Smart Card 1 data pin. UART1_TXD MFP7 GPIO UART1 data transmitter output pin.

- Page 32 ML51 [2] [3] [4] Pin Name Description 16 P0.6 MFP0 General purpose digital I/O pin. UART0_RXD MFP7 GPIO UART0 data receiver input pin. C1_SDA MFP8 GPIO C1 data input/output pin. PWM1_CH5 MFP11 GPIO PWM1 channel 5 output. INT0 MFP15 GPIO External interrupt 0 input pin.

- Page 33 ML51 [2] [3] [4] Pin Name Description 17 23 14 22 P0.0 MFP0 General purpose digital I/O pin. SPI0_MOSI MFP3 GPIO SPI0 MOSI (Master Out, Slave In) pin. SPI1_MOSI MFP4 GPIO SPI1 MOSI (Master Out, Slave In) pin. UART0_RXD MFP7 GPIO UART0 data receiver input pin.

- Page 34 ML51 [2] [3] [4] Pin Name Description PWM1_CH3 MFP12 GPIO PWM1 channel 3 output. 27 19 31 P4.1 MFP0 General purpose digital I/O pin. UART2_TXD MFP8 GPIO UART2 data transmitter output pin. SC0_CLK MFP8 GPIO Smart Card 0 clock pin. C0_SCL MFP9 GPIO...

- Page 35 ML51 [2] [3] [4] Pin Name Description MFP13 GPIO Timer1 event counter input/toggle output pin. 28 41 P3.3 MFP0 General purpose digital I/O pin. SPI1_SS MFP4 GPIO SPI1 slave select pin. PWM1_CH0 MFP11 GPIO PWM1 channel 0 output. MFP13 GPIO Input Capture channel 0 PWM0_BRAKE MFP15...

- Page 36 ML51 [2] [3] [4] Pin Name Description 47 P2.7 MFP0 General purpose digital I/O pin. UART1_TXD MFP6 GPIO UART1 data transmitter output pin. PWM1_BRAKE MFP11 GPIO PWM1 Brake input pin. PWM1_CH4 MFP12 GPIO PWM1 channel 4 output/capture input. ACMP0_O MFP15 GPIO Analog comparator 0 output pin.

-

Page 37: Block Diagram

ML51 BLOCK DIAGRAM 5.1 ML51 FULL FUNCTION BLOCK Power 1T High POR / LVR / BOD Performance Management 8051 Core Max. Memory Timer 0/1 64/32/16/8KB Access APROM Flash Max. 4KB Timer 2 ICAP0~2 LDROM Flash with Input Capture Max. Bytes Data Flash Timer 3 Digital... -

Page 38: Memory Organization

ML51 MEMORY ORGANIZATION A standard 80C51 based microcontroller divides the memory into two different sections, Program Memory and Data Memory. The Program Memory is used to store the instruction codes, whereas the Data Memory is used to store data or variations during the program execution. The Data Memory occupies a separate address space from Program Memory. - Page 39 ML51 The other individual Program Memory block is called LDROM. The normal function of LDROM is to store the Boot Code for ISP. It can update APROM space and CONFIG bytes. The code in APROM can also re-program LDROM. For ISP details and configuration bit setting related with APROM and LDROM, see Section 27.4“In-System-Programming (ISP)”.

-

Page 40: 6.2 Data Memory

ML51 FFFFH FC00H F800H F400H F000H 7FFFH 7C00H 7800H 7400H APROM 7000H 3FFFH 64K bytes 3C00H 3800H APROM 3400H 32K bytes 3000H 0FFFH 0BFFH APROM 07FFH 16K bytes 03FFH LDROM 0000H 0000H 0000H 0000H CHPCON[1] BS = 0 CHPCON[1] BS = 0 CHPCON[1] BS = 1 CHPCON[1] BS = 0 The logic boundary addresses of APROM and LDROM are defined by CONFIG1[2:0]. - Page 41 ML51 The lower 128 bytes of internal RAM are present in all 80C51 devices. The lowest 32 bytes as general purpose registers are grouped into 4 banks of 8 registers. Program instructions call these registers as R0 to R7. Two bits RS0 and RS1 in the Program Status Word (PSW[3:4]) select which Register Bank is used.

-

Page 42: Figure 6.2-2 Internal 256 Bytes Ram Addressing

ML51 Indirect Accessing RAM Direct or Indirect Accessing RAM Bit-addressable Register Bank 3 Register Bank 2 General Purpose General Purpose Registers Registers Register Bank 1 Register Bank 0 Figure 6.2-2 Internal 256 Bytes RAM Addressing Dec. 05, 2018 Page 42 of 401 Rev 1.00... -

Page 43: 6.3 On-Chip Xram

ML51 6.3 On-Chip XRAM The ML51 provides additional on-chip 4/2/1 Kbytes auxiliary RAM called XRAM to enlarge the RAM space. It occupies the address space from 00H through FFH. The 4/2/1 Kbytes of XRAM are indirectly accessed by move external instruction MOVX @DPTR or MOVX @Ri. (See the demo code below.) Note that the stack pointer cannot be located in any part of XRAM. -

Page 44: Special Function Register (Sfr)

ML51 SPECIAL FUNCTION REGISTER (SFR) The ML51 uses Special Function Registers (SFR) to control and monitor peripherals and their modes. The SFR reside in the register locations 80 to FFH and are accessed by direct addressing only. SFR those end their addresses as 0H or 8H are bit-addressable. It is very useful in cases where user would like to modify a particular bit directly without changing other bits via bit-field instructions. -

Page 45: Table 7.1-1 Special Function Register (Sfr) Memory Map

ML51 Table 7.1-1 Special Function Register (SFR) Memory Map Addr. SPI1CR0 SPI1CR1 SPI1SR SPI1DR DMA1BAH EIP1 EIPH1 S1CON PWM0DTEN PWM0DTCNT PWM0MEN PWM0MD LVRFLTEN LVRDIS P0MF10 P0MF32 P0MF54 P0MF76 P1MF10 P1MF32 P1MF54 DMA1TSR MTM1DA SPI0CR0 SPI0SR SPI0DR DMA0BAH EIPH0 SPI0CR1 P1MF76 P2MF10 P2MF32 P2MF54... - Page 46 ML51 ADCCON0 AUXR0 BODCON0 IAPTRG IAPUEN IAPAL IAPAH PIPS0 PIPS1 PIPS2 PIPS3 PIPS4 PIPS5 PIPS6 C0ADDR1 C0ADDR2 C0ADDR3 C1ADDR1 C1ADDR2 C1ADDR3 SBUF SBUF1 EIE0 EIE1 P2SR SCON P0SR P1SR CHPCON DMA0CR DMA0MA DMA0CNT DMA0CCNT CKSWT CKEN SFRS P0UP P1UP P2UP P3UP P4UP P5UP...

-

Page 47: Table 7.1-2 Sfr Definitions And Reset Values

ML51 Table 7.1-2 SFR Definitions And Reset Values Addr Reset Sym. Definition (Page) Value Extensive EIPH1 interrupt priority 0000 0000b PWKTH PT3H PSH_1 high 1 LVR Disable 0000 0000b LVRDIS LVRDIS[7:0] P1.5 and P1.4 Multi-Function 0000 0000b P1MF54 P1MF5 P1MF4 Select Extensive EIP1... - Page 48 ML51 Addr Reset Sym. Definition (Page) Value PWM0DT PWM Dead-time 0000 0000b PWMnDTCNT.8 PDT45EN PDT23EN PDT01EN Enable P0.1 and P0.0 P0MF10 Multi-Function 0000 0000b P0MF1 P0MF0 Select Serial port 1 SM0_1 SM1_1 SM2_1 0000 0000b S1CON REN_1 TB8_1 RB8_1 TI_1 RI_1 control / FE_1...

- Page 49 ML51 Addr Reset Sym. Definition (Page) Value B register 0000 0000b Extensive 0000 0000b EIP0 PSPI PWDT PPWM PCAP interrupt priority P5.1 and P5.0 P5MF10 Multi-Function 0000 0000b P5MF1 P5MF0 Select PDMA1 Current DMA1CC 0000 0000b CCNT[7:0] Transfer Count Input capture 2 0000 0000b C2H[7:0] high byte...

- Page 50 ML51 Addr Reset Sym. Definition (Page) Value P3.5 and P3.4Multi- 0000 0000b P3MF54 P3MF5 P3MF4 Function Select C1 control C1CON 0000 0000b register ADC Status 0000 0000b ADCSR SLOW ADCDIV[2:0] CMPHIT HDONE FDONE Register Input capture 1 0000 0000b C1H[7:0] high byte SC1 control SC1CR1...

- Page 51 ML51 Addr Reset Sym. Definition (Page) Value Accumulator 0000 0000b ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0 SC0 Transfer 0000 1010b SC0TSR TXEMPTY TXOV RXEMPTY RXOV Status Register PWM0CO PWM control 1 0000 0000b PWMMOD[1:0] PWMTYP FBINEN PWMDIV[2:0] SC Transfer 0000 1010b SC1TSR TXEMPTY...

- Page 52 ML51 Addr Reset Sym. Definition (Page) Value Output latch, 0000 0000b Port 4 P4.7 P4.6 P4.5 P4.4 P4.3 P4.2 P4.1 P4.0 Input, XXXX XXXXb SC0 Control SC0CR1 0000 0000b PBOFF TXDMAEN RXDMAEN CLKKEEP UARTEN Register1 PWM0FB Brake data 0000 0000b FBINLS FBD5 FBD4...

- Page 53 ML51 Addr Reset Sym. Definition (Page) Value PWM0 Control PWM0CO 0000 0000b PWMRUN LOAD PWMF CLRPWM register0 PWM0 Period PWM0PH 0000 0000b PWM0P[15:8] High Byte PWM1 Period PWM1PL 0000 0000b PWM1P[7:0] Low Byte Program status 0000 0000b word ADC Compare 0000 0000b ADCMPH ADCMP[15:8]...

- Page 54 ML51 Addr Reset Sym. Definition (Page) Value Timer 2 Mode LDEN 0000 0000b T2MOD T2DIV[2:0] CAPCR CMPCR LDTS[1:0] Auxiliary Register AUXR1 0000 0000b UART2PX UART1PX UART0PX PWM1 Period PWM1PH 0000 0000b PWM1P[7:0] high Byte ̅̅̅̅̅ T2CON Timer 2 control 0000 0000b Timed access 0000 0000b TA[7:0]...

- Page 55 ML51 Addr Reset Sym. Definition (Page) Value PWM1DT PWM Dead-time PWM1DTCNT.8 PDT45EN PDT23EN PDT01EN 0000 0000b Enable 0000 0000b C0 C control 0000 0000b C0TOC C0 time-out I2TOCEN I2TOF counter Port 5 Schmitt 0000 0000b P5S.7 P5S.6 P5S.5 P5S.4 P5S.3 P5S.2 P5S.1 P5S.0...

- Page 56 ML51 Addr Reset Sym. Definition (Page) Value Memory to Memory 3 Destination 0000 0000b MTM3DA MDAL[7:0] Address Low Byte C1 Time-out 0000 0000b C1TOC I2TOCEN I2TOF Counter Port 5 Mode P2M2 0000 0000b P2M2.7 P2M2.6 P2M2.5 P2M2.4 P2M2.3 P2M2.2 P5M2.1 P2M2.0 Select 2 PDMA 2 Current...

- Page 57 ML51 Addr Reset Sym. Definition (Page) Value Output latch, 0000 0000b Port 3 P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 Input, XXXX XXXXb IAPCN IAP control 0011 0000b IAPA[17:16] FOEN FCEN FCTRL[3:0] Pin Interrupt PIPS7 0000 0000b PSEL[2:0] BSEL[2:0] Control register 7 Memory to Memory 3...

- Page 58 ML51 Addr Reset Sym. Definition (Page) Value PDMA2 XRAM DMA2BA Base Address 0000 0000b MTMDA [7:4] XRAMA[7:4] High Byte SADDR Slave 0 address 0000 0000b SADDR[7:0] Internal V 0000 0000b VRFCON VRFSEL[2:0] ENLOAD ENVRF Control Interrupt enable 0000 0000b EADC EBOD IAP address high 0000 0000b...

- Page 59 ML51 Addr Reset Sym. Definition (Page) Value C0 Own Slave C0ADDR 0000 0000b C0ADDR2[7:1] Address 2 ADC Control ADCCON 0000 0000b ADCF ADCS ETGSEL1 ETGSEL0 ADCHS3 ADCHS2 ADCHS1 ADCHS0 register 0 Pin Interrupt PIPS0 0000 0000b PSEL[2:0] BSEL[2:0] Control 1 C0 Own Slave C0ADDR 0000 0000b...

- Page 60 ML51 Addr Reset Sym. Definition (Page) Value Clock Switch 0011 0000b CKSWT HXTST LXTST HIRCST LIRCST ECLKST OSC[2:0] Port4 Pull-Up P4UP 0000 0000b P4UP.7 P4UP.6 P4UP.5 P4UP.4 P4UP.3 P4UP.2 P4UP.1 P4UP.0 resister control PDMA1 Current DMA0CC 0000 0000b DMA0CCNT [7:0] Transfer Count Port 3 Pull-Up P3UP...

- Page 61 ML51 Addr Reset Sym. Definition (Page) Value Port1 Pull-Down 0000 0000b P1DW P1DW.7 P1DW.6 P1DW.5 P1DW.4 P1DW.3 P1DW.2 P1DW.1 P1DW.0 resister control Timer 0 low byte 0000 0000b TL0[7:0] Port0 Pull-Down P0DW 0000 0000b P0DW.7 P0DW.6 P0DW.5 P0DW.4 P0DW.3 P0DW.2 P0DW.1 P0DW.0 resister control...

- Page 62 ML51 Dec. 05, 2018 Page 62 of 401 Rev 1.00...

-

Page 63: 7.2 All Sfr Description

ML51 7.2 All SFR Description Note: the reset value show as following means U-unchanged; C-initialized by CONFIG; X- base on real chip status. P0 – Port 0 (Bit-addressable) P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 Address: 80H, All pages Reset value: 1111 1111b Name Description... - Page 64 ML51 Name Description DPH[7:0] Data pointer high byte This is the high byte of 16-bit data pointer. DPH combined with DPL serve as a 16-bit data pointer DPTR to access indirect addressed RAM or Program Memory. DPS (AUXR0.0) bit decides which data pointer, DPTR or DPTR1, is activated.

- Page 65 ML51 Name Description HXSG HXT gain value select 000 = L0 mode (smallest value) 001 = L1 mode 010 = L2 mode 011 = L3 mode 100 = L4 mode 101 = L5 mode 110 = L6 mode 111 = L7 mode (largest value) Reserved LXSG LXT gain value select...

- Page 66 ML51 Address: 87H, All pagess POR reset value: 0001 000b, other reset value: 000U 0000b Name Description SMOD Serial port 0 double baud rate enable Setting this bit doubles the serial port baud rate when UART0 is in Mode 2 or when Timer 1 overflow is used as the baud rate source of UART0 Mode 1 or 3.

- Page 67 ML51 Name Description Timer 1 overflow flag This bit is set when Timer 1 overflows. It is automatically cleared by hardware when the program executes the Timer 1 interrupt service routine. This bit can be set or cleared by software. Timer 1 run control 0 = Timer 1 Disabled.

- Page 68 ML51 Name Description GATE Timer 1 gate control ̅̅̅̅̅̅̅ logic level. 0 = Timer 1 will clock when TR1 is 1 regardless of INT1 ̅̅̅̅̅̅̅ is logic 1. 1 = Timer 1 will clock only when TR1 is 1 and INT1 C/T ̅...

- Page 69 ML51 P0DW 8AH, Page 1 0000_0000 b P1DW 8BH, Page 1 0000_0000 b P2DW 8CH, Page 1 0000_0000 b P3DW 8DH, Page 1 0000_0000 b P4DW 8EH, Page 1 0000_0000 b P5DW 8FH, Page 1 0000_0000 b PnDW.7 PnDW.6 PnDW.5 PnDW.4 PnDW.3 PnDW.2...

- Page 70 ML51 Address: 8DH, Page 0 Reset value: 0000 0000b Name Description TH1[7:0] Timer 1 high byte The TH1 register is the high byte of the 16-bit counting register of Timer 1. CKCON – Clock Control FASTWK PWMCKS T1OE T0OE CLOEN Address: 8EH, Page 0 Reset value: 1000 0000b Name...

- Page 71 ML51 Name Description CLOEN System clock output enable 0 = System clock output Disabled. 1 = System clock output Enabled from CLO pin. Reserved WKCON – Self Wake-up Timer Control WKTCK WKTF WKTR WKPS[2:0] Address: 8FH, PAGE 0 Reset value: 0000 0000b Name Description Reserved...

- Page 72 ML51 Address: 90H, All pages Reset value: 1111 1111b Name Description P1[7:0] Port 1 Port 1 is an maximum 8-bit general purpose I/O port. SFRS – SFR Page Selection SFRPAGE SFRPAGE Address: 91H, All pages Reset value: 0000 0000b Name Description SFRPAGE SFR page select...

- Page 73 ML51 Name Description PSSEL[2:0] Peripheral Source Select 000 = XRAM to XRAM 001 = SPI0 RX 010 = SMC/UART RX. 011 = SPI1 RX 100 = Reserved, No peripheral source select 101 = SPI0 TX 110 = SMC/UART TX. 111 = SPI1 TX Note: 001~011 : peripheral devices to XRAM memory 101~111 : XRAM memory to peripheral devices PDMA HALFTransfer Done Interrupt Enable Bit...

- Page 74 ML51 Name Description PnUP[7:0] P0.n pull-up enable 0 = Pn.x pull-up Disabled. 1 = Pn.x pull-up Enabled. DMAnMA – PDMA XRAM Base Address Low Byte Register SFR Address Reset Value DMA0MAL 93H, Page 0 0000_0000 b DMA1MAL ECH, Page 0 0000_0000 b DMA2MAL B4H, Page 2...

- Page 75 ML51 Register SFR Address Reset Value DMA0CCNT 95H, Page 0 0000_0000 b DMA1CCNT EEH, Page 0 0000_0000 b DMA2CCNT B6H, Page 2 0000_0000 b DMA3CCNT AEH, Page 2 0000_0000 b DMAnCCNT[7:0] Name Description CNT[7:0] PDMA Current Transfer Count The current transfer count for PDMA request operation. Current transfer count = CCNT[7:0] Note: while DMAnCNT=0xFF (total transfer count = 256) and DMAnCCNT = 0x00 , If PDMA FDONE flag (DMAnTSR[0])=0, that means, 1’st byte data is not complete.If PDMA FDONE flag...

- Page 76 ML51 Name Description OSC[2:0] Oscillator selection bits This field selects the system clock source. 00x = Internal 24 MHz oscillator. Defaul value accoding to HIRCEN(CKEN.5) enabled. 01x = External oscillator clock source accoding to ECLKEN(CKEN.3) enabled. 10x = Internal 38.4 kHz oscillator according to LIRCEN(CKEN.4) enabled. 110 = External High speed crystal/resonator clock source (4 MHz ~ 24 MHz) accoding to EHXTEN(CKEN.7) enabled.

- Page 77 ML51 Name Description Reserved CKSWTF Clock switch fault flag 0 = The previous system clock source switch was successful. 1 = User tried to switch to an instable or disabled clock source at the previous system clock source switch. If switching to an instable clock source, this bit remains 1 until the clock source is stable and switching is successful.

- Page 78 ML51 Name Description 9th transmitted bit This bit defines the state of the 9th transmission bit in serial port 0 Mode 2 or 3. It is not used in Mode 0 or 1. 9th received bit The bit identifies the logic level of the 9th received bit in serial port 0 Mode 2 or 3. In Mode 1, RB8 is the logic level of the received stop bit.

- Page 79 ML51 PnS.7 PnS.6 PnS.5 PnS.4 PnS.3 PnS.2 PnS.1 PnS.0 Name Description PnS[7:0] P0 Schmitt triggered input 0 = TTL level input of Pn.x. 1 = Schmitt triggered input of Pn.x. SBUF1 – Serial Port 1 Data Buffer SBUF1[7:0] Address: 9AH, Page 0 Reset value: 0000 0000b Name Description...

- Page 80 ML51 ESPI0 EFB0 EWDT EPWM0 ECAP Address: 9BH, Page 0 Reset value: 0000 0000b Name Description Enable Timer 2 interrupt 0 = Timer 2 interrupt Disabled. 1 = Timer 2 interrupt Enable. When interrupt generated, TF2 (T2CON.7) set 1 ESPI0 Enable SPI interrupt 0 = SPI interrupt Disabled.

- Page 81 ML51 Name Description EFB1 Enable Fault Brake 1 interrupt 0 = Fault Brake interrupt Disabled. 1 = Fault Brake interrupt Enable. When interrupt generated FBF (PWM1FBD.7) Enabled. EPWM1 Enable PWM1 interrupt 0 = PWM1 interrupt Disabled. 1 = PWM1 interrupt Enable. When interrupt generated PWMF (PWM1CON0.5) set 1. Enable I C1 interrupt 0 = I...

- Page 82 ML51 Name Description PORF POR Reset Flag 1: POR15 Reset Flag is active 0: POR15 Reset Flag is inactive Write 0 to clear this bit HFRF mirrored from AUXR0.5 Clear this bit by write AUXR0.5=0 or RSR.5=0 mirrored from PCON.4 Clear this bit by write PCON.4=0 or RSR.4=0 RSTPINF mirrored from AUXR0.6...

- Page 83 ML51 Name Description Boot select This bit defines from which block that MCU re-boots after all resets. 0 = MCU will re-boot from APROM after all resets. 1 = MCU will re-boot from LDROM after all resets. IAPEN IAP enable 0 = IAP function Disabled.

- Page 84 ML51 Name Description ETGSEL[1:0] External trigger source select When ADCEX (ADCCON1.1) is set, these bits select which pin output triggers ADC conversion. 00 = PWM0CH0. 01 = PWM0CH2. 10 = PWM0CH4. 11 = STADC pin. ADCHS[3:0] A/D converting channel select This filed selects the activating analog input source of ADC.

- Page 85 ML51 Name Description PSEL[2:0] Pin interrupt channel Port select 000 = P0 Port. 001 = P1 Port. 010 = P2 Port. 011 = P3 Port. 100 = P4 Port. 101 = P5 Port. 110 = Reserved. 111 = Reserved. Reserved BSEL[2:0] Pin interrupt channel bit select 000 = Pn.0.

- Page 86 ML51 Name Description HFIF Hard Fault Interrupt flag Once CPU fetches instruction address over Flash size while EHFI (EIE1.4)=1. MCU will be interrupt and this bit will be set via hardware. It is recommended that the flag be cleared via software.

- Page 87 ML51 Name Description BORST Brown-out reset enable This bit decides whether a brown-out reset is caused by a power drop below VBOD. 0 = Brown-out reset when V drops below VBOD Disabled. 1 = Brown-out reset when V drops below VBOD Enabled. BORF Brown-out reset flag When the MCU is reset by brown-out event, this bit will be set via hardware.

- Page 88 ML51 Name Description Reserved SPMEN SPROM Memory space mapping enable 0 = CPU memory address 0xff80~0xffff is mapping to APROM memory 1 = CPU memory address 0xff80~0xffff is mapping to SPROM memory SPUEN SPROM Memory space updated enable(TA protected) 0 = Inhibit erasing or programming SPROM bytes by IAP 1 = Allow erasing or programming SPROM bytes by IAP.

- Page 89 ML51 EADC EBOD Address: A8H, All pages Reset value: 0000 0000b Name Description Enable all interrupt This bit globally enables/disables all interrupts that are individually enabled. 0 = All interrupt sources Disabled. 1 = Each interrupt Enabled depending on its individual mask setting. Individual interrupts will occur if enabled.

- Page 90 ML51 Name Description SADDR[7:0] Slave 0 address This byte specifies the microcontroller’s own slave address for UATR0 multi-processor communication. VRFCON – Internal V Control (TA protected) VRFSEL[2:0] ENLOAD ENVRF Address: A9H,Page 1 Reset value: 0000 0000b Name Description Reserved VRFSEL Internal V Output Voltage Select This field selects V...

- Page 91 ML51 Name Description WDTR WDT run This bit is valid only when control bits in WDTEN[3:0] (CONFIG4[7:4]) are all 1. At this time, WDT works as a general purpose timer. 0 = WDT Disabled. 1 = WDT Enabled. The WDT counter starts running. WDCLR WDT clear Setting this bit will reset the WDT count to 00H.

- Page 92 ML51 Name Description VRFTIRM[6:0] Internal V Trim Select default=7’b1000000 Output MAX=7’b1111110; Output MIN=7’b0000000 1111111 = Untrimmed nature voltage = Medium voltage (1000000) BODCON1 – Brown-out Detection Control 1 (TA protected) LPBOD[1:0] BODFLT Address: ABH, Page 0 Reset value: POR: 0000 0001b / Others:0000 0UUUb Name Description Reserved...

- Page 93 ML51 Name Description AO0PEN Analog comparator 0 output to pin enable control 0 = pin output disabled 1= output to P4.1 Enabled Reserved CRVSSEL CRV Source Voltage Selection 0 = V is selected as CRV source voltage. 1 = The reference voltage (V ) is selected as CRV source voltage.

- Page 94 ML51 Name Description Reserved PDMA3H PDMA3H interrupt priority high bit PDMA2H PDMA2H interrupt priority high bit SMC1H SMC1H interrupt priority high bit PFB1H Fault Brake1 interrupt priority high bit PPWM1H PPWM1H interrupt priority high bit C interrupt priority high bit PACMPH ACMP interrupt priority high bit [8] EIPH2 is used in combination with the EIP2 to determine the priority of each interrupt source.

- Page 95 ML51 P3 – Port 3 (Bit-addressable) P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 Address: B0H, All pages Reset value: 1111 1111b Name Description P1[7:0] Port 3 Port 3 is an maximum 8-bit general purpose I/O port. P5 – Port 5 (Bit-addressable) P5.6 P5.5 P5.4...

- Page 96 ML51 Register SFR Address Reset Value P0M2 B2H, Page 1 0000_0000 b P1M2 B4H, Page 1 0000_0000 b P2M2 B6H, Page 1 0000_0000 b P3M2 C3H, Page 1 0000_0000 b P4M2 BAH, Page 1 0000_0000 b P5M2 BEH, Page 1 0000_0000 b PnM2.7 PnM2.6...

- Page 97 ML51 Name Description I2STAT1[7:3] C1 status code The MSB five bits of I CnSTAT contains the status code. There are 27 possible status codes. When I CnSTAT is F8H, no relevant state information is available and SI flag keeps 0. All other 26 status codes correspond to the I C states.

- Page 98 ML51 Name Description External interrupt 1 priority low bit Timer 0 interrupt priority low bit External interrupt 0 priority low bit [1] IP is used in combination with the IPH to determine the priority of each interrupt source. See Table 26.3-1 Setting Interrupt Priority Level for correct interrupt priority configuration.

- Page 99 ML51 Name Description Reserved PADC ADC interrupt priority low bit PBOD Brown-out detection interrupt priority low bit Serial port 0 interrupt priority low bit Timer 1 interrupt priority low bit External interrupt 1 priority low bit Timer 0 interrupt priority low bit External interrupt 0 priority low bit SADEN –...

- Page 100 ML51 Address: BBH, Page 0 Reset value: 0000 0000b Name Description SADDR1[7:0] Slave 1 address This byte specifies the microcontroller’s own slave address for UART1 multi-processor communication. CnDAT – I C Data Register SFR Address Reset Value C0DAT BCH, Page 0 0000_0000 b C1DAT B3H, Page 0...

- Page 101 ML51 Name Description Reserved The least significant three bits of I CnSTAT are always read as 0. CnCLK – I C Clock Register SFR Address Reset Value C0CLK BEH, Page 0 0000_1001 b C1CLK B5H, Page 0 0000_1001 b C0CLK[7:0] Address: BEH, Page 0 Reset value: 0000 1001b Name...

- Page 102 ML51 Name Description C0 time-out counter clock divider 0 = The clock of I C time-out counter is F 1 = The clock of I C time-out counter is F I2TOF C0 time-out flag This flag is set by hardware if 14-bit I C time-out counter overflows.

- Page 103 ML51 Name Description STOP flag When STO is set if the I C is in the master mode, a STOP condition is transmitted to the bus. STO is automatically cleared by hardware once the STOP condition has been detected on the bus.

- Page 104 ML51 CnADDRx – I Cn Own Slave Address Register SFR Address Reset Value C0ADDR0 C1H, Page 0 0000_0000 b C0ADDR1 A1H, Page 2 0000_0000 b C0ADDR2 A2H, Page 2 0000_0000 b C0ADDR3 A3H, Page 2 0000_0000 b C1ADDR0 B2H, Page 0 0000_0000 b C1ADDR1 A4H, Page 2...

- Page 105 ML51 Name Description CKDIV[7:0] Clock divider The system clock frequency F follows the equation below according to CKDIV value. , while CKDIV = 00H, CKDIV , while CKDIV = 01H to FFH. ADCRL – ADC Result Low Byte ADCR[3:0] Address: C2H, Page 0 Reset value: 0000 0000b...

- Page 106 ML51 Name Description SMOD0_1 Serial port 1 framing error access enable 0 = S1CON.7 accesses to SM0_1 bit. 1 = S1CON.7 accesses to FE_1 bit. BRCK Serial port 0 baud rate clock source This bit selects which Timer is used as the baud rate clock source when serial port 0 is in Mode 1 or 3.

- Page 107 ML51 Address: C6H, Page 0 Reset value: 0000 0000b Name Description RH3[7:0] Timer 3 reload high byte It holds the high byte of the reload value of Time 3. PORDIS – POR Disable (TA protected) PORDIS[7:0] Address: C6H, Page 1 reset value: 0000 0000b Name Description...

- Page 108 ML51 Name Description Timer 2 run control 0 = Timer 2 Disabled. Clearing this bit will halt Timer 2 and the current count will be preserved in TH2 and TL2. 1 = Timer 2 Enabled. Reserved ̅̅̅̅̅̅ CM/RL2 Timer 2 compare or auto-reload mode select This bit selects Timer 2 functioning mode.

- Page 109 ML51 Name Description LDTS[1:0] Auto-reload trigger select These bits select the reload trigger event. 00 = Reload when Timer 2 overflows. 01 = Reload when input capture 0 event occurs. 10 = Reload when input capture 1 event occurs. 11 = Reload when input capture 2 event occurs. AUXR1 –...

- Page 110 ML51 PIF7 PIF6 PIF5 PIF4 PIF3 PIF2 PIF1 PIF0 R (level) R (level) R (level) R (level) R (level) R (level) R (level) R (level) R/W (edge) R/W (edge) R/W (edge) R/W (edge) R/W (edge) R/W (edge) R/W (edge) R/W (edge) Address: CAH, Page 0 Reset value: 0000 0000b Name...

- Page 111 ML51 RCMP2H[7:0] Timer 2 reload/compare high byte This register stores the high byte of compare value when Timer 2 is configured in compare mode. Also it holds the high byte of the reload value in auto-reload mode. TL2 – Timer 2 Low Byte TL2[7:0] Address: CCH, Page 0 Reset value: 0000 0000b...

- Page 112 ML51 Name Description AINnDIDS ADC Channel digital input disable 0 = Enabled digital input at ADC channel n. 1 = Disabled digital input at ADC channel n . ADC channel n is read always 0. ADCMPH – ADC Compare High Byte ADCMP[11:4] Address: CFH, Page 0 Reset value: 0000 0000b...

- Page 113 ML51 Name Description These two bits select one of four banks in which R0 to R7 locate. Register Bank RAM Address 00H to 07H 08H to 0FH 10H to 17H 18H to 1FH Overflow flag OV is used for a signed character operands. For a ADD or ADDC instruction, OV will be set if there is a carry out of bit 6 but not out of bit 7, or a carry out of bit 7 but not bit 6.

- Page 114 ML51 Name Description LOAD PWM new period and duty load This bit is used to load period and duty control registers in their buffer if new period or duty value needs to be updated. The loading will act while a PWM period is completed. The new period and duty affected on the next PWM cycle.

- Page 115 ML51 POSSEL NEGSEL WKEN HYSEN ACMPIE ACMPEN Address: D2H, Page 0 Reset value: 0000 0000b Name Description POSSEL Comparator 0 positive Input Selection 00 = ACMP0_P0 (P2.5) pin. 01 = ACMP0_P1 (P2.3) pin. 10 = ACMP0_P2 (P2.1) pin. 11 = ACMP0_P3 (P3.0) pin. NEGSEL Comparator 0 Negative Input Selection 00 = ACMP0_N0 (P2.4) pin.

- Page 116 ML51 PWM1C3H CDH, Page 2 PWM1 Channel 3 Duty High Byte 0000_0000 b PWM1C4H CEH, Page 2 PWM1 Channel 4 Duty High Byte 0000_0000 b PWM1C5H CFH, Page 2 PWM1 Channel 5 Duty High Byte 0000_0000 b PWMnCx [15:8], n=0,1; x=0,1,2,3,4,5 Name Description PWMnCx[15:8]...

- Page 117 ML51 Name Description ACMPIE Comparator 1 Interrupt Enable Bit 0 = Comparator 1 interrupt Disabled. 1 = Comparator 1 interrupt Enabled. If WKEN (ACMPCR2[3]) is set to 1, the wake-up interrupt function will be enabled as well. ACMPEN Comparator 1 Enable Bit 0 = Comparator 1 Disabled.

- Page 118 ML51 Name Description Reserved CRV1CTL[2:0] Comparator 1 Reference Voltage Setting CRV1 = CRV source voltage * (2/12+CRV1CTL/12). Reserved CRV0CTL[2:0] Comparator 0 Reference Voltage Setting CRV0 = CRV source voltage * (2/12+CRV0CTL/12). SCnCR0 – SC Control Register Register SFR Address Reset Value SC0CR0 D6H, Page 1 0000_0000 b...

- Page 119 ML51 Name Description CONSEL Convention Selection 0 = Direct convention. 1 = Inverse convention. Note1: This bit is auto clear to “0”, if AUTOCEN(SCnCR0[3]) is writing “1” Note2: If AUTOCEN(SCnCR0[3]) is enabled, hardware will decide the convention and change the CONSEL (SCnCR0[4]) bits automatically after SCEN (SCnCR0[0]) =”1”.

- Page 120 ML51 Register SFR Address Reset Value SC0CR1 D7H, Page 0 0000_0000 b SC1CR1 E7H, Page 2 0000_0000 b PBOFF TXDMAEN RXDMAEN CLKKEEP UARTEN Name Description Odd Parity Enable Bit 0 = Even number of logic 1’s are transmitted or check the data word and parity bits in receiving mode.

- Page 121 ML51 Name Description UARTEN UART Mode Enable Bit 0 = Smart Card mode. 1 = UART mode. Note1:When operating in UART mode, user must set CONSEL (SCnCR0[4]) = 0 and AUTOCEN(SCnCR0[3]) = 0. Note2:When operating in Smart Card mode, user must set UARTEN(SCnCR1 [0]) = 0. Note3:When UART is enabled, hardware will generate a reset to reset FIFO and internal state machine.

- Page 122 ML51 Name Description P4[7:0] Port 4 Port 4 is an maximum 8-bit general purpose I/O port. SCnDR – SC Data Register Register SFR Address Reset Value SC0DR D9H, Page 1 0000_0000 b SC1DR D9H, Page 2 0000_0000 b SCnDR[7:0] Name Description SCnDR[7:0] SC / UART buffer data...

- Page 123 ML51 SCnEGT[7:0] Name Description SCnEGT SC Extra Guard Time [7:0] This field indicates the extra guard timer value. Note: The counter is ETU base . PWMnCxL – PWM0/1 Channel 0~5 Duty Low Byte n=0,1; x=0,1,2,3,4,5 Register SFR Address Description Reset Value PWM0C0L D2H, Page 1 PWM0 Channel 0 Duty Low Byte...

- Page 124 ML51 ETURDIV[7:0] Name Description ETURDIV[7:0] LSB bits of ETU Rate Divider The field indicates the LSB of clock rate divider. The real ETU is ETURDIV[11:0] + 1. Note1: ETURDIV[11:0] must be greater than 0x004. Note2: SCnETURD0 has to program first, then SCnETUDR2. SCnETURD1 –SC ETU Rate Divider Register Register SFR Address...

- Page 125 ML51 SC0IE DDH, Page 0 0000_0000 b SC1IE DCH, Page 2 0000_0000 b ACERRIEN BGTIEN TERRIEN TBEIEN RDAIEN Name Description Reserved ACERRIEN Auto Convention Error Interrupt Enable Bit This field is used to enable auto-convention error interrupt. 0 = Auto-convention error interrupt Disabled. 1 = Auto-convention error interrupt Enabled.

- Page 126 ML51 Name Description Reserved ACERRIF Auto Convention Error Interrupt Status Flag (Read Only) This field indicates auto convention sequence error. If the received TS at ATR state is neither 0x3B nor 0x3F, this bit will be set. Note: This bit is read only, but it can be cleared by writing “0” to it. BGTIF Block Guard Time Interrupt Status Flag (Read Only) This field is used for block guard time interrupt status flag.

- Page 127 ML51 Name Description Transmit /Receive in Active Status Flag (Read Only) 0 = This bit is cleared automatically when TX/RX transfer is finished 1 = This bit is set by hardware when TX/RX transfer is in active. Receiver Break Error Status Flag (Read Only) This bit is set to logic 1 whenever the received data input (RX) held in the “spacing state”...

- Page 128 ML51 Name Description PWMMOD PWM mode select [1:0] 00 = Independent mode. 01 = Complementary mode. 10 = Synchronized mode. 11 = Reserved. Group mode enable This bit enables the group mode. If enabled, the duty of first three pairs of PWM are decided by PWM01H and PWM01L rather than their original duty control registers.

- Page 129 ML51 CONT ETGTYP[1:0] ADCEX ADCEN Address: E1H, Page 0 Reset value: 0000 0000b Name Description Reserved ADC Half Done Interrupt Enable 0 = ADC interrupt is not set while half of A/D conversions are complete in continue mode 1 = ADC interrupt is set while half of A/D conversions are complete in continue mode CONT ADC Continue Sampling select 0 = ADC single sampling, ADC interrupt is set while an A/D conversion is completed...

- Page 130 ML51 Name Description CAPEN2 Input capture 2 enable 0 = Input capture channel 2 Disabled. 1 = Input capture channel 2 Enabled. CAPEN1 Input capture 1 enable 0 = Input capture channel 1 Disabled. 1 = Input capture channel 1 Enabled. CAPEN0 Input capture 0 enable 0 = Input capture channel 0 Disabled.

- Page 131 ML51 Name Description ADCMPO ADC comparator output value This bit is the output value of ADC result comparator based on the setting of ACMPOP. This bit updates after every A/D conversion complete. ADCAQT ADC acquisition time This 3-bit field decides the acquisition time for ADC sampling, following by equation below: ...

- Page 132 ML51 Address: E3H, Page 0 Reset value: 0000 0000b Name Description ADCDLY[7:0] ADC external trigger delay counter low byte This 8-bit field combined with ADCCON2.0 forms a 9-bit counter. This counter inserts a delay after detecting the external trigger. An A/D converting starts after this period of delay. ADCDLY External trigger delay time = Note that this field is valid only when ADCEX (ADCCON1.1) is set.

- Page 133 ML51 Name Description ADCBAH[3:0] ADC RAM base address (High byte) The most significant 4 bits of RAM base address to store ADC continue sampling data. RAM base address ADCBA[11:0] = {ADCBAH[3:0], ADCBAL[7:0]} C0L – Capture 0 Low Byte C0L[7:0] Address: E4H, Page 1 Reset value: 0000 0000b Name Description...

- Page 134 ML51 Address: E6H, Page 0 Reset value: 0000 0000b Name Description ADCCN[7:0] ADC Current Sampling Number The current sampling numbers for ADC continue sampling select. The current sampling number= ADCCN[7:0] + 1 C1L – Capture 1 Low Byte C1L[7:0] Address: E6H, Page 1 Reset value: 0000 0000b Name Description...

- Page 135 ML51 Name Description HDONE A/D Conversion Half Done Flag This bit is set by hardware when half of ADCSN A/D conversions are complete in continue mode. Note: This bit can be cleared by writing 0 to it FDONE A/D Conversion Full Done Flag This bit is set by hardware when all of ADCSN A/D conversions are complete in continue mode or single conversion in single mode.

- Page 136 ML51 Name Description FDONE PDMA Full Transfer Done Flag This bit is set by hardware when PDMA full transfer is done. Note: This bit can be cleared by writing 0 to it. PICON – Pin Interrupt Control PIT7 PIT6 PIT5 PIT4 PIT3 PIT2...

- Page 137 ML51 Name Description PIT0 Pin interrupt channel 0 type select This bit selects which type that pin interrupt channel 0 is triggered. 0 = Level triggered. 1 = Edge triggered. MTMnDA – Memory to Memory Destination Address Low Byte Register SFR Address Reset Value MTM0DA...

- Page 138 ML51 PIPEN – Pin Interrupt Positive Polarity Enable. PIPEN7 PIPEN6 PIPEN5 PIPEN4 PIPEN3 PIPEN2 PIPEN1 PIPEN0 Address: EBH, Page 1 Reset value: 0000 0000b Name Description PIPENn Pin interrupt channel n positive polarity enable This bit enables high-level/rising edge triggering pin interrupt channel n. The level or edge triggered selection depends on each control bit PITn in PICON.

- Page 139 ML51 Name Description Timer 2 interrupt priority low bit PSPI0 SPI0 interrupt priority low bit Fault Brake interrupt priority low bit PWDT WDT interrupt priority low bit PPWM0 PWM interrupt priority low bit PCAP Input capture interrupt priority low bit Pin interrupt priority low bit C interrupt priority low bit [3] EIP0 is used in combination with the EIPH0 to determine the priority of each interrupt source.

- Page 140 ML51 Name Description SSOE Slave select output enable ̅̅̅̅ pin This bit is used in combination with the DISMODF (SPInSR.3) bit to determine the feature of SS as shown in Table 17–1. Slave Select Pin Configurations. This bit takes effect only under MSTR = 1 and DISMODF = 1 condition.

- Page 141 ML51 Name Description SPR[1:0] SPI clock rate select These two bits select four grades of SPI clock divider. The clock rates below are illustrated under = 24 MHz condition. SPR3 SPR2 SPR1 SPR0 Divider SPI clock rate 12M bit/s 6M bit/s 3M bit/s 1.5M bit/s 750k bit/s...

- Page 142 ML51 Name Description SPR[3:2] SPI clock rate select These two bits select four grades of SPI clock divider. The clock rates below are illustrated under F = 24 MHz condition. SPR3 SPR2 SPR1 SPR0 Divider SPI clock rate 12M bit/s 6M bit/s 3M bit/s 1.5M bit/s...

- Page 143 ML51 Name Description SPIS[1:0] SPI Interval time selection between adjacent bytes SPIS[1:0] and CPHA select eight grades of SPI interval time selection between adjacent bytes. As below table: CPHA SPIS1 SPIS0 SPI clock SPIS[1:0] are valid only under Master mode (MSTR = 1). SPInSR –...

- Page 144 ML51 Name Description MODF Mode Fault error flag ̅̅̅̅ pin is configured as Mode Fault input (MSTR = 1 This bit indicates a Mode Fault error event. If SS ̅̅̅̅ is pulled low by external devices, a Mode Fault error occurs. Instantly and DISMODF = 0) and SS MODF will be set as logic 1.

- Page 145 ML51 DMA3BAH AAH, Page 2 0000_0000 b MTMDA [7:4] XRAMA[7:4] Name Description MDAH[7:0] Memory to Memory Destination Address (High Byte) The most significant 4 bits of XRAM address are used for memory to memory destination address. XRAM destination address = {MDAH[3:0], MDAL[7:0]} MAH[3:0] PDMA XRAM Base Address (High Byte) The most significant 4 bits of XRAM address to store or read for the peripheral source data;...

- Page 146 ML51 Address: F8H, All pages Reset value: 0000 0000b Name Description SM0_1/FE_1 Serial port 1 mode select SMOD0 _ 1 (T3CON.6) = 0: SM1_1 Table 15.5-2 Serial Port 1 Mode / baudrate Description for details. SMOD0 _ 1 (T3CON.6) = 1: SM0 _ 1/FE _ 1 bit is used as frame error (FE) status flag.

- Page 147 ML51 Name Description RI_1 Receiving interrupt flag This flag is set via hardware when a data frame has been received by the serial port 1 after bit in Mode 0 or after sampling the stop bit in Mode 1, 2, or 3. SM2 _ 1 bit as logic 1 the 8 has restriction for exception.

- Page 148 ML51 PWM0DTCNT[7:0] Name Description PWM0DTCNT PWM dead-time counter low byte [7:0] This 8-bit field combined with PWMnDTEN .4 forms a 9-bit PWM dead-time counter PWM0DTCNT. This counter is valid only when PWM is under complementary mode and the correspond PWMnDTEN bit for PWM pair is set. PDTCNT ...

- Page 149 ML51 Name Description PMDn PWMn mask data The PWMn signal outputs mask data once its corresponding PMENn is set. 0 = PWMn signal is masked by 0. 1 = PWMn signal is masked by 1. DMA1BAH – PDMA XRAM Base Address (High Byte) MDAH[3:0] MAH[3:0] Address: FDH, Page 0...

- Page 150 ML51 Name Description PDMA1 PDMA1 interrupt priority low bit PDMA0 PDMA0 interrupt priority low bit PSMC SMC interrupt priority low bit Hard fault interrupt priority low bit PWKT WKT interrupt priority low bit Timer 3 interrupt priority low bit Serial port 1 interrupt priority low bit [5] EIP1 is used in combination with the EIPH1 to determine the priority of each interrupt source.

- Page 151 ML51 Name Description LVRDIS[7:0] LVR disable To first writing 5AH to the LVRDIS and immediately followed by a writing of A5H will disable LVR. Dec. 05, 2018 Page 151 of 401 Rev 1.00...

-

Page 152: General 80C51 System Control

ML51 GENERAL 80C51 SYSTEM CONTROL A or ACC – Accumulator (Bit-addressable) ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0 Address: E0H, All pages Reset value: 0000 0000b Name Description ACC[7:0] Accumulator The A or ACC register is the standard 80C51 accumulator for arithmetic operation. B –... - Page 153 ML51 Name Description DPL[7:0] Data pointer low byte This is the low byte of 16-bit data pointer. DPL combined with DPH serve as a 16-bit data pointer DPTR to access indirect addressed RAM or Program Memory. DPS (AUXR0.0) bit decides which data pointer, DPTR or DPTR1, is activated.

-

Page 154: Table 7.2-1 Instructions That Affect Flag Settings

ML51 Name Description These two bits select one of four banks in which R0 to R7 locate. Register Bank RAM Address 00H to 07H 08H to 0FH 10H to 17H 18H to 1FH Overflow flag OV is used for a signed character operands. For a ADD or ADDC instruction, OV will be set if there is a carry out of bit 6 but not out of bit 7, or a carry out of bit 7 but not bit 6. - Page 155 ML51 SMOD SMOD0 Address: 87H, All pagess POR reset value: 0001 000b, other reset value: 000U 0000b Name Description General purpose flag 1 The general purpose flag that can be set or cleared by user via software. General purpose flag 0 The general purpose flag that can be set or cleared by user via software.

-

Page 156: O Port Structure And Operation

ML51 I/O PORT STRUCTURE AND OPERATION The ML51 has a maximum of 43 general purpose I/O pins which 40 bit-addressable general I/O pins grouped as 5 ports, P0 to P4, and 7 general I/O pins grouped as P5. Each port has its port control register (Px register). -

Page 157: 9.2 Push-Pull Mode

ML51 The second pull-high is the “strong” pull-high. This pull-high is used to speed up 0-to-1 transitions on a quasi-bidirectional port pin when the port latch changes from logic 0 to logic 1. When this occurs, the strong pull-high turns on for two-CPU-clock time to pull the port pin high quickly. Then it turns off “very weak”... - Page 158 ML51 Dec. 05, 2018 Page 158 of 401 Rev 1.00...

-

Page 159: 9.3 Input-Only Mode

ML51 9.3 Input-Only Mode Input-only mode provides true high-impedance input path. Although a quasi-bidirectional mode I/O can also be an input pin, but it requires relative strong input source. Input-only mode also benefits to power consumption reduction for logic 0 input always consumes current from V if in quasi-bidirectional mode. -

Page 160: 9.6 Control Registers Of I/O Ports

ML51 Logical OR. (ORL direct, A and ORL direct, #data) Logical exclusive OR. (XRL direct, A and XRL direct, #data) Jump if bit = 1 and clear it. (JBC bit, rel) Complement bit. (CPL bit) Increment. (INC direct) Decrement. (DEC direct) DJNZ Decrement and jump if not zero. - Page 161 ML51 Name Description P1[7:0] Port 1 Port 1 is an maximum 8-bit general purpose I/O port. P2 – Port 2 (Bit-addressable) P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 Address: A0H, All pages Reset value: 1111 1111b Name Description P1[7:0] Port 2 Port 2 is a maximum 8-bit general purpose I/O port.

- Page 162 ML51 Name Description Reserved The bits are always read as 0. P5[6:0] Port 5 Port 5 is an maximum 7-bit general purpose I/O port. Dec. 05, 2018 Page 162 of 401 Rev 1.00...

-

Page 163: Gpio Mode Control

ML51 9.6.2 GPIO Mode Control These registers control GPIO mode, which is configurable among four modes: input-only, quasi- bidirectional, push-pull, or open-drain. Each pin can be configured individually. As default after reset all GPIO setting as input only mode. PnM1 – Port Mode Select 1 Register SFR Address Reset Value... -

Page 164: Gpio Multi-Function Select

ML51 [1] PnM1 and PnM2 [n:0~5] are used in combination to determine the I/O mode of each pin of P0. See Table 7.2-1 Modes Configuration for Different I/O PnM1.X PnM2.X I/O Type Quasi-bidirectional Push-pull Input-only (high-impedance) Open-drain 9.6.3 GPIO Multi-Function Select PnMF10 –... - Page 165 ML51 PnMF3 PnMF2 Name Description PnMF3[7:4] Pn.3 multi-function select PnMF2[3:0] Pn.2 multi-function select PnMF54 – Pn.5 and Pn.4 Multi-Function Select Register SFR Address Reset Value P0MF54 FBH, Page 2 0000_0000 b P1MF54 FFH, Page 2 0000_0000 b P2MF54 F4H, Page 2 0000_0000 b P3MF54 E9H, Page 2...

-

Page 166: Input Type

ML51 Name Description PnMF7[7:4] Pn.7 multi-function select PnMF6[3:0] Pn.6 multi-function select For example: As list P2.5 can define as following as anyone of the list function. If want to define as PWM0_CH0 output, please setting P2MF54 |= 0xB0. Pin Name Description P2.5 MFP0... -

Page 167: Output Slew Rate Control

ML51 PnS – Port n Schmitt Triggered Input Register SFR Address Reset Value 99H, Page 1 0000_0000 b 9BH, Page 1 0000_0000 b 9DH, Page 1 0000_0000 b ACH, Page 1 0000_0000 b BBH, Page 1 0000_0000 b BFH, Page 1 0000_0000 b PnS.7 PnS.6... -

Page 168: Pull-Up Resister Control

ML51 Name Description PnSR[7:0] P0.n slew rate 0 = Pn.x normal output slew rate. 1 = Pn.x high-speed output slew rate. 9.6.6 Pull-Up Resister Control Pull up resister for each I/O pin is configurable individually. But even enabled the pull up resister only effect when GPIO setting as input mode. - Page 169 ML51 P3DW 8DH, Page 1 0000_0000 b P4DW 8EH, Page 1 0000_0000 b P5DW 8FH, Page 1 0000_0000 b PnDW.7 PnDW.6 PnDW.5 PnDW.4 PnDW.3 PnDW.2 PnDW.1 PnDW.0 Name Description PnDW[7:0] P0.n pull-down enable 0 = Pn.x pull-down Disabled. 1 = Pn.x pull-down Enabled. Dec.

- Page 170 ML51 10 TIMER/COUNTER 0 AND 1 Timer/Counter 0 and 1 on ML51 are two 16-bit Timers/Counters. Each of them has two 8-bit registers those form the 16-bit counting register. For Timer/Counter 0 they are TH0, the upper 8-bit register, and TL0, the lower 8-bit register.

- Page 171 ML51 Name Description C/T ̅ Timer 1 Counter/Timer select 0 = Timer 1 is incremented by internal system clock. 1 = Timer 1 is incremented by the falling edge of the external pin T1. Timer 1 mode select Timer 1 Mode Mode 0: 13-bit Timer/Counter Mode 1: 16-bit Timer/Counter Mode 2: 8-bit Timer/Counter with auto-reload from TH1...

- Page 172 ML51 Name Description Timer 0 overflow flag This bit is set when Timer 0 overflows. It is automatically cleared via hardware when the program executes the Timer 0 interrupt service routine. This bit can be set or cleared by software. Timer 0 run control 0 = Timer 0 Disabled.

- Page 173 ML51 Address: 8CH, Page 0 Reset value: 0000 0000b Name Description TH0[7:0] Timer 0 high byte The TH0 register is the high byte of the 16-bit counting register of Timer 0. TL1 – Timer 1 Low Byte TL1[7:0] Address: 8BH, Page 0 Reset value: 0000 0000b Name Description...

- Page 174 ML51 TH1 – Timer 1 High Byte TH1[7:0] Address: 8DH, Page 0 Reset value: 0000 0000b Name Description TH1[7:0] Timer 1 high byte The TH1 register is the high byte of the 16-bit counting register of Timer 1. CKCON – Clock Control FASTWK PWMCKS T1OE...

-

Page 175: Figure 10.1-1 Timer/Counters 0 And 1 In Mode 0

ML51 (T1M) 1/12 TL0 (TL1) T0 (T1) pin Timer Interrupt (TF1) TR0 (TR1) TH0 (TH1) T0 (T1) pin GATE T0OE (T1OE) INT0 (INT1) pin Figure 10.1-1 Timer/Counters 0 and 1 in Mode 0 10.2 Mode 1 (16-Bit Timer) Mode 1 is similar to Mode 0 except that the counting registers are fully used as a 16-bit counter. Roll- over occurs when a count moves FFFFH to 0000H. -

Page 176: Figure 10.3-1 Timer/Counters 0 And 1 In Mode 2

ML51 ̅̅̅̅̅̅̅ (INT1 ̅̅̅̅̅̅̅ ) pins. The enabled by setting the TR0 (TR1) bit as 1 and proper setting of GATE and INT0 ̅̅̅̅̅̅̅ (INT1 ̅̅̅̅̅̅̅ ) pins are just the same as Mode 0 and 1. functions of GATE and INT0 (T1M) 1/12 TL0 (TL1) -

Page 177: Figure 10.4-1 Timer/Counter 0 In Mode 3

ML51 1/12 T0 pin Timer 0 Interrupt T0 pin T0OE GATE INT0 pin Timer 1 Interrupt T1 pin T1OE Figure 10.4-1 Timer/Counter 0 in Mode 3 Dec. 05, 2018 Page 177 of 401 Rev 1.00... -

Page 178: Figure 10.4-1 Timer 2 Block Diagram

ML51 11 TIMER 2 AND INPUT CAPTURE Timer 2 is a 16-bit up counter cascaded with TH2, the upper 8 bits register, and TL2, the lower 8 bit register. Equipped with RCMP2H and RCMP2L, Timer 2 can operate under compare mode and auto- ̅̅̅̅̅̅... - Page 179 ML51 T2CON – Timer 2 Control ̅̅̅̅̅̅ CM/RL2 Address: C8H, All pages Reset value: 0000 0000b Name Description Timer 2 overflow flag This bit is set when Timer 2 overflows or a compare match occurs. If the Timer 2 interrupt and the global interrupt are enable, setting this bit will make CPU execute Timer 2 interrupt service routine.

- Page 180 ML51 Name Description CAPCR Capture auto-clear This bit is valid only under Timer 2 auto-reload mode. It enables hardware auto-clearing TH2 and TL2 counter registers after they have been transferred in to RCMP2H and RCMP2L while a capture event occurs. 0 = Timer 2 continues counting when a capture event occurs.

- Page 181 ML51 TL2[7:0] Address: CCH, Page 0 Reset value: 0000 0000b Name Description TL2[7:0] Timer 2 low byte The TL2 register is the low byte of the 16-bit counting register of Timer 2. TH2 – Timer 2 High Byte TH2[7:0] Address: CDH, Page 0 Reset value: 0000 0000b Name Description...

-

Page 182: Figure 11.1-1 Timer 2 Auto-Reload Mode And Input Capture Module Functional Block Diagram

ML51 11.1 Auto-Reload Mode ̅̅̅̅̅̅ . In this mode RCMP2H and The Timer 2 is configured as auto-reload mode by clearing CM/RL2 RCMP2L registers store the reload value. The contents in RCMP2H and RCMP2L transfer into TH2 and TL2 once the auto-reload event occurs if setting LDEN bit. The event can be the Timer 2 overflow or one of the triggering event on any of enabled input capture channel depending on the LDTS[1:0] (T2MOD[1:0]) selection. -

Page 183: Figure 11.2-1 Timer 2 Compare Mode And Input Capture Module Functional Block Diagram

ML51 11.2 Compare Mode ̅̅̅̅̅̅ . In this mode RCMP2H and Timer 2 can also be configured as the compare mode by setting CM/RL2 RCMP2L registers serve as the compare value registers. As Timer 2 up counting, TH2 and TL2 match RCMP2H and RCMP2L, TF2 (T2CON.7) will be set by hardware to indicate a compare match event. - Page 184 ML51 11.3 Input Capture Module The input capture module along with Timer 2 implements the input capture function. The input capture module is configured through CAPCON0~2 registers. The input capture module supports 3-channel inputs (CAP0, CAP1, and CAP2). Each input channel consists its own noise filter, which is enabled via setting ENF0~2 (CAPCON2[6:4]).

- Page 185 ML51 11.4 Control Registers of Timer2 Following is the Timer2 input capture multi function pin define. Group Pin Name GPIO Type Description P1.3 MFP13 P1.0 MFP13 Input Capture channel 0 P3.3 MFP13 P1.2 MFP13 Input Capture channel 1 P3.2 MFP13 P1.1 MFP13 Input Capture channel 2...

- Page 186 ML51 Name Description CAPF0 Input capture 0 flag This bit is set by hardware if the determined edge of input capture 0 occurs. This bit should cleared by software. CAPCON1 – Input Capture Control 1 CAP2LS[1:0] CAP1LS[1:0] CAP0LS[1:0] Address: E2H, Page 1 Reset value: 0000 0000b Name Description...

- Page 187 ML51 Name Description ENF1 Enable noise filer on input capture 1 0 = Noise filter on input capture channel 1 Disabled. 1 = Noise filter on input capture channel 1 Enabled. ENF0 Enable noise filer on input capture 0 0 = Noise filter on input capture channel 0 Disabled. 1 = Noise filter on input capture channel 0 Enabled.

- Page 188 ML51 C1H[7:0] Address: E7H, Page 1 Reset value: 0000 0000b Name Description C1H[7:0] Input capture 1 result high byte The C1H register is the high byte of the 16-bit result captured by input capture 1. C2L – Capture 2 Low Byte C2L[7:0] Address: EDH, Page 1 Reset value: 0000 0000b...

-

Page 189: Figure 11.4-1 Timer 3 Block Diagram

ML51 12 TIMER 3 Timer 3 is implemented simply as a 16-bit auto-reload, up-counting timer. The user can select the pre- scale with T3PS[2:0] (T3CON[2:0]) and fill the reload value into RH3 and RL3 registers to determine its overflow rate. User then can set TR3 (T3CON.3) to start counting. When the counter rolls over FFFFH, TF3 (T3CON.4) is set as 1 and a reload is generated and causes the contents of the RH3 and RL3 registers to be reloaded into the internal 16-bit counter. - Page 190 ML51 Name Description T3PS[2:0] Timer 3 pre-scalar These bits determine the scale of the clock divider for Timer 3. 000 = 1/1. 001 = 1/2. 010 = 1/4. 011 = 1/8. 100 = 1/16. 101 = 1/32. 110 = 1/64. 111 = 1/128.

- Page 191 ML51 13 WATCHDOG TIMER (WDT) The ML51 provides one Watchdog Timer (WDT). It can be configured as a time-out reset timer to reset whole device. Once the device runs in an abnormal status or hangs up by outward interference, a WDT reset recover the system. It provides a system monitor, which improves the reliability of the system.

- Page 192 ML51 Name Description WDTR WDT run This bit is valid only when control bits in WDTEN[3:0] (CONFIG4[7:4]) are all 1. At this time, WDT works as a general purpose timer. 0 = WDT Disabled. 1 = WDT Enabled. The WDT counter starts running. WDCLR WDT clear Setting this bit will reset the WDT count to 00H.

-

Page 193: Figure 13.1-1 Wdt As A Time-Out Reset Timer

ML51 Table 11.4-1 Watchdog Timer-out Interval Under Different Pre-scalars WDPS.2 WDPS.1 WDPS.0 Clock Divider Scale WDT Time-Out Timing 1.66 ms 6.64 ms 13.31 ms 1/16 26.62 ms 1/32 53.25 ms 1/64 106.66 ms 1/128 213.12 ms 1/256 426.64 ms [1] This is an approximate value since the deviation of LIRC. Since the limitation of the maxima vaule of WDT timer delay. -

Page 194: Figure 13.2-1 Watchdog Timer Block Diagram

ML51 delays to expect a counter clearing by setting WDCLR to avoid the system reset by WDT if the device operates normally. If no counter reset by writing 1 to WDCLR during this 512-clock period, a WDT reset will happen. Setting WDCLR bit is used to clear the counter of the WDT. This bit is self-cleared for user monitoring it. - Page 195 ML51 However, the current consumption of Idle mode still keeps at a “mA” level. To further reducing the current consumption to “uA” level, the CPU should stay in Power-down mode when nothing needs to be served, and has the ability of waking up at a programmable interval. The ML51 is equipped with this useful function by WDT waking up.

-

Page 196: Figure 13.2-1 Self Wake-Up Timer Block Diagram

ML51 14 SELF WAKE-UP TIMER (WKT) The ML51 has a dedicated Self Wake-up Timer (WKT), which serves for a periodic wake-up timer in low power mode or for general purpose timer. WKT remains counting in Idle or Power-down mode. When WKT is being used as a wake-up timer, a start of WKT can occur just prior to entering a power management mode. - Page 197 ML51 Name Description WKTF WKT overflow flag This bit is set when WKT overflows. If the WKT interrupt and the global interrupt are enabled, setting this bit will make CPU execute WKT interrupt service routine. This bit is not automatically cleared via hardware and should be cleared via software.

- Page 198 ML51 15 SERIAL PORT (UART0 & UART1) The ML51 includes two enhanced full duplex serial ports enhanced with automatic address recognition and framing error detection. As control bits of these two serial ports are implemented the same. Generally speaking, in the following contents, there will not be any reference to serial port 1, but only to serial port 0.

-

Page 199: Figure 15.1-1 Serial Port Mode 0 Timing Diagram

ML51 Group Pin Name GPIO Type Description P2.3 MFP6 P1.1 MFP7 UART1_TXD UART1 data transmitter output pin. P0.3 MFP8 P5.0 MFP2 15.1 Mode 0 Mode 0 provides synchronous communication with external devices. Serial data centers and exits through RXD pin. TXD outputs the shift clocks. 8-bit frame of data are transmitted or received. Mode 0 therefore provides half-duplex communication because the transmitting or receiving data is via the same data line RXD. -

Page 200: Figure 15.2-1 Serial Port Mode 1 Timing Diagram

ML51 Reception is initiated by the condition REN (SCON.4) = 1 and RI (SCON.0) = 0. This condition tells the serial port controller that there is data to be shifted in. This process will continue until 8 bits have been received. -

Page 201: Figure 15.3-1 Serial Port Mode 2 And 3 Timing Diagram

ML51 2. Either SM2 (SCON.5) = 0, or the received stop bit = 1 while SM2 = 1 and the received data matches “Given” or “Broadcast” address. (For enhancement function, see Section 15.7“Multiprocessor Communication” and Section 15.8“Automatic Address Recognition”.) If these conditions are met, then the SBUF will be loaded with the received data, the RB8 (SCON.2) with stop bit, and RI will be set. -

Page 202: Table 15.5-1 Serial Port 0 Mode / Baudrate Description

ML51 1. RI (SCON.0) = 0, and 2. Either SM2 (SCON.5) = 0, or the received 9th bit = 1 while SM2 = 1 and the received data matches “Given” or “Broadcast” address. (For enhancement function, see Section 15.7“Multiprocessor Communication” and Section 15.8“Automatic Address Recognition”.) If these conditions are met, the SBUF will be loaded with the received data, the RB8(SCON.2) with the received 9 bit and RI will be set. -

Page 203: Table 15.5-2 Serial Port 1 Mode / Baudrate Description

ML51 Time1 TM1 (CKCON[3]) = 0 Time1 TM1 (CKCON[3]) = 1 Timer 3 scale 65536 (256 RL3) Time1 TM1 (CKCON[3]) = 0 Time1 ... - Page 204 ML51 (S1CON[7:6]) (T3CON[7]) divided by 12 Timer 3 scale 65536 (256 RL3) Timer 3 scale 65536 (256 RL3) divided by 64 divided by 32 Timer 3 ...

- Page 205 ML51 scale 65536 (256 RL3) SCON_1 = 0x52; //UART1 Mode1,REN_1=1,TI_1=1 T3CON = 0xF8; //T3PS2=0,T3PS1=0,T3PS0=0(Prescale=1), RH3 = value high byte RL3 = value low byte T3CON|= 0x08; Following list some popular baudrate value base on different Fsys and the deviation value: Fsys Value Baud Rate TH1 Value (Hex)

- Page 206 ML51 Fsys Value Baud Rate TH1 Value (Hex) RH3,RL3 Value (Hex) Baudrate Deviation 460800 FFFD 0.000000% 691200 FFFE 0.000000% 1382400 FFFF 0.000000% 4800 FF28 0.067515% 9600 FF94 0.067515% 19200 FFCA 0.067515% 16600000 38400 FFE5 0.067515% 57600 FFEE 0.067515% 115200 FFF7 0.067515% 4800 FF30...

- Page 207 ML51 The framing error bit, FE, is located in SCON.7. This bit normally serves as SM0. While the framing error accessing enable bit SMOD0 (PCON.6) is set 1, it serves as FE flag. Actually, SM0 and FE locate in different registers. The FE bit will be set 1 via hardware while a framing error occurs.

- Page 208 ML51 5. After all data bytes have been received, set SM2 back to 1 to wait for next address. SM2 has no effect in Mode 0, and in Mode 1 can be used to check the validity of the stop bit. For Mode 1 reception, if SM2 is 1, the receiving interrupt will not be issue unless a valid stop bit is received.

- Page 209 ML51 In the above example SADDR is the same and the SADEN data is used to differentiate between the two slaves. Slave 0 requires 0 in bit 0 and it ignores bit 1. Slave 1 requires 0 in bit 1 and bit 0 is ignored.

- Page 210 ML51 The use of don’t-care bits provides flexibility in defining the Broadcast address, however in most applications, interpreting the “don’t-cares” as all ones, the broadcast address will be FFH. On reset, SADDR and SADEN are initialized to 00H. This produces a “Given” address of all “don’t cares”...

- Page 211 ML51 Name Description 9th transmitted bit This bit defines the state of the 9th transmission bit in serial port 0 Mode 2 or 3. It is not used in Mode 0 or 1. 9th received bit The bit identifies the logic level of the 9th received bit in serial port 0 Mode 2 or 3. In Mode 1, RB8 is the logic level of the received stop bit.

- Page 212 ML51 Name Description SM2_1 Multiprocessor communication mode enable The function of this bit is dependent on the serial port 1 mode. Mode 0: No effect. Mode 1: This bit checks valid stop bit. 0 = Reception is always valid no matter the logic level of stop bit. 1 = Reception is valid only when the received stop bit is logic 1 and the received data matches “Given”...

- Page 213 ML51 Name Description SMOD Serial port 0 double baud rate enable Setting this bit doubles the serial port baud rate when UART0 is in Mode 2 or when Timer 1 overflow is used as the baud rate source of UART0 Mode 1 or 3. See Table 15.5-1 Serial Port 0 Mode / baudrate Description for details.

- Page 214 ML51 Name Description SBUF1[7:0] Serial port 1 data buffer This byte actually consists two separate registers. One is the receiving resister, and the other is the transmitting buffer. When data is moved to SBUF1, it goes to the transmitting buffer and is shifted for serial transmission.

- Page 215 ML51 SADEN[7:0] Address: B9H, Page 0 Reset value: 0000 0000b Name Description SADEN[7:0] Slave 0 address mask This byte is a mask byte of UART0 that contains “don’t-care” bits (defined by zeros) to form the device’s “Given” address. The don’t-care bits provide the flexibility to address one or more slaves at a time.

-

Page 216: Figure 16.1-1 Sc Controller Block Diagram

ML51 16 SMART CARD INTERFACE (SC) The ML51 provides Smart Card Interface controller (SC controller) with asynchronous protocal based on ISO/IEC 7816-3 standard. Software controls GPIO pins as the smartcard reset function and card detection function. This controller also provides UART emulation for high precision baud rate communication. - Page 217 ML51 Following is the Smart Card multi function pin define Group Pin Name GPIO Type Description P2.4 MFP13 P2.0 MFP7 P5.5 MFP2 SC_DAT / UART2 data receiver input pin. UART2_RXD P0.1 MFP6 P4.4 MFP8 P4.0 MFP8 Smart Card UART2 P2.5 MFP13 P2.1 MFP7...

- Page 218 ML51 Name Description T Mode 0 = T0 (ISO7816-3 T = 0 mode). 1 = T1 (ISO7816-3 T = 1 mode). The T mode controls the BGT (Block Guard Time). Block guard time means the minimum bit length between the leading edges of two consecutive characters between different transfer directions.

- Page 219 ML51 SCnCR1 – SC Control Register Register SFR Address Reset Value SC0CR1 D7H, Page 0 0000_0000 b SC1CR1 E7H, Page 2 0000_0000 b PBOFF TXDMAEN RXDMAEN CLKKEEP UARTEN Name Description Odd Parity Enable Bit 0 = Even number of logic 1’s are transmitted or check the data word and parity bits in receiving mode.

- Page 220 ML51 Name Description UARTEN UART Mode Enable Bit 0 = Smart Card mode. 1 = UART mode. Note1:When operating in UART mode, user must set CONSEL (SCnCR0[4]) = 0 and AUTOCEN(SCnCR0[3]) = 0. Note2:When operating in Smart Card mode, user must set UARTEN(SCnCR1 [0]) = 0. Note3:When UART is enabled, hardware will generate a reset to reset FIFO and internal state machine.

- Page 221 ML51 Register SFR Address Reset Value SC0ETURD0 DBH, Page 1 0111_0011 b SC1ETURD0 DBH, Page 2 0111_0011 b ETURDIV[7:0] Name Description ETURDIV[7:0] LSB bits of ETU Rate Divider The field indicates the LSB of clock rate divider. The real ETU is ETURDIV[11:0] + 1. Note1: ETURDIV[11:0] must be greater than 0x004.

- Page 222 ML51 Name Description ETURDIV MSB bits of ETU Rate Divider [11:8] The field indicates the MSB of clock rate divider. The real ETU is ETURDIV[11:0] + 1. Note1: ETURDIV[11:0] must be greater than 0x004. Note2: SCnETURD0 has to program first, then SCnETUDR1 . ScnIE –...

- Page 223 ML51 Name Description RDAIEN Receive Data Reach Interrupt Enable Bit This field is used to enable received data interrupt. 0 = Receive data interrupt Disabled. 1 = Receive data interrupt Enabled. ScnIS – SC Interrupt Status Register Register SFR Address Reset Value SC0IS DEH, Page 0...

- Page 224 ML51 SCnTSR – SC Transfer Status Register Register SFR Address Reset Value SC0TSR DFH, Page 0 0000_1010 b SC1TSR DFH, Page 2 0000_1010 b TXEMPTY TXOV RXEMPTY RXOV Name Description Transmit /Receive in Active Status Flag (Read Only) 0 = This bit is cleared automatically when TX/RX transfer is finished 1 = This bit is set by hardware when TX/RX transfer is in active.

- Page 225 ML51 Name Description RXOV RX Overflow Error Status Flag (Read Only) This bit is set when RX buffer overflow. Note: This bit is read only, but it can be cleared by writing 0 to it. 16.3 Operating Modes 16.3.1 Smart Card Mode The Smart Card Interface controller supports activation, cold reset, warm reset and deactivation sequence by software control.

- Page 226 ML51 Activation and Cold Reset The activation and cold reset sequence is shown in Figure 15.3-2 Set SC_RST to low by software programming to ‘0’ Set SC_PWR at high level by software programming to ‘1’ before timing T1 and SC_DAT at high level (reception mode) by software programming to ‘1’...

- Page 227 ML51 SC_RST Undefined SC_DAT Suggesting timing (Unit SC Clock) 400 <= T6 <= 40000 Time Comment SC_RST to SC_DAT Reception Mode SC_DAT Reception Mode to SC_RST Assert SC_RST start to ATR Appear 42106 Note: This value is measured by chip IO pin, the real value will depended on system design Figure 15.3-3 SC Warm Reset Sequence Deactivation The deactivation sequence is showedin Figure 15.3-4...

-

Page 228: Figure 16.4-1 Sc Data Character

ML51 Set UARTEN (SCCR2[0]) bit to enter UART mode. Fill “0” to CONSEL (SCnCR1[4]) and AUTOCEN (SCnCR1[3]) field. (In UART mode, those fields must be “0”) Select the UART baud rate by setting ETURDIV[11:0] ({SCnETURD1[3:0]:SCnETURD0[7:0]}) fields. For example, if smartcard module clock is 12 MHz and target baud rate is 115200bps, ETURDIV should fill with (12000000 / 115200 –... -

Page 229: Figure 16.4-2 Initial Character Ts

ML51 Start Start Character T0 Direct Convention t = 12 ~ 9600 ETU Start Start Character T0 Inverse Convention t = 12 ~ 9600 ETU Direct Convention 0_ 1101_ 1100_ 1 (0x3B) 0_ 1100_ 0000_ 1 (0x3F) Inverse Convention Figure 16.4-2 Initial Character TS 16.4.2 Error Signal and Character Repetition According to ISO7816-3 T=0 mode description, as shown in Figure 16.4-3,if the receiver receives a... -

Page 230: Figure 16.4-4 Transmit Direction Block Guard Time Operation

ML51 In transmit direction, the smart card sends data to smart card host controller, first. After the period is greater than (16.5 or 22.5, by T bit setting), the smart card host controller begin to send the data. Last Receiver Data Transmitter Data Block Guard Time Figure 16.4-4 Transmit Direction Block Guard Time Operation... -

Page 231: Figure 17.1-1 Spi Block Diagram

ML51 17 SERIAL PERIPHERAL INTERFACE (SPI) The ML51 provides two Serial Peripheral Interface (SPI) block to support high-speed serial communication. SPI is a full-duplex, high-speed, synchronous communication bus between microcontrollers or other peripheral devices such as serial EEPROM, LCD driver, or D/A converter. It provides either Master or Slave mode, high-speed rate up to , transfer complete and write collision flag. -

Page 232: Figure 17.1-2 Spi Multi-Master, Multi-Slave Interconnection

ML51 register is free to accept a second data, as the first received data will be transferred to the read data buffer. The 2 set, 16 pins of SPI interface and 4 pins of SPI0 interface which are Master-In/Slave-Out (MISO), ̅̅̅̅... -

Page 233: Figure 17.1-3 Spi Single-Master, Single-Slave Interconnection

ML51 Figure 17.1-2 shows a typical interconnection of SPI devices. The bus generally connects devices together through three signal wires, MOSI to MOSI, MISO to MISO, and SPCLK to SPCLK. The Master devices select the individual Slave devices by using four pins of a parallel port to control the ̅̅̅̅... - Page 234 ML51 17.2 SPI Protocol Registers Following is the SPI multi function pin define list: Group Pin Name GPIO Type Description P0.2 MFP3 SPI0_CLK SPI0 serial clock pin. P6.2 MFP4 P0.1 MFP3 SPI0_MISO SPI0 MISO (Master In, Slave Out) pin. P6.1 MFP4 SPI0 P0.0...

- Page 235 ML51 Name Description SPIEN SPI enable 0 = SPI function Disabled. 1 = SPI function Enabled. LSBFE LSB first enable 0 = The SPI data is transferred MSB first. 1 = The SPI data is transferred LSB first. MSTR Master mode enable This bit switches the SPI operating between Master and Slave modes.

- Page 236 ML51 Name Description SPR[1:0] SPI clock rate select These two bits select four grades of SPI clock divider. The clock rates below are illustrated under = 24 MHz condition. SPR3 SPR2 SPR1 SPR0 Divider SPI clock rate 12M bit/s 6M bit/s 3M bit/s 1.5M bit/s 750k bit/s...