Table of Contents

Advertisement

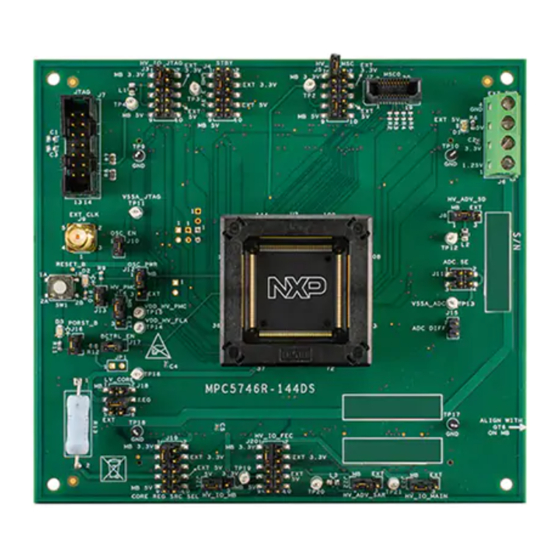

NXP Semiconductors

Data Sheet: Technical Data

SPC5746R Microcontroller

Data Sheet

Features

• This document provides electrical specifications, pin

assignments, and package diagrams for the MPC5746R

series of microcontroller units (MCUs).

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

Document Number MPC5746R

MPC5746R

• For functional characteristics, see the MPC5746R

Microcontroller Reference Manual.

Rev. 6, 06/2017

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for NXP Semiconductors MPC5746R

- Page 1 Rev. 6, 06/2017 MPC5746R SPC5746R Microcontroller Data Sheet Features • For functional characteristics, see the MPC5746R Microcontroller Reference Manual. • This document provides electrical specifications, pin assignments, and package diagrams for the MPC5746R series of microcontroller units (MCUs). NXP reserves the right to change the production detail specifications as may be...

-

Page 2: Table Of Contents

20.1 General notes for specifications at maximum junction 16.1.6 Power up/down sequencing........53 temperature................89 17 Flash memory specifications..............54 21 Ordering information................. 90 17.1 Flash memory program and erase specifications....54 22 Revision history................. 91 SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 3: Introduction

Introduction 1 Introduction The MPC5746R family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive- focused products designed for flexibility to support a variety of applications. The advanced and cost-efficient host processor core of the MPC5746R automotive controller family complies with the Power Architecture embedded category. -

Page 4: Block Diagram

Introduction 1.1 Block diagram MPC5746R Computational Shell - Fast Domain 200MHz Double INTC Nexus JTAGM JTAGC Aurora Router Safety Lake SWT_1 SWT_0 STM_1 STM_0 E200 z425 - 200 MHz E200 z425 - 200 MHz E200 z424 - 200 MHz Nexus3p... -

Page 5: Package Pinouts And Signal Descriptions

PFLASH PRAM 2 x SMPU 2x XBIC 2x XBAR PBRIDGE_0 Figure 2. Peripherals allocation 2 Package pinouts and signal descriptions For package pinouts and signal descriptions, refer to the Reference Manual. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 6: Absolute Maximum Ratings

Relative to V –0.3 — SS_HV_IO Relative to V — DD_HV_IO Maximum DC injection current for digital Per pin, applies to all digital pins –5 INJD Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 7: Electromagnetic Compatibility (Emc)

13. Moisture sensitivity per JEDEC test method A112. 4 Electromagnetic Compatibility (EMC) EMC measurements to IC-level IEC standards are available from NXP on request. 5 Electrostatic discharge (ESD) The following table describes the ESD ratings of the device. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 8: Operating Conditions

125.0 °C ambient Voltage External core supply voltage LVD/HVD enabled — 1.32 DD_LV 4, 5, LVD/HVD disabled 1.18 — 1.38 I/O supply voltage — DD_HV_IO_MAIN Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 9 4. Maximum core voltage is not permitted for entire product life. See absolute maximum rating. 5. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 10 A _BD Voltage Buddy core supply voltage — 1.18 — 1.32 DD_LV_BD Buddy I/O supply voltage — — DD_HV_IO_B Buddy slew rate on power supply pins — — — V/ms RAMP_BD SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 11: Dc Electrical Specifications

DC electrical specifications 7 DC electrical specifications The following table describes the DC electrical specifications. Table 5. DC electrical specifications Value Symbol Parameter Conditions Unit Maximum operating MPC5746R/ — — DD_LV current on the V MPC5745R DD_LV supply MPC5743R/ —... -

Page 12: O Pad Specification

Each I/O pin on the device supports specific drive configurations. See the signal description table in the device reference manual for the available drive configurations for each I/O pin. 8.1 Input pad specifications SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 13 1. Supported input levels vary according to pad types. Pad type "pad_sr_hv" supports only the CMOS input level, while pad type "pad_isatww_st_hv" supports TTL and CMOS levels. Refer to the IO spreadsheet attached to the Reference Manual for the pad type of each pin. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 14 — DD_HV_IO 1. Weak pull-up/down is enabled within tWK_PU = 1 µs after internal/external reset has been asserted. Output voltage will depend on the amount of capacitance connected to the pin. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 15: Output Pad Specifications

Figure 4. Weak pull-up electrical characteristics definition Analog input leakage and pull up/down information is located in the ADC input description section. 8.2 Output pad specifications The following figure provides the description of output DC electrical characteristics. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 16 4.5V < VDD_HV_IO < 5.0V — — 0.2 * VDD_H MSCR[OERC] = 11, IOL = 48mA V_IO MSCR[OERC] = 10, IOL = 24mA MSCR[OERC] = 01, IOL = 12mA Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 17: I/O Pad Current Specifications

Table 10. I/O current consumption at VDD_HV_IO = 3.6 V Cell VDD_HV_IO Load (pF) Period1 (ns) MSCR[OERC] Idde AVG (mA) Idde RMS (mA) pad_sr_hv 3.63 Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 18: Reset Pad (Porst, Reset) Electrical Characteristics

MAXSEG "Device operating conditions". Note The MPC5746R I/O Signal Description and Input Multiplexing Tables are contained in a Microsoft Excel workbook file attached to the Reference Manual. 9 Reset pad (PORST, RESET) electrical characteristics The device implements a dedicated bidirectional reset pin (PORST). - Page 19 . Device state is unknown. It may NFRST either be reset or remains in current state depending on extra condition (temperature, voltage, device). • c) PORST asserted for longer than W . Device is under reset. NFRST SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 20 Input hysteresis CMOS 3.5 V < VDD_HV_IO < 5.5 V 0.1 * — — PORST DD_HV_IO Minimum supply for strong pulldown — — — DD_POR activation Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 21 ESR1 input not filtered pulse — — — NFNMI 1. An external 4.7 KOhm pull-up resistor is recommended to be used with the PORST and RESET pins for fast negation of the signals. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 22: Oscillator And Fmpll

— PLL0 1. PLL0IN clock retrieved directly from either internal RCOSC or external FXOSC clock. Input characteristics are granted when using internal RCOSC or external oscillator is used in functional mode. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 23 4.75 5.25 S_XTAL on XTAL pin 5.25 5.75 Oscillator Transconductance = -40 °C to 150 ≤ 8 MHz mA/V XTAL °C ≤ 20 MHz XTAL Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 24 )/XTAL (C (pF) EXTAL XTAL 00000 00001 00010 00011 00100 00101 00110 00111 01000 01001 01010 10.3 01011 11.2 01100 12.2 01101 13.1 01110 14.0 Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 25 Startup time to reach within fvar_noT Factory trimming — — µs start_noT already applied Startup time to reach within f Factory trimming — — µs start_T var_T already applied Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 26: Adc Modules

< 5.5V DD_HV_IO resistance 100KΩ 3.0V < V < 5.5V DD_HV_IO 5KΩ 3.0V < V < 5.5V DD_HV_IO ΔPUPD RPUPD pull up/down 3.0V < V < 5.5V — — DD_HV_IO resistance mismatch SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 27: Sar Adc

(5) Center of a step of the actual transfer (3 ) curve 1 LSB (ideal) 4089 4090 4091 4092 4093 4094 4095 (LSB in(A) ideal Offset Error OSE Figure 10. ADC characteristics and error definitions SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 28 Differential non-linearity — –1 — Offset error — –6 — Gain error — –6 — Input (double ADC Max leakage 150 °C — — channel) Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 29: S/D Adc

• The ADC performance specifications are not guaranteed if two or more ADCs simultaneously sample the same shared channel. 11.3 S/D ADC The SD ADCs are Sigma Delta 16-bit analog-to-digital converters with 333 Ksps maximum output rate. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 30 After calibration — — Signal to noise ratio in 4.5 < V < 5.5 — — DIFF150 DD_HV_ADV_SD differential mode 150 DD_HV_ADR_D DD_HV_ADV_D ksps output rate Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 31 DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 2 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 4 < 150 °C Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 32 DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 8 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_DS DD_HV_ADV_SD GAIN = 16 < 150 °C Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 33 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 2 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 34 — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 8 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_DS DD_HV_ADV_SD = 16 < 150 °C Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 35 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 2 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 36 — DD_HV_ADV_SD DD_HV_ADR_SD DD_HV_ADV_SD GAIN = 8 < 150 °C 4.5 < V < 5.5 — — DD_HV_ADV_SD DD_HV_ADR_DS DD_HV_ADV_SD = 16 < 150 °C Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 37 GROUP ADCD_M OSR = 24 — — 235.5 Tclk OSR = 28 — — OSR = 32 — — 314.5 OSR = 36 — — Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 38 Overdrive recovery time After input comes within range from — — 2*δ — ODRECOVERY saturation GROUP ADCD_S HPF = ON HPF = OFF — — 2*δ — GROUP Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 39: Temperature Sensor

14. This capacitance does not include pin capacitance, that can be considered together with external capacitance, before sampling switch. 12 Temperature sensor The following table describes the temperature sensor electrical characteristics. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 40: Lvds Fast Asynchronous Serial Transmission (Lfast) Pad

The same LVDS pad is used for the Microsecond Channel (MSC) and DSPI LVDS interfaces, with different characteristics given in the following tables. 13.1 LFAST interface timing diagrams SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 41 150 mV p-p (MSC/SIPI) Data Bit Period T = 1 / F DATA Min. common mode input at RX 150 mV Signal excursions below this level NOT allowed Figure 12. LFAST timing definition SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 42: Lfast And Msc /Dspi Lvds Interface Electrical

The LVDS pad electrical characteristics in this table apply to both the LFAST and High- speed Debug (HSD) LVDS pad, and the MSC/DSPI LVDS pad except where noted in the conditions. All LVDS pad electrical characteristics are valid from -40 °C to 150 °C. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 43 — — Mbps DATA Common mode voltage — 1.08 — 1.32 Differential output voltage swing (terminated) — Rise/Fall time (10%–90% of swing) — 0.26 — Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 44 4. All LFAST and High-Speed Debug LVDS pad electrical characteristics are valid from -40 °C to 150 °C. NOTE For optimum LVDS performance, it is recommended to set the neighbouring GPIO pads to use Weak Drive. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 45: Lfast Pll Electrical Characteristics

PLL phase lock — — — µs LOCK ΔPER Input reference clock single period jitter Single period, — — (peak to peak) = 10 MHz RF_REF Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 46: Aurora Lvds Electrical Characteristics

15 Aurora LVDS electrical characteristics The following table describes the Aurora LVDS electrical characteristics. All Aurora electrical characteristics are valid from -40 °C to 150 °C. All specifications valid for maximum transmit data rate F SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 47: Power Management Pmc Por Lvd Sequencing

The following NPN transistors are recommended for use with the on-chip voltage regulator controller: ON Semiconductor NJD2873. The collector of the external transistor is preferably connected to the same voltage supply source as the V DD_HV_PMC pin. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 48: Power Management Integration

Base to emitter voltage 0.95 Minimum voltage at transistor collector 16.1.2 Power management integration In order to ensure correct functionality of the device, it is recommended to follow the integration scheme shown below. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 49 Minimum VDD_HV_IO external — — — µF HV_IO capacitance Minimum V external capacitance — µF HV_FLA DD_HV_FLA Minimum V external — — µF HV_ADC_SA DD_HV_ADV_SAR capacitance Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 50: Regulator Example For The Njd2873 Transistor

16.1.3 Regulator example for the NJD2873 transistor VDD_HV_PMC The bypass transistor VRC_CTL MUST be operated out of saturation region. VDD_LV Mandatory decoupling capacitor network VRC_CTL capacitor: may or may not be required Figure 18. Regulator example SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 51: Regulator Example For The 2Scr574D Transistor

Figure 19. Regulator example 16.1.5 Device voltage monitoring The LVD/HVDs for the device and their levels are given in the following table. Voltage monitoring threshold definition is provided in the following figure. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 52 Trim Symbol Parameter Conditions Unit bits . Up Opt. POR085_c LV internal supply power on Rising voltage (power up) Enab reset Falling voltage (power down) Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 53: Power Up/Down Sequencing

VDD_HV_ADR_S AR=0 VDD_HV_ADV_S AR=0 VDD_S TDBY VDD_LV VDD_HV_PMC VDD_HV_IO_MAIN VDD_HV_IO_JTAG VDD_HV_IO_FEC VDD_HV_IO_MS C VDD_HV_ADR_S D Amps VDD_HV_ADV_S D VDD_HV_ADR_S AR Amps VDD_HV_ADV_S AR Figure 21. Device supply relation during power-up/power-down sequence SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 54: Flash Memory Specifications

25 °C. Typical program and erase times may be used for throughput calculations. 3. Conditions: ≤ 150 cycles, nominal voltage. 4. Plant Programing times provide guidance for timeout limits used in the factory. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 55: Flash Memory Array Integrity And Margin Read

Number of program/erase cycles per block — 1,000 250,000 for 256 KB blocks. cycles Data Minimum data retention. Blocks with 0 - 1,000 P/E — Years retention cycles. Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 56: Data Retention Vs Program/Erase Cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 57: Flash Memory Ac Timing Specifications

UT0-AID bit is set. This time also applies to the plus four plus four UT0-AISUS to UT0-AID setting in the event of a Margin Read system system suspend request. clock clock periods periods SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 58: Flash Read Wait State And Address Pipeline Control Settings

TCKRISE TMS, TDI data setup time — TMSS TDIS TMS, TDI data hold time — TMSH TDIH TCK low to TDO data valid — TDOV Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 59 2. Applies to all pins, limited by pad slew rate. Refer to IO delay and transition specification and add 20 ns for JTAG delay. Figure 22. JTAG test clock input timing SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 60 AC specifications TMS, TDI Figure 23. JTAG test access port timing JCOMP Figure 24. JTAG JCOMP timing SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 61: Nexus Interface Timing

— EVTIPW EVTO Pulse Width — EVTOPW TCK cycle time — TCYC Absolute minimum TCK cycle time (TDO sampled on posedge of — TCYC TCK) Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 62 7. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay. Figure 26. Nexus output timing EVTI EVTO Figure 27. Nexus event trigger and test clock timings SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 63: Aurora Lvds Interface Timing

2. Startup time is defined as the time taken by LVDS transmitter for settling after its pwr_down (power down) has been deasserted. Here it is assumed that current reference is already stable (see Bias start-up time). LVDS functionality is guaranteed only after the startup time. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 64 0.17 Transmit lane total jitter — 0.35 Differential output skew — Lane to lane output skew — 1000 Aurora lane unit interval 625 Mbps 1600 1600 1.25Gbps 1. ± 100 PPM SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 65: Dspi Timing With Cmos And Lvds

Full duplex – Classic timing (Table Full duplex – Modified timing (Table Output only mode (SCK/SOUT/PCS) (Table 40 Table Output only mode TSB mode (SCK/SOUT/PCS) (Table LVDS (Master mode) Full duplex – Modified timing (Table SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 66: Dspi Master Mode Full Duplex Timing With Cmos

PCS = 0 pF ) - 35 — SCK = 50 pF PCS medium and PCS = 0 pF ) - 35 — SCK strong Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 67 SCK clock mode is selected, in which case, N is automatically set to 0 clock cycles (PCS and SCK are driven by the same edge of DSPI_CLKn). 4. t is the period of DSPI_CLKn clock, the input clock to the DSPI module. Maximum frequency is 100 MHz (min t = 10 ns). SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 68 (CPOL = 0) SCK Output (CPOL = 1) First Data Data Last Data First Data Data Last Data SOUT Figure 30. DSPI CMOS master mode – classic timing, CPHA = 0 SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 69 Characteristic Condition Value Unit Pad drive Load (C SCK cycle time SCK drive strength Very strong 25 pF 33.0 — Strong 50 pF 80.0 — Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 70 31.0 — Medium 50 pF 52.0 — SIN hold time SIN hold time from SCK drive strength Very strong 0 pF -1 + (P — Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 71 7. PCSx and PCSS using same pad configuration. 8. Input timing assumes an input slew rate of 1 ns (10% - 90%) and uses TTL voltage thresholds. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 72 PCSx SCK Output (CPOL=0) SCK Output (CPOL=1) Data First Data Last Data Data Data SOUT Last Data First Data Figure 34. DSPI CMOS master mode – modified timing, CPHA = 1 SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 73 25 pF differential SIN setup time to SCK drive strength LVDS 15 pF — CPHA = 1 to 25 pF differential SIN Hold Time Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 74 DSPI_MCR[SMPL_PT]. The value must be 0, 1 or 2. If the baud rate divide ratio is /2 or /3, this value is automatically set to 1. 8. SOUT Data Valid and Data hold are independent of load capacitance if SCK and SOUT load capacitances are the same value. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 75 First Data Last Data Data SOUT First Data Last Data Figure 37. DSPI LVDS master mode – modified timing, CPHA = 1 18.2.1.4 DSPI master mode – output only Table 43 SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 76 • TSB = 1 or ITSB = 1 automatically selects MTFE = 1 and CPHA = 1. • All output timing is worst case and includes the mismatching of rise and fall times of the output pads. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 77 3. With TSB mode or Continuous SCK clock mode selected, PCS and SCK are driven by the same edge of DSPI_CLKn. This timing value is due to pad delays and signal propagation delays. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 78: Dspi Cmos Slave Mode

— Time Strong 50 pF — (SS inactive to SOUT Medium 50 pF — High-Z or invalid) Data Setup Time for — — — Inputs Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 79 F irst D a ta L a s t D a ta S IN Figure 39. DSPI Slave Mode - Modified transfer format timing (MFTE = 0/1) — CPHA = 0 SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 80: Fec Timing

Table 46. MII-lite receive signal timing Value Unit Spec Characteristic RXD[3:0], RX_DV, RX_ER to RX_CLK setup — RX_CLK to RXD[3:0], RX_DV, RX_ER hold — RX_CLK pulse width high RX_CLK period RX_CLK pulse width low RX_CLK period SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 81: Mii-Lite Transmit Signal Timing

= 25 p , where CL is the external load to the device. The internal package capacitance is accounted for, and does not need to be subtracted from the 25 p value. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 82: Mii-Lite Async Inputs Signal Timing

(TTL levels) to the valid input and output levels, 0.8 V and 2.0 V (TTL levels). For 5 V operation, timing is referenced from MDC = 50% to 2.2 V/3.5 V input and output levels. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 83: Rmii Serial Management Channel Timing

The FEC functions correctly with a maximum MDC frequency of 2.5 MHz. Table 50. RMII serial management channel timing Value Unit Spec Characteristic MDC falling edge to — MDIO output invalid (minimum propagation delay) Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 84: Rmii Receive Signal Timing (Rxd[1:0], Crs_Dv)84

RX_CLK frequency, which is half that of the REF_CLK frequency. All timing specifications are referenced from REF_CLK = 1.4 V to the valid input levels. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 85: Rmii Transmit Signal Timing (Txd[1:0], Tx_En)

Table 52. RMII transmit signal timing Value Unit Spec Characteristic REF_CLK to TXD[1:0], TX_EN invalid — REF_CLK to TXD[1:0], TX_EN valid — REF_CLK pulse width high REF_CLK period REF_CLK pulse width low REF_CLK period SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 86: Uart Timings

MIPW 19 Obtaining package dimensions Package dimensions are provided in package drawings. To find a package drawing, go to http://www.nxp.com and perform a keyword search for the drawing's document number. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 87: Thermal Characteristics

Junction to Ambient Natural Convection Single layer board (1s) 49.9 °C/W θJA 1, 2, Junction to Ambient Natural Convection Four layer board (2s2p) 33.8 °C/W θJA Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 88 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

-

Page 89: General Notes For Specifications At Maximum Junction

When a heat sink is used, the thermal resistance is expressed in the following equation as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance: θJA θJC θCA SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 90: Ordering Information

2M / 128KB 176 LQFP 200 MHz SPC5743RK1MLQ5 Sample PD 2M / 128 KB 144 LQFP 200 MHz PPC5746R2K1MMZ5A Sample ED 4M / 256 KB 1 MB 292 MAPBGA 200 MHz SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... -

Page 91: Revision History

"32 KB RAM Standby Regulator Current" (was DDSTBY_REG "Standby Leakage Current"); changed condition to "V @1.2 V to 5.9 V, Tj = DDSTBY 150C" (was "V @1.3 V...") DDSTBY Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors... - Page 92 | specification added footnote to parameter and added new row with more detailed GAIN "After calibration" conditions. • Moved footnote "S/D ADC is functional in the range..." from the Z to the SNR parameters. Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 93 • LVD_HV • HVD_HV • LVD_IO • LVD_SAR • Removed following specs: • LVD_FLASH • HVD_FLASH • LVD_MSC_3V3 • LVD_MSC_5V0 • LVD_FEC_5V0 • LVD_JTAG • HVD_SAR Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 94 Freescale website. Drawings removed from this document. In section Thermal characteristics • Added table for 144 LQFP. Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 95 In section DC electrical specifications • In Table 5 • IDD_LV spec: • MPC5746R/MPC5745R Max value changed to 700 mA. • MPC5743R/MPC5742R Max value changed to 610 mA. • IDDSTBY_ON TA=40°C and TA=85°C values updated. • IVDDA values updated. In section...

- Page 96 • For the FEC I/O supply voltage, MSC I/O supply voltage, and JTAG I/O supply voltage specs, removed the LVD enabled/disabled distinction. • Added footnote to I MAXSEG In section I/O pad current specifications Table continues on the next page... SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 97 Changed Freescale to NXP throughout the datasheet. Ordering information added rows for SPC5746RK1MLU3, SPC5745RK1MMT5 and SPC5743RK1MLU5. Table 3 added footnote in V DD_HV_PMC Table 28 for the rowset C changed the Minimum and Typical values. HV_FLA SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017 NXP Semiconductors...

- Page 98 Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2013–2017 NXP B.V. Document Number MPC5746R Revision 6, 06/2017...

Need help?

Do you have a question about the MPC5746R and is the answer not in the manual?

Questions and answers