Table of Contents

Advertisement

Quick Links

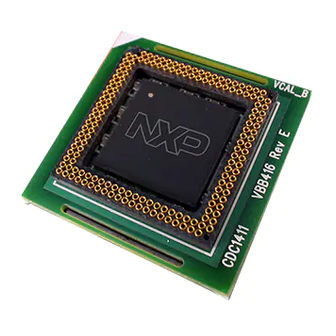

Freescale Semiconductor

MPC5566 Microcontroller

Reference Manual

This MPC5566 Reference Manual set consists of the following files:

•

MPC5566 Reference Manual Addendum, Rev 2

•

MPC5566 Microcontroller Reference Manual, Rev 2

© Freescale Semiconductor, Inc., 2012. All rights reserved.

MPC5566RM

Rev. 2.1, 05/2012

Advertisement

Chapters

Table of Contents

Summary of Contents for NXP Semiconductors MPC5566

- Page 1 Freescale Semiconductor MPC5566RM Rev. 2.1, 05/2012 MPC5566 Microcontroller Reference Manual This MPC5566 Reference Manual set consists of the following files: • MPC5566 Reference Manual Addendum, Rev 2 • MPC5566 Microcontroller Reference Manual, Rev 2 © Freescale Semiconductor, Inc., 2012. All rights reserved.

-

Page 2: Mpc5566 Reference Manual,

MPC5566RM. For convenience, the addenda items are grouped by revision. Please check our website http://www.freescale.com/powerarchitecture for the latest updates. The current version available of the MPC5566 Microcontroller Reference Manual is Revision 2.0. © Freescale Semiconductor, Inc., 2009–2012. All rights reserved. - Page 3 Data Register Empty and LIN Transmit Data Ready DMA requests eSCIB_COMBTX ESCIB.SR[TDRE] || eSCIB combined DMA ESCIB.SR[TC] || request of the Transmit ESCIB.SR[TXRDY] Data Register Empty and LIN Transmit Data Ready DMA requests MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor...

-

Page 4: Mpc5566 Reference Manual Addendum, Rev

Peripheral bridge A off-platform PBRIDGE_A_OPACR1 32-bit Base + 0x0044 peripheral access control register 1 Peripheral bridge A off-platform PBRIDGE_A_OPACR2 32-bit Base + 0x0048 peripheral access control register 2 Reserved — — Base + (0x004C- 0xC3F7_FFFF) MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor... - Page 5 Peripheral bridge B off-platform PBRIDGE_B_OPACR2 32-bit Base + 0x0048 peripheral access control register 2 Peripheral bridge B off-platform PBRIDGE_B_OPACR3 32-bit Base + 0x004C peripheral access control register 3 Reserved — — (Base + 0x0050)- 0xFFF0_3FFF) MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor...

- Page 6 • Bit 22-23–TRIGSELC: Correct the input select description as follows: 00: Replace the term “Invalid value” with “No Trigger” • Bit 30-31–TRIGSELD: Correct the input select description as follows: 00: Replace the term “Invalid value” with “No Trigger” MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor...

- Page 7 INTC as an interrupt event setting the flag bit. MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor...

-

Page 8: Table Of Contents

INTC_CPR Read INTC_IACKR Write INTC_EOIR INTVEC in INTC_IACKR PRI in INTC_CPR Last In / First Out Entry in LIFO Peripheral Interrupt Request 100 Peripheral Interrupt Request 200 Raised Priority Preserved Timing Diagram MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor... - Page 9 “To use the 8–20 MHz OSC, the PLL predivider must be configured for divide-by-two operation (FMPLL_SYNCR)” by tying PLLCFG[2] low (set PREDIV to 0b000).” Revision history Table 2 provides a revision history for this document. MPC5566 Reference Manual Addendum, Rev. 2 Freescale Semiconductor...

- Page 10 • Clarified note in the INTC Interrupt Acknowledge Register • Added a note in the INTC Memory Map table • Clarified note at the end of the MPC5566 Interrupt Request Sources table • Added a paragraph to the Section 10.4.2.1.4, “Priority Comparator Submodule”...

- Page 11 How to Reach Us: Home Page: www.freescale.com Web Support: http://www.freescale.com/support USA/Europe or Locations Not Listed: Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany...

- Page 12 MPC5566 Microcontroller Reference Manual Devices Supported: MPC5566 MPC5566 RM Rev. 2.0 23 Apr 2008...

- Page 13 Fax: 303-675-2150 Freescale™ and the Freescale logo are trademarks of Freescale LDCForFreescaleSemiconductor@hibbertgroup.com Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2008. All rights reserved. MPC5566 RM Rev. 2.0 23 Apr 2008...

- Page 14 RSTOUT ........... . . 2-19 2.3.1.3 Phase Locked-Loop Configuration / External Interrupt Request / GPIO MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 15 DATA[25]_FEC_RX_DV_GPIO[53] ....... 2-22 2.3.2.17 External Data / Ethernet Transmit Enable / GPIO MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 16 MDO[3:1] ........... . 2-25 2.3.3.6 Nexus Message Data Out / GPIO MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 17 SINA_PCSC[2]_GPIO[94] ........2-27 MPC5566 Reference Manual, Rev. 2...

- Page 18 AN[5]_DAN2– ..........2-31 MPC5566 Reference Manual, Rev. 2...

- Page 19 ETPUA[5]_ETPUA[17]_GPIO[119] ....... 2-34 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 20 ETPUA[30]_PCSC[3]_GPIO[144] ....... . . 2-37 2.3.9.30 eTPU A Channel / DSPI C / GPIO MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 21 GPIO[206:207] ..........2-40 MPC5566 Reference Manual, Rev. 2...

- Page 22 VPP ............2-43 MPC5566 Reference Manual, Rev. 2...

- Page 23 3.3.1.3 Effective to Real Address Translation ....... 3-16 MPC5566 Reference Manual, Rev. 2...

- Page 24 4.4.2.3.3Loss-of-Lock Reset ........4-8 MPC5566 Reference Manual, Rev. 2...

- Page 25 Overview ............6-3 MPC5566 Reference Manual, Rev. 2...

- Page 26 6.3.1.29 Pad Configuration Registers 53 (SIU_PCR53) ..... . . 6-33 6.3.1.30 Pad Configuration Registers 54 (SIU_PCR54) ..... . . 6-34 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 27 6.3.1.74 Pad Configuration Register 108 (SIU_PCR108) ..... . 6-61 6.3.1.75 Pad Configuration Register 109 (SIU_PCR109) ..... . 6-62 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 28 6.3.1.119 Pad Configuration Registers 211–212 (SIU_PCR211–SIU_PCR212) ..6-91 6.3.1.120 Pad Configuration Register 213 (SIU_PCR213) ..... 6-91 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 29 6.3.1.164 Chip Configuration Register (SIU_CCR) ......6-115 6.3.1.165 External Clock Control Register (SIU_ECCR) ..... 6-116 MPC5566 Reference Manual, Rev. 2 xviii...

- Page 30 Introduction ..............8-1 MPC5566 Reference Manual, Rev. 2...

- Page 31 9.2.2.12 eDMA Clear DONE Status Bit Register (EDMA_CDSBR) ... . . 9-18 9.2.2.13 eDMA Interrupt Request Registers (EDMA_IRQRH, EDMA_IRQRL) . . . 9-19 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 32 10.3.1.3 INTC Interrupt Acknowledge Register (INTC_IACKR) ....10-11 10.3.1.4 INTC End-of-Interrupt Register (INTC_EOIR) ..... 10-13 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 33 Block Diagrams ........... . 11-1 MPC5566 Reference Manual, Rev. 2...

- Page 34 11.4.3.3 FM Calibration Routine ........11-29 MPC5566 Reference Manual, Rev. 2...

- Page 35 12.4 Functional Description ............12-21 MPC5566 Reference Manual, Rev. 2...

- Page 36 12.4.2.10.1Address Decoding for External Master Accesses ... . 12-60 12.4.2.10.2Bus Transfers Initiated by an External Master ....12-61 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 37 13.4.1.4 Flash Read Cycles—Buffer Hit ........13-23 MPC5566 Reference Manual, Rev. 2...

- Page 38 15.2 Modes of Operation ............15-4 MPC5566 Reference Manual, Rev. 2...

- Page 39 FEC Frame Reception ..........15-35 MPC5566 Reference Manual, Rev. 2...

- Page 40 16.3.2.2.1External Boot MMU Configuration ......16-8 16.3.2.2.2Single Bus Master or Multiple Bus Masters ....16-9 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 41 17.4.4.4 Unified Channel Operating Modes ....... 17-28 17.4.4.4.1General Purpose Input/Output Mode (GPIO) ....17-29 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 42 User Mode ............18-11 MPC5566 Reference Manual, Rev. 2...

- Page 43 Overview ............19-2 MPC5566 Reference Manual, Rev. 2...

- Page 44 19.4.3.1 CFIFO Basic Functionality ........19-59 MPC5566 Reference Manual, Rev. 2...

- Page 45 19.5.2.1 Command Queue/CFIFO Transfers ......19-112 MPC5566 Reference Manual, Rev. 2...

- Page 46 20.3.2.8 DSPI Transmit FIFO Registers 0–3 (DSPIx_TXFRn) ....20-26 20.3.2.9 DSPI Receive FIFO Registers 0–3 (DSPIx_RXFRn) ....20-27 MPC5566 Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 47 DSPI Baud Rate and Clock Delay Generation ......20-53 MPC5566 Reference Manual, Rev. 2...

- Page 48 21.2 External Signal Description ........... . 21-3 MPC5566 Reference Manual, Rev. 2...

- Page 49 21.4.10.1 Features of the LIN Hardware ........21-36 MPC5566 Reference Manual, Rev. 2...

- Page 50 22.4.2.1 Arbitration Process ......... . . 22-25 MPC5566 Reference Manual, Rev. 2...

- Page 51 23.5.3.4 Pin Values after POR Negates ........23-7 MPC5566 Reference Manual, Rev. 2...

- Page 52 25.1.3.3 Reduced-Port Mode ..........25-5 MPC5566 Reference Manual, Rev. 2...

- Page 53 25.7.2.6 MCKO ........... . . 25-24 MPC5566 Reference Manual, Rev. 2...

- Page 54 25.13.3 Program Trace Synchronization Messages ......25-53 MPC5566 Reference Manual, Rev. 2...

- Page 55 25.15.2 Features ............25-74 MPC5566 Reference Manual, Rev. 2...

- Page 56 A.2 MPC5566 Register Map ........

- Page 57 B.3 Device-Specific Information ........... . B-4 B.3.1 MPC5566 Calibration Bus Implementation ....... . . B-4 B.4 Signals and Pads .

-

Page 58: Mpc5566 Microcontroller Reference Manual, Rev

Introduction Overview The MPC5566 microcontroller (MCU) is a member of the MPC5500 family of next generation powertrain microcontrollers built on Power Architecture™ technology. The MPC5500 family contains a host processor core that complies with the Power Architecture embedded category, which is 100 percent user mode compatible with the original Power PC™... -

Page 59: Rev.

MII signals. The upper 16-bits of the 32-bit external bus interface (EBI) are used to connect to an external Ethernet device. The FEC contains built-in transmit and receive message FIFOs and DMA support. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 60: Rev.

Introduction Block Diagram Figure 1-1 is a block diagram of the MPC5566. e200z6 Core Core registers Master Slave GPRs (64 bits) Internal Integer Master Slave SPRs SRAM execution unit 128 KB Unified Master Slave 32-KB Flash Multiply cache 3 MB... -

Page 61: Features

Introduction Features This section provides a high-level description of the features found in the MPC5566. • Operating parameters — Fully static operation, up to 144 MHz — –40 to 150 °C junction temperature — Low-power design – Less than 1.2 Watts power dissipation –... - Page 62 – Conversion instructions between single precision floating point and fixed point — Long cycle time instructions, except for guarded loads. Do not increase interrupt latency in the MPC5566 to reduce latency; long cycle time instructions are aborted upon interrupt requests. — Extensive system development support through Nexus debug module •...

- Page 63 • System integration unit (SIU) – Centralized GPIO control of bus pins: 416 BGA package: 178 pins – 416 CSP BGA package: 225 pins — Centralized pad control on a per-pin basis MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 64 — Four selectable time bases plus a shared time or angle counter bus — DMA and interrupt request support — Motor control capability • Enhanced time processor units (eTPUs) — Two 32-channel engines MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 65 Two enhanced serial communication interface (eSCI) modules — UART mode provides NRZ format and half or full duplex interface — eSCI bit rate up to 1 Mb/sec. — Advanced error detection, and optional parity generation and detection MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 66 — Three test data registers: a bypass register, a boundary scan register, and a device identification register — TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 67 — Address recognition for broadcast, single-station address, promiscuous mode, and multicast hashing — Ethernet channel uses DMA burst transactions to transfer data to and from external/system memory MPC5566 Microcontroller Reference Manual, Rev. 2 1-10 Freescale Semiconductor...

-

Page 68: Mpc5500 Family Comparison

Introduction MPC5500 Family Comparison The following table compares the product features of the MPC5554 versus the MPC5566: Table 1-1. MPC5554 and MPC5566 Comparison Module MPC5554 MPC5566 PowerPC core e200z6 e200z6 Variable Length Encoding (VLE) — Unified cache (KB) Memory management unit (MMU) -

Page 69: Detailed Features

Introduction Table 1-1. MPC5554 and MPC5566 Comparison (continued) Module MPC5554 MPC5566 Enhanced Time Processing Unit (eTPU) 64 channels 64 channels eTPU A eTPU B Code memory (KB) Parameter RAM (KB) Nexus Class 3 Class 3 Interrupt controller (INT) Enhanced queued analog-to-digital converter (eQADC) - Page 70 32-bits and the normal integer type. Low latency fixed-point and floating-point add, subtract, multiply, divide, compare, and conversion operations are provided, and most operations can be pipelined. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 1-13...

-

Page 71: System Bus Crossbar Switch (Xbar)

1. Although this device has a maximum of 329 interrupts, the logic requires that the total number of interrupts be divisible by four. Therefore, the total number of interrupts specified for this device is 332. MPC5566 Microcontroller Reference Manual, Rev. 2 1-14... -

Page 72: Frequency Modulated Phase-Locking Loop (Fmpll)

The error correction status module (ECSM) provides status information regarding platform memory errors reported by error-correcting codes. 1.5.9 Flash Memory The MPC5566 provides 3 MB of programmable, non-volatile, flash memory storage. Non-volatile memory (NVM) can be used for instruction and/or data storage. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 73: Cache

• Booting from internal flash memory • Single master booting from external memory • Serial boot loading (program is downloaded to SRAM over an eSCI or FlexCAN peripheral and then executed) MPC5566 Microcontroller Reference Manual, Rev. 2 1-16 Freescale Semiconductor... -

Page 74: Enhanced Management Input/Output System (Emios)

RAM to form a powerful time processing subsystem. The MPC5566 has two eTPU engines. You can use the high-level assembler and compiler, along with the eTPU documentation set, to develop customized eTPU functions. The eTPU supports several features of older TPU versions, making it easy to port earlier application versions. -

Page 75: Enhanced Serial Communications Interface (Esci)

The channels and register content are transmitted using a SPI-like protocol. The MPC5566 has four DSPI modules (A, B, C, and D). The DSPIs have three configurations: • Serial peripheral interface (SPI) configuration where the DSPIs operate as serial ports only with support for queues. -

Page 76: Fast Ethernet Controller (Fec)

The JTAGC module is compliant with the IEEE® 1149.1-2001 standard. 1.5.21 Fast Ethernet Controller (FEC) The MPC5566 fast Ethernet controller includes these distinctive features: • IEEE 802.3 MAC (compliant with IEEE 802.3 1998 edition) •... -

Page 77: Mpc5500 Family Memory Map

4 KB boundary. Peripheral modules may be redundantly mapped. You must use the MMU to prevent corruption. Table 1-2 shows a detailed list of the device memory map. Table 1-2. MPC5566 Detailed Memory Map Allocated Size Used Size Address Range... - Page 78 Introduction Table 1-2. MPC5566 Detailed Memory Map (continued) Allocated Size Used Size Address Range (bytes) (bytes) 0xC3FA_0000–0xC3FA_3FFF 16 KB 1056 Modular timer system (eMIOS) 0xC3FA_4000–0xC3FB_FFFF 112 KB Reserved 0xC3FC_0000–0xC3FC_3FFF 16 KB 3 KB Enhanced time processing unit (eTPU) registers 0xC3FC_4000–0xC3FC_7FFF...

-

Page 79: Multi-Master Operation Memory Map

Introduction Table 1-2. MPC5566 Detailed Memory Map (continued) Allocated Size Used Size Address Range (bytes) (bytes) 0xFFFC_0000–0xFFFC_3FFF 16 KB 1152 Controller area network (FlexCAN A) 0xFFFC_4000–0xFFFC_7FFF 16 KB 1152 Controller area network (FlexCAN B) 0xFFFC_8000–0xFFFC_BFFF 16 KB 1152 Controller area network (FlexCAN C) 0xFFFC_C000–0xFFFC_FFFF... - Page 80 MCU acting as a slave in a multi-master system from the point of view of the external master. Table 1-4. MPC5566 Family Slave Memory Map as Seen from an External Master External Address Range...

- Page 81 Introduction MPC5566 Microcontroller Reference Manual, Rev. 2 1-24 Freescale Semiconductor...

-

Page 82: Block Diagram

Read the last two columns in Table 2-1 for a list of BGA package connections provided by the VertiCal assembly. NOTE The Vertical assembly has ball connections for all the available signals on the device. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 83 DDA0 DAN3+_AN[6] SSA0 DAN3–_AN[7] DDA1 ANW_AN[8] SSA1 ANX_AN[9] DDSYN eQADC ANY_AN[10] POWER/ SSSYN GROUND ANZ_AN[11] FLASH SDS_MA[0]_AN[12] SDO_MA[1]_AN[13] STBY SDI_MA[2]_AN[14] FCK_AN[15] AN[16:39] DDEH GPIO[111:112]_ETRIG[0:1] DD33 REFBYPC NO CONNECT Figure 2-1. MPC5566 Signals MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 84: External Signal Descriptions

The PA field is from 1- to 3-bits wide, depending on the PCR register. Figure 2-3 explains the symbol definitions used in the P/A/G column for Table 2-1. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 85: Device Signals Summary

/ – RSTCFG_ Reset configuration input RSTCFG / – / Up DDEH6 GPIO[210] GPIO BOOTCFG[0]_ Boot configuration input BOOTCFG IRQ[2]_ External interrupt request – / Down AA25 AB26 DDEH6 / Down GPIO[211] GPIO MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 86 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset BOOTCFG[1]_ Boot configuration input BOOTCFG IRQ[3]_ External interrupt request – / Down AB24 DDEH6 / Down GPIO[212]...

- Page 87 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset DATA[18]_ External data bus FEC_TX_ER_ Ethernet transmit error – / Up – / Up DDE3 GPIO[46] GPIO...

-

Page 88: Cal_Addr[8]_Cal_Cs

Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset BDIP_ External burst data in progress – / Up – / Up DDE2 GPIO[63] GPIO WE/BE[0:1]_ External write/byte enable –... -

Page 89: Cal_Ts

Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset CAL_TS Calibration transfer start – / Up – / Up — AA11 DDE12 NEXUS EVTI Nexus event in... - Page 90 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset CNTXC_ FlexCAN C transmit PCSD[3]_ DSPI D peripheral chip select – / Up – / Up DDEH6...

- Page 91 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset SCKB_ DSPI B clock PCSC[1]_ DSPI C peripheral chip select – / Up – / Up DDEH10...

- Page 92 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset AN[8]_ Single-ended analog input I / – AN[8] / – DDA1 External multiplexed analog input AN[9]_ Single-ended analog input I / –...

- Page 93 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset Voltage reference low – / – – SSINT REFBYPC Reference bypass capacitor input – – / –...

- Page 94 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset ETPUA[29]_ eTPU A channel (output only) – / – / PCSC[2]_ DSPI C peripheral chip select DDEH1...

- Page 95 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset EMIOS[8:9]_ eMIOS channel – / – / AC17, ETPUA[8:9]_ eTPU A channel (output only) N21, AD23 DDEH4...

- Page 96 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset GPIO EMIOS[14:15]_ eMIOS channel (output only) – / Up – / Up H24, G25 J26, H27 DDEH6...

- Page 97 Signal Description Table 2-1. MPC5566 Signal Properties (continued) Status After Vertical During Signal Names Signal Functions Type Voltage Type Reset Package Assembly Reset M10, M11, N10, N11, P10, P11, R10, R11, T1, T4, M11, N11, T10, T12, N12, N13, T13, T14, External I/O supply input 1.8–3.3 V...

- Page 98 AF24, AG25 For each pin in the table, each line in a Function row is a separate function of the pin. For all MPC5566 I/O pins the selection of primary pin function or secondary function or GPIO is done in the MPC5566 SIU except where explicitly noted.

-

Page 99: Detailed Signal Description

The pins are reserved for the clock and inverted clock outputs for DDR memory interface. Detailed Signal Description This section gives detailed descriptions of the device signals. Read Section 2.2.2, “Device Signals Summary,” for the signal properties. MPC5566 Microcontroller Reference Manual, Rev. 2 2-18 Freescale Semiconductor... -

Page 100: Reset And Configuration Signals

The alternate function is an external interrupt request input, and the second alternate function is the data output for the DSPI module D. 2.3.1.5 Phase Locked-Loop Configuration PLLCFG[2] The MPC5566 does not use PLLCFG[2], therefore PLLCFG[2] is tied low. Read Section 11.3.1.1, “Synthesizer Control Register (FMPLL_SYNCR).” MPC5566 Microcontroller Reference Manual, Rev. 2... -

Page 101: Rstcfg_Gpio[210]

ADDR[9:11] and is an external bus address function. 2.3.2.3 External Address / GPIO ADDR[8:11]_GPIO[4:7] ADDR[8:11]_GPIO[4:7] are the External Bus Interface (EBI) address signals. 2.3.2.4 External Address / GPIO ADDR[12:29]_GPIO[8:25] ADDR[12:29]_GPIO[8:25] are External Bus Interface (EBI) address signals. MPC5566 Microcontroller Reference Manual, Rev. 2 2-20 Freescale Semiconductor... -

Page 102: External Address / Master Address Expansion / Gpio Addr[30:31]_Addr[6:7]_Gpio[26:27]

DATA[20]_FEC_TXD[0]_GPIO[48] is an EBI data signal. The alternate signal is FEC transmit data [0] function. 2.3.2.12 External Data / Ethernet Receive Error / GPIO DATA[21]_FEC_RX_ER_GPIO[49] DATA[21]_FEC_RX_ER_GPIO[49] is an EBI data signal. The alternate function is FEC receive error function. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-21... -

Page 103: Data[22]_Fec_Rxd[0]_Gpio[50]

DATA[28]_FEC_TXD[1]_GPIO[56] is an EBI data signal. The alternate function is FEC transmit data [1]. 2.3.2.20 External Data / Ethernet Receive Data / GPIO DATA[29]_FEC_RXD[1]_GPIO[57] DATA[29]_FEC_RXD[1]_GPIO[57] is an EBI data signal.The alternate function is FEC receive data [1]. MPC5566 Microcontroller Reference Manual, Rev. 2 2-22 Freescale Semiconductor... -

Page 104: Data[30]_Fec_Rxd[2]_Gpio[58]

TS_GPIO[69] is asserted by the EBI owner to indicate the start of a transfer. 2.3.2.29 External Transfer Acknowledge / GPIO TA_GPIO[70] TA_GPIO[70] is asserted by the EBI owner to acknowledge that the slave has completed the current transfer. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-23... -

Page 105: Tea_Fec_Rxd[3]_Gpio[71]

EVTO is an output that provides timing to a development tool for a single watchpoint or breakpoint occurrence. 2.3.3.3 Nexus Message Clock Out MCKO MCKO is a free running clock output to the development tools which is used for timing of the MDO and MSEO signals. MPC5566 Microcontroller Reference Manual, Rev. 2 2-24 Freescale Semiconductor... -

Page 106: Mdo[0]

TDI provides the serial test instruction and data input for the on-chip test logic. 2.3.4.3 JTAG Test Data Output TDO provides the serial test data output for the on-chip test logic. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-25... -

Page 107: Cntxa_Txda_Gpio

CAN C Transmit / DSPI D / GPIO CNTXC_PCSD[3]_GPIO[87] CNTXC_PCSD[3]_GPIO[87] is the transmit pin for the FlexCAN C module. The alternate function is PCSD[3], a peripheral chip select for the DSPI D module. MPC5566 Microcontroller Reference Manual, Rev. 2 2-26 Freescale Semiconductor... -

Page 108: Cnrxc_Pcsd[4]_Gpio[88

SINA_PCSC[2]_GPIO[94] — SINA is the primary function and is the data input pin for the DSPI A module. The alternate signal function is PCSC[2], a peripheral chip select for the DSPI C module. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 109: Souta_Pcsc[5]_Gpio[95

PCSA[5]_PCSB[3]_GPIO[101] — The PCSA[5] is the primary function and is a peripheral chip select output pin for the DSPI A module. The alternate function is PCSB[3], a peripheral chip select output pin for the DSPI B module. MPC5566 Microcontroller Reference Manual, Rev. 2 2-28 Freescale Semiconductor... -

Page 110: Sckb_Pcsc[1]_Gpio[102

PCSB[3]_SINC_GPIO[108] — PCSB[3] is the primary function and is a peripheral chip select output pin for the DSPI B module. SINC is the alternate function and is the data input for the DSPI C module. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 111: Pcsb[4]_Sckc_Gpio[109

Analog Input / Differential Analog Input AN[4]_DAN2+ AN[4] is a single-ended analog input to the two on-chip ADCs. DAN2+ is the positive terminal of the differential analog input DAN2 (DAN2+ to DAN2–). MPC5566 Microcontroller Reference Manual, Rev. 2 2-30 Freescale Semiconductor... -

Page 112: An[5]_Dan2–

AN[11] is an analog input pin. ANZ is an analog input in external multiplexed mode. NOTE Attempts to convert the input voltage applied to AN[12], AN[13], AN[14], and AN[15] while a non-eQADC function is selected causes an undefined conversion result. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-31... -

Page 113: An[12]_Ma[0]_Sds

AN[15]_FCK is an analog input pin. The alternate function is the free running clock for the eQADC SSI. This pin has reduced analog to digital conversion accuracy as compared to the AN[0:7] and AN[16:39] analog input pins. This pin is configured by setting the pad configuration register, SIU_PCR218. MPC5566 Microcontroller Reference Manual, Rev. 2 2-32 Freescale Semiconductor... -

Page 114: Tcrclka_Irq[7]_Gpio[113

A TCR Clock / External Interrupt Request / GPIO TCRCLKA_IRQ[7]_GPIO[113] TCRCLKA_IRQ[7]_GPIO[113] is the TCR clock input for the eTPU A module. The alternate function is an external interrupt request input for the SIU module. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-33... -

Page 115: Etpua[0]_Etpua[12]_Gpio[114]

ETPUA[5]_ETPUA[17]_GPIO[119] is an input/output channel pin for the eTPU A module. The alternate function, ETPUA[17], is an output channel for the eTPU A module. When configured as ETPUA[17], the pin functions as output only. MPC5566 Microcontroller Reference Manual, Rev. 2 2-34 Freescale Semiconductor... -

Page 116: Etpua[12:15]_Pcsb[1:5]_Gpio[126:129]

A Channel / DSPI B / GPIO ETPUA[12]_PCSB[1]_GPIO[126] ETPUA[12]_PCSB[1]_GPIO[126] is an input/output channel pin for the eTPU A module. The alternate function is a peripheral chip select for the DSPI B module. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-35... -

Page 117: Etpua[16:19]_Pcsd[1:4]_Gpio[130:133]

A Channel / External Interrupt / GPIO ETPUA[20]_IRQ[8]_GPIO[134] ETPUA[20]_IRQ[8]_GPIO[134] is an input/output channel pin for the eTPU A module. The alternate function is an external interrupt request input for the SIU module. MPC5566 Microcontroller Reference Manual, Rev. 2 2-36 Freescale Semiconductor... -

Page 118: Etpua[24:27]_Irq[12:15]_Gpio[138:141]

A Channel / DSPI C / GPIO ETPUA[31]_PCSC[4]_GPIO[145] ETPUA[31]_PCSC[4]_GPIO[145] is an input/output channel pin for the eTPU A module. The alternate function is a peripheral chip select for the DSPI C module. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-37... -

Page 119: Tcrclkb_Irq[6]_Gpio[146

Output Channel / DSPI C / GPIO EMIOS[12]_SOUTC_GPIO[191] EMIOS[12]_SOUTC_GPIO[191] is an output channel pin for the eMIOS module. The alternate function is the data output signal for the DSPI C module. MPC5566 Microcontroller Reference Manual, Rev. 2 2-38 Freescale Semiconductor... -

Page 120: Emios[13]_Soutd_Gpio[192

ETPU B (output only). 2.3.10.10 eMIOS Channel / eTPU B Output Channel / GPIO EMIOS[19]_ETPUB[3]_GPIO[198] EMIOS[19]_ETPUB[3]_GPIO[198] is an input/output channel pin for the eMIOS module. The alternate function is an ETPU B output channel. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-39... -

Page 121: Emios Channel /Etpu B Output Channel / Gpio Emios[20:21]_Etpub[4:5]_Gpio[199:200]

(DDRAM) interface support. The pad types for GPIO[206:207] is F (1.62–3.6 V). Read Section 6.3.1.115, “Pad Configuration Registers 206–207 (SIU_PCR206–SIU_PCR207).” The GPIO[206:207] pins can be selected as sources for the ADC trigger in the SIU_ETISR. MPC5566 Microcontroller Reference Manual, Rev. 2 2-40 Freescale Semiconductor... -

Page 122: Calibration Bus Signals

496 pin assembly. 2.3.12.7 Calibration Output Enable CAL_OE CAL_OE is the primary function and is a calibration output enable. It is functional only when using the 496 pin assembly. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-41... -

Page 123: Xtal

1.5 V regulator control circuit. RCVSS 2.3.14.3 Voltage Regulator Control Output RCCTL is the output pin for the on-chip 1.5 V regulator control circuit. RCCTL MPC5566 Microcontroller Reference Manual, Rev. 2 2-42 Freescale Semiconductor... -

Page 124: Vddan

2.3.14.11 Internal Logic Supply Input is the 1.5 V logic supply input. 2.3.14.12 External I/O Supply Input DDEn is the 1.8–3.3 V, with a tolerance of ±10% external I/O supply input. DDEn MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-43... -

Page 125: Clkout Engclk

The power/ground segmentation applies regardless of whether a particular pin is configured for its primary function or GPIO. Table 2-2. MPC5566 Device Power/Ground Segmentation Voltage Power Segment... - Page 126 +5% to –10%. DDSYN DDA1 During read operations, VPP can be as high as 5.3 V and as low as 3.0 V. Table 2-3. MPC5566 Device Power/Ground Segmentation for the 496 Pin Assembly Power Voltage I/O Pins Powered by Segment...

- Page 127 Signal Description Table 2-3. MPC5566 Device Power/Ground Segmentation for the 496 Pin Assembly (continued) Power Voltage I/O Pins Powered by Segment Segment Range 1.8–3.3 V CLKOUT, ENGCLK DDE5 EVTI, EVTO, MCKO, MDO[3:0], MDO[11:4]_GPIO[82:75], MSEO[1:0], RDY, TCK, TDI, TDO, 1.8–3.3 V...

-

Page 128: Etpu Pin Connections And Serialization

• • • IN 4 IN 13 IN 14 IN 3 DSPI C Figure 2-4. ETPUA[0:15]—DSPI C I/O Connections Table 2-4. ETPUA[0:15]—DSPI C I/O Mapping DSPI C Serialized eTPU A Channel Output Input MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-47... -

Page 129: Etpua[16:31]

ETPUA[16:23] are also connected to the ETPUA[4:11]_ETPUA[16:23]_GPIO[118:125] pins. eTPU A ETPUA[16]_ CH16 IN GPIO[130] CH16 OUT IN 7 IN 5 DSPI B DSPI D Figure 2-5. ETPUA[16:21]—DSPI B–DSPI D I/O Connections MPC5566 Microcontroller Reference Manual, Rev. 2 2-48 Freescale Semiconductor... - Page 130 14, 15 are connected to eMIOS channels. DSPI B serialized output channels 0 through 7 are not connected. Table 2-6. ETPUA[16:31]—DSPI D I/O Mapping DSPI D Serialized eTPU A Channel Output Inputs MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-49...

-

Page 131: Etpub[0:31]

ETPUB[16:23] channels. The output channels of ETPUB[0:15] are serialized on DSPI A. The full ETPUB to DSPI A connections are given in Table 2-7. MPC5566 Microcontroller Reference Manual, Rev. 2 2-50 Freescale Semiconductor... - Page 132 • • • IN 15 IN 8 IN 7 IN 0 DSPI A Figure 2-7. ETPUB[31:0]—DSPI A I/O Connections Table 2-7. ETPUB[0:15]—DSPI A I/O Mapping DSPI A Serialized eTPU B Channel Output Inputs MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-51...

-

Page 133: Emios Pin Connections And Serialization

EMIOS[10]_ CH10 IN GPIO[189] CH10 OUT CH11 IN EMIOS[11]_ GPIO[190] CH11 OUT IN 1 IN 0 IN 7 IN 6 DSPI B DSPI D Figure 2-8. EMIOS[10:11]—DSPI B–DSPI D I/O Connections MPC5566 Microcontroller Reference Manual, Rev. 2 2-52 Freescale Semiconductor... - Page 134 GPIO[203]_ EMIOS[14] eMIOS CH14 IN EMIOS[14]_ IRQ[0]_ CH14 OUT GPIO[193] CH15 IN EMIOS[15]_ IRQ[1]_ CH15 OUT GPIO[194] GPIO[204]_ OUT 15 OUT 14 EMIOS[15] DSPI D Figure 2-10. EMIOS[14:15]—DSPI D I/O Connections MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 2-53...

- Page 135 Signal Description MPC5566 Microcontroller Reference Manual, Rev. 2 2-54 Freescale Semiconductor...

-

Page 136: Introduction

GPRs defined for integer instructions. Refer to the e200z6 PowerPC Core Reference Manual for more information on the e200z6 core. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 137: Block Diagram

Multiply Instruction Unit Control Unit Instruction Buffer Unified Cache Address 32-KB Data In Branch Data Out Unit Unit Load/ Store Unit Bus Interface Unit Address Data Control Figure 3-1. e200z6 Block Diagram MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 138: Overview

— Minimize power use by the cache by selecting CORG = 1 or by setting WAM = 1. Refer to Table 3-9. • Periodic timer and watchdog functions • Periodic system integrity can be monitored through parallel signature checks MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 139: Instruction Unit Features

Pipelined operation supports throughput of one load or store operation per cycle • Dedicated 64-bit interface to memory supports saving and restoring of up to two registers per cycle for load multiple and store multiple word instructions MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 140: Mmu Features

The integer execution unit consists of a 32-bit arithmetic unit (AU), a logic unit (LU), a 32-bit barrel shifter (shifter), a mask-insertion unit (MIU), a condition register manipulation unit (CRU), a count-leading-zeros unit (CLZ), a 32 x 32 hardware multiplier array, result feed-forward hardware, and support hardware for division. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 141: Core Registers And Programmer's Model

Data is transferred between memory and registers with explicit load and store instructions only. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 142 The number to the right of the special-purpose registers (SPRs) is the decimal number used in the instruction syntax to access the register (for example, the integer exception register (XER) is SPR 1). MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 143 (read-only) L1CSR0 2 - Optional registers defined by the Power SPR 1010 L1CFG0 Architecture embedded category SPR 515 L1FINV0 SPR 1016 3 - Read-only registers Figure 3-2. Supervisor Mode Programmer’s Model MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 144: Power Architecture Registers

Link register (LR). The LR provides the branch target address for the branch conditional to link register (bclr, bclrl) instructions, and is used to hold the address of the instruction that follows a branch and link instruction, typically used for linking to subroutines. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 145: Supervisor-Level Only Registers

— Software-use special purpose registers (SPRGs). The SPRG0–SPRG7 registers are provided for operating system use. — Exception syndrome register (ESR). The ESR register provides a syndrome to differentiate between the different kinds of exceptions which can generate the same interrupt. MPC5566 Microcontroller Reference Manual, Rev. 2 3-10 Freescale Semiconductor... - Page 146 — Timer status register (TSR). This register contains status on timer events and the most recent watchdog timer-initiated processor reset. For more details about these registers, refer to the Power Architecture embedded category specifications. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-11...

-

Page 147: Core-Specific Registers

Debug facility registers — Debug control register 3 (DBCR3) controls for debug functions not described in the Power Architecture embedded category. — Debug counter register (DBCNT) provides counter capability for debug functions. MPC5566 Microcontroller Reference Manual, Rev. 2 3-12 Freescale Semiconductor... -

Page 148: E200Z6 Core Complex Features Not Supported In The Device

The OCR[WKUP] bit in the e200z6 OnCE control register (OCR) has no effect. Machine check The machine check input pin is not supported. HID0 [EMCP] has no effect, and MCSR[MCP] always reads a negated value. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-13... -

Page 149: Functional Description

SIZE[0:3] Page size = 4 KB,16 KB, 64 KB, 256 KB, 1 MB, 4 MB, 16 MB, 64 MB, 256 MB SX, SW, SR Supervisor execute, write, and read permission bits MPC5566 Microcontroller Reference Manual, Rev. 2 3-14 Freescale Semiconductor... -

Page 150: Translation Flow

TLB entries. TLB_entry[V] TLB entry Hit TLB_entry[TS] AS (from MSR[IS] or MSR[DS]) Process ID private page shared page TLB_entry[TID] TLB_entry[EPN] EA page number bits Figure 3-4. Virtual Address and TLB-Entry Compare Process MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-15... -

Page 151: Effective To Real Address Translation

UR—User read permission. Allows loads and load-type cache management instructions to access the page while in user mode. • UW—User write permission. Allows stores and store-type cache management instructions to access the page while in user mode. MPC5566 Microcontroller Reference Manual, Rev. 2 3-16 Freescale Semiconductor... -

Page 152: Mmu Assist Registers (Mas[0:4], Mas[6])

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 — TLBSEL — ESEL — Undefined on Power Up ⎯ Unchanged on Reset Reset Figure 3-7. MAS Register 0 Format — MAS[0] MAS[0] fields are defined in Table 3-3. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-17... -

Page 153: Mas[1] Register

Translation address space. This bit is compared with the IS or DS fields of the MSR (depending on the type of access) to determine if this TLB entry can be used for translation. MPC5566 Microcontroller Reference Manual, Rev. 2 3-18 Freescale Semiconductor... -

Page 154: Mas[2] Register

1 This page is considered cache-inhibited. Memory coherence required.The e200z6 does not support the memory coherence required attribute, and thus it is ignored. 0 Memory coherence is not required. 1 Memory coherence is required. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-19... -

Page 155: Mas[3] Register

16 17 18 19 20 21 22 — TLBSELD — TIDSELD — TSIZED — WD ID MD GD ED Undefined on Power Up ⎯ Unchanged on Reset Reset Figure 3-11. MMU Assist Register 4 MAS[4] MPC5566 Microcontroller Reference Manual, Rev. 2 3-20 Freescale Semiconductor... -

Page 156: Mas[6] Register

Table 3-8. MAS[6] — TLB Search Context Register 0 Field Description 0–7 Reserved, must be cleared. 8–15 PID value for searches SPID 16–30 Reserved, must be cleared. AS value for searches MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-21... -

Page 157: L1 Cache

Control Logic Control Data Array Address/ Processor Interface Tag Array Data Unit Core Data Data Data Path Address Address Address Path Memory Management Unit Figure 3-13. e200z6 Unified Cache Block Diagram MPC5566 Microcontroller Reference Manual, Rev. 2 3-22 Freescale Semiconductor... -

Page 158: Cache Organization

(and valid). For invalid lines, the V bit is clear, causing the cache line to be ignored during lookups. Valid lines have their V bit set and D bit cleared, MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 159 • • DW0 DW1 DW2 DW3 Status Set 127 Data or instruction Reference A[0:19] Select HIT 7 HIT 2 Logical OR HIT 1 Comparator HIT 0 Figure 3-15. Cache Lookup Flow MPC5566 Microcontroller Reference Manual, Rev. 2 3-24 Freescale Semiconductor...

-

Page 160: Cache Line Replacement Algorithm

MMU permissions are set so that no cacheable page has X (execute) permission which also has R (read) or W (write) permission, i.e. can be cacheable and accessed with both instruction and data accesses. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 161: L1 Cache Control And Status Register 0 (L1Csr0)

Bit 3 corresponds to way 3. The WID and WDD bits can be used for locking ways of the cache, and also are used in determining the replacement policy of the cache. MPC5566 Microcontroller Reference Manual, Rev. 2 3-26 Freescale Semiconductor... - Page 162 When set, write accesses are performed in copyback mode unless the “W” page attribute from an optional MMU is set. Disable push buffer 0 = Push buffer enabled 1 = Push buffer disabled MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-27...

- Page 163 Writing a 0 to this bit while an invalidation operation is in progress will be ignored. Cache invalidation operations require approximately134 cycles to complete. Invalidation occurs regardless of the enable (CE) value. MPC5566 Microcontroller Reference Manual, Rev. 2 3-28 Freescale Semiconductor...

-

Page 164: L1 Cache Configuration Register 0 (L1Cfg0)

00 - The cache implements a block size of 32 bytes Cache replacement policy 9–10 CREPL 10 - The cache implements a pseudo-round-robin replacement policy Cache locking APU available 1 - The cache implements the line locking APU MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-29... -

Page 165: Interrupt Types

• Byte ordering error from a misaligned access across a page boundary to a page with mismatched E bits • Cache locking exception • Precise external termination error and the current MSR[ME] = 1. MPC5566 Microcontroller Reference Manual, Rev. 2 3-30 Freescale Semiconductor... - Page 166 SRR[0:1] Data translation lookup did not match a valid entry in the TLB error Instruction IVOR 14 — SRR[0:1] Instruction translation lookup did not match a valid TLB entry TLB error MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-31...

-

Page 167: Bus Interface Unit (Biu)

• Timer status register (TSR)—provides status of the timer facilities. • Time base registers (TBU and TBL)—two 32-bit registers (upper and lower) that are concatenated to provide a long-period, 64-bit counter. MPC5566 Microcontroller Reference Manual, Rev. 2 3-32 Freescale Semiconductor... -

Page 168: Signal Processing Extension Apu (Spe Apu)

The e200z6 core has a 64-bit architectural accumulator register that holds the results of the SPE multiply accumulate (MAC) fixed-point instructions. The accumulator allows back-to-back execution of dependent fixed-point MAC instructions, something that is found in the inner loops of DSP code such as filters. The MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 3-33... -

Page 169: External References

Not the mask bit 62 of CSRR0, DSRR0, or SRR0 respectively. The destination address is [D,C]SRR0[32:62] || 0b0. bclr, bclrl, bcctr, bcctrl Not the mask bit 62 of the LR or CTR respectively. The destination address is [LR,CTR][32:62] || 0b0. MPC5566 Microcontroller Reference Manual, Rev. 2 3-34 Freescale Semiconductor... -

Page 170: Introduction

All reset sources initiate execution of the MCU boot assist module (BAM) program with the exception of the software external reset. 1. Unless noted otherwise, the use of ‘clock’ or ‘clocks’ in this section is a reference to the system clock. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 171: External Signal Description

SER bit of the system reset control register (SIU_SRCR). Refer to Section 11.1.4, “FMPLL Modes of Operation” for details of PLL configuration. NOTE During a power on reset, RSTOUT is tri-stated. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 172: Reset Configuration (Rstcfg)

SIU_RSR remain set until another reset occurs. The SERF bit is set when a software external reset occurs, but no previously set bits in the SIU_RSR are cleared. Refer to Section 4.3.1.1, “Reset Status Register (SIU_RSR)” for additional information. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 173 0 No watchdog timer or debug reset occurred. 1 A watchdog timer or debug reset occurred. Checkstop reset status 0 No enabled checkstop reset occurred. 1 An enabled checkstop reset occurred. 6–13 Reserved. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 174: System Reset Control Register (Siu_Srcr)

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 The CRE bit is reset to 1 by POR. Other resets sources do not reset the bit value. Figure 4-2. System Reset Control Register (SIU_SRCR) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 175: Functional Description

RCHW. Hence, the available reset vector addresses are: 0x0000_0004 0x0000_4004 0x0001_0004 0x0001_C004 0x0002_0004 0x0003_0004 Serial Boot Specified over serial download MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 176: Reset Sources

RSTOUT are kept asserted until the FMPLL is locked. After the FMPLL is locked, the reset controller waits an additional predetermined number of clock cycles before negating the RSTOUT pin. The WKPCFG and BOOTCFG[0:1] pins are sampled 4 clock cycles before the negation of RSTOUT, MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 177: External Reset

SIU_RSR. The LLRS bit is set, and all other reset status bits in the SIU_RSR are cleared. Refer to Section 4.2.2, “Reset Output (RSTOUT)” Refer to Chapter 11, “Frequency Modulated Phase Locked Loop and System Clocks (FMPLL),” for more information on loss-of-lock. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 178: Loss-Of-Clock Reset

Debug tool sets the software system reset (SSR) bit in the system reset control register (SIU_SRCR) The debug tool writes a one to the software external reset (SER) bit in the system reset control register (SIU_SRCR) to generate an external software reset. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 179: Checkstop Reset

RSTCFG is asserted), and the data is updated in the SIU_RSR. The reset source status bits in the SIU_RSR are unaffected. Refer to Section 4.2.2, “Reset Output (RSTOUT).” Refer to Chapter 24, “IEEE 1149.1 Test Access Port Controller (JTAGC),” for more information. MPC5566 Microcontroller Reference Manual, Rev. 2 4-10 Freescale Semiconductor... -

Page 180: Software System Reset

This reset configuration is defined by: • Configuration pins • A reset configuration halfword (RCHW), if present • Serial port, if a serial boot is used The following sections describe these configuration pins and the RCHW. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 4-11... -

Page 181: Rstcfg Pin

MMU is configured, how the external bus is configured, the FlexCAN or eSCI module pin configuration, Nexus enabling, and password selection. Refer to Chapter 2, “Signal Description” for information about the BOOTCFG pins. MPC5566 Microcontroller Reference Manual, Rev. 2 4-12 Freescale Semiconductor... -

Page 182: Pllcfg[0:1] Pins

0x5A. BOOT_BLOCK_ADDRESS is explained in Section 16.3.2.2.5, “Read the Reset Configuration Halfword.” The fields of the RCHW are shown in Figure 4-3. BOOT_BLOCK_ADDRESS + 0x0000_0000 Boot Identifier = 0x5A Figure 4-3. RCHW Fields MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 4-13... - Page 183 CAN/SCI boot is initiated. For an external boot, only block 0 is checked for a valid boot identifier, and if not found, a CAN/SCI boot is initiated. MPC5566 Microcontroller Reference Manual, Rev. 2 4-14 Freescale Semiconductor...

-

Page 184: Invalid Rchw

RCHW from the first address of each of the six blocks in the low address space (LAS) of internal flash. Table 4-9 shows the LAS addresses. Table 4-9. LAS Block Memory Addresses Block Address 0x0000_0000 0x0000_4000 0x0001_0000 0x0001_C000 0x0002_0000 0x0003_0000 MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 4-15... -

Page 185: Reset Configuration Timing

4 clock cycles before the negation of RSTOUT and stored in the reset status register (SIU_RSR). BOOTCFG[0:1] are latched only if RSTCFG is asserted. WKPCFG is not dependent on RSTCFG. MPC5566 Microcontroller Reference Manual, Rev. 2 4-16 Freescale Semiconductor... - Page 186 This clock count is dependent on the configuration of the FMPLL (Refer to Section 4.2.2, “RSTOUT”). If the FMPLL is configured for 1:1 (dual controller) operation or for bypass mode, this clock count is 16000. Figure 4-4. Reset Configuration Timing MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 4-17...

-

Page 187: Reset Flow

False RESET asserted True Set latch, wait 8 clock cycles False RESET Set RGF bit asserted True To entry point in internal reset flow Figure 4-5. External Reset Flow Diagram MPC5566 Microcontroller Reference Manual, Rev. 2 4-18 Freescale Semiconductor... - Page 188 The clock count depends on the FMPLL configuration. Refer to Section 4.2.2, “Reset Output (RSTOUT).” If the FMPLL is configure in dual controller (1:1) or bypass mode, the clock count is 16000. Figure 4-6. Internal Reset Flow Diagram MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 4-19...

- Page 189 Reset MPC5566 Microcontroller Reference Manual, Rev. 2 4-20 Freescale Semiconductor...

-

Page 190: Introduction

• Override the privilege level of a master to change it to user mode privilege • Designate masters as trusted or untrusted Peripherals can implement the following restrictions: MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 191 Slave 0 FLASH — Slave 1 — Slave 3 SRAM — Slave 6 PBRIDGE A PBRIDGE A FMPLL EBI control FLASH control eMIOS eTPU reg eTPU PRAM eTPU PRAM mirror eTPU SCM MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 192: Features

Supports a pair of slave accesses for 64-bit instruction fetches. • Provides configurable per-module write buffering support. • Provides configurable per-module and per-master access protections. 5.1.4 Modes of Operation The PBRIDGE has only one operating mode. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 193: External Signal Description

Additionally, these registers must only be read from or written to by a 32-bit aligned access. PBRIDGE registers are mapped into the PBRIDGE A and MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 194: Master Privilege Control Register (Pbridge_X_Mpcr)

Master trusted for writes. Determines whether the master is trusted for write accesses. Trusted by default. MTW0 0 Write accesses from the CPU are not trusted 1 Write accesses from the CPU are trusted MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 195 Master privilege level. Determines how the privilege level of the EBI is determined. Accesses not forced to MPL3 user mode by default. 0 Accesses from the EBI are forced to user mode. 1 Accesses from the EBI are not forced to user mode. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 196: Ripheral Access Control Registers (Pbridge_X_Opacr)

To ensure code compatibility across all the MPC55XX family of products, writes to those addresses must be qualified with SIU_MIDR[PARTNUM]. NOTE Write PBRIDGE_x_PACR and PBRIDGE_x_OPACR with a read/modify/write for code compatibility. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 197 The SP0 and TP0 bits default values are always used, even though the bits are writeable. The default value is 0b0000 for PACR peripheral access fields that are unused or not connected. Figure 5-3. Peripheral Access Control Registers (PBRIDGE_x_PACRn) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 198 Note: For PBRIDGE_A_PACR0 and PBRIDGE_B_PACR0, you must have supervisor privileges to access PBRIDGE registers. Note: Even though the SP0 bit (1) is writeable, the reset value for SP0 is always used. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

- Page 199 0b0101 1–7 — 0b0000 PBRIDGE_A_OPACR0 PBRIDGE_A_Base + 0x0040 FMPLL 0b0100 EBI control 0b0100 Flash control 0b0100 — 0b0100 0b0100 5–7 — 0b0100 PBRIDGE_A_OPACR1 PBRIDGE_A_Base + 0x0044 eMIOS 0b0100 1–7 — 0b0100 MPC5566 Microcontroller Reference Manual, Rev. 2 5-10 Freescale Semiconductor...

- Page 200 — 0b0100 PBRIDGE_B_OPACR2 PBRIDGE_B_Base + 0x0048 FlexCAN A 0b0100 FlexCAN B 0b0100 FlexCAN C 0b0100 FlexCAN D 0b0100 4–7 — 0b0100 PBRIDGE_B_OPACR3 PBRIDGE_B_Base + 0x004C — 0b0100 1–6 — 0b0100 0b0100 MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 5-11...

-

Page 201: Functional Description

INTC_EOIR that consumes at least the number of system clock cycles that the actual write is delayed. Refer to Section 10.4.3.1.2, “End-of-Interrupt Exception Handler.” MPC5566 Microcontroller Reference Manual, Rev. 2 5-12 Freescale Semiconductor... -

Page 202: Read Cycles

Table 5-7. On-Platform and Off-Platform Peripherals On-Platform Off-Platform Enhanced direct memory access (eDMA) Deserial serial peripheral interface (DSPI) PBridge A and B Enhanced queued analog-to-digital converter (eQADC) Interrupt controller (INTC) Enhanced serial communication interface (eSCI) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 5-13... - Page 203 The PBRIDGE also supports buffered writes, allowing write accesses to be terminated on the system bus in a single clock cycle, and then subsequently performed on the slave interface. Write buffering is controllable on a per-peripheral basis. The PBRIDGE implements a two-entry 32-bit write buffer. MPC5566 Microcontroller Reference Manual, Rev. 2 5-14 Freescale Semiconductor...

-

Page 204: Introduction

SIU. One signal, from the muxed signals shown on the right side of the diagram, is assigned to a ball on the device. The SIU registers are accessed using the crossbar switch. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... - Page 205 IMUX DSPI signals, and I/O channels eQADC triggers Figure 6-1. SIU Block Diagram NOTE The power-on reset detection module, pad interface/pad ring module, and peripheral I/O channels are external to the SIU. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor...

-

Page 206: Overview

In normal mode, the SIU provides the register interface and logic that controls the device and system configuration, the reset controller, and GPIO. The SIU continues operation with no changes in stop mode. Debug SIU operation in debug mode is identical to operation in normal mode. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 207: Detailed Signal Descriptions

DDEH below the switch point value for more than two clock cycles. The switch point value is between the maximum V and minimum V specifications for the V input pins. DDEH MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 208: Reset Output (Rstout)

2. BAM module boots from internal flash (default = 0b00) 3. Boot value from internal flash is written to BOOTCFG[0:1] field in the reset status register (SIU_RSR) 4. BOOTCFG[0:1] values are latched and driven as output signals from the SIU MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 209: I/O Weak Pullup Reset Configuration (Wkpcfg)

IRQ flag bit is set to 1. For example, the IRQ flag bit is set if a rising-edge event occurs under the following conditions: • Previous filtered IRQ state was a logic 0 • Current latched IRQ state is a logic 1 • Rising-edge event is enabled for the IRQ MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 210: External Interrupts

An overrun IRQ exists for each overrun flag bit in the overrun status register (SIU_OSR). An overrun IRQ asserts when all of the following occur: • Enable bit is set in the IRQ rising- and/or falling-edge event registers (SIU_IREER, SIU_IFEER) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 211: Edge-Detect Events

SIU_MIDR MCU ID register Base + 0x0008 Reserved Base + 0x000C SIU_RSR Reset status register Base + 0x0010 SIU_SRCR System reset control register Base + 0x0014 SIU_EISR SIU external interrupt status register MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 212: Register Descriptions

The register figures use the following notational conventions in this section: Write 1 to clear the bit to 0. — Not applicable. Reserved or unimplemented bit. Bit value is uninitialized upon reset. Bit value is unchanged upon reset. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 213: Mcu Id Register (Siu_Midr)

MPC5566 reads 0x5566. CSP configuration: 0 Standard package 1 CSP package 17–19 Package settings. PKG selects the pin package for the MPC5566 device. 000 Select for Legacy compatibility 001–01x Reserved 100–101Reserved 110 Select the 416 package 110 Select the 496 calibration assembly 111 Reserved 20–23... -

Page 214: Reset Status Register (Siu_Rsr)

Reset Source Priority Group • Power on reset (POR) Highest • External reset • Software system reset Higher • Loss-of-clock Lower • Loss-of-lock • Watchdog • Checkstop • Software external reset Lowest MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-11... - Page 215 0 The last reset source acknowledged by the reset controller was not a watchdog timer or debug reset. 1 The last reset source acknowledged by the reset controller was a watchdog timer or debug reset. MPC5566 Microcontroller Reference Manual, Rev. 2 6-12...

- Page 216 Except for a POR request or writing a 1 to the software external reset flag (SERF) bit, all reset requests, regardless of priority are not serviced until the current reset completes. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-13...

-

Page 217: System Reset Control Register (Siu_Srcr)

The SSR bit always reads 0. A write of 0 to this bit has no effect. The CRE bit is set to 1 by POR. Other reset sources cannot set the CRE bit. Figure 6-4. System Reset Control Register (SIU_SRCR) MPC5566 Microcontroller Reference Manual, Rev. 2 6-14 Freescale Semiconductor... -

Page 218: External Interrupt Status Register (Siu_Eisr)

The IRQ flag bit is set regardless of the state of the DMA or interrupt request enable bit in SIU_DIRER. The IRQ flag bit remains set until cleared by software or through the servicing of a DMA or interrupt request. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-15... -

Page 219: Dma Interrupt Request Enable Register (Siu_Direr)

Address: Base + 0x0018 Access: R/W Reset R EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE EIRE Reset Figure 6-6. DMA Interrupt Request Enable Register (SIU_DIRER) MPC5566 Microcontroller Reference Manual, Rev. 2 6-16 Freescale Semiconductor... -

Page 220: Dma/Interrupt Request Select Register (Siu_Dirsr)

DMA interrupt request select n. Selects between a DMA transfer or external interrupt request when an DIRSn edge-triggered event occurs on the corresponding IRQ[n] pin. 0 Interrupt request is selected. 1 DMA request is selected.Reserved MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-17... -

Page 221: Overrun Status Register (Siu_Osr)

Overrun flag n. This bit is set when an overrun occurs on IRQ[n]. Bit 31 (OVF0) is the overrun flag for IRQ[0]; bit 16 OVFn (OVF15) is overrun flag for IRQ[15]. 0 No overrun occurred. 1 An overrun occurred. MPC5566 Microcontroller Reference Manual, Rev. 2 6-18 Freescale Semiconductor... -

Page 222: Overrun Request Enable Register (Siu_Orer)

Overrun request enable n. Enables the overrun request when an overrun occurs on the IRQ[n] pin. Bit 31 (ORE0) is OREn the enable overrun flag for IRQ[0]; bit 16 (ORE15) is overrun flag for IRQ[15]. 0 Overrun request is disabled. 1 Overrun request is enabled. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-19... -

Page 223: Irq Rising-Edge Event Enable Register (Siu_Ireer)

Address: Base + 0x002C Access: R/W Reset R IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE IFEE Reset Figure 6-11. IRQ Falling-Edge Event Enable Register (SIU_IFEER) MPC5566 Microcontroller Reference Manual, Rev. 2 6-20 Freescale Semiconductor... -

Page 224: Irq Digital Filter Register (Siu_Idfr)

For a 100 MHz system clock, this gives a range of 20 ns to 328 µs. The minimum time of three clocks accounts for synchronization of the IRQ input pins with the system clock. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor... -

Page 225: Pad Configuration Registers (Siu_Pcr)

The PA fields in PCR0 through 3 and PCR4 through 7 must not be configured simultaneously to select ADDR[8:11] as an input. Only one pin is to be configured to provide the address input. Figure 6-13. Sample PCR Register Description MPC5566 Microcontroller Reference Manual, Rev. 2 6-22 Freescale Semiconductor... - Page 226 Open drain output enable. Controls output driver configuration for the pads. Either open drain or push/pull driver configurations can be selected. This feature applies to output pins only. 0 Disable open drain for the pad (push/pull driver enabled). 1 Enable open drain for the pad. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-23...

-

Page 227: Pad Configuration Register 0 (Siu_Pcr0)

When configured as CS[0] or ADDR[8], clear the ODE bit to 0. Refer to the EBI section for weak pullup settings when configured as CS[0] or ADDR[8]. Figure 6-14. CS[0]_ADDR[8]_GPIO[0] Pad Configuration Register (SIU_PCR0) MPC5566 Microcontroller Reference Manual, Rev. 2 6-24 Freescale Semiconductor... -

Page 228: Pad Configuration Registers 1–3 (Siu_Pcr1–Siu_Pcr3)

Table 6-19 for bit field definitions. Table 6-21 lists the PA values for CS[1:3]_ADDR[9:11]_GPIO[1:3]. Table 6-21. PCR1–PCR3 PA Field Descriptions PA Field Pin Function 0b00 GPIO[1:3] 0b01 CS[1:3] 0b10 ADDR[9:11] 0b11 CS[1:3] MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-25... -

Page 229: Pad Configuration Registers 4–7 (Siu_Pcr4–Siu_Pcr7)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as ADDR[8:26]. Figure 6-17. ADDR[12:26]_GPIO[8:22] Pad Configuration Registers (SIU_PCR8–SIU_PCR22) MPC5566 Microcontroller Reference Manual, Rev. 2 6-26 Freescale Semiconductor... -

Page 230: Pad Configuration Registers 23–25 (Siu_Pcr23–Siu_Pcr25)

Figure 6-18. ADDR[27:29]_GPIO[23:25] Pad Configuration Registers (SIU_PCR23–SIU_PCR25) Refer to Table 6-19 for bit field definitions. Table 6-24 lists the PA field for ADDR[27:29]_GPIO[23:25]. Table 6-24. PCR23–PCR25 PA Field Descriptions PA Field Pin Function GPIO[23:25] ADDR[27:29] MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-27... -

Page 231: Pad Configuration Registers 26–27 (Siu_Pcr26–Siu_Pcr27)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[0:15]. Figure 6-20. DATA[0:15]_GPIO[28:43] Pad Configuration Registers (SIU_PCR28–SIU_PCR43) MPC5566 Microcontroller Reference Manual, Rev. 2 6-28 Freescale Semiconductor... -

Page 232: Pad Configuration Registers 44 (Siu_Pcr44)

Refer to the EBI section for weak pullup settings when configured as DATA[17]. Figure 6-22. DATA[17]_FEC_CRS_GPIO[45] Pad Configuration Registers (SIU_PCR45) 6.3.1.22 Pad Configuration Registers 46 (SIU_PCR46) The SIU_PCR46 register controls the function, direction, and electrical attributes of DATA[18]_FEC_TX_ER_GPIO[46]. MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-29... -

Page 233: Pad Configuration Registers 47 (Siu_Pcr47)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[20]. Figure 6-25. DATA[20]_FEC_TXD[0]_GPIO[48] Pad Configuration Registers (SIU_PCR48) MPC5566 Microcontroller Reference Manual, Rev. 2 6-30 Freescale Semiconductor... -

Page 234: Pad Configuration Registers 49 (Siu_Pcr49)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[22] FEC_RXD[0]. Figure 6-27. DATA[22]_FEC_RXD[0] GPIO[50] Pad Configuration Registers (SIU_PCR50) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-31... -

Page 235: Pad Configuration Registers 51 (Siu_Pcr51)

Table 6-19 for bit field definitions. Table 6-28 lists the PA fields for DATA[23]_FEC_TXD[3]_GPIO[51]. Table 6-28. PCR51 PA Field Descriptions PA Field Pin Function 0b00 GPIO[51] 0b01 DATA[23] 0b10 FEC_TXD[3] 0b11 DATA[23] MPC5566 Microcontroller Reference Manual, Rev. 2 6-32 Freescale Semiconductor... -

Page 236: Pad Configuration Registers 52 (Siu_Pcr52)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[25] or FEC_RX_DV. Figure 6-30. DATA[25]_FEC_RX_DV_GPIO[53] Pad Configuration Registers (SIU_PCR53) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-33... -

Page 237: Pad Configuration Registers 54 (Siu_Pcr54)

Table 6-19 for bit field definitions. Table 6-31 lists the PA fields for DATA[26]_FEC_TX_EN_GPIO[54]. Table 6-31. PCR54 PA Field Descriptions PA Field Pin Function 0b00 GPIO[54] 0b01 DATA[26] 0b10 FEC_RX_DV 0b11 DATA[26] MPC5566 Microcontroller Reference Manual, Rev. 2 6-34 Freescale Semiconductor... -

Page 238: Pad Configuration Registers 55 (Siu_Pcr55)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[28] or FEC_TXD[1]. Figure 6-33. DATA[28]_FEC_TXD[1]_GPIO[56] Pad Configuration Registers (SIU_PCR56) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-35... -

Page 239: Pad Configuration Registers 57 (Siu_Pcr57)

Table 6-19 for bit field definitions. Table 6-34 lists the PA fields for DATA[29]_FEC_RXD[1]_GPIO[57]. Table 6-34. PCR57 PA Field Descriptions PA Field Pin Function 0b00 GPIO[57] 0b01 DATA[29] 0b10 FEC_RXD[1] 0b11 DATA[29] MPC5566 Microcontroller Reference Manual, Rev. 2 6-36 Freescale Semiconductor... -

Page 240: Pad Configuration Registers 58 (Siu_Pcr58)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as DATA[31] or FEC_RXD[3]. Figure 6-36. DATA[31]_FEC_RXD[3]_GPIO[59] Pad Configuration Registers (SIU_PCR59) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-37... -

Page 241: Pad Configuration Registers 60–61 (Siu_Pcr60–Siu_Pcr61)

Figure 6-37. TSIZ[0:1]_GPIO[60:61] Pad Configuration Register (SIU_PCR60–SIU_PCR61) Refer to Table 6-19 for bit field definitions. Table 6-46 lists the PA fields for TSIZ[0:1]_GPIO[60:61]. Table 6-37. PCR60–PCR61 PA Field Definition PA Field Pin Function GPIO[60:61] TSIZ[0:1] MPC5566 Microcontroller Reference Manual, Rev. 2 6-38 Freescale Semiconductor... -

Page 242: Pad Configuration Register 62 (Siu_Pcr62)

Figure 6-39. BDIP_GPIO[63] Pad Configuration Register (SIU_PCR63) Refer to Table 6-19 for bit field definitions. Table 6-46 lists the PA fields for BDIP_GPIO[63]. Table 6-39. PCR63 PA Field Definition PA Field Pin Function GPIO[63] BDIP MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-39... -

Page 243: Pad Configuration Registers 64–65 (Siu_Pcr64–Siu_Pcr65)

Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. When configured as WE/BE[2:3], clear the ODE bit to 0. Refer to the EBI section for weak pullup settings when configured as WE/BE[2:3]. Figure 6-41. WE/BE[2:3]_GPIO[66:67] Pad Configuration Registers (SIU_PCR66–SIU_PCR67) MPC5566 Microcontroller Reference Manual, Rev. 2 6-40 Freescale Semiconductor... -

Page 244: Pad Configuration Register 68 (Siu_Pcr68)

When configured as TS, clear the ODE bit to 0. When EBI is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as TS. Figure 6-43. TS_GPIO[69] Pad Configuration Register (SIU_PCR69) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-41... -

Page 245: Pad Configuration Register 70 (Siu_Pcr70)

PA fields for TA_GPIO[70]. Table 6-44. PCR70 PA Field Definition PA Field Pin Function GPIO[70] 6.3.1.44 Pad Configuration Register 71 (SIU_PCR71) The SIU_PCR71 register controls the function, direction, and electrical attributes of TEA_GPIO[71]. MPC5566 Microcontroller Reference Manual, Rev. 2 6-42 Freescale Semiconductor... -

Page 246: Pad Configuration Register 72 (Siu_Pcr72)

Table 6-19 for bit field definitions. Table 6-46 lists the PA field for BR_FEC_MDC_GPIO[72]. Table 6-46. PCR72 PA Field Definition PA Field Pin Function 0b00 GPIO[72] 0b01 0b10 FEC_MDC 0b11 Invalid value MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-43... -

Page 247: Pad Configuration Register 73 (Siu_Pcr73)

If external master operation is enabled, clear the HYS bit to 0. Refer to the EBI section for weak pullup settings when configured as BB. Figure 6-48. BB_GPIO[74] Pad Configuration Register PCR74 MPC5566 Microcontroller Reference Manual, Rev. 2 6-44 Freescale Semiconductor... -

Page 248: Pad Configuration Register 82–75 (Siu_Pcr82–Siu_Pcr75)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-50. CNTXA_TXDA_GPIO[83] Pad Configuration Register (SIU_PCR83) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-45... -

Page 249: Pad Configuration Register 84 (Siu_Pcr84)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-52. CNTXB_PCSC[3]_GPIO[85] Pad Configuration Register (SIU_PCR85) MPC5566 Microcontroller Reference Manual, Rev. 2 6-46 Freescale Semiconductor... -

Page 250: Pad Configuration Register 86 (Siu_Pcr86)

Table 6-19 for bit field definitions. Table 6-52 lists the PA fields for CNRXB_PCSC[4]_GPIO[86]. Table 6-52. PCR86 PA Field Definitions PA Field Pin Function 0b00 GPIO[86] 0b01 CNRXB 0b10 PCSC[4] 0b11 CNRXB MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-47... -

Page 251: Pad Configuration Register 87 (Siu_Pcr87)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-55. CNRXC_PCSD[4]_GPIO[88] Pad Configuration Register (SIU_PCR88) MPC5566 Microcontroller Reference Manual, Rev. 2 6-48 Freescale Semiconductor... -

Page 252: Pad Configuration Register 89 (Siu_Pcr89)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-57. RXDA_GPIO[90] Pad Configuration Register (SIU_PCR90) MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-49... -

Page 253: Pad Configuration Register 91 (Siu_Pcr91)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-59. RXDB_PCSD[5]_GPIO[92] Pad Configuration Register (SIU_PCR92) MPC5566 Microcontroller Reference Manual, Rev. 2 6-50 Freescale Semiconductor... -

Page 254: Pad Configuration Register 93 (Siu_Pcr93)

WPE WPS RESET: The SCKA function is available on the MPC5566 only. When SCKA is configured for master operation, set the OBE bit to 1, or clear to 0 for slave operation. When configured as GPDO, set the OBE bit to 1. -

Page 255: Pad Configuration Register 94 (Siu_Pcr94)

WPE WPS RESET: The SINA function is available on the MPC5566 only. When configured as SINA or PCSC[2], the OBE bit has no effect. When configured as GPDO, set the OBE bit to 1. When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. -

Page 256: Pad Configuration Registers 96 (Siu_Pcr96)

WPE WPS RESET: The PCSA[0] function is available on the MPC5566 only. When configured as PSCA[0], set the OBE bit to 1 for master operation, and clear to 0 for slave operation. When configures as PCSD[2], the OBE bit has no effect. When configured as GPDO, set the OBE bit to 1. -

Page 257: Pad Configuration Registers 97 (Siu_Pcr97)

WPE WPS RESET: The PCSA[1] function is available on the MPC5566 only. When configured as PCSA[1] or PCSB[2], the OBE bit has no effect. When configured as GPDO, set the OBE bit to 1. When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. -

Page 258: Pad Configuration Register 99 (Siu_Pcr99)

Table 6-19 for bit field definitions. Table 6-65 lists the PA fields for PCSA[3]_SIND_GPIO[99]. Table 6-65. PCR99 PA Field Definitions PA Field Pin Function 0b00 GPIO[99] 0b01 PCSA[3] 0b10 SIND 0b11 PCSA[3] MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-55... -

Page 259: Pad Configuration Register 100 (Siu_Pcr100)

WPE WPS RESET: The PCSA[4] function is available on the MPC5566 only. When configured as PCSA[4] or SOUTD, the OBE bit has no effect. When configured as GPDO, set the OBE to 1. When PCSA[4] or SOUTD is configured for slave operation, set the IBE bit to 1. When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. -

Page 260: Pad Configuration Register 102 (Siu_Pcr102)

Table 6-19 for bit field definitions. Table 6-68 lists the PA fields for SCKB_PCSC[1]_GPIO[102]. Table 6-68. PCR102 PA Field Definitions PA Field Pin Function 0b00 GPIO[102] 0b01 SCKB 0b10 PCSC[1] 0b11 SCKB MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-57... -

Page 261: Pad Configuration Register 103 (Siu_Pcr103)

When the pad is configured as an output, set the IBE bit to 1 to show the pin state in the GPDI register. Clear the IBE bit to 0 to reduce power consumption. When configured as GPDI, set the IBE bit to 1. Figure 6-71. SOUTB_PCSC[5]_GPIO[104] Pad Configuration Register (SIU_PCR104) MPC5566 Microcontroller Reference Manual, Rev. 2 6-58 Freescale Semiconductor... -

Page 262: Pad Configuration Register 105 (Siu_Pcr105)

Table 6-19 for bit field definitions. Table 6-71 lists the PA fields for PCSB[0]_PCSD[2]_GPIO[105]. Table 6-71. PCR105 PA Field Definitions PA Field Pin Function 0b00 GPIO[105] 0b01 PCSB[0] 0b10 PCSD[2] 0b11 PCSB[0] MPC5566 Microcontroller Reference Manual, Rev. 2 Freescale Semiconductor 6-59... -

Page 263: Pad Configuration Register 106 (Siu_Pcr106)