Table of Contents

Advertisement

Advertisement

Table of Contents

Summary of Contents for Profichip VPC3+C

- Page 1 VPC3+C User Manual Revision 1.03 Th e Cl ever Al t er n a t i ve...

- Page 2 Required corrections are included in subsequent versions. We gratefully accept suggestions for improvements. Copyright Copyright © profichip GmbH 2004-2006. All Rights Reserved. Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content are not allowed.

-

Page 3: Table Of Contents

6.2.4 Slave_Diag (SAP 60)............44 6.2.5 Write_Read_Data / Data_Exchange (Default_SAP)..46 6.2.6 Global_Control (SAP 58) ..........50 6.2.7 RD_Input (SAP 56) ............51 6.2.8 RD_Output (SAP 57) ............51 6.2.9 Get_Cfg (SAP 59)............52 Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 4 10.7.3 Timing in the Asynchronous Intel Mode......87 10.7.4 Timing in the Synchronous Motorola Mode ....89 10.7.5 Timing in the Asynchronous Motorola Mode ....91 10.8 Package ..................94 10.9 Processing Instructions ..............96 Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 5: Introduction

VPC3+C in existing applications without any restrictions or SW- modifications. However, downgrading from VPC3+C to VPC3+ is only possible, if the additional features of VPC3+C (4K Byte RAM, DP-V1- or DP-V2-functionality, 3.3V supply) are not used. As there are also simple devices in the automation engineering area, such... - Page 6 1 Introduction Notes: Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 7: Functional Description

80C166/165/167 Motorola: HC11-, HC16-, and HC916 types The VPC3+C handles the physical layer 1 and the data link layer 2 of the ISO/OSI-reference-model excluding the analog RS485 drivers. The integrated 4K Byte Dual-Port-RAM serves as an interface between the VPC3+C and the software/application. In case of using 2K Byte the entire memory is divided into 256 segments, with 8 bytes each. - Page 8 Station_Address, etc.) and the data buffers. In the UART, the parallel data flow is converted into the serial data flow and vice-versa. The VPC3+C is capable of automatically identifying the baud rates (9.6 Kbit/s - 12 Mbit/s). The Idle Timer directly controls the bus times on the serial bus line.

-

Page 9: Pin Description

Address Bus CPU, Memory C165 Mode: Address Bus Serial Transmit Port PROFIBUS Interface Request to Send PROFIBUS Interface C32 mode: ‘0’ I(C) Address Bus CPU, Memory C165 mode: Address Bus Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 10 Beginning with Step B of the VPC3+ the communication RAM has been extended to 4K Byte, whereas Step A only has 2K Byte. To access the entire 4K Byte RAM in VPC3+C an additional address signal AB11 is required. Which pin is assigned to A11 depends on the Processor Interface Mode used (see Figure 3-2).

-

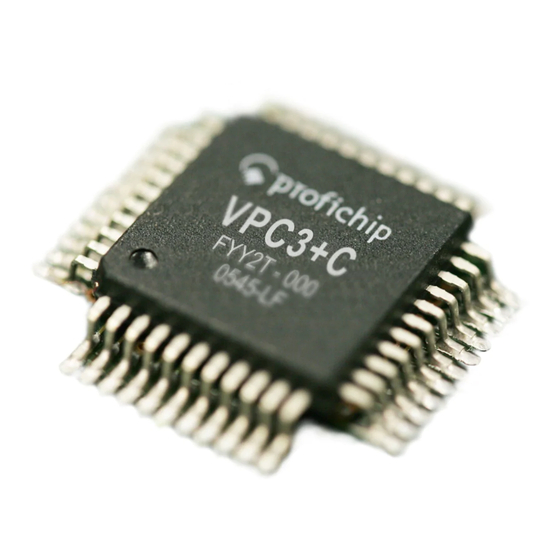

Page 11: Pinout

Pin Description 3 Pinout VPC3+C has a 44-pin PQFP housing with the following pinout: XTEST0 XTEST1 RESET XREADY/XDTACK XDATAEXCH/SYNC Figure 3-3: VPC3+C Pinout For details about package outline and dimensions see section 10.8. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 12 3 Pin Description Notes: Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 13: Memory Organization

Data out means output data from DP-Master to DP-Slave number of buffers depends on the entries in the SAP-List **** DXB out means input data from another DP-Slave (slave-to-slave communication) Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 14 4 Memory Organization Internal VPC3+C RAM (2K/4K Byte) Segment 0 Segment 1 Segment 2 8/16 bit segment addresses (pointer to the buffers) Segment 254 Segment 255 Building of the physical buffer address: 2K Byte Mode: Segment base address (8 bit)

-

Page 15: Control Parameters (Latches/Registers)

Control Parameters (Latches/Registers) These cells can be either read-only or write-only. In the Motorola Mode the VPC3+C carries out ‘address swapping’ for an access to the address locations 00H - 07H (word registers). That is, the VPC3+C internally generates an even address from an odd address and vice-versa. - Page 16 Sync Pulse Width Register Control_Command value for Control_Command_Reg 7..0 comparison with SYNCH telegram Group_Select value for comparison Group_Select_Reg 7..0 with SYNCH telegram Reserved Figure 4-3: Assignment of the Internal Parameter-Latches for WRITE Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 17: Organizational Parameters (Ram)

These parameters can be written and read. Address Intel Mot. Name Bit No. Significance R_TS_Adr Setup Station_Address of the VPC3+C Pointer to a RAM address which is preset SAP_List_Ptr with FFh or to SAP-List R_User_WD_Value 7..0 In DP_Mode an internal 16-bit watchdog timer monitors the user. - Page 18 Register 0), this cell defines the length of the Prm_Buf. R_DXBout_Buf_Ptr2 Segment base address of DXBout_Buf 2 R_DXBout_Buf_Ptr3 Segment base address of DXBout_Buf 3 Figure 4-4: Assignment of the Organizational Parameters Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 19: Asic Interface

**) When a large number of parameters have to be transmitted from the DP-Master to the DP-Slave, the Aux-Buffer 1/2 must have the same length as the Parameter-Buffer. Sometimes this could reach the limit of the available memory in the VPC3+C. When Spec_Prm_Buf_Mode = 1 the parameterization data are processed directly in this special buffer and the Aux-Buffers can be held compact. - Page 20 1 = Monitoring the following start bit is switched off Set_Prm telegram overwrites this memory cell in the DP_Mode. (Refer to the user specific data.) Figure 5-1: Coding of Mode Register 0, Low-Byte Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 21: Mode Register 1

1 = PrmCmd is supported bit 13 Spec_Clear_Mode: Special Clear Mode (Fail Safe Mode) 0 = No special clear mode. 1 = Special clear mode. VPC3+C will accept data telegrams with data unit = 0 bit 12 Spec_Prm_Buf_Mode: Special-Parameter-Buffer Mode 0 = No Special-Parameter-Buffer. - Page 22 After this action, VPC3+ sets User_LEAVE-MASTER to ’0’ again. bit 2 Go_Offline: Going into the Offline state 1 = After the current request ends, VPC3+C goes to the Offline state and sets Go_Offline to ’0’ again. bit 1 EOI: End-of-Interrupt 1 = VPC3+C disables the interrupt output and sets EOI to ’0‘...

-

Page 23: Mode Register 2

Setting parameters for Mode Register 2 may take place in the Offline State only (like Mode Register 0). Bit Position Address Designation Reset Value Mode Reg 2 7 .. 0 Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 24 0 = New_GC_Command interrupt is only generated, if a changed Global_Control telegram is received 1 = New_GC_Command interrupt is generated after every Global_Control telegram (default) Figure 5-4: Coding of Mode Register 2 Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 25: Status Register

ASIC Interface 5 Status Register The Status Register shows the current VPC3+C status and can be read only. Bit Position Address Designation Status-Reg WD_State DP_State (Intel) 7..0 See below for coding Bit Position Address Designation Status-Reg (Intel) 15..8 VPC3+ Release... - Page 26 0111 = 45,45 Kbit/s 1000 = 19,20 Kbit/s 1001 = 9,60 Kbit/s 1111 = after reset and during baud rate search Rest = not possible Figure 5-6: Status Register, High-Byte Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 27: Interrupt Controller

1 ms expires. This interrupt inactive time can be set via EOI_Time_Base in Mode Register 0. This makes it possible to enter the interrupt routine again when an edge-triggered interrupt input is used. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... -

Page 28: Interrupt Request Register

5.3.1 Interrupt Request Register Bit Position Address Designation Int-Req-Reg 7 .. 0 (Intel) See below for coding Bit Position Address Designation Int-Req-Reg 15 .. 8 (Intel) See below for coding Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 29 ASIC Interface 5 Interrupt-Request-Register, Low-Byte, Address 00H (Intel): bit 7 DXB_Out: VPC3+C has received a DXB telegram and made the new output data available in the ‘N’ buffer. bit 6 New_Ext_Prm_Data: The VPC3+C has received a Set_Ext_Prm telegram and made the data available in the Parameter-Buffer.

- Page 30 5 ASIC Interface Interrupt Request Register 0, High-Byte, Address 01H (Intel): bit 15 FDL_Ind: The VPC3+C has received an acyclic service request and made the data available in an Indication-Buffer. bit 14 Poll_End_Ind: The VPC3+C have send the response to an acyclic service.

-

Page 31: Interrupt Acknowledge / Mask Register

User_Prm_Data_Okay etc.). Watchdog Timer The VPC3+C is able to identify the baud rate automatically. The state ma- chine is in the BAUD_SEARCH state after each RESET and also after the Watchdog (WD) Timer has expired in the BAUD_CONTROL state. -

Page 32: Automatic Baud Rate Identification

5 ASIC Interface 5.4.1 Automatic Baud Rate Identification The VPC3+C starts searching for the transmission rate using the highest baud rate. If no SD1 telegram, SD2 telegram, or SD3 telegram was received completely and without errors during the monitoring time, the search continues using the next lower baud rate. - Page 33 ASIC Interface 5 If the monitoring time expires, the VPC3+C goes to BAUD_CONTROL state again and generates the WD_DP_CONTROL_Timeout interrupt. In addition, the DP State Machine is reset, that is, it generates the reset states of the buffer management. This operation mode is recommended for the most applications.

- Page 34 5 ASIC Interface Notes: Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 35: Profibus Dp Interface

PROFIBUS DP Interface PROFIBUS DP Interface DP Buffer Structure The DP_Mode is enabled in the VPC3+C with ‘DP_Mode = 1’ (see Mode Register 0). In this mode, the following SAPs are permanently reserved: Default SAP: Write and Read data (Data_Exchange) - Page 36 Parameter- Buffer Figure 6-1: DP_SAP Buffer Structure The VPC3+C first stores the parameter telegrams (Set_Slave_Add and Set_(Ext_)Prm) and the configuration telegram (Chk_Cfg) in Aux-Buffer 1 or Aux-Buffer 2. If the telegrams are error-free, data is exchanged with the corresponding target buffer (Set_Slave_Add-Buffer, Parameter-Buffer and Config-Buffer).

- Page 37 Aux-Buffer 2 available (R_Aux_Buf_Sel: Set_Prm = 1) for this telegram. The other telegrams are then read via Aux-Buffer 1 (R_Aux_Buf_Sel: Set_Slave_Adr = 0, Chk_Cfg = 0). If the buffers are too small, the VPC3+C responds with “no resources” (RR)! Bit Position...

-

Page 38: Description Of The Dp Services

R_TS_Adr und R_Real_No_Add_Change RAM registers. If SAP55 is enabled and the Set_Slave_Add telegram is received correctly, the VPC3+C enters the pure data in the Aux-Buffer 1/2, exchanges the Aux-Buffer 1/2 for the Set_Slave_Add-Buffer, stores the entered data length in R_Len_SSA_Data, generates the New_SSA_Data interrupt and internally stores the New_Slave_Add as Station_Address and the No_Add_Chg as Real_No_Add_Chg. -

Page 39: Set _Prm (Sap 61)

User_Prm_Data), or the first eight data bytes (with User_Prm_Data). The first seven bytes are specified according to the standard. The eighth byte is used for VPC3+C specific characteristics. The additional bytes are available to the application. If a PROFIBUS DP extension shall be used, the bytes 7-9 are called DPV1_Status and must be coded as described in section 7, “PROFIBUS DP Extensions”. - Page 40 6 PROFIBUS DP Interface Bit Position Byte Designation Station Status WD_Fact_1 WD_Fact_2 minT Ident_Number_High Ident_Number_Low Group_Ident Spec_User_Prm_Byte /DPV1_Status_1 DPV1_Status_2 DPV1_Status_3 User_Prm_Data Figure 6-5: Format of the Set_Prm Telegram Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 41 1 = Start bit monitoring in the receiver is disabled Figure 6-6: Spec_User_Prm_Byte / DPV1_Status_1 It is recommended not to use the DPV1_Status bytes (bytes 7-9) for user parameter data. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 42 In the case of a positive validation of more than seven data bytes, the VPC3+C carries out the following reaction: The VPC3+C exchanges Aux-Buffer 1/2 (all data bytes are entered here) for the Parameter-Buffer, stores the input data length in R_Len_Prm_Data and triggers the New_Prm_Data interrupt.

-

Page 43: Chk_Cfg (Sap 62)

Cfg_Conflict signal during the positive or negative acknowledgement of the first Chk_Cfg telegram. Then the user must repeat the validation, because the VPC3+C have made a new Config-Buffer available. The User_Cfg_Data_Okay_Cmd and User_Cfg_Data_Not_Okay_Cmd acknowledgements are read accesses to defined memory cells with the relevant Not_Allowed, User_Cfg_Finished, or Cfg_Conflict signals. -

Page 44: Slave_Diag (Sap 60)

Two buffers are available for diagnosis. These two buffers can have different lengths. One Diagnosis-Buffer, which is sent on a diagnosis request, is always assigned to the VPC3+C. The user can pre-process new diagnosis data in the other buffer parallel. If the new diagnosis data are to... - Page 45 Figure 6-9: Diagnosis Buffer Assignment The New_Diag_Cmd is also a read access to a defined control parameter indicating which Diagnosis-Buffer belongs to the user after the exchange or whether both buffers ar e currently assigned to the VPC3+C (No_Buffer, iag_Buf1, Diag_Buf2). Bit Position Address...

-

Page 46: Write_Read_Data / Data_Exchange (Default_Sap)

For power-on, LEAVE-MASTER and the Global_Control telegram with ‘Clear_Data = 1’, the VPC3+C deletes the ‘D’ buffer and then shifts it to ‘N'. This also takes place during power-up (entering the WAIT-PRM state). If the user fetches this buffer, he receives U_Buffer_Cleared during the Revision 1.03... - Page 47 Figure 6-12: Dout-Buffer Management When reading the Next_Dout_Buffer_Cmd the user gets the information which buffer (‘U’ buffer) belongs to the user after the change, or whether a change has taken place at all. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 48 (cleared) data can be sent for a RD_Output telegram before the first data cycle. Reading Inputs The VPC3+C sends the input data from the ‘D’ buffer. Prior to sending, the VPC3+C fetches the Din-Buffer from ‘N’ to ‘D'. If no new buffer is present in ‘N', there is no change. user makes...

- Page 49 00 = Nil 01 = Din_Buf_Ptr1 10 = Din_Buf_Ptr2 11 = Din_Buf_Ptr3 Figure 6-14: Din-Buffer Management Bit Position Address Designation ⇓ ⇓ New_Din_Buf_Cmd Din_Buf_Ptr1 Din_Buf_Ptr2 Din_Buf_Ptr3 Figure 6-15: Coding of New_Din_Buf_Cmd Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 50: Global_Control (Sap 58)

The interrupt behavior regarding to the reception of a Global_Control telegram can be configured via bit 8 of Mode Register 2. The VPC3+C either generates the New_GC_Control interrupt after each receipt of a Global_Control telegram (default) or just in case if the Global_Control differs from the previous one. -

Page 51: Rd_Input (Sap 56)

6.2.8 RD_Output (SAP 57) The VPC3+C fetches the output data from the Dout_Buffer in ‘U’. The user must preset the output data with ‘0’ during start-up so that no invalid data can be sent here. If there is a buffer change from ‘N’ to ‘U’ (through the Next_Dout_Buffer_Cmd) between the first call-up and the repetition, the new output data is sent during the repetition. -

Page 52: Get_Cfg (Sap 59)

Config-Buffer, sets ‘En_Change_Cfg_buffer = 1’ (see Mode Register 1) and the VPC3+C then exchanges the Config-Buffer for the Read_Config-Buffer. If there is a change in the configuration data during operation (for example, for a modular DP systems), the user must return with Go_Offline command (see Mode Register 1) to WAIT-PRM. -

Page 53: Profibus Dp Extensions

If the DP-Slave requires Fail_Safe but the DP-Master doesn’t the Prm_Fault bit is set. If the VPC3+C should be used for DXB, IsoM or redundancy mode, the parameterization data must be packed in a Structured_Prm_Data block to distinguish between the User_Prm_Data. The bit Prm_Structure indicates this. -

Page 54: Profibus Dp-V1

PROFIBUS DP-V1 7.2.1 Acyclic Communication Relationships The VPC3+C supports acyclic communication as described in the DP-V1 specification. Therefore a memory area is required which contains all SAPs needed for the communication. The user must do the initialization of this area (SAP-List) in Offline state. Each entry in the SAP-List consists of 7 bytes. - Page 55 SAP_Number: 0 – 51 Byte 1 Request_SA: The source address of a request is compared with this value. At differences, the VPC3+C response with “no service activated” (RS). The default value for this entry is 7FH. Byte 2 Request_SSAP: The source SAP of a request is compared with this value. At differences, the VPC3+C response with “no service activated”...

- Page 56 (RS) or if no free buffer is available with “no resource” (RR). After finishing the processing of the incoming telegram, the INUSE bit is reset and the bits USER and IND are set by VPC3+C. Now the FDL_Ind interrupt is generated. Polling telegrams do not produce interrupts. The RESP bit indicates response data, provided by the user in the Response- Buffer.

-

Page 57: Diagnosis Model

Poll_End_Ind interrupt clear Poll_End_Ind interrupt search for SAP with Response_Sent = 1 clear Response_Sent Figure 7-6: FDL-Interface of VPC3+C (e.g. same Buffer for Indication and Response) 7.2.2 Diagnosis Model The format of the device related diagnosis data depends on the GSD keyword DPV1_Slave in the GSD. -

Page 58: Profibus Dp-V2

+ 2 T All Data_Exchange telegrams containing the function code 7 (Send and Request Data Multicast) are responded with destination address 127. If Publisher mode is not enabled, these requests are ignored. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 59 Structured_Lengt Structure_Type Slot_Number Reserved Version Publisher_Addr Publisher_Length Sample_Offset Sample_Length further link entries Figure 7-8 at o f th truc ed_P ta w ith DXB Li ecific link is grey caled Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 60 DXB_Link_Buf and set R_Len_DXB_Link_Buf. Also the user must enter the default status message in DXB_Status_Buf with the received links and write the appropriate values to R_Len_DXB_Status_Buf. After that, the parameterization interrupt can be acknowledged. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 61 The VPC3+C processes DXBout-Buffers like the Dout-Buffers. The only difference is that the DXBout-Buffers are not cleared by the VPC3+C. The VPC3+C writes the received and filtered broadcast data in the 'D' buffer. The buffer contains also the Publisher_Address and the Sample_Length.

- Page 62 01 = DXBout_Buf_Ptr1 10 = DXBout_Buf_Ptr2 11 = DXBout_Buf_Ptr3 bit 1-0 D: Assignment of the D-Buffer 00 = Nil 01 = DXBout_Buf_Ptr1 10 = DXBout_Buf_Ptr2 11 = DXBout_Buf_Ptr3 Figure 7-12: DXBout-Buffer Management Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 63 In state DATA-EXCH the links are monitored in intervals defined by the parameterized watchdog time. After the monitoring time runs out, the VPC3+C evaluates the Link_Status of each Publisher and updates the bit Link_Status. The timer restarts again automatically. Link_...

-

Page 64: Isom (Isochron Mode)

The IsoM synchronizes DP-Master, DP-Slave and DP-Cycle. The isochron cycle time starts with the transmission of the SYNCH telegram by the IsoM master. If the VPC3+C supports the IsoM, a synchronization signal at Pin 13 (XDATAEXCH/SYNC) is generated by each reception of a SYNCH telegram. - Page 65 Isochron Mode To enable the Isochron Mode in the VPC3+C, bit SYNC_Ena in Mode Register 2 must be set. Additionally the Spec_Clear_Mode in Mode Register 0 must be set. The polarity of the SYNC signal can be adjusted with the SYNC_Pol bit.

- Page 66 7 PROFIBUS DP Extensions Bit Position Byte Designation Station_Status WD_Fact_1 WD_Fact_2 minT Ident_Number_High Ident_Number_Low Group_Ident DPV1_Status_1 DPV1_Status_2 DPV1_Status_3 User_Prm_Data Figure 7-18: Format of Set_Prm telegram for IsoM Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 67 For this mechanism the interrupt controller ist used. Hence no signal will be generated, if the mask for DX_Out in the IMR is set. Since the synchronization signal is now the DX_Out interrupt, it remains until the interrupt acknowledge. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 68 7 PROFIBUS DP Extensions Notes: Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 69: Hardware Interface

RAM belong to the processor interface of the VPC3+C. The VPC3+C is supplied with a clock pulse rate of 48MHz. In addition, a clock divider is integrated. The clock pulse is divided by 2 (Pin: DIVIDER = '1') or 4 (Pin: DIVIDER = '0') and applied to the pin CLKOUT 2/4. - Page 70 8 Hardware Interface used in the synchronous Intel mode. One figure shows the minimum con- figuration of a system with the VPC3+C, where the chip is connected to an EPROM version of the controller. Only a clock generator is necessary as an additional device in this configuration.

- Page 71 The lower address bits AB7..0 are stored with the ALE signal in an in- ternal address latch. The internal CS decoder is activated. VPC3+C generates its own CS signal from the address lines AB10..3. The VPC3+C selects the relevant address window from the AB2..0 signals.

- Page 72 This means additional hardware and a fixed assignment. If the CPU is clocked by the VPC3+C, the output clock pulse (CLKOUT 2/4) must be 4 times larger than the E_Clock. That is, a clock pulse sig- nal must be present at the CLK input that is at least 10 times larger than the desired system clock pulse (E_Clock).

-

Page 73: Application Examples (Principles)

Por t 2 PSEN AB 15..0 AB10 VPC3+ Reset Reset Mode Address- EPROM Decoder 3K 3 64kB 32kB 1K 1K RD W R Figure 8-4: 80C32 System with External Memory Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 74 DB 15..0 (82288) + 82244 VPC3+ AB(10..0) AB 12..1 AB 23..0 VPC3+ Reset Reset driver, control logic Mode CSRAM address EPROM CSEPROM decoder 64kB 32kB Figure 8-5: 80286 System (X86 Mode) Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 75: Application With 80C32 (2K Byte Ram Mode)

Figure 8-6: 80C32 Application in 2K Byte mode The internal chipselect is a ctivated when the address inputs AB[10..3] of the VPC3+C are set to '0'. the example above the start address of the VPC3+C is set to 1000H. Processor VPC3+ B DB[7..0] address AD[7..0]... -

Page 76: Application With 80C32 (4K Byte Ram Mode)

Figure 8-8: 80C32 Application in 4K Byte mode The internal chipselect is activated when the address inputs AB[10..3] of the VPC3+C are set to '0'. In the example above the start address of the VPC3+C is set to 2000H. Processor VPC3+ B DB[7..0]... -

Page 77: Application With 80C165

AB(10..0) Figure 8-10: 80C165 Application Dual Port RAM Controller The internal 4K Byte RAM of the VPC3+C is a single-port RAM. An integrated Dual-Port RAM controller, however, permits an almost simultaneous access of both ports (bus interface and microsequencer interface). When there is a simultaneous access of both ports, the bus interface has priority. -

Page 78: Uart

(not in the target hardware environment!). Name Value Function VSS (GND) All outputs high-resistance XTEST0 Normal VPC3+ function VSS (GND) Various test modes XTEST1 Normal VPC3+ function Figure 8-11: Test Ports Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... -

Page 79: Profibus Interface

PROFIBUS Interface PROFIBUS Interface Pin Assignment The data transmission is performed in RS485 operating mode (i.e., physical S485). The VPC3+C is connected via the following signals to galvanically isolated in terface drivers. Signal Name Input/Output Function Output Request to send... -

Page 80: Example For The Rs485 Interface

To minimize the capacity of the bus lines the user should avoid additional capacities. The typical capa city of a bus statio n should be 15...25 pF. Figure 9-2: Example for the RS485 Interface Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... -

Page 81: Operational Specifications

Input LOW current µA Input HIGH current µA Tri-state leakage current +1 0 µA Current consumption (3.3V) Current consumption (5V) Input capacitance Output capacitance Bi-directional buffer capacitance Figure 10-3: General DC Characteristics Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... -

Page 82: Ratings For The Output Drivers

Output current HIGH level, 4mA cell -4.0 Output current LOW level, 8mA cell Output current HIGH level, 8mA cell -8.0 Figure 10-5: DC Specification of I/O Drivers for 5V Operation Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... -

Page 83: Dc Electrical Characteristics Specification For 3.3V Operation

Figure 10-6: DC Specification of I/O Drivers for 3.3V Operation otes: For 3.3V operation the VPC3+C is equipped with 5V tolerant inputs except or the clock pin CLK. When using 3.3V supply voltage the clock input needs o be 3.3V level. -

Page 84: Timing Characteristics

CLK. When using 3.3V supply voltage the clock input needs to be 3.3V level. Interrupt: After acknowledging an interrupt with EOI, the interrupt output of the VPC3+C is deactivated for at least 1 us or 1 ms depending on the bit EOI_Time_Base in Mode Register 0. Parameter Unit Interrupt inactive time EOI_Timebase = ‘0’... -

Page 85: Timing In The Synchronous Intel Mode

. Th reques t for an access to the VPC3+C is generated from the fa llin g ed read signal (XRD) and from the rising edge of the write signal (XWR). - Page 86 XRD / XWR cycletime ALE ↓ to XWR ↓ XWR pulsewidth data setuptime to XWR ↑ XWR ↑ to ALE ↑ data holdtime after XWR ↑ Figure 10-11: Timing, Synchronous Intel Mode Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 87: 10.7.3 Timing In The Asynchronous Intel Mode

In the asynchronous Intel mode, the VPC3+C acts like a memory with ready logic. The access time depends on the type of access. The request for an access to the VPC3+C is generated from the falling edge of the read signal (XRD) or the rising edge of the write signal (XWR). - Page 88 XCS holdtime after XRD / XWR ↑ XREADY holdtime after XRD / XWR data setuptime to XWR ↑ XWR pulsewidth data holdtime after XWR ↑ Figure 10-14: Timing, Asynchronous Intel Mode Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 89: 10.7.4 Timing In The Synchronous Motorola Mode

Operational Specifications 10 10.7.4 Timing in the Synchronous Motorola Mode If the CPU is clocked by the VPC3+C, the output clock pulse (CLKOUT 2/4) must be 4 times larger than the E_Clock. That is, a clock pulse signal must be present at the CLK input that is at least 10 times larger than the desired system clock pulse (E_Clock). - Page 90 R_W holdtime after E_Clock ↓ XCS setuptime to E_Clock ↑ XCS holdtime after E_Clock ↓ Data setuptime to E_Clock ↓ Data holdtime after E_Clock ↓ Figure 10-17: Timing, Synchronous Motorola Mode Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 91: 10.7.5 Timing In The Asynchronous Motorola Mode

Ready logic, whereby the access times depend on the type of access. The request for an access of the VPC3+C is generated from the falling edge of the AS signal (in addition: XCS = '0', R_W = '1'). The request for a write access is generated from the rising edge of the AS signal (in addition: XCS = '0', R_W = '0'). - Page 92 10 Operational Specifications AB10..0 valid DB7..0 data alid XDTACK (normal) XDTACK (early) Figure 10-19: Asynchronous Motorola Mode (WRITE) Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 93 XCS holdtime after AS ↑ XDTACK holdtime after AS ↑ Data setuptime to AS ↑ AS pulsewidth (write access) Data holdtime after AS ↑ Figure 10-20: Timing, Asynchronous Motorola Mode Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 94: Package

10 Operational Specifications 10.8 Package Figure 10-21: Package Drawing Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006... - Page 95 2. Dimension b does not include dambar protrusion. Allowable dambar protrusion shall be 0.08 mm total in excess of the b dimension at maximum material condition. Dambar cannot be located on the lower radius of the lead foot. Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

-

Page 96: Processing Instructions

The VPC3+C is a cracking-endangered component that must be properly handled. A drying process must be carried out before the VPC3+C is processed. The component must be dried for 24 hours at 125°C and then processed within 48 hours. Due to the solderability of the component this drying process may be carried out once only. - Page 97 10.05.2004 First release V1.01 18.07.2004 Re-formatting and correction of typing errors V1.02 22.09.2004 Some minor corrections V1.03 12.01.2006 Consecutive paging Additional figures for FDL-Interface Figure 9-2 updated Figure 10-10 revised Revision 1.03 VPC3+C User Manual Copyright © profichip GmbH 2004-2006...

- Page 98 GmbH Einsteinstrasse 6 91074 Herzogenaurach Germany Phone : +49.9132.744-200 Fax: +49.9132.744-204 Th e Cl e ver Al t er n a t i ve www.profichip.com...

Need help?

Do you have a question about the VPC3+C and is the answer not in the manual?

Questions and answers