Table of Contents

Advertisement

Quick Links

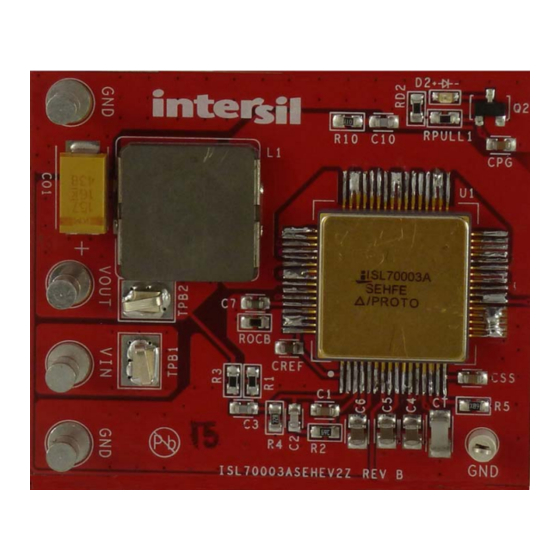

ISL70003ASEHEV2Z Evaluation Board User Guide

The ISL70003ASEHEV2Z evaluation board is designed to

demonstrate the performance of the

as a 12V input to 3.3V output, 6A output current POL regulator,

with a significantly reduced size footprint compared to the

ISL70003ASEHEV1Z platform, making it ideal for wiring into

an existing circuit. For more detailed information, please refer

to the

ISL70003ASEH

datasheet.

The ISL70003ASEHEV2Z evaluation board accepts a nominal

input voltage of 12V and provides a regulated output voltage of

3.3V with output current ranging from 0A to 6A. There is a green

LED indicating PGOOD. The input voltage and output voltage

presets can be changed to alternate voltages by resistor

substitutions.

The ISL70003ASEHEV2Z evaluation board is configured to run

from the nominal 300kHz internal oscillator of the

ISL70003ASEH.

Specifications

This board has been configured and optimized for the following

operating conditions:

• 12V V

, 3.3V V

, I

= 6A maximum

IN

OUT

OUT

• Power density of 9W/sq. inch of active area

• 89% peak efficiency

V

IN

August 28, 2015

UG046.0

ISL70003ASEH

product

ISL70003ASEH

FIGURE 1. ISL70003ASEHEV2Z BLOCK DIAGRAM

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

Key Features

• Simple to use

• Small size PCB, 2.25 sq. inches

• Power-good LED

References

ISL70003ASEH

Datasheet

Ordering Information

PART NUMBER

ISL70003ASEHEV2Z

ISL70003ASEH radiation and SEE

hardened 3V to 12V, 6A synchronous buck

regulator evaluation board

|

Copyright Intersil Americas LLC 2015. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

User Guide 046

DESCRIPTION

V

OUT

Advertisement

Table of Contents

Summary of Contents for Intersil ISL70003ASEHEV2Z

-

Page 1: Key Features

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-468-3774 Copyright Intersil Americas LLC 2015. All Rights Reserved UG046.0 Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries. All other trademarks mentioned are the property of their respective owners. - Page 2 User Guide 046 ISL70003ASEHEV2Z Evaluation Board FIGURE 2. ISL70003ASEH TOP VIEW FIGURE 3. ISL70003ASEH BOTTOM VIEW Submit Document Feedback UG046.0 August 28, 2015...

-

Page 3: What's Inside

3.3V on this circuit. To modify the output voltage, substitute for a different value according to Equation PCB Plane Allocation On the ISL70003ASEHEV2Z, four layers of two ounce copper is (EQ. 1) k... - Page 4 User Guide 046 Heatsink Mounting Guidelines When designing for >6A of output current place a Schottky clamp diode as close as possible to the LXx and PGNDx pins of The R64.C package has a heatsink mounted on the underside of the IC.

-

Page 5: Typical Performance Curves

0.06 0.04 0.02 0.00 -0.02 LOAD CURRENT (A) LOAD CURRENT (A) FIGURE 5. ISL70003ASEHEV2Z AMBIENT LOAD REGULATION FIGURE 4. EFFICIENCY vs LOAD vs TEMPERATURE = 12V, V = 3.3V, f = 300kHz LXx VOLTAGE, 5V/DIV LXx VOLTAGE, 5V/DIV OUTPUT VOLTAGE, 50mV/DIV... - Page 6 TO OUTPUT CAPACITOR GROUND. DRAWN BY: DATE: ENGINEER: DATE: TIM KLEMANN LARRY GOUGH 06/22/2015 RELEASED BY: DATE: TITLE: ISL70003ASEH UPDATED BY: DATE: EVALUATION / DEMO 2N7002-7-F BOARD SCHEMATIC TESTER MASK# HRDWR ID REV. ISL70003ASEHEV2Z FILENAME: SHEET FIGURE 10. ISL70003ASEHEV2Z SCHEMATIC...

-

Page 7: Bill Of Materials

Bill of Materials REFERENCE DESIGNATOR QTY UNITS DESCRIPTION PART NUMBER MANUFACTURER PWB-PCB, ISL70003ASEHEV2ZREVBPCB IMAGINEERING INC ISL70003ASEHEV2Z, REVB, ROHS CAP, SMD, 1206, 390pF, 50V, 12065A391FAT2A 1%, C0G, ROHS CC1, CC2 CAPACITOR, SMD, 1812, 10µF, C4532X7R1E106M 25V, 20%, X7R CAPACITOR, SMD, 2220, 10µF,... - Page 8 RES, SMD, 0805, 100k, 1/8W, CR0805-8W-1003FT VENKEL 1%, TF, ROHS Place assy in bag BAG, STATIC, 3x5, ZIP LOC D810 (212403-012) INTERSIL COMMON STOCK AFFIX TO BACK OF PCB LABEL-DATE CODE_LINE 1: LABEL-DATE CODE INTERSIL YRWK/REV#, LINE 2: BOM NAME Submit Document Feedback UG046.0...

-

Page 9: Board Layout

User Guide 046 Board Layout FIGURE 11. TOP SILKSCREEN LAYER FIGURE 12. TOP COMPONENT PLACEMENT LAYER Submit Document Feedback UG046.0 August 28, 2015... - Page 10 User Guide 046 Board Layout (Continued) FIGURE 13. LAYER 2 FIGURE 14. LAYER 3 Submit Document Feedback UG046.0 August 28, 2015...

- Page 11 FIGURE 15. BOTTOM COMPONENT LAYER FIGURE 16. BOTTOM SILK SCREEN LAYER Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.

Need help?

Do you have a question about the ISL70003ASEHEV2Z and is the answer not in the manual?

Questions and answers