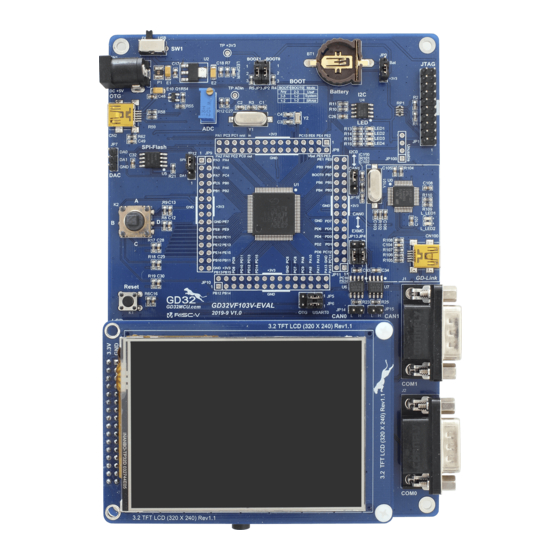

GigaDevice Semiconductor GD32VF103 Manuals

Manuals and User Guides for GigaDevice Semiconductor GD32VF103. We have 2 GigaDevice Semiconductor GD32VF103 manuals available for free PDF download: User Manual

GigaDevice Semiconductor GD32VF103 User Manual (536 pages)

RISC-V 32-bit MCU

Brand: GigaDevice Semiconductor

|

Category: Microcontrollers

|

Size: 10 MB

Table of Contents

-

-

Risc-V Cpu22

-

Memory Map24

-

-

-

Overview32

-

-

Mass Erase34

-

-

Overview47

-

VDD /V Dda48

-

Power Domain51

-

-

Overview57

-

-

-

-

Overview94

-

-

Characteristics102

-

Overview102

-

-

Introduction108

-

Main Features108

-

-

-

-

-

-

Overview129

-

Characteristics129

-

-

-

Characteristics133

-

Overview133

-

Block Diagram134

-

-

DMA Operation134

-

Circular Mode137

-

-

Arbitration136

-

-

10 Debug (DBG)

148-

Overview148

-

-

Pin Assignment148

-

Debug Reset149

-

-

-

-

Introduction153

-

Main Features153

-

ADC Clock156

-

ADCON Switch156

-

Conversion Modes156

-

ADC Interrupts173

-

ADC Registers174

-

-

Data Alignment161

-

DMA Request163

-

External Trigger163

-

Refint163

-

ADC Sync Mode166

-

Free Mode167

-

-

-

Characteristics188

-

Overview188

-

DAC Conversion190

-

DAC Trigger190

-

DMA Request192

-

-

-

-

-

Overview202

-

Characteristics202

-

-

-

Overview208

-

Characteristics208

-

-

-

-

Characteristics213

-

-

RTC Reset214

-

RTC Reading214

-

-

Overview213

-

-

Characteristics223

-

Overview223

-

Block Diagram224

-

-

-

-

15 Timer(Timerx)

222-

-

-

-

Block Diagram318

-

Characteristics318

-

Overview318

-

-

-

-

Overview279

-

Characteristics279

-

Block Diagram279

-

-

-

-

Characteristics328

-

Overview328

-

-

-

LIN Mode337

-

Synchronous Mode338

-

-

USART Receiver333

-

USART Interrupts342

-

-

-

Characteristics354

-

Overview354

-

Arbitration357

-

-

Smbus Support368

-

-

-

-

Characteristics380

-

Overview380

-

-

NSS Function382

-

-

CRC Function389

-

DMA Function389

-

SPI Interrupts389

-

Status Flags389

-

Error Flags390

-

DMA Function403

-

Error Flags404

-

I2S Interrupts404

-

Status Flags404

-

Operation401

-

-

I2S Clock400

-

-

-

Characteristics416

-

Overview416

-

-

-

Characteristics427

-

Overview427

-

-

Working Mode428

-

-

Data Reception432

-

CAN Interrupts439

-

-

Error Flags438

-

-

-

Characteristics461

-

Overview461

-

Block Diagram462

-

-

-

Operation Guide471

-

Interrupts475

-

-

Data FIFO468

-

Advertisement

GigaDevice Semiconductor GD32VF103 User Manual (65 pages)

Brand: GigaDevice Semiconductor

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

-

Usbd_Conf.h18

-

Usb_Conf.h18

-

Descriptor20

-

IN Direction28

-

Audio29

-

CDC33

-

Dfu36

-

Msc42

-

Hid45

-

USB Printer47

-

Usbh_Conf.h49

-

Usb_Conf.h49

-

Hid Host61

-

Msc Host62

Advertisement

Related Products

- GigaDevice Semiconductor GD32150C-START

- GigaDevice Semiconductor GD32170C-START

- GigaDevice Semiconductor GD32W515 Series

- GigaDevice Semiconductor GD32F403 Series

- GigaDevice Semiconductor GD32F3x0

- GigaDevice Semiconductor GD32F330F8

- GigaDevice Semiconductor GD32H757

- GigaDevice Semiconductor GD32GD32F350 Series

- GigaDevice Semiconductor GD32H7 Series

- GigaDevice Semiconductor GD32F310K-START