Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Holtek HT45F8550

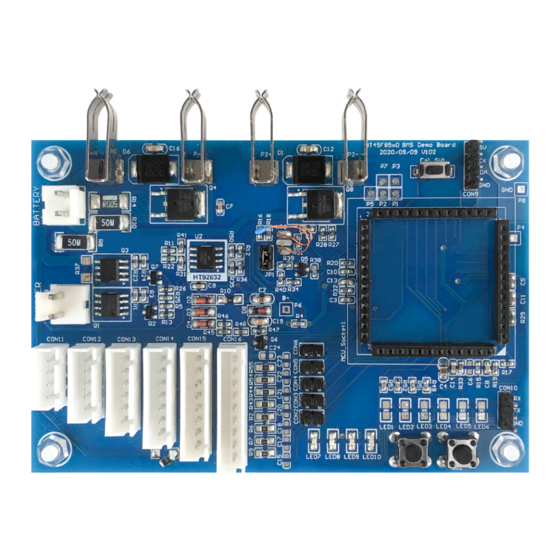

- Page 1 BMS Flash MCU HT45F8550 Revision: V1.70 Date: January 31, 2024...

-

Page 2: Table Of Contents

HT45F8550 BMS Flash MCU Table of Contents Features ......................... 7 CPU Features ..........................7 Peripheral Features ........................7 General Description ....................8 Block Diagram ....................... 9 Pin Assignment ..................... 9 Pin Description ....................10 Interconnection Signal Description ....................14 Absolute Maximum Ratings ................14 Recommended Operating Ratings .............. - Page 3 HT45F8550 BMS Flash MCU Flash Program Memory ..................29 Structure ............................29 Special Vectors ...........................29 Look-up Table ..........................29 Table Program Example ......................30 In Circuit Programming – ICP .....................31 On-Chip Debug Support – OCDS ....................31 In Application Programming – IAP ....................32 Data Memory ....................... 46 Structure ............................46...

- Page 4 HT45F8550 BMS Flash MCU Watchdog Timer ....................73 Watchdog Timer Clock Source ....................73 Watchdog Timer Control Register ....................73 Watchdog Timer Operation ......................74 Reset and Initialisation ..................75 Reset Functions ..........................75 Reset Initial Conditions ......................79 Input/Output Ports ....................82 Pull-high Resistors ........................82 Port A Wake-up ...........................83...

- Page 5 HT45F8550 BMS Flash MCU A/D Conversion Function ......................136 A/D Converter Programming Examples ..................137 Comparator ....................... 138 Comparator Operation ......................138 Comparator Registers .......................138 Comparator Interrupt .........................139 Programming Considerations ....................139 Serial Interface Module – SIM ................140 SPI Interface ..........................140 C Interface ..........................147 UART Interface ....................

- Page 6 HT45F8550 BMS Flash MCU VIN and VBATn Spike Suppression Resistors ................186 Cell Voltage Monitor Scan Frequency ..................186 Voltage Spike Suppression Method ..................188 Thermal Consideration ......................188 Application Circuits ..................190 3S Battery Monitoring Typical Application Circuit ..............190 5S Battery Monitoring Typical Application Circuit ..............191 8S Battery Monitoring Typical Application Circuit ..............192...

-

Page 7: Features

HT45F8550 BMS Flash MCU Features CPU Features • Operating voltage =8MHz: 1.8V~5.5V ♦ =12MHz: 2.7V~5.5V ♦ =16MHz: 3.3V~5.5V ♦ • Up to 0.25μs instruction cycle with 16MHz system clock at V • Power down and wake-up functions to reduce power consumption •... -

Page 8: General Description

BMS Flash MCU General Description The HT45F8550 is a Flash Memory BMS 8-bit high performance RISC architecture microcontroller with an integrated accumulative cell voltage monitor module, designed for BMS applications. For memory features, the Flash Memory offers users the convenience of multi-programming features. -

Page 9: Block Diagram

HT45F8550 BMS Flash MCU Block Diagram Pin- Shared Reset With Port A Circuit BGREF 8K × 16 512 × 8 VREFI INT0~ Interrupt EEPROM Stack INT1 Controller 128 × 8 8-level VREF Pin-Shared Watchdog LVD/LVR With Port A & B... -

Page 10: Pin Description

2. The OCDSDA and OCDSCK pins are used as the OCDS dedicated pins and only available for the HT45V8550 device which is the OCDS EV chip of the HT45F8550. 3. For less pin-count package types there will be unbonded pins which should be properly configured to avoid unwanted current consumption resulting from floating input conditions. - Page 11 HT45F8550 BMS Flash MCU Pin Name Function Description PAS0 General purpose I/O. Register enabled pull-high and PAWU CMOS wake-up PAPU PAS0 PA1/INT0/SDO INTEG INT0 — External Interrupt 0 INTC0 PAS0 — CMOS SPI serial data output PAS0 General purpose I/O. Register enabled pull-high and...

- Page 12 HT45F8550 BMS Flash MCU Pin Name Function Description PBS0 CMOS General purpose I/O. Register enabled pull-high PBPU PBS0 INTEG INT1 — External Interrupt 1 PB1/INT1/AN1/XT2 INTC2 PBS0 — A/D Converter analog input channel 1 PBS0 — LXT oscillator pin PBS0 CMOS General purpose I/O.

- Page 13 HT45F8550 BMS Flash MCU Pin Name Function Description PCS1 CMOS General purpose I/O. Register enabled pull-high PCPU PCS1 PC4/SDI/SDA — SPI serial data input PCS1 NMOS I C data line PCS1 CMOS General purpose I/O. Register enabled pull-high PCPU PCS1...

-

Page 14: Interconnection Signal Description

HT45F8550 BMS Flash MCU Interconnection Signal Description Several lines are not connected to external package pins. These signal lines are interconnected between the MCU and the Accumulative Cell Voltage Monitor and are listed in the following table. Accumulative Cell Function... -

Page 15: D.c. Characteristics

HT45F8550 BMS Flash MCU D.C. Characteristics For data in the following tables, note that factors such as oscillator type, operating voltage, operating frequency, pin load conditions, temperature and program instruction type, etc., can all exert an influence on the measured values. -

Page 16: Standby Current Characteristics

HT45F8550 BMS Flash MCU Standby Current Characteristics Ta=25°C, unless otherwise specified. Test Conditions Max. Symbol Operation Mode Min. Typ. Max. Unit @85°C Conditions 1.8V — 0.45 1.50 3.00 WDT off — 0.45 1.80 3.50 μA — SLEEP Mode 1.8V —... -

Page 17: A.c. Characteristics

HT45F8550 BMS Flash MCU A.C. Characteristics For data in the following tables, note that factors such as oscillator type, operating voltage, operating frequency and temperature etc., can all exert an influence on the measured values. High Speed Internal Oscillator – HIRC During the program writing operation the writer will trim the HIRC oscillator at a user selected HIRC frequency and user selected voltage of either 3V or 5V. -

Page 18: Low Speed Internal Oscillator Characteristics - Lirc

HT45F8550 BMS Flash MCU Low Speed Internal Oscillator Characteristics – LIRC Test Conditions Symbol Parameter Min. Typ. Max. Unit Temp. 25°C LIRC Frequency LIRC 2.2V~5.5V -40°C~85°C -10% +10% LIRC Start-up Time — — — — μs START External Low Speed Crystal Oscillator Characteristics – LXT... -

Page 19: Input/Output Characteristics

HT45F8550 BMS Flash MCU Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions System Reset Delay Time Reset source from Power-on reset or LVR — RR =5V/ms Hardware Reset System Reset Delay Time RSTD — — LVRC/WDTC/RSTC Register Software Reset System Reset Delay Time —... -

Page 20: Memory Characteristics

HT45F8550 BMS Flash MCU Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions External Interrupt Minimum Pulse Width — — — — μs Note: The R internal pull-high resistance value is calculated by connecting to ground and enabling the input pin with a pull-high resistor and then measuring the pin current at the specified supply voltage level. - Page 21 HT45F8550 BMS Flash MCU Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions SAINS[3:0]=0000B, SAVRS[1:0]=01B, =2.0μs ADCK 1.8V SAINS[3:0]=0000B, SAVRS[1:0]=01B, =10μs ADCK SAINS[3:0]=0000B, SAVRS[1:0]=01B, =0.5μs ADCK SAINS[3:0]=0000B, SAVRS[1:0]=01B, Integral Non-linearity — =0.5μs ADCK SAINS[3:0]=0000B, SAVRS[1:0]=01B, =10μs ADCK SAINS[3:0]=0000B, SAVRS[1:0]=01B, =0.5μs...

-

Page 22: Lvd/Lvr Electrical Characteristics

HT45F8550 BMS Flash MCU LVD/LVR Electrical Characteristics Ta=25°C Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions LVR enable, voltage select 1.7V LVR enable, voltage select 1.9V Low Voltage Reset Voltage — LVR enable, voltage select 2.55V -3% 2.55 +3% LVR enable, voltage select 3.15V -3% 3.15 +3%... -

Page 23: Comparator Electrical Characteristics

HT45F8550 BMS Flash MCU Comparator Electrical Characteristics Ta=25°C Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions Operating Voltage — — — — — — Additional Current for Comparator Enable μA — — — — — Power Down Current Comparator disable μA... -

Page 24: Accumulative Cell Voltage Monitor Electrical Characteristics

HT45F8550 BMS Flash MCU Symbol Parameter Test Condition Min. Typ. Max. Unit Voltage Regulator Regulator Output Voltage =10mA 4.95 5.00 5.05 LOAD Regulator Output Current =7.5V, Ta=-40~85 — — ∆V Load Regulation =0~30mA — — LOAD ∆V ×∆V ) Line Regulation =7.5V~36V, I... -

Page 25: I 2 C Electrical Characteristics

HT45F8550 BMS Flash MCU C Electrical Characteristics Ta=25°C Test Conditions Symbol Parameter Min. Typ. Max. Unit Conditions No clock debounce — — C Standard Mode (100kHz) f — 2 system clock debounce — — Frequency (Note) 4 system clock debounce —... -

Page 26: Power-On Reset Characteristics

Time System Architecture A key factor in the high-performance features of the Holtek range of microcontrollers is attributed to their internal system architecture. The device takes advantage of the usual features found within RISC microcontrollers providing increased speed of operation and enhanced performance. The... -

Page 27: Program Counter

HT45F8550 BMS Flash MCU (System Clock) Phase Clock T1 Phase Clock T2 Phase Clock T3 Phase Clock T4 Program Counter PC+1 PC+2 Fetch Inst. (PC) Pipelining Execute Inst. (PC-1) Fetch Inst. (PC+1) Execute Inst. (PC) Fetch Inst. (PC+2) Execute Inst. (PC+1) System Clocking and Pipelining Fetch Inst. -

Page 28: Stack

HT45F8550 BMS Flash MCU Stack This is a special part of the memory which is used to save the contents of the Program Counter only. The stack is organized into 8 levels and neither part of the data nor part of the program space, and is neither readable nor writeable. -

Page 29: Flash Program Memory

HT45F8550 BMS Flash MCU Flash Program Memory The Program Memory is the location where the user code or program is stored. For this device the Program Memory is Flash type, which means it can be programmed and re-programmed a large number of times, allowing the user the convenience of code modification on the same device. - Page 30 HT45F8550 BMS Flash MCU The accompanying diagram illustrates the addressing data flow of the look-up table. Program Memory Last Page or TBHP Register Data 16 bits TBLP Register User Selected Register TBLH Register High Byte Low Byte Table Program Example The following example shows how the table pointer and table data is defined and retrieved from the microcontroller.

-

Page 31: In Circuit Programming - Icp

There is an EV chip named HT45V8550 which is used to emulate the real MCU device named HT45F8550. The EV chip device also provides an “On-Chip Debug” function to debug the real MCU device during the development process. The EV chip and the real MCU device are almost functionally compatible except for “On-Chip Debug”... -

Page 32: In Application Programming - Iap

Program Writer or PC. In addition, the IAP interface can also be any type of communication protocol, such as UART, using I/O pins. Regarding the internal firmware, the user can select versions provided by Holtek or create their own. The following section illustrates the procedures regarding how to implement the IAP firmware. - Page 33 HT45F8550 BMS Flash MCU Write page data to FD0L/FD0H Read data word to FD0H/FD0L (32 words/page) Flash Memory Flash Memory FARH/FARL Page addr. FARH/FARL Word m =FA12~FA5 =FA12~FA0 =FA12~FA0 Page n Write buffer addr. =FA4~FA0 00000b FD0H FD0L Write Buffer Note: “m”...

- Page 34 HT45F8550 BMS Flash MCU Register Name CFWEN FMOD2 FMOD1 FMOD0 FWPEN FRDEN — — — — — — — CLWB FARL FARH — — — FA12 FA11 FA10 FD0L FD0H FD1L FD1H FD2L FD2H FD3L FD3H IAP Register List • FARL Register...

- Page 35 HT45F8550 BMS Flash MCU • FD0H Register Name Bit 7~0 D15~D8: The first Flash Memory data bit 15 ~ bit 8 Note that when 8-bit data is written into the high byte data register FD0H, the whole 16 bits of data stored in the FD0H and FD0L registers will simultaneously be loaded into the 16-bit write buffer after which the contents of the Flash memory address register pair, FARH and FARL, will be incremented by one.

- Page 36 HT45F8550 BMS Flash MCU • FD3H Register Name Bit 7~0 D15~D8: The fourth Flash Memory data bit 15 ~ bit 8 • FC0 Register Name CFWEN FMOD2 FMOD1 FMOD0 FWPEN FRDEN Bit 7 CFWEN: Flash Memory Erase/Write function enable control...

- Page 37 HT45F8550 BMS Flash MCU Bit 0 FRD: Flash Memory read control bit 0: Do not initiate Flash Memory read or indicating that a Flash Memory read process has completed 1: Initiate a Flash Memory read process This bit is set by software and cleared to zero by the hardware when the Flash memory read process has completed.

- Page 38 HT45F8550 BMS Flash MCU the contents is 0000h or not. If the flash memory page erase operation fails, users should go back to Step 2 and execute the page erase operation again. 4. Write data into the specific page. Refer to the “Flash Memory Write Procedure” for details.

- Page 39 HT45F8550 BMS Flash MCU Flash Memory Erase/Write Function Enable Procedure The Flash Memory Erase/Write Function Enable Mode is specially designed to prevent the flash memory contents from being wrongly modified. In order to allow users to change the Flash memory data using the IAP control registers, users must first enable the Flash memory Erase/Write function.

- Page 40 HT45F8550 BMS Flash MCU Flash Memory Erase/Write Function Enable Procedure FMOD[2:0]=110 Set FWPEN=1 Hardware start a timer Wrtie the following pattern to Flash Data register FD1L=00h, FD1H=04h FD2L=0Dh, FD2H=09h FD3L=C3h, FD3H=40h Is timer Time-out FWPEN=0? Is pattern correct? CFWEN=1 CFWEN=0...

- Page 41 HT45F8550 BMS Flash MCU Flash Memory Write Procedure After the Flash memory erase/write function has been successfully enabled as the CFWEN bit is set high, the data to be written into the flash memory can be loaded into the write buffer. The selected flash memory page data should be erased by properly configuring the IAP control registers before the data write procedure is executed.

- Page 42 HT45F8550 BMS Flash MCU Write Flash Memory Flash Memory Erase/Write Function Enable Procedure Page Erase FMOD[2:0]=001 Set CLWB Bit Set Erase Page Address FARH=xxH, FARL=xxH Write dummy data into FD0H (Tag Address) Tag address Finish ? FWT=1 FWT=0 ? Blank Check with Table Read...

- Page 43 HT45F8550 BMS Flash MCU Flash Memory Non-Consecutive Write Description The main difference between Flash Memory Consecutive and Non-Consecutive Write operations is whether the data words to be written are located in consecutive addresses or not. If the data to be written is not located in consecutive addresses the desired address should be re-assigned after a data word is successfully written into the Flash Memory.

- Page 44 HT45F8550 BMS Flash MCU Write Flash Memory Flash Memory Erase/Write Function Enable Procedure Page Erase FMOD[2:0]=001 Set CLWB Bit Set Erase Page Address FARH =xxH, FARL=xxH Write dummy data into FD0H (Tag Address) Tag address Finish ? FWT=1 FWT=0 ?

- Page 45 HT45F8550 BMS Flash MCU Important Points to Note for Flash Memory Write Operations 1. The “Flash Memory Erase/Write Function Enable Procedure” must be successfully activated before the Flash Memory erase/write operation is executed. 2. The Flash Memory erase operation is executed to erase a whole page.

-

Page 46: Data Memory

HT45F8550 BMS Flash MCU Data Memory The Data Memory is a volatile area of 8-bit wide RAM internal memory and is the location where temporary information is stored. Categorised into two types, the first of these is an area of RAM, known as the Special Function Data Memory. -

Page 47: Data Memory Addressing

HT45F8550 BMS Flash MCU Data Memory Addressing For the device that supports the extended instructions, there is no Bank Pointer for Data Memory addressing. The desired Sector is pointed by the MP1H or MP2H register and the certain Data Memory address in the selected sector is specified by the MP1L or MP2L register when using indirect addressing access. - Page 48 HT45F8550 BMS Flash MCU Sector 0 Sector 1 Sector 0 Sector 1 IAR0 IAR1 PCPU MP1L LXTC MP1H SIMC0 SIMC1 TBLP SIMD TBLH SIMC2/SIMA TBHP SIMTOC STATUS VBGRC TB1C IAR2 MFI0 MP2L MFI1 MP2H MFI2 RSTFC SLEDC0 INTEG SLEDC1 INTC0...

-

Page 49: Special Function Register Description

HT45F8550 BMS Flash MCU Special Function Register Description Most of the Special Function Register details will be described in the relevant functional section, however several registers require a separate description in this section. Indirect Addressing Registers – IAR0, IAR1, IAR2 The Indirect Addressing Registers, IAR0, IAR1 and IAR2, although having their locations in normal RAM register space, do not actually physically exist as normal registers. -

Page 50: Accumulator - Acc

HT45F8550 BMS Flash MCU Example 2 data .section ´data´ adres1 db ? adres2 db ? adres3 db ? adres4 db ? block db ? code .section at 0 ´code´ org 00h start: mov a, 04h ; setup size of block... -

Page 51: Program Counter Low Register - Pcl

HT45F8550 BMS Flash MCU Program Counter Low Register – PCL To provide additional program control functions, the low byte of the Program Counter is made accessible to programmers by locating it within the Special Purpose area of the Data Memory. By manipulating this register, direct jumps to other program locations are easily implemented. - Page 52 HT45F8550 BMS Flash MCU • STATUS Register Name “x”: unknown SC: The result of the “XOR” operation which is performed by the OV flag and the MSB Bit 7 of the instruction operation result. Bit 6 CZ: The operational result of different flags for different instructions For SUB/SUBM/LSUB/LSUBM instructions, the CZ flag is equal to the Z flag.

-

Page 53: Eeprom Data Memory

HT45F8550 BMS Flash MCU EEPROM Data Memory This device contains an area of internal EEPROM Data Memory. EEPROM is by its nature a non-volatile form of re-programmable memory, with data retention even when its power supply is removed. By incorporating this kind of data memory, a whole new host of application possibilities are made available to the designer. - Page 54 HT45F8550 BMS Flash MCU • EEC Register Name — EREN MODE WREN RDEN — — Bit 7 Unimplemented, read as “0” EREN: Data EEPROM erase enable Bit 6 0: Disable 1: Enable This bit is used to enable data EEPROM erase function and must be set high before erase operations are carried out.

-

Page 55: Read Operation From The Eeprom

HT45F8550 BMS Flash MCU 2. Ensure that the f clock is stable before executing the erase or write operation. 3. Ensure that the erase or write operation is totally complete before changing the contents of the EEPROM related registers or activating the IAP function. -

Page 56: Write Operation To The Eeprom

HT45F8550 BMS Flash MCU For page erase operations the start address of the desired EEPROM page should first be placed in the EEA registers and the dummy data to be written is placed in the EED registers. The maximum data length for a page is 16 bytes. Note that the write operation to the EED register is used to tag address, it must be implemented to determine which addresses to be erased. -

Page 57: Write Protection

HT45F8550 BMS Flash MCU will not be cleared. A page write is initiated in the same way as a byte write initiation except that the EEPROM data can be written up to 16 bytes. The EEPROM address lower 4 bits are internally incremented by one following the reception of each data byte in the page write mode. -

Page 58: Programming Considerations

HT45F8550 BMS Flash MCU Programming Considerations Care must be taken that data is not inadvertently written to the EEPROM. Protection can be enhanced by ensuring that the Write Enable bit is normally cleared to zero when not writing. Also the Memory Pointer high byte register, MP1H or MP2H, could be normally cleared to zero as this would inhibit access to Sector 1 where the EEPROM control register exists. - Page 59 HT45F8550 BMS Flash MCU MOV READ_DATA, A PAGE_READ_FINISH: CLR IAR1 ; disable EEPROM read function CLR MP1H Erasing a Data Page to the EEPROM − polling method MOV A, 040H ; setup memory pointer low byte MP1L MOV MP1L, A ; MP1L points to EEC register MOV A, 01H ; setup memory pointer high byte MP1H MOV MP1H, A SET IAR1.4 ; set MODE bit, select page operation mode MOV A, EEPROM_ADRES ; user defined address MOV EEA, A ; ~~~~ The data length can be up to 16 bytes (Start) ~~~~...

- Page 60 HT45F8550 BMS Flash MCU Writing a Data Page to the EEPROM - polling method MOV A, 040H ; setup memory pointer low byte MP1L MOV MP1L, A ; MP1 points to EEC register MOV A, 01H ; setup memory pointer high byte MP1H MOV MP1H, A SET IAR1.4 ; set MODE bit, select page operation mode MOV A, EEPROM_ADRES ; user defined address MOV EEA, A ; ~~~~ The data length can be up to 16 bytes (Start) ~~~~ CALL WRITE_BUF CALL WRITE_BUF JMP WRITE_START ; ~~~~ The data length can be up to 16 bytes (End) ~~~~ WRITE_BUF: MOV A, EEPROM_DATA ; user defined data...

-

Page 61: Oscillators

HT45F8550 BMS Flash MCU Oscillators Various oscillator options offer the user a wide range of functions according to their various application requirements. The flexible features of the oscillator functions ensure that the best optimisation can be achieved in terms of speed and power saving. Oscillator selections and operation are selected through a combination of configuration option and relevant control registers. -

Page 62: External Crystal/Ceramic Oscillator - Hxt

HT45F8550 BMS Flash MCU High Speed Oscillators HXTEN IDLE0 Prescaler HIRCEN HIRC SLEEP Low Speed Oscillators LXTEN CKS2~CKS0 IDLE2 LIRC SLEEP LIRC System Clock Configurations External Crystal/Ceramic Oscillator – HXT The External Crystal/Ceramic System Oscillator is one of the high frequency oscillator choices, which is selected via a software control bit, FHS. -

Page 63: Internal High Speed Internal Rc Oscillator - Hirc

HT45F8550 BMS Flash MCU Internal High Speed Internal RC Oscillator – HIRC The internal RC oscillator is one of the high frequency oscillator choices, which is selected via a software control bit, FHS. It is a fully integrated system oscillator requiring no external components. -

Page 64: Internal 32Khz Oscillator - Lirc

As Holtek has provided the device with both high and low speed clock sources and the means to switch between them dynamically, the user can optimise the operation of their microcontroller to achieve the best performance/power ratio. -

Page 65: System Operation Modes

HT45F8550 BMS Flash MCU High Speed Oscillators HXTEN IDLE0 Prescaler HIRCEN HIRC SLEEP Low Speed Oscillators LXTEN CKS2~CKS0 IDLE2 LIRC SLEEP LIRC PSC0 Time Base 0 Prescaler 0 CLKSEL0[1:0] PSC1 Prescaler 1 Time Base 1 CLKSEL1[1:0] Device Clock Configurations Note: When the system clock source f... -

Page 66: Control Registers

HT45F8550 BMS Flash MCU FAST Mode This is one of the main operating modes where the microcontroller has all of its functions operational and where the system clock is provided by one of the high speed oscillators. This mode operates allowing the microcontroller to operate normally with a clock source will come from one of the high speed oscillators, either the HXT or HIRC oscillator, selected by the FHS bit in the SCC register. - Page 67 HT45F8550 BMS Flash MCU • SCC Register Name CKS2 CKS1 CKS0 — FHIDEN FSIDEN — — Bit 7~5 CKS2~CKS0: System clock selection 000: f 001: f 010: f 011: f 100: f 101: f 110: f 111: f These three bits are used to select which clock is used as the system clock source. In...

- Page 68 HT45F8550 BMS Flash MCU Bit 1 HIRCF: HIRC oscillator stable flag 0: HIRC unstable 1: HIRC stable This bit is used to indicate whether the HIRC oscillator is stable or not. When the HIRCEN bit is set high to enable the HIRC oscillator or the HIRC frequency selection is changed by application program, the HIRCF bit will first be cleared to zero and then set high after the HIRC oscillator is stable.

-

Page 69: Operating Mode Switching

HT45F8550 BMS Flash MCU Operating Mode Switching The device can switch between operating modes dynamically allowing the user to select the best performance/power ratio for the present task in hand. In this way microcontroller operations that do not require high performance can be executed using slower clocks thus requiring less operating current and prolonging battery life in portable applications. - Page 70 HT45F8550 BMS Flash MCU FAST Mode CKS2~CKS0=111 SLOW Mode FHIDEN=0, FSIDEN=0 HALT instruction is executed SLEEP Mode FHIDEN=0, FSIDEN=1 HALT instruction is executed IDLE0 Mode FHIDEN=1, FSIDEN=1 HALT instruction is executed IDLE1 Mode FHIDEN=1, FSIDEN=0 HALT instruction is executed IDLE2 Mode...

- Page 71 HT45F8550 BMS Flash MCU Entering the SLEEP Mode There is only one way for the device to enter the SLEEP Mode and that is to execute the “HALT” instruction in the application program with both the FHIDEN and FSIDEN bits in the SCC register equal to “0”.

-

Page 72: Standby Current Considerations

HT45F8550 BMS Flash MCU Entering the IDLE2 Mode There is only one way for the device to enter the IDLE2 Mode and that is to execute the “HALT” instruction in the application program with the FHIDEN bit in the SCC register equal to “1” and the FSIDEN bit in the SCC register equal to “0”. -

Page 73: Programming Considerations

HT45F8550 BMS Flash MCU Each pin on Port A can be set using the PAWU register to permit a negative transition on the pin to wake up the system. When a Port A pin wake-up occurs, the program will resume execution at the instruction following the “HALT”... -

Page 74: Watchdog Timer Operation

HT45F8550 BMS Flash MCU When these bits are changed to any other values due to environmental noise the microcontroller will be reset; this reset operation will be activated after a delay time, , and the WRF bit in the RSTFC register will be set high. -

Page 75: Reset And Initialisation

HT45F8550 BMS Flash MCU Under normal program operation, a Watchdog Timer time-out will initialise a device reset and set the status bit TO. However, if the system is in the SLEEP or IDLE Mode, when a Watchdog Timer time-out occurs, the TO bit in the status register will be set and only the Program Counter and Stack Pointer will be reset. - Page 76 HT45F8550 BMS Flash MCU Power-on Reset RSTD SST Time-out Power-On Reset Timing Chart Internal Reset Control There is an internal reset control register, RSTC, which is used to provide a reset when the device operates abnormally due to the environmental noise interference. If the content of the RSTC register is set to any value other than 01010101B or 10101010B, it will reset the device after a delay time, .

- Page 77 HT45F8550 BMS Flash MCU Low Voltage Reset – LVR The microcontroller contains a low voltage reset circuit in order to monitor the supply voltage of the device and provides an MCU reset should the value fall below a certain predefined level. The LVR function can be enabled or disabled by the LVRC control register.

- Page 78 HT45F8550 BMS Flash MCU • RSTFC Register Name — — — — RSTF LVRF — — — — — — — — “x”: unknown Bit 7~4 Unimplemented, read as “0” RSTF: Reset control register software reset flag Bit 3 Refer to the Internal Reset Control section.

-

Page 79: Reset Initial Conditions

HT45F8550 BMS Flash MCU Reset Initial Conditions The different types of reset described affect the reset flags in different ways. These flags, known as PDF and TO are located in the status register and are controlled by various microcontroller operations, such as the SLEEP or IDLE Mode function or Watchdog Timer. The reset flag are shown... - Page 80 HT45F8550 BMS Flash MCU Register Reset WDT Time-out WDT Time-out LVR Reset Name (Power On) (Normal Operation) (IDLE/SLEEP) PAWU 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0...

- Page 81 HT45F8550 BMS Flash MCU Register Reset WDT Time-out WDT Time-out LVR Reset Name (Power On) (Normal Operation) (IDLE/SLEEP) - 1 1 1 1 1 1 1 - 1 1 1 1 1 1 1 - 1 1 1 1 1 1 1...

-

Page 82: Input/Output Ports

“-” stands for unimplemented Input/Output Ports Holtek microcontrollers offer considerable flexibility on their I/O ports. With the input or output designation of every pin fully under user program control, pull-high selections for all ports and wake-up selections on certain pins, the user is provided with an I/O structure to meet the needs of a wide range of application possibilities. -

Page 83: Port A Wake-Up

HT45F8550 BMS Flash MCU • PxPU Register Name PxPU7 PxPU6 PxPU5 PxPU4 PxPU3 PxPU2 PxPU1 PxPU0 PxPUn: I/O Port x Pin pull-high function control 0: Disable 1: Enable The PxPUn bit is used to control the pin pull-high function. Here the “x” can be A, B, C or D. -

Page 84: I/O Port Control Registers

HT45F8550 BMS Flash MCU I/O Port Control Registers Each I/O port has its own control register known as PAC~PDC, to control the input/output configuration. With this control register, each CMOS output or input can be reconfigured dynamically under software control. Each pin of the I/O ports is directly mapped to a bit in its associated port control register. -

Page 85: Pin-Shared Functions

HT45F8550 BMS Flash MCU Bit 5~4 SLEDC05~SLEDC04: PB3~PB0 Source Current Selection 00: Source current = Level 0 (Min.) 01: Source current = Level 1 10: Source current = Level 2 11: Source current = Level 3 (Max.) Bit 3~2 SLEDC03~SLEDC02: PA7~PA4 Source Current Selection 00: Source current = Level 0 (Min.) - Page 86 HT45F8550 BMS Flash MCU The most important point to note is to make sure that the desired pin-shared function is properly selected and also deselected. For most pin-shared functions, to select the desired pin-shared function, the pin-shared function should first be correctly selected using the corresponding pin-shared control register.

- Page 87 HT45F8550 BMS Flash MCU • PAS1 Register Name PAS17 PAS16 PAS15 PAS14 PAS13 PAS12 PAS11 PAS10 Bit 7~6 PAS17~PAS16: PA7 Pin-Shared Function Selection 00: PA7 01: PTP 10: Reserved 11: AN6 Bit 5~4 PAS15~PAS14: PA6 Pin-Shared Function Selection 00: PA6/CTCK...

- Page 88 HT45F8550 BMS Flash MCU • PBS1 Register Name — — PBS15 PBS14 PBS13 PBS12 PBS11 PBS10 — — — — Bit 7~6 Unimplemented, read as “0” Bit 5~4 PBS15~PBS14: PB6 Pin-Shared function selection 00: PB6 01: SCK/SCL 10: C+ 11: Reserved...

- Page 89 HT45F8550 BMS Flash MCU • PCS1 Register — Name — PCS15 PCS14 PCS13 PCS12 PCS11 PCS10 — — — — Bit 7~6 Unimplemented, read as “0” Bit 5~4 PCS15~PCS14: PC6 Pin-Shared Function Selection 00: PC6 01: PC6 10: SCS 11: Reserved...

-

Page 90: I/O Pin Structures

HT45F8550 BMS Flash MCU I/O Pin Structures The accompanying diagram illustrates the internal structure of the I/O logic function. As the exact logical construction of the I/O pin will differ from this drawing, it is supplied as a guide only to assist with the functional understanding of the I/O logic function. -

Page 91: Timer Modules - Tm

HT45F8550 BMS Flash MCU Timer Modules – TM One of the most fundamental functions in any microcontroller device is the ability to control and measure time. To implement time related functions the device includes a Timer Modules, abbreviated to the name TM. The TM is a multi-purpose timing unit and serves to provide operations such as Timer/Counter, Compare Match Output and Single Pulse Output as well as being the functional unit for the generation of PWM signals. -

Page 92: Tm Interrupts

HT45F8550 BMS Flash MCU TM Interrupts The Compact Type, Standard Type and Periodic Type TMs each have two internal interrupts, one for each of the internal comparator A or comparator P, which generate a TM interrupt when a compare match condition occurs. When a TM interrupt is generated it can be used to clear the counter and also to change the state of the TM output pin. -

Page 93: Programming Considerations

HT45F8550 BMS Flash MCU Programming Considerations The TM Counter Registers and the Compare CCRA and CCRP registers, all have a low and high byte structure. The high bytes can be directly accessed, but as the low bytes can only be accessed via an internal 8-bit buffer, reading or writing to these register pairs must be carried out in a specific way. -

Page 94: Compact Type Tm - Ctm

HT45F8550 BMS Flash MCU Compact Type TM – CTM Although the simplest form of the three TM types, the Compact TM type still contains three operating modes, which are Compare Match Output, Timer/Event Counter and PWM Output modes. The Compact TM can also be controlled with an external input pin and can drive one external output pin. -

Page 95: Compact Type Tm Register Description

HT45F8550 BMS Flash MCU Compact Type TM Register Description Overall operation of the Compact TM is controlled using a series of registers. A read only register pair exists to store the internal counter 16-bit value, while a read/write register pair exists to store the internal 16-bit CCRA value. - Page 96 HT45F8550 BMS Flash MCU the Compare Match Output Mode or the PWM Output Mode then the CTM output pin will be reset to its initial condition, as specified by the CTOC bit, when the CTON bit changes from low to high.

- Page 97 HT45F8550 BMS Flash MCU This is the output control bit for the CTM output pin. Its operation depends upon whether CTM is being used in the Compare Match Output Mode or in the PWM Output Mode. It has no effect if the CTM is in the Timer/Counter Mode. In the Compare Match Output Mode it determines the logic level of the CTM output pin before a compare match occurs.

-

Page 98: Compact Type Tm Operating Modes

HT45F8550 BMS Flash MCU • CTMAH Register Name Bit 7~0 D15~D8: CTM CCRA High Byte Register bit 7 ~ bit 0 CTM 16-bit CCRA bit 15 ~ bit 8 • CTMRP Register Name Bit 7~0 D7~D0: CTM CCRP 8-bit register, compared with the CTM Counter bit 15 ~ bit 8... - Page 99 HT45F8550 BMS Flash MCU the CTIO1 and CTIO0 bits in the CTMC1 register. The CTM output pin can be selected using the CTIO1 and CTIO0 bits to go high, to go low or to toggle from its present condition when a compare match occurs from Comparator A.

- Page 100 HT45F8550 BMS Flash MCU Counter Value CTCCLR = 1; CTM [1:0] = 00 CCRA = 0 CCRA > 0 Counter cleared by CCRA value Counter overflow 0xFFFF CCRA=0 Resume CCRA Pause Stop Counter Restart CCRP Time CTON CTPAU CTPOL No CTMAF flag...

- Page 101 HT45F8550 BMS Flash MCU Timer/Counter Mode To select this mode, bits CTM1 and CTM0 in the CTMC1 register should be set to “11” respectively. The Timer/Counter Mode operates in an identical way to the Compare Match Output Mode generating the same interrupt flags. The exception is that in the Timer/Counter Mode the CTM output pin is not used.

- Page 102 HT45F8550 BMS Flash MCU Counter Value CTDPX = 0; CTM [1:0] = 10 Counter cleared by CCRP Counter Reset when CTON returns high CCRP Counter Stop if Pause Resume CTON bit low CCRA Time CTON CTPAU CTPOL CCRA Int. Flag CTMAF CCRP Int.

- Page 103 HT45F8550 BMS Flash MCU Counter Value CTDPX = 1; CTM [1:0] = 10 Counter cleared by CCRA Counter Reset when CTON returns high CCRA Counter Stop if Pause Resume CTON bit low CCRP Time CTON CTPAU CTPOL CCRP Int. Flag CTMPF CCRA Int.

-

Page 104: Standard Type Tm - Stm

HT45F8550 BMS Flash MCU Standard Type TM – STM The Standard Type TM contains four operating modes, which are Compare Match Output, Timer/ Event Counter, Single Pulse Output and PWM Output modes. The Standard TM can also be controlled with one external input pin and can drive one external output pin. - Page 105 HT45F8550 BMS Flash MCU Register Name STMC0 STPAU STCK2 STCK1 STCK0 STON — — — STMC1 STM1 STM0 STIO1 STIO0 STOC STPOL STDPX STCCLR STMDL STMDH STMAL STMAH STMRP STRP7 STRP6 STRP5 STRP4 STRP3 STRP2 STRP1 STRP0 16-bit Standard TM Register List •...

- Page 106 HT45F8550 BMS Flash MCU • STMC1 Register Name STM1 STM0 STIO1 STIO0 STOC STPOL STDPX STCCLR Bit 7~6 STM1~STM0: STM operating mode selection 00: Compare Match Output Mode 01: Undefined 10: PWM Output Mode or Single Pulse Output Mode 11: Timer/Counter Mode These bits setup the required operating mode for the STM.

- Page 107 HT45F8550 BMS Flash MCU This is the output control bit for the STM output pin. Its operation depends upon whether STM is being used in the Compare Match Output Mode or in the PWM Output Mode/Single Pulse Output Mode. It has no effect if the STM is in the Timer/Counter Mode.

- Page 108 HT45F8550 BMS Flash MCU • STMAL Register Name Bit 7~0 D7~D0: STM CCRA Low Byte Register bit 7 ~ bit 0 STM 16-bit CCRA bit 7 ~ bit 0 • STMAH Register Name Bit 7~0 D15~D8: STM CCRA High Byte Register bit 7 ~ bit 0 STM 16-bit CCRA bit 15 ~ bit 8 •...

-

Page 109: Standard Type Tm Operation Modes

HT45F8550 BMS Flash MCU Standard Type TM Operation Modes The Standard Type TM can operate in one of four operating modes, Compare Match Output Mode, PWM Output Mode, Single Pulse Output Mode or Timer/Counter Mode. The operating mode is selected using the STM1 and STM0 bits in the STMC1 register. - Page 110 HT45F8550 BMS Flash MCU Counter overflow Counter Value STCCLR = 0; STM [1:0] = 00 CCRP > 0 CCRP=0 Counter cleared by CCRP value 0xFFFF CCRP > 0 Counter Resume Restart CCRP Pause Stop CCRA Time STON STPAU STPOL CCRP Int.

- Page 111 HT45F8550 BMS Flash MCU Counter Value STCCLR = 1; STM [1:0] = 00 CCRA = 0 CCRA > 0 Counter cleared by CCRA value Counter overflow 0xFFFF CCRA=0 Resume CCRA Pause Stop Counter Restart CCRP Time STON STPAU STPOL No STMAF flag...

- Page 112 HT45F8550 BMS Flash MCU Timer/Counter Mode To select this mode, bits STM1 and STM0 in the STMC1 register should be set to “11” respectively. The Timer/Counter Mode operates in an identical way to the Compare Match Output Mode generating the same interrupt flags. The exception is that in the Timer/Counter Mode the STM output pin is not used.

- Page 113 HT45F8550 BMS Flash MCU Counter Value STDPX = 0; STM [1:0] = 10 Counter cleared by CCRP Counter Reset when STON returns high CCRP Counter Stop if Pause Resume STON bit low CCRA Time STON STPAU STPOL CCRA Int. Flag STMAF CCRP Int.

- Page 114 HT45F8550 BMS Flash MCU Counter Value STDPX = 1; STM [1:0] = 10 Counter cleared by CCRA Counter Reset when STON returns high CCRA Counter Stop if Pause Resume STON bit low CCRP Time STON STPAU STPOL CCRP Int. Flag STMPF CCRA Int.

- Page 115 HT45F8550 BMS Flash MCU Single Pulse Output Mode To select this mode, bits STM1 and STM0 in the STMC1 register should be set to “10” respectively and also the STIO1 and STIO0 bits should be set to “11” respectively. The Single Pulse Output Mode, as the name suggests, will generate a single shot pulse on the STM output pin.

- Page 116 HT45F8550 BMS Flash MCU Counter Value STM [1:0] = 10 ; STIO [1:0] = 11 Counter stopped by CCRA Counter Reset when STON returns high CCRA Counter Stops by Resume Pause software CCRP Time STON Auto. set by STCK pin...

-

Page 117: Periodic Type Tm - Ptm

HT45F8550 BMS Flash MCU Periodic Type TM – PTM The Periodic Type TM contains four operating modes, which are Compare Match Output, Timer/Event Counter, Single Pulse Output and PWM Output modes. The Periodic TM can also be controlled with one external input pin and can drive one external output pin. - Page 118 HT45F8550 BMS Flash MCU Register Name PTMC0 PTPAU PTCK2 PTCK1 PTCK0 PTON — — — PTMC1 PTM1 PTM0 PTIO1 PTIO0 PTOC PTPOL PTCCLR PTMDL PTMDH — — — — — — PTMAL PTMAH — — — — — — PTMRPL...

- Page 119 HT45F8550 BMS Flash MCU • PTMC1 Register Name PTM1 PTM0 PTIO1 PTIO0 PTOC PTPOL PTCCLR Bit 7~6 PTM1~PTM0: PTM operating mode selection 00: Compare Match Output Mode 01: Undefined 10: PWM Output Mode or Single Pulse Output Mode 11: Timer/Counter Mode These bits setup the required operating mode for the PTM.

- Page 120 HT45F8550 BMS Flash MCU This is the output control bit for the PTM output pin. Its operation depends upon whether PTM is being used in the Compare Match Output Mode or in the PWM Output Mode/Single Pulse Output Mode. It has no effect if the PTM is in the Timer/Counter Mode.

-

Page 121: Periodic Type Tm Operation Modes

HT45F8550 BMS Flash MCU • PTMAH Register Name — — — — — — — — — — — — — — — — — — Bit 7~2 Unimplemented, read as “0” Bit 1~0 D9~D8: PTM CCRA High Byte Register bit 1 ~ bit 0 PTM 10-bit CCRA bit 9 ~ bit 8 •... - Page 122 HT45F8550 BMS Flash MCU flag, generated from a compare match occurs from Comparator P, will have no effect on the PTM output pin. The way in which the PTM output pin changes state are determined by the condition of the PTIO1 and PTIO0 bits in the PTMC1 register. The PTM output pin can be selected using the PTIO1 and PTIO0 bits to go high, to go low or to toggle from its present condition when a compare match occurs from Comparator A.

- Page 123 HT45F8550 BMS Flash MCU Counter Value PTCCLR = 1; PTM [1:0] = 00 CCRA = 0 CCRA > 0 Counter cleared by CCRA value Counter overflow 0x3FF CCRA=0 Resume CCRA Pause Stop Counter Restart CCRP Time PTON PTPAU PTPOL No PTMAF flag...

- Page 124 HT45F8550 BMS Flash MCU Timer/Counter Mode To select this mode, bits PTM1 and PTM0 in the PTMC1 register should be set to “11” respectively. The Timer/Counter Mode operates in an identical way to the Compare Match Output Mode generating the same interrupt flags. The exception is that in the Timer/Counter Mode the PTM output pin is not used.

- Page 125 HT45F8550 BMS Flash MCU Counter Value PTM [1:0] = 10 Counter cleared by CCRP Counter Reset when PTON returns high CCRP Counter Stop if Pause Resume PTON bit low CCRA Time PTON PTPAU PTPOL CCRA Int. Flag PTMAF CCRP Int.

- Page 126 HT45F8550 BMS Flash MCU Single Pulse Output Mode To select this mode, bits PTM1 and PTM0 in the PTMC1 register should be set to “10” respectively and also the PTIO1 and PTIO0 bits should be set to “11” respectively. The Single Pulse Output Mode, as the name suggests, will generate a single shot pulse on the PTM output pin.

- Page 127 HT45F8550 BMS Flash MCU Counter Value PTM [1:0] = 10; PTIO [1:0] = 11 Counter stopped by CCRA Counter Reset when PTON returns high CCRA Counter Stops by Resume Pause software CCRP Time PTON Auto. set by PTCK pin Software...

-

Page 128: Analog To Digital Converter

HT45F8550 BMS Flash MCU Analog to Digital Converter The need to interface to real world analog signals is a common requirement for many electronic systems. However, to properly process these signals by a microcontroller, they must first be converted into digital signals by A/D converters. By integrating the A/D conversion electronic circuitry into the microcontroller, the need for external components is reduced significantly with the corresponding follow-on benefits of lower costs and reduced component space requirements. -

Page 129: A/D Converter Register Description

HT45F8550 BMS Flash MCU A/D Converter Register Description Overall operation of the A/D converter is controlled using a series of registers. A read only register pair exists to store the A/D converter data 12-bit value. Three registers, SADC0, SADC1 and SADC2, are the control registers which setup the operating conditions and control function of the A/D converter. - Page 130 HT45F8550 BMS Flash MCU The relevant pin-shared function selection bits determine which pins on I/O ports are used as analog inputs for the A/D converter input and which pins are not to be used as the A/D converter input. When the pin is selected to be an A/D converter input, its original function whether it is an I/O or other pin-shared function will be removed.

- Page 131 HT45F8550 BMS Flash MCU • SADC1 Register Name SAINS3 SAINS2 SAINS1 SAINS0 — SACKS2 SACKS1 SACKS0 — — Bit 7~4 SAINS3~SAINS0: A/D converter input signal selection 0000: External signal – External analog channel input, ANn 0001: Internal signal – Internal A/D converter power supply voltage AV 0010: Internal signal –...

-

Page 132: A/D Converter Reference Voltage

HT45F8550 BMS Flash MCU Bit 3~2 SAVRS1~SAVRS0: A/D converter reference voltage selection 00: Internal A/D converter power, AV 01: External VREF pin 1x: Internal PGA output voltage, V These bits are used to select the A/D converter reference voltage source. When the internal reference voltage source is selected, the reference voltage derived from the external VREF pin will automatically be switched off. -

Page 133: A/D Converter Operation

HT45F8550 BMS Flash MCU change their function between A/D inputs and other functions. All pull-high resistors, which are setup through register programming, will be automatically disconnected if the pins are setup as A/D converter inputs. Note that it is not necessary to first setup the A/D pin as an input in the port control register to enable the A/D converter input as when the relevant A/D converter input function selection bits enable an A/D converter input, the status of the port control register will be overridden. -

Page 134: A/D Conversion Rate And Timing Diagram

HT45F8550 BMS Flash MCU For example, if the system clock operates at a frequency of 8MHz, the SACKS2~SACKS0 bits should not be set to “000”, “001” or “111”. Doing so will give A/D conversion clock periods that are less than the minimum A/D conversion clock period or greater than the maximum A/D conversion clock period which may result in inaccurate A/D conversion values. -

Page 135: Summary Of A/D Conversion Steps

HT45F8550 BMS Flash MCU ON2ST ADCEN A/D sampling time A/D sampling time START Start of A/D conversion Start of A/D conversion Start of A/D conversion ADBZ End of A/D End of A/D conversion conversion SACS[3:0] 0011B 0010B 0000B 0001B (SAINS[3:0]=0000B) -

Page 136: Programming Considerations

HT45F8550 BMS Flash MCU • Step 9 The A/D conversion procedure can now be initialised by setting the START bit from low to high and then low again. • Step 10 If A/D conversion is in progress, the ADBZ flag will be set high. After the A/D conversion process is completed, the ADBZ flag will go low and then output data can be read from the SADOH and SADOL registers. -

Page 137: A/D Converter Programming Examples

HT45F8550 BMS Flash MCU A/D Converter Programming Examples The following two programming examples illustrate how to setup and implement an A/D conversion. In the first example, the method of polling the ADBZ bit in the SADC0 register is used to detect when the conversion cycle is complete, whereas in the second example, the A/D converter interrupt is used to determine when the conversion is complete. -

Page 138: Comparator

HT45F8550 BMS Flash MCU mov a,SADOL ; read low byte conversion result value mov SADOL_buffer,a ; save result to user defined register mov a,SADOH ; read high byte conversion result value mov SADOH_buffer,a ; save result to user defined register EXIT_INT_ISR: mov a,status_stack mov STATUS,a ; restore STATUS from user defined memory mov a,acc_stack ; restore ACC from user defined memory reti Comparator An analog comparator is contained within the device. The comparator function offers flexibility via their register controlled features such as power-down, polarity select, hysteresis etc. -

Page 139: Comparator Interrupt

HT45F8550 BMS Flash MCU • CMPC Register Name — CMPEN CMPPOL CMPO — — — CMPHYEN — — — — — — — — Bit 7 Unimplemented, read as “0” Bit 6 CMPEN: Comparator Enable Control 0: Disable 1: Enable This is the Comparator on/off control bit. -

Page 140: Serial Interface Module - Sim

HT45F8550 BMS Flash MCU Serial Interface Module – SIM The device contains a Serial Interface Module, which includes both the four-line SPI interface or two-line I C interface types, to allow an easy method of communication with external peripheral hardware. Having relatively simple communication protocols, these serial interface types allow the... - Page 141 HT45F8550 BMS Flash MCU • Transmission complete flag • Rising or falling active clock edge The status of the SPI interface pins is determined by a number of factors such as whether the device is in the master or slave mode and upon the condition of certain control bits such as CSEN and SIMEN.

- Page 142 HT45F8550 BMS Flash MCU SPI Control Registers There are also two control registers for the SPI interface, SIMC0 and SIMC2. Note that the SIMC2 register also has the name SIMA which is used by the I C function. The SIMC0 register is used to control the enable/disable function and to set the data transmission clock frequency.

- Page 143 HT45F8550 BMS Flash MCU • SIMC2 Register Name CKPOLB CKEG CSEN WCOL Bit 7~6 D7~D6: Undefined bits These bits can be read or written by application program. Bit 5 CKPOLB: SPI clock line base condition selection 0: The SCK line will be high when the clock is inactive...

- Page 144 HT45F8550 BMS Flash MCU SPI Communication After the SPI interface is enabled by setting the SIMEN bit high, then in the Master Mode, when data is written to the SIMD register, transmission/reception will begin simultaneously. When the data transfer is complete, the TRF flag will be set automatically, but must be cleared using the application program.

- Page 145 HT45F8550 BMS Flash MCU SCK (CKPOLB=1) SCK (CKPOLB=0) D7/D0 D6/D1 D5/D2 D4/D3 D3/D4 D2/D5 D1/D6 D0/D7 SDI Data Capture Write to SIMD (SDO changes as soon as writing occurs; SDO is floating if SCS=1) Note: For SPI slave mode, if SIMEN=1 and CSEN=0, SPI is always enabled and ignores the SCS level.

- Page 146 HT45F8550 BMS Flash MCU SPI Bus Enable/Disable To enable the SPI bus, set CSEN=1 and SCS=0, then wait for data to be written into the SIMD (TXRX buffer) register. For the Master Mode, after data has been written to the SIMD (TXRX buffer) register, then transmission or reception will start automatically.

-

Page 147: I 2 C Interface

HT45F8550 BMS Flash MCU Slave Mode • Step 1 Select the SPI Slave mode using the SIM2~SIM0 bits in the SIMC0 control register • Step 2 Setup the CSEN bit and setup the MLS bit to choose if the data is MSB or LSB first, this setting must be the same with the Master devices. - Page 148 HT45F8550 BMS Flash MCU C interface Operation The I C serial interface is a two line interface, a serial data line, SDA, and serial clock line, SCL. As many devices may be connected together on the same bus, their outputs are both open drain types.

- Page 149 HT45F8550 BMS Flash MCU The SIMDEB1 and SIMDEB0 bits determine the debounce time of the I C interface. This uses the system clock to in effect add a debounce time to the external clock to reduce the possibility of glitches on the clock line causing erroneous operation. The debounce time, if selected, can be chosen to be either 2 or 4 system clocks.

- Page 150 HT45F8550 BMS Flash MCU C Address Register The SIMA register is also used by the SPI interface but has the name SIMC2. The SIMA register is the location where the 7-bit slave address of the slave device is stored. Bits 7~1 of the SIMA register define the device slave address.

- Page 151 HT45F8550 BMS Flash MCU Bit 1 SIMEN: SIM Enable Control 0: Disable 1: Enable The bit is the overall on/off control for the SIM interface. When the SIMEN bit is cleared to zero to disable the SIM interface, the SDI, SDO, SCK and SCS, or SDA...

- Page 152 HT45F8550 BMS Flash MCU Bit 2 SRW: I C slave read/write flag 0: Slave device should be in receive mode 1: Slave device should be in transmit mode The SRW flag is the I C Slave Read/Write flag. This flag determines whether the master device wishes to transmit or receive data from the I C bus.

- Page 153 HT45F8550 BMS Flash MCU Start Set SIM[2:0]=110 Set SIMEN Write Slave Address to SIMA C Bus Interrupt=? CLR SIME SET SIME Poll SIMF to decide when Wait for Interrupt to go to I C Bus ISR Goto Main Program Goto Main Program...

- Page 154 HT45F8550 BMS Flash MCU C Bus Slave Address Acknowledge Signal After the master has transmitted a calling address, any slave device on the I C bus, whose own internal address matches the calling address, must generate an acknowledge signal. The acknowledge signal will inform the master that a slave device has accepted its calling address.

- Page 155 HT45F8550 BMS Flash MCU Start SIMTOF=1? SET SIMTOEN HAAS=1? CLR SIMTOF HTX=1? SRW=1? RETI Read from SIMD to CLR HTX SET HTX release SCL Line CLR TXAK RETI Dummy read from SIMD Write data to SIMD to to release SCL Line...

- Page 156 HT45F8550 BMS Flash MCU When an I C time-out counter overflow occurs, the counter will stop and the SIMTOEN bit will be cleared to zero and the SIMTOF bit will be set high to indicate that a time-out condition has occurred.

-

Page 157: Uart Interface

HT45F8550 BMS Flash MCU UART Interface The device contains an integrated full-duplex asynchronous serial communications UART interface that enables communication with external devices that contain a serial interface. The UART function has many features and can transmit and receive data serially by transferring a frame of data with eight or nine data bits per transmission as well as being able to detect errors when the data is overwritten or incorrectly framed. -

Page 158: Uart Data Transfer Scheme

HT45F8550 BMS Flash MCU UART Data Transfer Scheme The above block diagram shows the overall data transfer structure arrangement for the UART. The actual data to be transmitted from the MCU is first transferred to the TXR_RXR register by the application program. - Page 159 HT45F8550 BMS Flash MCU Bit 6 NF: Noise flag 0: No noise is detected 1: Noise is detected The NF flag is the noise flag. When this read only flag is “0”, it indicates no noise condition. When the flag is “1”, it indicates that the UART has detected noise on the receiver input.

- Page 160 HT45F8550 BMS Flash MCU Bit 0 TXIF: Transmit TXR_RXR data register status 0: Character is not transferred to the transmit shift register 1: Character has transferred to the transmit shift register (TXR_RXR data register is empty) The TXIF flag is the transmit data register empty flag. When this read only flag is “0”, it indicates that the character is not transferred to the transmitter shift register.

- Page 161 HT45F8550 BMS Flash MCU Bit 3 STOPS: Number of Stop bits selection 0: One stop bit format is used 1: Two stop bits format is used This bit determines if one or two stop bits are to be used. When this bit is equal to “1”, two stop bits are used.

- Page 162 HT45F8550 BMS Flash MCU Bit 5 BRGH: Baud Rate speed selection 0: Low speed baud rate 1: High speed baud rate The bit named BRGH selects the high or low speed mode of the Baud Rate Generator. This bit, together with the value placed in the baud rate register BRG, controls the Baud Rate of the UART.

-

Page 163: Baud Rate Generator

HT45F8550 BMS Flash MCU • TXR_RXR Register The TXR_RXR register is the data register which is used to store the data to be transmitted on the TX pin or being received from the RX pin. Name TXRX7 TXRX6 TXRX5 TXRX4... -

Page 164: Uart Setup And Control

HT45F8550 BMS Flash MCU UART Setup and Control For data transfer, the UART function utilizes a non-return-to-zero, more commonly known as NRZ, format. This is composed of one start bit, eight or nine data bits, and one or two stop bits. Parity is supported by the UART hardware, and can be setup to be even, odd or no parity. -

Page 165: Uart Transmitter

HT45F8550 BMS Flash MCU The following diagram shows the transmit and receive waveforms for both 8-bit and 9-bit data formats. Parity Bit Next Start Start Stop Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6... -

Page 166: Uart Receiver

HT45F8550 BMS Flash MCU The read-only TXIF flag is set by the UART hardware and if set indicates that the TXR_RXR register is empty and that other data can now be written into the TXR_RXR register without overwriting the previous data. If the TEIE bit is set then the TXIF flag will generate an interrupt. -

Page 167: Managing Receiver Errors

HT45F8550 BMS Flash MCU At this point the receiver will be enabled which will begin to look for a start bit. When a character is received the following sequence of events will occur: • The RXIF bit in the USR register will be set when the TXR_RXR register has data available. -

Page 168: Uart Interrupt Structure

HT45F8550 BMS Flash MCU Overrun Error – OERR The TXR_RXR register is composed of a two byte deep FIFO data buffer, where two bytes can be held in the FIFO register, while a third byte can continue to be received. Before this third byte has been entirely shifted in, the data should be read from the TXR_RXR register. - Page 169 HT45F8550 BMS Flash MCU two receiver interrupt conditions have a shared enable control bit. These enable bits can be used to mask out individual UART interrupt sources. The address detect condition, which is also a UART interrupt source, does not have an associated flag, but will generate a UART interrupt when an address detect condition occurs if its function is enabled by setting the ADDEN bit in the UCR2 register.

-

Page 170: Uart Power Down And Wake-Up

HT45F8550 BMS Flash MCU 9th bit if BNO=1 UART Interrupt ADDEN 8th bit if BNO=0 Generated √ √ × √ ADDEN Bit Function UART Power Down and Wake-up When the UART clock, f , is switched off, the UART will cease to function. If the MCU switches... -

Page 171: Low Voltage Detector - Lvd

HT45F8550 BMS Flash MCU Low Voltage Detector – LVD The device has a Low Voltage Detector function, also known as LVD. This enables the device to monitor the power supply voltage, V , and provide a warning signal should it fall below a certain level. -

Page 172: Interrupts

HT45F8550 BMS Flash MCU LVDEN LVDO LVDS LVDINT LVD Operation The Low Voltage Detector also has its own interrupt which is contained within one of the Multi-function interrupts, providing an alternative means of low voltage detection, in addition to polling the LVDO bit. - Page 173 HT45F8550 BMS Flash MCU Function Enable Bit Request Flag Notes CTMPE CTMPF — CTMAE CTMAF — STMPE STMPF — STMAE STMAF — PTMPE PTMPF — PTMAE PTMAF — Interrupt Register Bit Naming Conventions Register Name INTEG — — — —...

- Page 174 HT45F8550 BMS Flash MCU Bit 4 INT0F: INT0 interrupt request flag 0: No request 1: Interrupt request Bit 3 MF0E: Multi-function 0 interrupt control 0: Disable 1: Enable Bit 2 CPE: Comparator interrupt control 0: Disable 1: Enable Bit 1...

- Page 175 HT45F8550 BMS Flash MCU • INTC2 Register Name UARTF SIMF INT1F TB1F UARTE SIME INT1E TB1E Bit 7 UARTF: UART interrupt request flag 0: No request 1: Interrupt request Bit 6 SIMF: SIM interrupt request flag 0: No request 1: Interrupt request...

- Page 176 HT45F8550 BMS Flash MCU • MFI1 Register Name CTMAF CTMPF PTMAF PTMPF CTMAE CTMPE PTMAE PTMPE Bit 7 CTMAF: CTM Comparator A match interrupt request flag 0: No request 1: Interrupt request Bit 6 CTMPF: CTM Comparator P match interrupt request flag...

-

Page 177: Interrupt Operation

HT45F8550 BMS Flash MCU Interrupt Operation When the conditions for an interrupt event occur, such as a TM Comparator P or Comparator A match or A/D conversion completion etc., the relevant interrupt request flag will be set. Whether the request flag actually generates a program jump to the relevant interrupt vector is determined by the condition of the interrupt enable bit. -

Page 178: External Interrupt

HT45F8550 BMS Flash MCU Legend EMI auto disabled in ISR Request Flag, no auto reset in ISR Request Master Priority Interrupt Name Enable Bits Vector Flags Enable Request Flag, auto reset in ISR High INT0 Pin INT0F INT0E Enable Bits... -

Page 179: Comparator Interrupt

HT45F8550 BMS Flash MCU Comparator Interrupt The comparator interrupt is controlled by the internal comparator. A comparator interrupt request will take place when the comparator interrupt request flag, CPF, is set, a situation that will occur when the comparator output bit changes state. To allow the program to branch to its respective interrupt vector address, the global interrupt enable bit, EMI, and comparator interrupt enable bit, CPE, must first be set. - Page 180 HT45F8550 BMS Flash MCU The purpose of the Time Base Interrupt is to provide an interrupt signal at fixed time periods. Their clock sources f or f , originate from the internal clock source f /4 or f and then...

-

Page 181: Tm Interrupts

HT45F8550 BMS Flash MCU Bit 2~0 TB02~TB00: Time Base 0 time-out period selection 000: 2 PSC0 001: 2 PSC0 010: 2 PSC0 011: 2 PSC0 100: 2 PSC0 101: 2 PSC0 110: 2 PSC0 111: 2 PSC0 • TB1C Register... -

Page 182: Uart Transfer Interrupt

HT45F8550 BMS Flash MCU UART Transfer Interrupt The UART Transfer Interrupt is controlled by several UART transfer conditions. When one of these conditions occurs, an interrupt pulse will be generated to get the attention of the microcontroller. These conditions are a transmitter data register empty, transmitter idle, receiver data available, receiver overrun, address detect and an RX pin wake-up. -

Page 183: Programming Considerations

HT45F8550 BMS Flash MCU Programming Considerations By disabling the relevant interrupt enable bits, a requested interrupt can be prevented from being serviced, however, once an interrupt request flag is set, it will remain in this condition in the interrupt register until the corresponding interrupt is serviced or until the request flag is cleared by the application program. -

Page 184: Accumulative Cell Voltage Monitor

HT45F8550 BMS Flash MCU Accumulative Cell Voltage Monitor The Accumulative Cell Voltage Monitor is designed to monitor an accumulative voltage from 1 to N and outputs the divide-by-N voltage to the analog multiplexer. Each divided accumulative cell voltage from pin VBATn can be observed sequentially and measured by using the internal A/D converter after simple software settings or external pin connections. -

Page 185: Vin, Vreg, Vout Capacitors

HT45F8550 BMS Flash MCU × 1/1 BAT1 × 1/2 BAT2 × 1/3 BAT3 × 1/4 BAT4 × 1/5 BAT5 × 1/6 BAT6 × 1/7 BAT7 × 1/8 BAT8 Power on states Accumulative Cell Voltage Monitor Truth Table VBAT8 ÷8 BAT8 VBAT7 ÷7... -

Page 186: Vin And Vbatn Spike Suppression Resistors

HT45F8550 BMS Flash MCU VIN and VBATn Spike Suppression Resistors The appropriate VIN and VBATn spike suppression resistors corresponded to R1 and Rn lower the voltage spike and inrush current applied on any I/O pins, which can improve the stability of VREG that provides the power source to the MCUs. - Page 187 HT45F8550 BMS Flash MCU ≥10ms SCAN SCAN SCAN SCAN PD[3:1] BAT2 BAT6 BAT2 BAT8 BAT4 4.2V BAT5 BAT1 BAT1 BAT7 BAT3 VOUT [S8:S1] WAIT WAIT ≥5ms WAIT WAIT ADC Enable 8S Battery Monitoring Timing PD[3:1] BAT2 BAT2 4.2V BAT4 BAT1...

-

Page 188: Voltage Spike Suppression Method

HT45F8550 BMS Flash MCU Voltage Spike Suppression Method Loading Discharge Current Discharge Current Conducting wire Conducting wire HT45F8550 VBAT8 VBAT7 Simplified Typical BMS System Discharge Path Diagram Most battery-management systems would monitor charge and discharge current to prevent over- current damage. Due to the parasitic inductance on conducting wires and PCB layout connections, a large voltage spike may occur while the MCU-controlled MOS rapidly shuts down the charge or discharge current, and this spike may damage MCU VBATn or VIN pins. - Page 189 HT45F8550 BMS Flash MCU effect of rising ambient temperature on the maximum recommended power dissipation. 1.18 28SSOP Ambient Temperature ( 48LQFP-EP Ambient Temperature ( Rev. 1.70 January 31, 2024...

-

Page 190: Application Circuits

PA3/SDI/SDA/CX PB6/SCK/SCL/C+ PA7/PTP/AN6 HT45F8550 28SSOP Note: 1. If less than 8 serial batteries are used, connect the unused VBATn to the highest voltage potential. Do not leave any VBATn pin floating to prevent damage to the device. 2. The bold lines indicate that these connections need to be as short as possible. -

Page 191: Battery Monitoring Typical Application Circuit

PA3/SDI/SDA/CX PB6/SCK/SCL/C+ PA7/PTP/AN6 HT45F8550 28SSOP Note: 1. If less than 8 serial batteries are used, connect the unused VBATn to the highest voltage potential. Do not leave any VBATn pin floating to prevent damage to the device. 2. The bold lines indicate that these connections need to be as short as possible. -

Page 192: 8S Battery Monitoring Typical Application Circuit

PA3/SDI/SDA/CX PB6/SCK/SCL/C+ PA7/PTP/AN6 HT45F8550 48LQFP-EP Note: 1. If less than 8 serial batteries are used, connect the unused VBATn to the highest voltage potential. Do not leave any VBATn pin floating to prevent damage to the device. 2. The bold lines indicate that these connections need to be as short as possible. -

Page 193: Instruction Set

In the case of Holtek microcontroller, a comprehensive and flexible set of over 60 instructions is provided to enable programmers to implement their application with the minimum of programming overheads. -

Page 194: Logical And Rotate Operation

The standard logical operations such as AND, OR, XOR and CPL all have their own instruction within the Holtek microcontroller instruction set. As with the case of most instructions involving data manipulation, data must pass through the Accumulator which may involve additional programming steps. -

Page 195: Instruction Set Summary

HT45F8550 BMS Flash MCU Instruction Set Summary The instructions related to the data memory access in the following table can be used when the desired data memory is located in Data Memory sector 0. Table Conventions x: Bits immediate data... - Page 196 HT45F8550 BMS Flash MCU Mnemonic Description Cycles Flag Affected Data Move MOV A,[m] Move Data Memory to ACC None MOV [m],A Move ACC to Data Memory Note None MOV A,x Move immediate data to ACC None Bit Operation CLR [m].i...

-

Page 197: Extended Instruction Set

HT45F8550 BMS Flash MCU Extended Instruction Set The extended instructions are used to support the full range address access for the data memory. When the accessed data memory is located in any data memory sector except sector 0, the extended instruction can be used to directly access the data memory instead of using the indirect addressing access. - Page 198 HT45F8550 BMS Flash MCU Mnemonic Description Cycles Flag Affected Branch LSZ [m] Skip if Data Memory is zero Note None LSZA [m] Skip if Data Memory is zero with data movement to ACC Note None LSNZ [m] Skip if Data Memory is not zero...

-

Page 199: Instruction Definition

HT45F8550 BMS Flash MCU Instruction Definition ADC A,[m] Add Data Memory to ACC with Carry Description The contents of the specified Data Memory, Accumulator and the carry flag are added. The result is stored in the Accumulator. Operation ACC ← ACC + [m] + C... - Page 200 HT45F8550 BMS Flash MCU ANDM A,[m] Logical AND ACC to Data Memory Description Data in the specified Data Memory and the Accumulator perform a bitwise logical AND operation. The result is stored in the Data Memory. Operation [m] ← ACC “AND” [m]...

- Page 201 HT45F8550 BMS Flash MCU DAA [m] Decimal-Adjust ACC for addition with result in Data Memory Description Convert the contents of the Accumulator value to a BCD (Binary Coded Decimal) value resulting from the previous addition of two BCD variables. If the low nibble is greater than 9 or if AC flag is set, then a value of 6 will be added to the low nibble.

- Page 202 HT45F8550 BMS Flash MCU JMP addr Jump unconditionally Description The contents of the Program Counter are replaced with the specified address. Program execution then continues from this new address. As this requires the insertion of a dummy instruction while the new address is loaded, it is a two cycle instruction.

- Page 203 HT45F8550 BMS Flash MCU Return from subroutine Description The Program Counter is restored from the stack. Program execution continues at the restored address. Operation Program Counter ← Stack Affected flag(s) None RET A,x Return from subroutine and load immediate data to ACC...

- Page 204 HT45F8550 BMS Flash MCU RLCA [m] Rotate Data Memory left through Carry with result in ACC Description Data in the specified Data Memory and the carry flag are rotated left by 1 bit. Bit 7 replaces the Carry bit and the original carry flag is rotated into the bit 0. The rotated result is stored in the Accumulator and the contents of the Data Memory remain unchanged.

- Page 205 HT45F8550 BMS Flash MCU SBC A, x Subtract immediate data from ACC with Carry Description The immediate data and the complement of the carry flag are subtracted from the Accumulator. The result is stored in the Accumulator. Note that if the result of subtraction is negative, the C flag will be cleared to 0, otherwise if the result is positive or zero, the C flag will be set to 1.

- Page 206 HT45F8550 BMS Flash MCU SIZ [m] Skip if increment Data Memory is 0 Description The contents of the specified Data Memory are first incremented by 1. If the result is 0, the following instruction is skipped. As this requires the insertion of a dummy instruction while the next instruction is fetched, it is a two cycle instruction.

- Page 207 HT45F8550 BMS Flash MCU SUB A,x Subtract immediate data from ACC Description The immediate data specified by the code is subtracted from the contents of the Accumulator. The result is stored in the Accumulator. Note that if the result of subtraction is negative, the C flag will be cleared to 0, otherwise if the result is positive or zero, the C flag will be set to 1.

- Page 208 HT45F8550 BMS Flash MCU TABRD [m] Read table (specific page) to TBLH and Data Memory Description The low byte of the program code (specific page) addressed by the table pointer (TBLP and TBHP) is moved to the specified Data Memory and the high byte moved to TBLH.

-

Page 209: Extended Instruction Definition

HT45F8550 BMS Flash MCU Extended Instruction Definition The extended instructions are used to directly access the data stored in any data memory sections. LADC A,[m] Add Data Memory to ACC with Carry Description The contents of the specified Data Memory, Accumulator and the carry flag are added. - Page 210 HT45F8550 BMS Flash MCU LCLR [m] Clear Data Memory Description Each bit of the specified Data Memory is cleared to 0. Operation [m] ← 00H Affected flag(s) None LCLR [m].i Clear bit of Data Memory Description Bit i of the specified Data Memory is cleared to 0.

- Page 211 HT45F8550 BMS Flash MCU LDECA [m] Decrement Data Memory with result in ACC Description Data in the specified Data Memory is decremented by 1. The result is stored in the Accumulator. The contents of the Data Memory remain unchanged. Operation ACC ←...

- Page 212 HT45F8550 BMS Flash MCU LRL [m] Rotate Data Memory left Description The contents of the specified Data Memory are rotated left by 1 bit with bit 7 rotated into bit 0. Operation [m].(i+1) ← [m].i; (i=0~6) [m].0 ← [m].7 Affected flag(s)

- Page 213 HT45F8550 BMS Flash MCU LRRA [m] Rotate Data Memory right with result in ACC Description Data in the specified Data Memory is rotated right by 1 bit with bit 0 rotated into bit 7. The rotated result is stored in the Accumulator and the contents of the Data Memory remain unchanged.

- Page 214 HT45F8550 BMS Flash MCU LSDZ [m] Skip if decrement Data Memory is 0 Description The contents of the specified Data Memory are first decremented by 1. If the result is 0 the following instruction is skipped. As this requires the insertion of a dummy instruction while the next instruction is fetched, it is a three cycle instruction.

- Page 215 HT45F8550 BMS Flash MCU LSIZA [m] Skip if increment Data Memory is zero with result in ACC Description The contents of the specified Data Memory are first incremented by 1. If the result is 0, the following instruction is skipped. The result is stored in the Accumulator but the specified Data Memory contents remain unchanged.

- Page 216 HT45F8550 BMS Flash MCU LSWAP [m] Swap nibbles of Data Memory Description The low-order and high-order nibbles of the specified Data Memory are interchanged. Operation [m].3~[m].0 ↔ [m].7~[m].4 Affected flag(s) None LSWAPA [m] Swap nibbles of Data Memory with result in ACC Description The low-order and high-order nibbles of the specified Data Memory are interchanged.

- Page 217 HT45F8550 BMS Flash MCU LTABRDL [m] Read table (last page) to TBLH and Data Memory Description The low byte of the program code (last page) addressed by the table pointer (TBLP) is moved to the specified Data Memory and the high byte moved to TBLH.

-

Page 218: Package Information

HT45F8550 BMS Flash MCU Package Information Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the Holtek website the latest version of the Package/Carton Information. -

Page 219: 28-Pin Ssop (150Mil) Outline Dimensions

HT45F8550 BMS Flash MCU 28-pin SSOP (150mil) Outline Dimensions & " Dimensions in inch Symbol Min. Nom. Max. 0.236 BSC 0.154 BSC 0.008 — 0.012 C’ 0.390 BSC — — 0.069 0.025 BSC 0.004 — 0.010 0.016 — 0.050 0.004... -

Page 220: 48-Pin Lqfp-Ep (7Mm×7Mm) Outline Dimensions

HT45F8550 BMS Flash MCU 48-pin LQFP-EP (7mm×7mm) Outline Dimensions THERMALLY ENHANCED VARIATIONS ONLY Dimensions in inch Symbol Min. Nom. Max. 0.354 BSC 0.276 BSC 0.354 BSC 0.276 BSC 0.020 BSC 0.170 — 0.211 0.170 — 0.211 0.007 0.009 0.011 0.053 0.055... - Page 221 HOLTEK disclaims all liability arising from the information and its application. In addition, HOLTEK does not recommend the use of HOLTEK’s products where there is a risk of personal hazard due to malfunction or other reasons. HOLTEK hereby declares that it does not authorise the use of these products in life-saving, life-sustaining or safety critical components.

Need help?

Do you have a question about the HT45F8550 and is the answer not in the manual?

Questions and answers