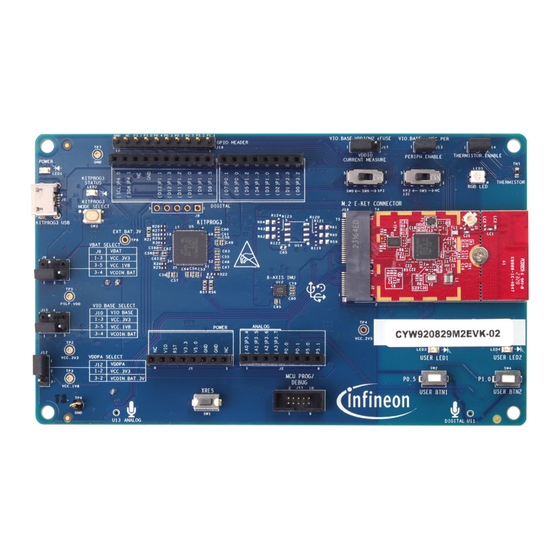

Infineon AIROC CYW20829 Manual

Bluetooth & bluetooth le system on chip hardware design guidelines for two-layer pcb

Hide thumbs

Also See for AIROC CYW20829:

- User manual (54 pages) ,

- Manual (19 pages) ,

- Quick start manual (4 pages)

Table of Contents

Advertisement

Quick Links

AN239046

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE

system on chip hardware design guidelines for

two-layer PCB

About this document

Scope and purpose

This document provides hardware guidance on how to design a two-layer PCB with CYW20829.

Intended audience

This document is intended for hardware engineers creating two-layer PCB layout designs with CYW20829.

Application note

Please read the sections "Important notice" and "Warnings" at the end of this document

002-39046 Rev **

www.infineon.com

2023-12-22

Advertisement

Table of Contents

Summary of Contents for Infineon AIROC CYW20829

-

Page 1: About This Document

This document provides hardware guidance on how to design a two-layer PCB with CYW20829. Intended audience This document is intended for hardware engineers creating two-layer PCB layout designs with CYW20829. Application note Please read the sections “Important notice” and “Warnings” at the end of this document 002-39046 Rev ** www.infineon.com 2023-12-22... -

Page 2: Table Of Contents

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Table of contents Table of contents About this document ........................1 Table of contents ..........................2 Introduction .......................... 3 Schematic design considerations ..................... 4 PAVDD supply for CYW20829 ........................4 Crystal specifications and requirements .................... -

Page 3: Introduction

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Introduction Introduction This document provides basic guidelines on the two-layer PCB layout for CYW20829. Document structure Section 2, Schematic design considerations provides the schematic design considerations. •... -

Page 4: Schematic Design Considerations

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Schematic design considerations Schematic design considerations PAVDD supply for CYW20829 For CYW20829 Class 1.5, BT_PAVDD must be connected to VCCPA_0 (PALDO_OUT (2.5 V)) • For CYW20829 Class 2.0, BT_PAVDD must be connected to VCCRF (RFLDO_OUT (1.2 V)) •... - Page 5 AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Schematic design considerations Table 1 Reference crystal electrical specifications for 24 MHz crystal Parameter Conditions Minimum Typical Maximum Unit Nominal frequency 24.000 Oscillation mode Fundamental Frequency accuracy Includes operating temperature ±20...

-

Page 6: Rf Filter

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Schematic design considerations Table 2 32 kHz XTAL oscillator characteristics Parameter Symbol Conditions Minimum Typical Maximum Unit Output frequency – – – oscout Frequency tolerance –... -

Page 7: Programming Interface

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Schematic design considerations Programming interface CYW20829 adopts MiniProg4 as a programming and debug kit. A 5-pin or 10-pin connector is needed to connect to MiniProg4 (see Figure Figure 5 MiniProg4... -

Page 8: Hci Uart Interface

HCI UART CTS To connect these GPIOs, a connector or test points are necessary. These GPIOs can be used for other functionality as well. Note: Contact Infineon support for the HCI mode configuration FW. Application note 002-39046 Rev ** 2023-12-22... -

Page 9: Component Placement For Two-Layer Pcb

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB Component placement for two-layer PCB A two-layer PCB is possible for CYW20829 design to optimize cost. As a rule, the order of the front-end component placement should follow the received signal flow from the antenna to the antenna matching circuit, filter circuit, and to the chip RF pin. -

Page 10: Antenna Placement

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB Figure 7 Bypass capacitors in the PMU and RF front-end area Antenna placement Place the PCB antenna as close as possible to the CYW20829 chip. Always place the antenna in a corner of the PCB with sufficient clearance from the rest of the circuit. - Page 11 AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB Antenna tuning TOP layer RF Trace Components Antenna Two ground Solid ground beneath RF vias trace on the bottom layer within the green area Two ground Bottom layer...

-

Page 12: Rf Filter

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB RF filter Place the filter between the antenna matching components and the CYW20829 device to attenuate harmonics from CYW20829. A 50 Ω impedance microstrip is used for all connections of the filter. Components need to be placed together as closely as possible. -

Page 13: Crystal Placement

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB PIN 16 Sufficient GND vias As short as possible Power Inductor No other signal L1 4.7 μH overlap with it on the bottom layer Figure 10 Power inductor isolation and placement... - Page 14 AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Component placement for two-layer PCB Load cap 24M Crystal The bottom layer must be solid ground within the green area The bottom layer must be solid 32K Crystal ground within the green area...

-

Page 15: Pcb Layers And Routing

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB PCB layers and routing PCB layers and routing Ground vias Do not use long and thin traces to connect components to ground vias; instead, cover the entire ground pad with ground copper and place the ground vias as close to the ground pad as possible. -

Page 16: References

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB References References A wealth of data is available at www.infineon.com to help you to select the right device, and quickly and effectively integrate the device into your design. [1] Datasheets CYW20829 −... -

Page 17: Revision History

AIROC™ CYW20829 Bluetooth® & Bluetooth® LE system on chip hardware design guidelines for two-layer PCB Revision history Revision history Document Date Description of changes revision 2023-12-22 Initial release. Application note 002-39046 Rev ** 2023-12-22... -

Page 18: Disclaimer

All referenced product or service names and trademarks are the property of their respective owners. The Bluetooth® word mark and logos are registered trademarks owned by Bluetooth SIG, Inc., and any use of such marks by Infineon is under license.

Need help?

Do you have a question about the AIROC CYW20829 and is the answer not in the manual?

Questions and answers