Table of Contents

Advertisement

Quick Links

Circuits from the Lab

neered and tested for quick and easy system integra-

tion to help solve today's analog, mixed-signal, and

RF design challenges. For more information and/or

support, visit

10 Mbps/100 Mbps/1000 Mbps Dual Channel, Low Power Industrial Ethernet PHY

EVALUATION AND DESIGN SUPPORT

Circuit Evaluation Boards

►

CN0506 Circuit Evaluation Board (EVAL-CN0506-FMCZ)

►

Design and Integration Files

►

Schematics, Layout Files, Bill of Materials

►

CIRCUIT FUNCTIONS AND BENEFITS

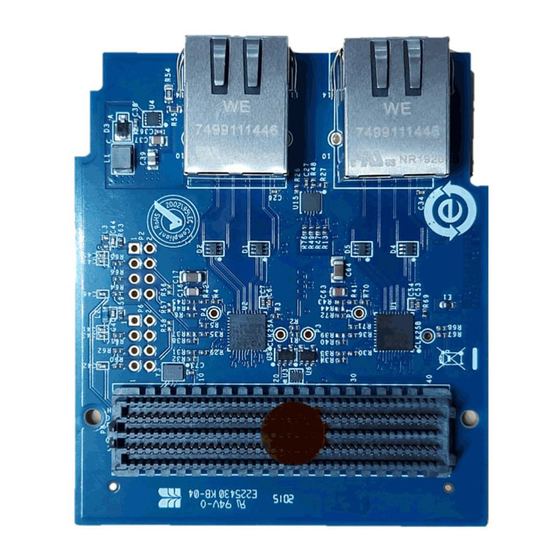

The circuit shown in

Figure 1

is a dual channel, low latency,

low power Ethernet physical layer (PHY) card that supports 10

Mbps, 100 Mbps, and 1000 Mbps speeds for industrial Ethernet

applications using line and ring network topologies.

Dual channels enable line and ring network topologies that are

commonly used for industrial sensing, control, and distributed con-

trol systems. The Ethernet PHY was extensively tested for electro-

magnetic compatibility (EMC) and electrostatic discharge (ESD)

robustness and supports automatic negotiation to enable linking

with remote PHY devices at the highest common speed advertised.

IEEE 1588 time stamping in the PHY reduces timing uncertainty

Figure 1. EVAL-CN0506-FMCZ Simplified Block Diagram (All Connections and Decoupling Not Shown)

analog.com

Circuits from the Lab

engineers. Standard engineering practices have been employed in the design and construction of each circuit,

and their function and performance have been tested and verified in a lab environment at room temperature.

However, you are solely responsible for testing the circuit and determining its suitability and applicability for

your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special,

incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any

Circuits from the Lab circuits. (Continued on last page)

®

reference designs are engi-

www.analog.com/CN0506.

™

circuits from Analog Devices have been designed and built by Analog Devices

Devices Connected/Referenced

ADIN1300

Robust, Industrial, Low Latency and Low Power

10 Mbps, 100 Mbps, and 1 Gbps Ethernet PHY

LT3502

1.1 MHz, 500 mA Step-Down Regulator

2

LTC4316

Single I

C/SMBus Address Translator

in real-time applications and enhances link loss detection for redun-

dant and real-time applications.

The circuit consists of two individual, independent 10 Mbps, 100

Mbps, and 1000 Mbps PHYs, each with an energy efficient Ethernet

(EEE) PHY core with all the associated common analog circuitry,

input and output clock buffering, management interface, subsystem

registers, media access control (MAC) interface, and control logic.

The design is powered from the host field programmable gate array

(FPGA) mezzanine card (FMC) development board, eliminating the

need for an external power supply. A software programmable clock

enables media independent interface (MII), reduced MII (RMII), and

reduced Gigabit MII (RGMII) MAC interface modes. RJ45 ports with

integrated magnetics keep the solution as compact as possible.

The solution supports cable lengths up to 150 meters at gigabit

speeds and up to 180 meters at 100 Mbps or 10 Mbps.

This solution is typically used in ring or bus topologies. The auto-

matic negotiation feature allows connection with other PHY devices

at the highest supported speed.

Circuit Note

CN-0506

Rev. A | 1 of 6

Advertisement

Table of Contents

Summary of Contents for Analog Devices CN-0506

- Page 1 However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any...

- Page 2 Circuit Note CN-0506 CIRCUIT DESCRIPTION A PHY is the physical interface transceiver that implements the ETHERNET physical layer functions of the open systems interconnection (OSI) model. A PHY encodes and decodes the data transmitted and Ethernet is the most common type of packet-based physical con-...

- Page 3 Circuit Note CN-0506 By default, the clock for each channel is set to 25 MHz on power PHYSICAL LAYER—MAC INTERFACE up. When using the RMII MAC interface, the clock can be program- The MAC interface is the wired medium on the CN0506 and there med to 50 MHz.

- Page 4 The Linux device tree supported for the different modes and carrier combinations can be found on the CN0506 HDL page. For more information on the standard Analog Devices, Inc., Linux image, see Figure 4. Peak PHY Differential Output Voltage FPGA Image user guide.

- Page 5 Xilinx ZC706. An HDMI monitor ► 6. Use the USB Type A dongle to connect the wireless keyboard Analog Devices, Inc. Linux image, configured for use with the ► and mouse to the USB OTG adaptor. CN0506 7. Apply the power connector to the Xilinx ZC706 and plug the other end into the wall.

- Page 6 Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab circuits at any time without notice but is under no obligation to do so.

Need help?

Do you have a question about the CN-0506 and is the answer not in the manual?

Questions and answers