Table of Contents

Advertisement

Quick Links

Copyright

Copyright © 2021 MITAC COMPUTING TECHNOLOGY CORPORATION. All rights

reserved. No part of this manual may be reproduced or translated without prior

written consent from MITAC COMPUTING TECHNOLOGY CORPORATION.

Trademark

All registered and unregistered trademarks and company names contained in this

manual are property of their respective owners including, but not limited to the

following.

®

TYAN

is a trademark of MITAC COMPUTING TECHNOLOGY CORPORATION.

®

Intel

is a trademark of Intel

AMI, AMI BIOS are trademarks of AMI Technologies.

Microsoft

®

, Windows

®

Nuvoton

is a trademark of Nuvoton Technology Corporation.

Notice

Information contained in this document is furnished by MITAC COMPUTING

TECHNOLOGY CORPORATION and has been reviewed for accuracy and reliability

prior to printing. MITAC assumes no liability whatsoever, and disclaims any express

or implied warranty, relating to sale and/or use of TYAN

or warranties relating to fitness for a particular purpose or merchantability. MITAC

retains the right to make changes to product descriptions and/or specifications at

any time, without notice. In no event will MITAC be held liable for any direct or

indirect, incidental or consequential damage, loss of use, loss of data or other

malady resulting from errors or inaccuracies of information contained in this

document.

S7105

Version 1.0i

®

Corporation.

®

are trademarks of Microsoft Corporation.

http://www.tyan.com

®

products including liability

1

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for TYAN S7105

- Page 1 TECHNOLOGY CORPORATION and has been reviewed for accuracy and reliability prior to printing. MITAC assumes no liability whatsoever, and disclaims any express ® or implied warranty, relating to sale and/or use of TYAN products including liability or warranties relating to fitness for a particular purpose or merchantability. MITAC retains the right to make changes to product descriptions and/or specifications at any time, without notice.

- Page 2 http://www.tyan.com...

-

Page 3: Table Of Contents

4.1 Flash Utility ..................143 4.2 AMIBIOS Post Code (Aptio) ............144 Appendix I: How to recover UEFI BIOS ..........151 Appendix II: Fan and Temp Sensors ............ 153 Glossary ....................157 Technical Support .................. 163 http://www.tyan.com... -

Page 4: Before You Begin

1 x S7105 Motherboard 2 x CPU clip for Narrow Non-Fabric CPU Carrier 2 x M.2 Screw Kit 1 x S7105 Quick reference guide ® 1 x TYAN Driver’s and Utilities DVD IMPORTANT NOTE: Sales sample may not come with the accessory listed above. -

Page 5: Chapter 1: Instruction

S7105 is capable of offering scalable 32 and 64-bit computing, high-bandwidth memory design, and lightning-fast PCI-E bus implementation. The S7105 not only empowers you in today’s demanding IT environment but also offers a smooth path for future application upgradeability. All of these rich feature sets provides the S7105 with the power and flexibility to meet demanding requirements for today’s IT environments. - Page 6 Intel Optane DC Notification Persistent Memory Module (DCPMM) only supported with specific 2nd Gen Intel Xeon Scalable Processor (codename: Cascade Lake). Please contact Tyan Technical Support for more detail. (1) PCI-E Gen3 x16 slot, (5) PCI-E Expansion Slots PCI-E Gen3 x16 slots...

- Page 7 USB device/PXE via LAN/Storage, Feature User Configurable FAN PWM Duty Cycle, Console Redirection, ACPI sleeping states S4,S5, ACPI 6.1 Form Factor Proprietary Physical Dimension Board Dimension 14.2" x 13.2" (361.5 x 336.2mm) FCC (DoC) Class B Regulation CE (DoC) Class A http://www.tyan.com...

-

Page 8: Software Specifications

Mechanical Compliant KFT48 Chassis NOTE: 1. The specifications are subject to change without notice. 2. Please visit our Web site for the latest update. 1.3 Software Specifications ® For OS (operation system) support, please check with TYAN support for latest information. http://www.tyan.com... -

Page 9: Chapter 2: Board Installation

To avoid damaging the motherboard and associated components, do not use torque force greater than 5~7 kgf/cm (4.35 ~ 6.09 lb/in) on each mounting screw for motherboard installation. Do not apply power to the board if it has been damaged. http://www.tyan.com... -

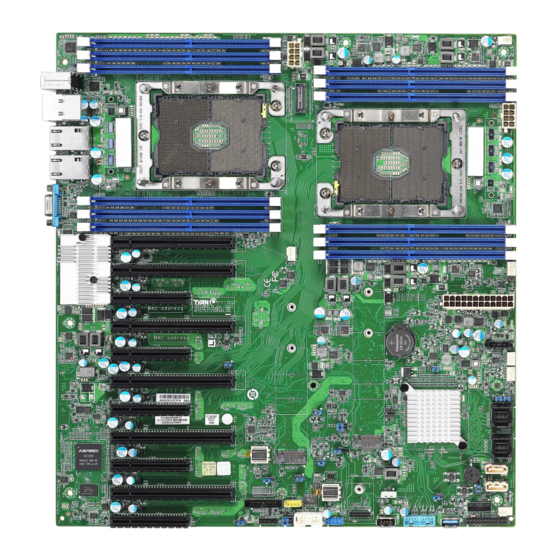

Page 10: Board Image

2.1 Board Image S7105 This picture is representative of the latest board revision available at the time of publishing. The board you receive may not look exactly like the above picture. http://www.tyan.com... -

Page 11: Block Diagram

2.2 Block Diagram S7105 Block Diagram http://www.tyan.com... -

Page 12: Mainboard Mechanical Drawing

2.3 Mainboard Mechanical Drawing http://www.tyan.com... -

Page 13: Board Parts, Jumpers And Connectors

The board you receive may not look exactly like the above diagram. But for the DIMM number please refer to the above placement for memory installation. For the latest board revision, please visit our web site at http://www.tyan.com. http://www.tyan.com... - Page 14 PCI Express Gen 3 x 8 (PCIE_9) PCI Express Gen 3 x16 (PCIE_4) PCI Express Gen 3 x16 (PCIE_10) PCI Express Gen 3 x 8 (PCIE_5) PCI Express Gen 3 x16 (PCIE_11) PCI Express Gen 3 x 16 (PCIE_6) http://www.tyan.com...

- Page 15 Jumper Legend OPEN - Jumper OFF Without jumper cover CLOSED - Jumper ON With jumper cover http://www.tyan.com...

- Page 16 HDD_LED- FAULT_LED2- PWR_SW# LAN1_ACTLED+ LAN1_ACTLED- RST_SW# SMBUS_SDA SMBUS_SCL SYS_ID_SW# INTRUSION# TEMP_SENSOR LAN2_ACTLED+ NMI_SW# LAN2_ACTLED- TYPEA_USB2: Vertical Type-A USB2.0 Connector Signal Signal USB_VCC_TYPE_A USB_N2_TYPE_A1_R USB_P2_TYPE_A1_R TYPEA_USB3: Vertical Type-A USB3.0 Connector Signal Signal SSRX- SSRX+ USB DATA2- USB DATA2+ SSTX- SSTX+ http://www.tyan.com...

- Page 17 HD_COM2: COM Port Header Signal Signal Key-Pin SSATA0/SSATA1: SATA DOM Connector PIN Define SATA TX DP SATA TX DN Connects to the Serial ATA ready drives via SATA RX DN the Serial ATA cable. SATA RX DP VCC 5V http://www.tyan.com...

- Page 18 J122: VROC Header (full featured RAID 0, 1, 10, 5, using Intel VROC, for NVMe SSD SKU) Signal Signal VCC3_AUX PCH_SATA_RAID_KEY J202: Chassis Intrusion Header Signal Signal INTRUDER SSATA_SGPIO1: SSATA SGPIO Pin Header Signal Signal SSDATA IN SSDATA OUT SSLOAD SSCLOCK P3V3_AUX http://www.tyan.com...

- Page 19 VGA2: Front Panel VGA Header Signal Signal VGA_HD_5V VGA_HD_R VGA_HD_G HD_VGA_B VGA_HD_DAT VGA_HD_HS VGA_HD_CLK VGA_HD_VS http://www.tyan.com...

- Page 20 FAN_HD1: Fan Connector (Reserved for Barebone) Signal Signal FAN_T1 FAN_T6 FAN_T2 FAN_T7 FAN_T3 FAN_T8 FAN_T4 FAN_T9 FAN_T5 FAN_T10 PWM_REAR12 PWM_FRONT3 FAN_T11 FAN_SDA FAN_T12 FAN_SCK VCC3_AUX PWM_BB3 PWR_BTN1: System Power Button Signal Signal FP_PWR_BTN_N FP_PWR_BTN_N RST_BTN1: System Reset Button Signal Signal FP_RST_BTN_N FP_RST_BTN_N http://www.tyan.com...

- Page 21 3. Move the jumper cap to close Pin_2 and Pin_3 for several seconds to Clear CMOS. 4. Put jumper cap back to Pin_1 and Pin_2 (Default setting). 5. Reconnect power connectors to the motherboard and power on Clear CMOS system. DBG_HD1: TYAN Module Header Signal Signal VCC3 LPC_FRAME_N LAD0...

-

Page 22: Led Definitions

2.5 LED Definitions http://www.tyan.com... - Page 23 Beat LED The LED blinks per second to Blinking Green indicate that the BMC controller is working normally The green LED lights up when Green the power of PCH is normal. Signal + VCC3_AUX Rear ID ID_LED State Description http://www.tyan.com...

-

Page 24: Installing The Processor And Heat Sink

Specifications on page 5. Check our website at http://www.tyan.com for latest processor support. NOTE: MITAC TYAN is not liable for damage as a result of operating an unsupported configuration. Processor Installation for LGA3647 Socket Follow the steps below to install the processors and heat sinks. NOTE: Please save and replace the CPU protection cap when returning for service. - Page 25 Save and replace the CPU cover if the processor is removed from its socket. Align the heatsink with the CPU socket by the guide pins and make sure the gold arrow is located in the correct direction. Then place the heatsink onto the top of the CPU socket. http://www.tyan.com...

- Page 26 NOTE: When disassembling the heatsink, loosen the screws in reverse order (4321). NOTE: Always check with the manufacturer of the heat sink & processor to ensure that the thermal interface material is compatible with the processor and meets the manufacturer’s warranty requirements. http://www.tyan.com...

-

Page 27: Tips On Installing Motherboard In Chassis

If there are any studs missing, you will know right away since the motherboard will not be able to be securely installed. http://www.tyan.com... - Page 28 Some chassis include plastic studs instead of metal. Although the plastic studs are usable, MITAC recommends using metal studs with screws that will fasten the motherboard more securely in place. Below is a chart detailing what the most common motherboard studs look like and how they should be installed. http://www.tyan.com...

-

Page 29: Installing The Memory

Before installing memory, ensure that the memory you have is compatible with the http://www.tyan.com motherboard and processor. Check the TYAN Web site at for details of the type of memory recommended for your motherboard. This platform supports (6)+(6) DDR4 RDIMM/RDIMM 3DS/LRDIMM/ LRDIMM 3DS 2933/2666 / Intel Optane DC Persistent Memory Module (DCPMM) ... - Page 30 2. Use paired memory installation for max performance. 3. Populate the same DIMM type in each channel, specifically - Use the same DIMM size - Use the same # of ranks per DIMM 4. Always install with CPU0 Socket first. http://www.tyan.com...

- Page 31 Quantity of Memory Module Populated Single CPU Populated (CPU0) P0_MC0_DIM_CH_A0 P0_MC0_DIM_CH_B0 P0_MC0_DIM_CH_C0 Recommended P0_MC1_DIM_CH_D0 P0_MC1_DIM_CH_E0 P0_MC1_DIM_CH_F0 Quantity of Memory Module Populated Dual CPU Populated (CPU0 & CPU1) P0_MC0_DIM_CH_A0 P0_MC0_DIM_CH_B0 P0_MC0_DIM_CH_C0 P0_MC1_DIM_CH_D0 P0_MC1_DIM_CH_E0 P0_MC1_DIM_CH_F0 Recommended P1_MC0_DIM_CH_A0 P1_MC0_DIM_CH_B0 P1_MC0_DIM_CH_C0 P1_MC1_DIM_CH_D0 P1_MC1_DIM_CH_E0 P1_MC1_DIM_CH_F0 http://www.tyan.com...

- Page 32 1 DCPMM per socket and 1 DCPMM per node case. DDR4 Type Capacity DRAM1 RDIMM 3DS RDIMM LRDIMM 3DS LRDIMM Any Capcity DRAM2 RDIMM 3DS RDIMM LRDIMM 3DS LRDIMM Any Capacity and Preferably, >=32GB DRAM3 RDIMM 16GB or 32GB DRAM4 RDIMM 3DS RDIMM LRDIMM Any Capacity http://www.tyan.com...

- Page 33 Memory Installation Procedure Follow these instructions to install memory modules into the S7105. Unlock the clips as shown in the illustration. Insert the memory module firmly into the socket by gently pressing down until it sits flush with the socket.

-

Page 34: Attaching Drive Cables

2.9 Attaching Drive Cables Attaching Serial ATA Cables S7105 is equipped with two (2) Serial ATA (SATA) channel. Connections for the drives are very simple. There is no need to set Master/Slave jumpers on SATA drives. If you are in need of SATA/SAS cables or power adapters please contact your place of purchase. -

Page 35: Installing Add-In Cards

Doing so allows air to circulate within the chassis more easily, thus improving cooling for all installed devices. NOTE: You must always unplug the power connector to the motherboard before performing system hardware changes to avoid damaging the board or expansion device. http://www.tyan.com... -

Page 36: Connecting External Devices

10/100/1000 Mbps LAN Link/Activity LED Scheme Left LED Right LED Link Green 10 Mbps Active Blinking Green Solid Green Link Green 100 Mbps Solid Green Active Blinking Green Solid Yellow Link Green 1000 Mbps Solid Yellow Active Blinking Green No Link http://www.tyan.com... -

Page 37: Installing The Power Supply

2.12 Installing the Power Supply There are three (3) power connectors on your S7105 motherboard. The S7105 supports EPS 12V power supply. PWCN1: ATX 24-pin Main Power Connector Signal Signal VCC3 VCC3 VCC3 -12V VCC5 PS_ON# VCC5 PWR_OK 5VSB VCC5... -

Page 38: Finishing Up

In the rare circumstance that you have experienced difficulty, you can find help by asking your vendor for assistance. If they are not available for assistance, please find setup information and documentation online at our website or by calling your vendor’s support line. http://www.tyan.com... -

Page 39: Chapter 3: Bios Setup

The table below shows how to navigate in the setup program using the keyboard. Function Left/Right Arrow Keys Change from one menu to the next Up/Down Arrow Keys Move between selections Enter Open highlighted section PgUp/PgDn Keys Change pages Change options Exit http://www.tyan.com... - Page 40 The following pages provide the details of BIOS menu. Please be noticed that the BIOS menu are continually changing due to the BIOS updating. The BIOS menu provided are the most updated ones when this manual is written. Please visit TYAN’s website at http://www.tyan.com for the information of BIOS updating.

-

Page 41: Main Menu

Note that the options listed below are for options that can directly be changed within the Main Setup screen. System Date Set the Date. Use Tab to switch between Date elements. Default Ranges: Year: 2010-2079 Months: 1-12 Days: dependent on month System Time Set the Time. Use Tab to switch between Time elements. http://www.tyan.com... -

Page 42: Advanced Menu

This formset allows the user to manage Intel® Virtual RAID on CPU. Trusted Computing Trusted Computing Settings. ACPI Settings System ACPI Parameters. S5 RTC Wake Settings Enable system to wake from S5 using RTC alarm. Serial Port Console Redirection Serial Port Console Redirection. http://www.tyan.com... - Page 43 USB Configuration Parameters. Onboard Device Configuration Onboard Device Configuration. Option ROM Dispatch Policy Option ROM Dispatch Policy. NVDIMM ADR Configuration NVDIMM ADR Configuration. AST2500 Super IO Configuration System Super IO Chip Parameters. Hardware Health Configuration Hardware health Configuration Parameters. http://www.tyan.com...

- Page 44 Select Advanced Network Stack Configuration Network Stack [Enabled] Step 3. Save changes and reboot. iSCSI Initiator Name The worldwide unique name of iSCSI Initiator. Only IQN format is accepted. Enter [iqn.xxx]. xxx ranges from 4 to 223. http://www.tyan.com...

- Page 45 3.3.1.1 Add an Attempt Read only. NOTE: Only LAN1 supports iSCSI function. http://www.tyan.com...

- Page 46 IP4 / IP6 / Autoconfigure Connection Retry Count The minimum value is 0 and the maximum is 16. 0 means no retry. Connection Establishing Timeout The timeout value in milliseconds. The minimum value is 100 milliseconds and the maximum is 20 seconds. http://www.tyan.com...

- Page 47 Target Port Target Port. Boot LUN Hexadecimal representation of the LU number. Examples are: 4752-3A4F-6b7e- 3F99, 6734-9-156f-127, 4186-9. Authentication Type Authentication method: CHAP, Kerberos, or None. CHAP / None Save Changes Must reboot system manually for changes to take place. http://www.tyan.com...

- Page 48 3.3.1.2 Delete Attempts Attempt 1 MAC: 34:12:78:56:00:00, PFA: Bus 1/ Dev 0 / Func 0, iSCSI mode: Disabled, IP version: IP4. Disabled / Enabled Commit Changes and Exit Commit Changes and Exit. Discard Changes and Exit Discard Changes and Exit. http://www.tyan.com...

- Page 49 Change the order of Attempts using +/- keys. Use arrow keys to select the attempt then press +/- to move the attempt up/down in the attempt order list. Attempt 1 / Attempt # Commit Changes and Exit Commit Changes and Exit. Discard Changes and Exit Discard Changes and Exit. http://www.tyan.com...

- Page 50 Socket Configuration ->VMD config for PStackN(CPUN) PCIE Slot Location PStack0(CPU0) VMD Port 1A PCIE_1 PStack0(CPU0) VMD Port 1C PCIE_2 PStack1(CPU0) VMD Port 2A PCIE_5 PStack1(CPU0) VMD Port 2C PCIE_6 http://www.tyan.com...

- Page 51 PCIE_7 PStack1(CPU1) VMD Port 2A PCIE_11 PStack2(CPU1) VMD Port 3A PCIE_9 PStack2(CPU1) VMD Port 3C PCIE_10 All Intel VMD Controllers Select to see more information about the Intel VMD Controllers. http://www.tyan.com...

- Page 52 3.3.2.1 All Intel VMD Controllers Create RAID Volume This page allows you to create a RAID volume. Non-RAID Physical Disks Read only. http://www.tyan.com...

- Page 53 Enable RAID spanned over VMD Controllers Enter RAID spanned over VMD Controllers. blank / X Port 0, VMD0, INTEL SSDPE2MD400G4 X – to Select Disk. blank / X Port 1, VMD1, INTEL SSDPEDME400G4 X – to Select Disk. blank / X http://www.tyan.com...

- Page 54 Create a volume with the settings specified above. NOTE: For Create Volume to be configurable, the following items Enable RAID spanned over VMD Controllers, Port 0, VMD0, INTEL SSDPE2MD400G4 and Port 1, VMD1, INTEL SSDPEDME400G4 must be set to [X]. http://www.tyan.com...

- Page 55 3.3.2.1.1.1 Create Volume Press ‘y’ to create, ‘n’ to discard. Volume0, RAID0(Stripe), 708.0GB, Normal Select to see more information about the RAID volume. http://www.tyan.com...

- Page 56 3.3.2.1.1.1.1 Volume0, RAID0(Stripe), 708.0GB, Normal Read only. http://www.tyan.com...

- Page 57 3.3.2.1.1.1.1.1 Delete Delete the RAID Volume Deleting a volume will reset the disks to non-RAID. Yes / No http://www.tyan.com...

- Page 58 3.3.2.1.2 Port 0, VMD0, INTEL SSDPE2MD400G4 SN: xxxx, … Port 1, VMD1, INTEL SSDPEDMD400G4 SN: xxxx, …. Read only. http://www.tyan.com...

- Page 59 3.3.3 Trusted Computing Security Device Support Enables or Disables BIOS support for security device. O.S. will not show Security Device. TCG EFI protocol and INT1A interface will not be available. Enabled / Disabled http://www.tyan.com...

- Page 60 3.3.4 ACPI Settings Enable ACPI Auto Configuration Enable or disable BIOS ACPI Auto Configuration. Disabled / Enabled Enable Hibernation Enable or disable System ability to Hibernate (OS/S4 Sleep State). This option may not be effective with some OS. Disabled / Enabled http://www.tyan.com...

- Page 61 Select 0-23. For example enter 3 for 3am and 15 for 3pm. Wake up minute Select 0-59 for Minute. Wake up second Select 0-59 for Second. When Wake system from S5 is set to [Dynamic Time] Wake up Minute increase 1-5. http://www.tyan.com...

- Page 62 Console redirection enable or disable. Disabled / Enabled Legacy Console Redirection Settings Legacy Console redirection settings. Console Redirection Settings The settings specify how the host computer (which the user is using) will exchange data. Both computers should have the same or compatible settings. http://www.tyan.com...

- Page 63 1’s in the data bits is odd. Mark: parity bit is always 1. Space: parity bit is always 0. Mark and Space parity do not allow for error detection. None / Even / Odd / Mark / Space http://www.tyan.com...

- Page 64 Redirection after BIOS POST The settings specify if BootLoader is selected than Legacy console redirection is disabled before booting to Legacy OS. Default value is Always Enable which means Legacy Console Redirection is enabled for Legacy OS. Always Enable / BootLoader http://www.tyan.com...

- Page 65 3.3.6.2 Legacy Console Redirection Settings Legacy Serial Redirection Port Select a COM port to display redirection of Legacy OS and Legacy OPROM Messages. COM1 http://www.tyan.com...

- Page 66 VT-UTF8 / VT100 / VT100+ / ANSI Bits per Second Select serial port transmission speed. The speed must be matched on the other side. Long or noisy lines may require lower speeds. 115200 / 9600 / 19200 / 57600 http://www.tyan.com...

- Page 67 ‘start’ signal can be sent to restart the flow. Hardware flow control uses two wires to send start/stop signal. None / Hardware RTS/CTS / Software Xon/Xoff Data Bits / Parity / Stop Bits Read only. http://www.tyan.com...

- Page 68 Enables or Disables 64bit capable Devices to be Decoded in Above 4G Address Space (Only if System Supports 64 bit PCI Decoding). Enabled / Disabled SR-IOV Support If system has SR-IOV capable PCIe Devices, this option Enables or Disables Single Root IO Virtualization Support. Enabled / Disabled http://www.tyan.com...

- Page 69 Enable Ipv4 HTTP Boot Support. If disabled IPV4 HTTP boot option will not be created. Disabled / Enabled Ipv6 PXE Support Enable Ipv6 PXE Boot Support. If disabled IPV6 PXE boot option will not be created. Disabled / Enabled http://www.tyan.com...

- Page 70 Enable Ipv6 HTTP Boot Support. If disabled IPV6 HTTP boot option will not be created. Disabled / Enabled PXE boot wait time Wait time to press ESC key to abort the PXE boot. Media detect count Number of times presence of media will be checked. http://www.tyan.com...

- Page 71 Legacy / Do not launch / UEFI Storage Controls the execution of UEFI and Legacy Storage OpROM. Legacy / Do not launch / UEFI Video Controls the execution of UEFI and Legacy Video OpROM Legacy / Do not launch / UEFI http://www.tyan.com...

- Page 72 Other PCI Devices Determines OpROM execution policy for devices other than Network, Storage, or Video. Legacy / Do not launch / UEFI http://www.tyan.com...

- Page 73 USB Mass Storage Driver Support Enable/Disable USB Mass Storage Driver Support. Enabled / Disabled Port 60/64 Emulation Enables I/O Port 60h/64h emulation support. This should be enabled for the complete USB keyboard legacy support for non-USB aware OSes. Enabled / Disabled http://www.tyan.com...

- Page 74 Maximum time the device will take before it properly reports itself to the Host Controller. ‘AUTO’ uses default value: for a Root port it is 100 ms, for a Hub port the delay is taken from Hub descriptor. Auto / Manual http://www.tyan.com...

- Page 75 Turn on / off Spread Spectrum Setting for IsCLK. Disabled / Enabled Chassis Intrusion detect Enabled: when a chassis open event is detected, the BIOS will record the event. Disabled / Enabled NMI Button Enable or Disable NMI button. Disabled / Enabled http://www.tyan.com...

- Page 76 Enable or disable onboard LAN1 Option ROM. Disabled / Enabled Onboard LAN2 (X550) Enable or disable onboard LAN2 Option ROM. Disabled / Enabled PCIE_1 Empty ~ PCIE_11 Empty Enable or Disable Option ROM execution for selected Slot. Disabled / Enabled http://www.tyan.com...

- Page 77 3.3.13 NVDIMM ADR Configuration Assert ADR on Reset Assert ADR on Reset. Disabled / Enabled Assert ADR on Shutdown Assert ADR on Shutdown. Disabled / Enabled http://www.tyan.com...

- Page 78 3.3.14 AST2500 Super IO Configuration Super IO Chip Read only. http://www.tyan.com...

- Page 79 / IO=3F8h, IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; / IO=2F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; / IO=3E8h, IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; / IO=2E8h, IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; http://www.tyan.com...

- Page 80 [Enabled]. PWM Minimal Duty Cycle PWM Minimal Duty Cycle. 15% Duty Cycle / 30% Duty Cycle / 45% Duty Cycle BMC Alert Beep Enable / Disable BMC Alert Beep. On / Off PMBus Support PMBus Support. Disabled / Enabled http://www.tyan.com...

- Page 81 http://www.tyan.com...

- Page 82 3.3.15.1 Sensor Data Register Monitoring When you enter the Sensor Data Register Monitoring submenu, you will see the following dialog window pop out. Please wait 8~10 seconds. NOTE: SDR can not be modified. Read only. http://www.tyan.com...

-

Page 83: Platform Configuration

3.4 Platform Configuration PCH Configuration Displays and provides option to change the PCH Settings. Server ME Configuration Configure Server ME Technology Parameters. http://www.tyan.com... - Page 84 PCH Devices Enable/Disable Intel® IO Controller Hub devices. PCI Express Configuration PCI Express Configuration settings. PCH SATA Configuration SATA devices and settings. PCH sSATA Configuration sSATA devices and settings. USB Configuration USB Configuration Settings. Azalia Configuration Azalia related configuration options. http://www.tyan.com...

- Page 85 PCH DFX Configuration PCH DFX Configuration Options. http://www.tyan.com...

- Page 86 3.4.1.1 PCH Devices Restore AC Power Loss Select AC Power state when power is reapplied after a power failure. Power On / Power Off / Last State http://www.tyan.com...

- Page 87 3.4.1.2 PCI Express Configuration PCI Express Root Port 1~20 PCI Express Root Port 1~20 Settings. http://www.tyan.com...

- Page 88 L1 Substates PCI Express L1 Substates settings. Disabled / L1.1 / L1.2 / L1.1 & L1.2 PCIe Speed Configure PCIe Speed. Auto / Gen1 / Gen2 / Gen3 Max Payload Size PCIE Max Payload Size Selection. MPL128B / MPL256B http://www.tyan.com...

- Page 89 Determines how SATA controller(s) operate. AHCI / RAID Port 0 Enable or Disable SATA Port. Disabled / Enabled Hot Plug Designates this port as Hot Pluggable. Disabled / Enabled Configure as eSATA Configures port as External SATA (eSATA). Disabled / Enabled http://www.tyan.com...

- Page 90 Otherwise all drives spin up at boot. Disabled / Enabled SATA Device Type Identify the SATA port is connected to Solid State Drive or Hard disk Drive. Hard Disk Drive / Solid State Drive http://www.tyan.com...

- Page 91 Determines how SATA controller(s) operate. AHCI / RAID Port 0 Enable or Disable SATA Port. Disabled / Enabled Hot Plug Designates this port as Hot Pluggable. Disabled / Enabled Configure as eSATA Configures port as External SATA (eSATA). Disabled / Enabled http://www.tyan.com...

- Page 92 Otherwise all drives spin up at boot. Disabled / Enabled sSATA Device Type Identify the SATA port is connected to Solid State Drive or Hard disk Drive. Hard Disk Drive / Solid State Drive http://www.tyan.com...

- Page 93 3.4.1.5 USB Configuration XHCI Idle L1 Enabled XHCI Idle L1. Disabled to workaround USB3 hot plug will fail after 1 hot plug removal. Please put the system to G3 for the new settings to take effect. Enabled / Disabled http://www.tyan.com...

- Page 94 3.4.1.6 Azalia Configuration Azalia Enable or Disable Azalia audio device. Enabled / Disabled http://www.tyan.com...

- Page 95 Enabled / Disabled Enable/Disable ADR Timer Held-off for DEBUG PURPOSES ONLY!. Enabled / Held-off ADR timer expire time Select proper ADR timer value: 25uS, 50uS, 100uS or 0. 25 uS / 50 uS / 100 uS / 0 us http://www.tyan.com...

- Page 96 ADR timer multiplier Select proper ADR timer multiplier: x1, 8, 24, 40, 56, 64, 72, 80, 88, 96. x1 / x8 / x24 / x40 / x56 / x64 / x72 / x80 / x88 / x96 http://www.tyan.com...

- Page 97 3.4.2 Miscellaneous Configuration Active Video Select active video type. Onboard Device / Offboard Device http://www.tyan.com...

- Page 98 3.4.3 Server ME Configuration Read only. http://www.tyan.com...

-

Page 99: Socket Configuration

Displays and provides option to change the UPI Settings. Memory Configuration Displays and provides option to change the Memory Settings. IIO Configuration Displays and provides option to change the IIO Settings. Advanced Power Management Configuration Displays and provides option to change the Power Management Settings. http://www.tyan.com... - Page 100 This should be enabled in order to boot legacy OSes that cannot support CPUs with extended CPUID functions. Disabled / Enabled Execute Disable Bit When disabled, forces the XD feature flag to always return 0. Disabled / Enabled Enable Intel® TXT Enables Intel® TXT. Disabled / Enabled http://www.tyan.com...

- Page 101 Hardware Prefetcher MLC Streamer Prefetcher (MSR 1A4h Bit[0]). Enabled / Disabled Adjacent Cache Prefetch MLC Spatial Prefetcher (MSR 1A4h Bit[1]). Enabled / Disabled Extended APCI Enable/Disable extended APIC support. Disabled / Enabled AES-NI Enable/disable AES-NI support. Disabled / Enabled http://www.tyan.com...

- Page 102 Selects the allocation size used to assign mmioh resources. Total mmioh space can be up to 32xgranularity. Per stack mmioh resource assignments are multiples of the granularity where 1 unit per stack is the default allocation. 1G / 4G / 16G / 64G / 256G / 1024G http://www.tyan.com...

- Page 103 Numa Enable or Disable Non uniform Memory Access (NUMA). Disabled / Enabled http://www.tyan.com...

- Page 104 3.5.3. UPI Configuration UPI General Configuration Displays and provides option to change the UPI General Settings. http://www.tyan.com...

- Page 105 Disable --- Reset it, Auto --- Auto decides based on Si Compatibility. Disabled / Enable / Auto Link L1 Enable Enable --- Set the c_l1_en, Disable --- Reset it, Auto --- Auto decides based on Si Compatibility. Disabled / Enable / Auto http://www.tyan.com...

- Page 106 3.5.3.1. UPI Status Read only http://www.tyan.com...

- Page 107 Maximum Memory Frequency Selections in Mhz. Do not select Reserved. Auto / 1866 / 2133 / 2400 / 2666 ECC Support Enable – Enables DDR ECC Support. Disable – Disables this feature. Auto – Sets it to MRC default setting: current default is Enable. Enabled / Disabled http://www.tyan.com...

- Page 108 3.5.4.1 Memory Topology Read only. http://www.tyan.com...

- Page 109 Partial mirror mode will enable the required size of memory to be mirrored. If rank sparing is enabled partial mirroring will not take effect. Mirror Enable will disable XPT Prefetch. Disabled / Partial Mirror mode 1LM / Partial Mirror mode 2LM Memory Rack Sparing Enable/Disable Memory Rank Sparing. Disabled / Enabled http://www.tyan.com...

- Page 110 Correctable Error Threshold Correctable Error Threshold (1 – 32767) used for sparing, tagging, and leaky bucket. SDDC Plus One Enable/Disable SDDC Plus One. Disabled / Enabled Patrol Scrub Enable/Disable Patrol Scrub. Disabled / Enabled http://www.tyan.com...

- Page 111 Enable/Disable PCIe ACPI Hot Plug globally, or allow per-port control. When Disabled, MSI is generated on HP event. When Enabled, _HPGPE message is generated. Disabled / Enable / Per-Port PCIe Access Control Services Enable or disable Access Control Services (ACS) in PCIe Downstream Switch Port. Disabled / Enable http://www.tyan.com...

- Page 112 Socket 0 PcieBr1D00F0 – Port 1A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). Socket 0 PcieBr2D00F0 – Port 2A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). Socket 0 PcieBr3D00F0 – Port 3A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). http://www.tyan.com...

- Page 113 Surprise Hot Plug Capable This option specifies if the link is considered Hot Plug capable. Disabled / Enabled PCI-E Port Link This option disables the link so that the no training occurs but the CFG space is still active. Enabled / Disabled http://www.tyan.com...

- Page 114 Disabled / Enabled Non-Transparent Bridge PCIe Port Definition Configures port as TB, NTB-NTB, or NTB-RP. Transparent Bridge / NTB to NTB / NTB to RP Hide Port? User can force to hide this root port from OS. No / Yes http://www.tyan.com...

- Page 115 Selects PCIe port Bifurcation for selected slot(s). x4x4x4x4 / x8x8 / x16 / Auto Socket 1 PcieBr1D00F0 – Port 1A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). Socket 1 PcieBr2D00F0 – Port 2A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). http://www.tyan.com...

- Page 116 Socket 1 PcieBr3D00F0 – Port 3A Settings related to PCI Express Ports (1A/1B/1C/1D/2A/2B/2C/2D/3A/3B/3C/3D). http://www.tyan.com...

- Page 117 Surprise Hot Plug Capable This option specifies if the link is considered Hot Plug capable. Disabled / Enabled PCI-E Port Link This option disables the link so that the no training occurs but the CFG space is still active. Enabled / Disabled http://www.tyan.com...

- Page 118 Disabled / Enabled Non-Transparent Bridge PCIe Port Definition Configures port as TB, NTB-NTB, or NTB-RP. Transparent Bridge / NTB to NTB / NTB to RP Hide Port? User can force to hide this root port from OS. No / Yes http://www.tyan.com...

- Page 119 3.5.5.3 Intel® VT for Directed I/O (VT-d) Intel® VT for Directed I/O (VT-d) Enable/Disable Intel® Virtualization Technology for Directed I/O (VT-d) by reporting the I/O device assignment to VMM through DMAR ACPI Tables. Enabled / Disabled http://www.tyan.com...

- Page 120 3.5.5.4 Intel® VMD Technology http://www.tyan.com...

- Page 121 Intel® VMD for Volume Management Device for PStack1 Enable/Disable Intel® Volume Management Device Technology in this Stack. Disabled / Enabled Intel® VMD for Volume Management Device for PStack2 Enable/Disable Intel® Volume Management Device Technology in this Stack. Disabled / Enabled http://www.tyan.com...

- Page 122 3.5.5.5 Advanced Power Management Configuration CPU P State Control P State Control Configuration Sub Menu, include Turbo, XE and ete. Hardware PM State Control Hardware P-State setting. CPU C State Control CPU C State setting. Package C State Control Package C State setting. http://www.tyan.com...

- Page 123 Max Performance / Max Efficient / Set by Intel Node Manager Energy Efficient Turbo Energy Efficient Turbo Disable, MSR 0x1FC [19]. Enabled / Disabled Turbo Mode Enable/Disable processor Turbo Mode (requires EMTTM enabled too). Disabled / Enabled CPU Flex Ratio Override Enable/Disable CPU Flex Ratio Programming. Disabled / Enabled http://www.tyan.com...

- Page 124 NOTE: When CPU Flex Ratio Override set to [Enabled], the following item can be configured. CPU Core Flex Ratio Non-Turbo Mode Processor Core Ratio Multiplier. http://www.tyan.com...

- Page 125 Disable: Hardware chooses a P-state based on OS Request (Legacy P-States). Native Mode: Hardware chooses a P-state based on OS guidance. Out of Band Mode: Hardware autonomously chooses a P-state (no OS guidance). Disabled / Native Mode / Out of Band Mode / Native Mode with NO Legacy Support http://www.tyan.com...

- Page 126 Enable/Disable CPU C6 (ACPI C3) report to OS. Disabled / Enabled / Auto Enhanced Halt State (C1E) Core C1E auto promotion Control. Takes effect after reboot. Disabled / Enabled OS ACPI Cx Report CC3/CC6 to OS ACPI C2 or ACPI C3. ACPI C2 / ACPI C3 http://www.tyan.com...

- Page 127 3.5.5.5.4 Package C State Control Package C State Package C State limit. C0/C1 state / C2 state / C6 (non Retention) state / C6 (Retention) state / No Limit / Auto http://www.tyan.com...

-

Page 128: Server Management

OS Watchdog Timer If enabled, starts a BIOS timer which can only be shut off by Management Software after the OS loads. Helps determine that the OS successfully loaded or follows the OS Boot Watchdog Timer policy. Enabled / Disabled http://www.tyan.com... - Page 129 Do Nothing / Reset / Power Down / Power Cycle BMC Logo Enable or Disable BMC Logo. Enabled / Disabled System Event Log Press <Enter> to change the SEL event log configuration. BMC network configuration Configure BMC network parameters. http://www.tyan.com...

- Page 130 Choose options for reactions to a full SEL. Do Nothing / Erase Immediately Log EFI Status Codes Disable the logging of EFI Status Codes or log only error code or only progress code or both. Disabled / Both / Error Code / Progress Code http://www.tyan.com...

- Page 131 BMC). Unspecified option will not modify any BMC network parameters during BIOS phase. Unspecified / Static / DynamicBmcDhcp / DynamicBmcNonDhcp Server Management Port 2 Enable/Disable BMC Share Nic. Enabled / Disabled Configure IPV6 Support Server Management Port 1 IPV6 Support Enable or Disable LAN1 IPV6 Support. Enabled / Disabled http://www.tyan.com...

- Page 132 Server Management Port 2 IPV6 Support Enable or Disable LAN1 IPV6 Support. Enabled / Disabled http://www.tyan.com...

-

Page 133: Security

Set user password in the Create New Password window. After you key in the password, the Confirm New Password window will pop out to ask for confirmation. Security Frozen Mode Enable or disable HDD security freeze lock. Disable to support secure erase function. Enabled / Disabled http://www.tyan.com... - Page 134 Secure boot activated when Platform Key (PK) is enrolled, System mode is User/Deployed, and CSM function is disabled. Disabled / Enabled Secure Boot Mode Secure Boot mode selector: Standard/Custom. In Custom mode Secure Boot Variables can be configured without authentication. Standard / Custom http://www.tyan.com...

- Page 135 Save NVRAM content of all Secure Boot variables to the files (EFI_SIGNATURE_LIST data format) in root folder on a target file system device. Platform Key (PK) Enroll Factory Defaults or load certificates from a file: 1. Public Key Certificate in: http://www.tyan.com...

- Page 136 EFI_CERT_X509 (DER encoded) c) EFI_CERT_RSA2048 (bin) d) EFI_CERT_SHA256, 384, 512 (bin) 2. Authenticated UEFI Variable 3. EFI PE/C0FF Image (SHA256) Key source: Default, External, Mixed, Test Set New / Append Authorized TimeStamps Enroll Factory Defaults or load certificates from a file: http://www.tyan.com...

- Page 137 Enroll Factory Defaults or load certificates from a file: 1. Public Key Certificate in: a) EFI_SIGNATURE_LIST b) EFI_CERT_X509 (DER encoded) c) EFI_CERT_RSA2048 (bin) d) EFI_CERT_SHA256, 384, 512 (bin) 2. Authenticated UEFI Variable 3. EFI PE/C0FF Image (SHA256) Key source: Default, External, Mixed, Test Set New / Append http://www.tyan.com...

-

Page 138: Boot

Bootup NumLock State Select the keyboard NumLock state. Off / On Quiet Boot Enable or disable Quiet Boot option. Disabled / Enabled Boot Option Priorities Boot Option #1 Select the first/second boot device. Device Name / Disabled http://www.tyan.com... - Page 139 Controls the placement of newly detected UEFI boot options. Default / Place First / Place Last Wait for ‘ESC’ If Error Wait for ‘ESC’ key to be pressed if error occurs. Disabled / Enabled Endless Boot Enable or disable Endless Boot. Disabled / Enabled http://www.tyan.com...

- Page 140 3.8.1 Delete Boot Option Boot Option #1 Remove an EFI boot option from the boot order. Select one to Delete / Device Name http://www.tyan.com...

-

Page 141: Save & Exit

Reset the system after saving the changes. Discard Changes and Reset Reset system setup without saving any changes. Save Changes Save changes done so far to any of the setup options. Discard Changes Discard changes done so far to any of the setup options. http://www.tyan.com... - Page 142 Restore Defaults Restore/Load Default values for all the setup options. Save as User Defaults Save the changes done so far as User Defaults. Restore User Defaults Restore the User Defaults to all the setup options. Boot Override Read only. http://www.tyan.com...

-

Page 143: Chapter 4: Diagnostics

BIOS flash failure, you must contact your dealer for a replacement BIOS. There are no exceptions. TYAN does not have a policy for replacing BIOS chips directly with end users. In no event will TYAN be held responsible for damages done by the end user. -

Page 144: Amibios Post Code (Aptio)

South Bridge initialization before microcode loading 0x05 OEM initialization before microcode loading 0x06 Microcode loading 0x07 AP initialization after microcode loading 0x08 North Bridge initialization after microcode loading 0x09 South Bridge initialization after microcode loading 0x0A OEM initialization after microcode loading 0x0B Cache initialization http://www.tyan.com... - Page 145 CPU post-memory initialization is started 0x33 CPU post-memory initialization. Cache initialization 0x34 CPU post-memory initialization. Application Processor(s) (AP) initialization 0x35 CPU post-memory initialization. Boot Strap Processor (BSP) selection 0x36 CPU post-memory initialization. System Management Mode(SMM) initialization 0x37 Post-Memory North Bridge initialization is started http://www.tyan.com...

- Page 146 Reserved for future AMI progress codes S3 Resume Error Codes 0xE8 S3 Resume Failed 0xE9 S3 Resume PPI not Found 0xEA S3 Resume Boot Script Error 0xEB S3 OS Wake Error 0xEC – 0xEF Reserved for future AMI error codes http://www.tyan.com...

- Page 147 CPU DXE initialization (CPU module specific) 0x67 CPU DXE initialization (CPU module specific) 0x68 PCI host bridge initialization 0x69 North Bridge DXE initialization is started 0x6A North Bridge DXE SMM initialization is started 0x6B North Bridge DXE initialization (North Bridge module specific) http://www.tyan.com...

- Page 148 USB initialization is started 0x9B USB Reset 0x9C USB Detect 0x9D USB Enable 0x9E -0x9F Reserved for future AMI codes 0xA0 IDE initialization is started 0xA1 IDE Reset 0xA2 IDE Detect 0xA3 IDE Enable 0xA4 SCSI initialization is started http://www.tyan.com...

- Page 149 No Console Output Devices are found 0xD7 No Console Input Devices are found 0xD8 Invalid password 0xD9 Error loading Boot Option (LoadImage returned error) 0xDA Boot Option is failed (StartImage returned error) 0xDB Flash update is failed 0xDC Reset protocol is not available http://www.tyan.com...

- Page 150 System is waking up from the S3 sleep state 0x40 System is waking up from the S4 sleep state 0xAC System has transitioned into ACPI mode. Interrupt controller is in PIC mode. 0xAA System has transitioned into ACPI mode. Interrupt controller is in APIC mode. http://www.tyan.com...

-

Page 151: Appendix I: How To Recover Uefi Bios

UEFI recovery bootloader that would prevent the recovery process itself from working. In no event shall Tyan be liable for direct, indirect, incidental, special or consequential damages arising from the BIOS update or recovery. - Page 152 “Flash update completed. Press any key to reset the system” displayed on screen. 8.Remove the USB disk and reboot. If your system does not have video output or the POST code halts at “FF” on the right-lower portion of the screen, please contact Tyan representatives for RMA service. http://www.tyan.com...

-

Page 153: Appendix Ii: Fan And Temp Sensors

The red spot indicates the sensor. Fan and Temp Sensor Location: Fan Sensor: It is located in the third pin of the fan connector, which detects the fan speed (rpm) Temp Sensor: refer to Figure 1: Sensor Location. They detect the system temperature around. http://www.tyan.com... - Page 154 BIOS Temp Sensor Name Explanation: http://www.tyan.com...

- Page 155 Temperature of the LSI SAS 3008 Chip P1_MOS_Area Temperature of the P1_MOS_Area P0_MOSFET_Temp The Max Temperature of CPU0 MOSFET P1_MOSFET_Temp The Max Temperature of CPU1 MOSFET The Max Temperature of CPU0 DIMM Area1 MOSFET P0_DIMM_MOS_1 The Max Temperature of CPU0 DIMM Area2 MOSFET P0_DIMM_MOS_2 http://www.tyan.com...

- Page 156 Temperature of GPU4 Core0 Slot GPU4_Core1_ TEMP Temperature of GPU4 Core1 Slot SYS_FAN_1 Fan Speed of SYS_FAN_1 SYS_FAN_2 Fan Speed of SYS_FAN_2 SYS_FAN_3 Fan Speed of SYS_FAN_3 SYS_FAN_4 Fan Speed of SYS_FAN_4 SYS_FAN_5 Fan Speed of SYS_FAN_5 SYS_FAN_6 Fan Speed of SYS_FAN_6 http://www.tyan.com...

-

Page 157: Glossary

(reading to or writing from a disk drive a single time is much faster than doing so repeatedly) there is the possibility of losing your data should the system crash. Information in a buffer is temporarily stored, not permanently saved. http://www.tyan.com... - Page 158 (like soundcards or keyboards) to access the main memory without involving the CPU. This frees up CPU resources for other tasks. As with IRQs, it is vital that you do not double up devices on a single line. Plug-n-Play devices will take care of this for you. http://www.tyan.com...

- Page 159 EEPROM (Electrically Erasable Programmable ROM): also called Flash BIOS, it is a ROM chip which can, unlike normal ROM, be updated. This allows you to keep ® up with changes in the BIOS programs without having to buy a new chip. TYAN ’s BIOS updates can be found at http://www.tyan.com...

- Page 160 PXE (Preboot Execution Environment): one of four components that together make up the Wired for Management 2.0 baseline specification. PXE was designed to define a standard set of preboot protocol services within a client with the goal of allowing networked-based booting to boot using industry standard protocols. http://www.tyan.com...

- Page 161 NVIDIA s (graphics communications processing units) and NVIDIA MCPs (media and processors). application Depending on the , NVIDIA SLI can deliver as much as two times the performance of a single GPU configuration. http://www.tyan.com...

- Page 162 CPUs without damaging the sensitive CPU pins. The CPU is lightly placed in an open ZIF socket, and a lever is pulled down. This shifts the processor over and down, guiding it into the board and locking it into place. http://www.tyan.com...

-

Page 163: Technical Support

(which can have expensive consequences). If these options are not available for you then TYAN can help. Besides designing innovative and quality products for over a decade, TYAN has continuously offered customers service beyond their expectations. - Page 164 (RMA) number. The RMA number Should be prominently displayed on the outside of the shipping carton and the package should be mailed prepaid. TYAN will pay to have the board shipped back to you. Notice for the USA Compliance Information Statement (Declaration of...

Need help?

Do you have a question about the S7105 and is the answer not in the manual?

Questions and answers